Flexible, Fan-Out, Wafer-Level Packaging Using Polydimethylsiloxane and Printed Redistribution Layers †

Abstract

1. Introduction

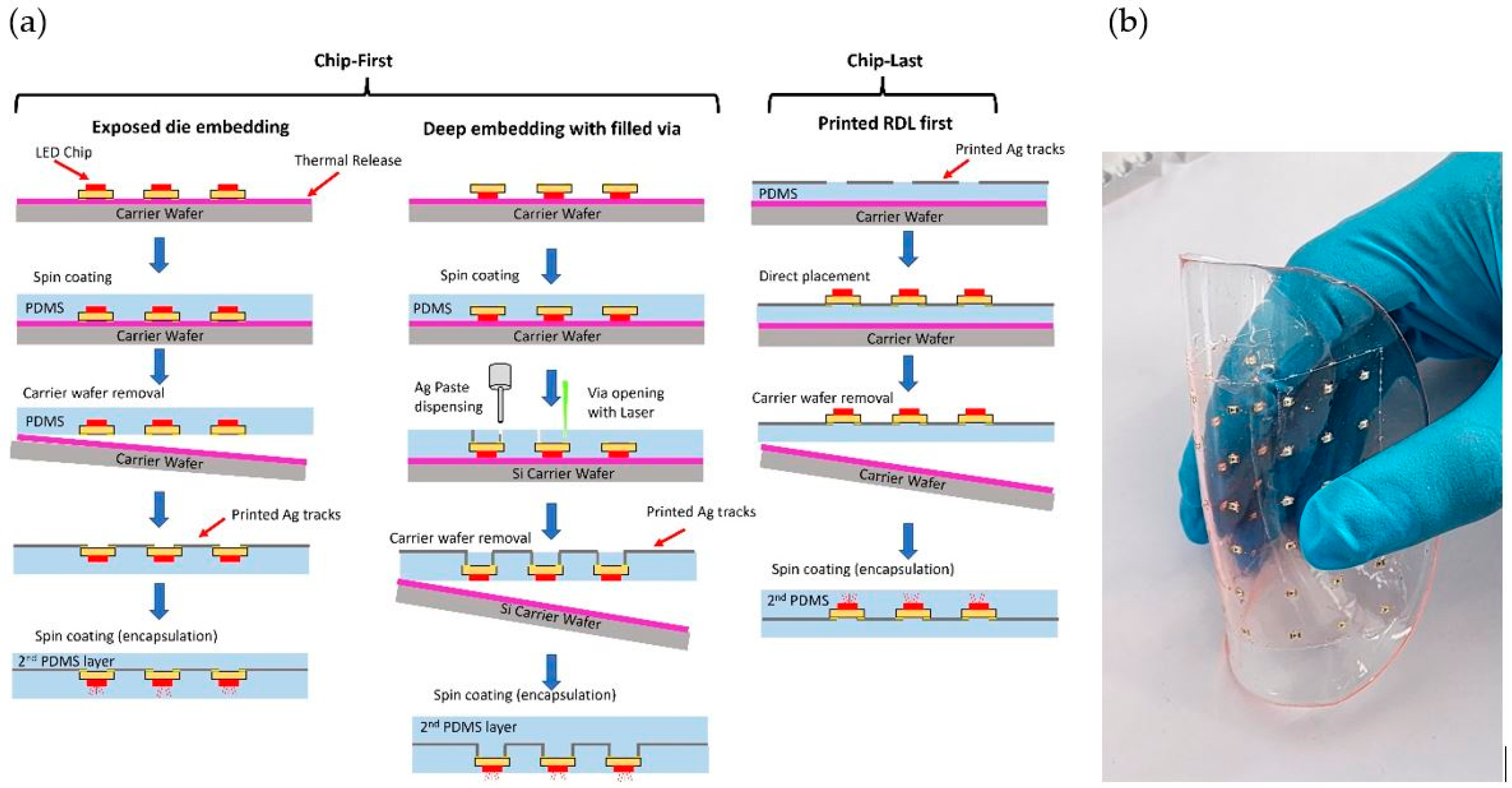

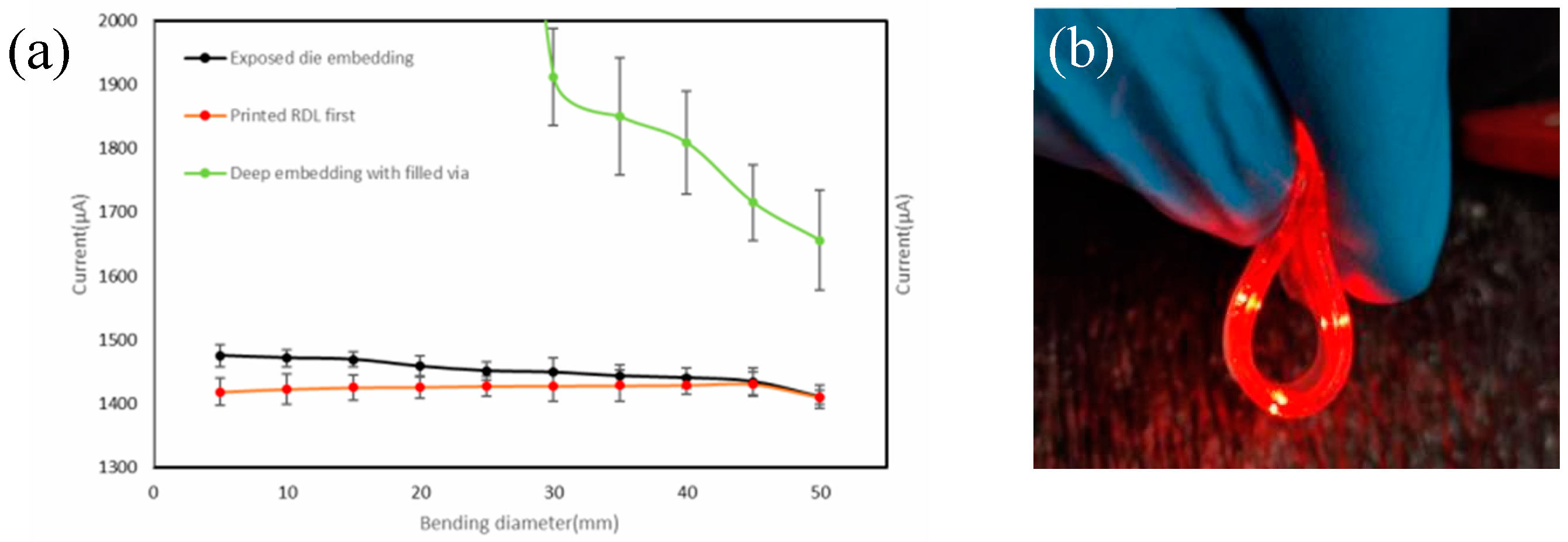

2. Results and Discussions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Iyer, S.S.; Alam, A. Flexible Hybrid Electronics Using Fan-Out Wafer-Level Packaging. In Embedded and Fan-Out Wafer and Panel Level Packaging Technologies for Advanced Application Spaces: High Performance Compute and System-in-Package; John Wiley & Sons: Hoboken, NJ, USA, 2021; pp. 233–260. [Google Scholar]

- Roshanghias, A.; Ma, Y.; Dreissigacker, M.; Braun, T.; Bretthauer, C.; Becker, K.-F.; Schneider-Ramelow, M. The Realization of Redistribution Layers for FOWLP by Inkjet Printing. Proceedings 2018, 2, 703. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Malik, M.H.; Khan, M.; Khan, S.; Roshanghias, A. Flexible, Fan-Out, Wafer-Level Packaging Using Polydimethylsiloxane and Printed Redistribution Layers. Proceedings 2024, 97, 153. https://doi.org/10.3390/proceedings2024097153

Malik MH, Khan M, Khan S, Roshanghias A. Flexible, Fan-Out, Wafer-Level Packaging Using Polydimethylsiloxane and Printed Redistribution Layers. Proceedings. 2024; 97(1):153. https://doi.org/10.3390/proceedings2024097153

Chicago/Turabian StyleMalik, Muhammad Hassan, Muhammad Khan, Sherjeel Khan, and Ali Roshanghias. 2024. "Flexible, Fan-Out, Wafer-Level Packaging Using Polydimethylsiloxane and Printed Redistribution Layers" Proceedings 97, no. 1: 153. https://doi.org/10.3390/proceedings2024097153

APA StyleMalik, M. H., Khan, M., Khan, S., & Roshanghias, A. (2024). Flexible, Fan-Out, Wafer-Level Packaging Using Polydimethylsiloxane and Printed Redistribution Layers. Proceedings, 97(1), 153. https://doi.org/10.3390/proceedings2024097153