An FPGA Platform Proposal for Real-Time Acoustic Event Detection: Optimum Platform Implementation for Audio Recognition with Time Restrictions †

Abstract

:1. Introduction

2. Hardware Platforms Comparison

3. Hardware Proposal and Basic Algorithm Implementation

3.1. Platform Description

- Memory Control Blocks (MCB) to manage auxiliary DDR memories.

- Digital Clock Managers (DCMs) able to modify some aspects of the clock signals such as multiply or divide the input frequency; (ii) condition a clock; (iii) phase shift; (iv) eliminate clock skew and (v) mirror, forward, or rebuffer a clock Signal.

- Block RAMs to implement two independent 18 kbits RAM or one 36 kbits in Xilinx series 7 FPGA.

- A DSP block which include a pre-adder, multiplication and accumulator able to implement different functions of digital signal processing.

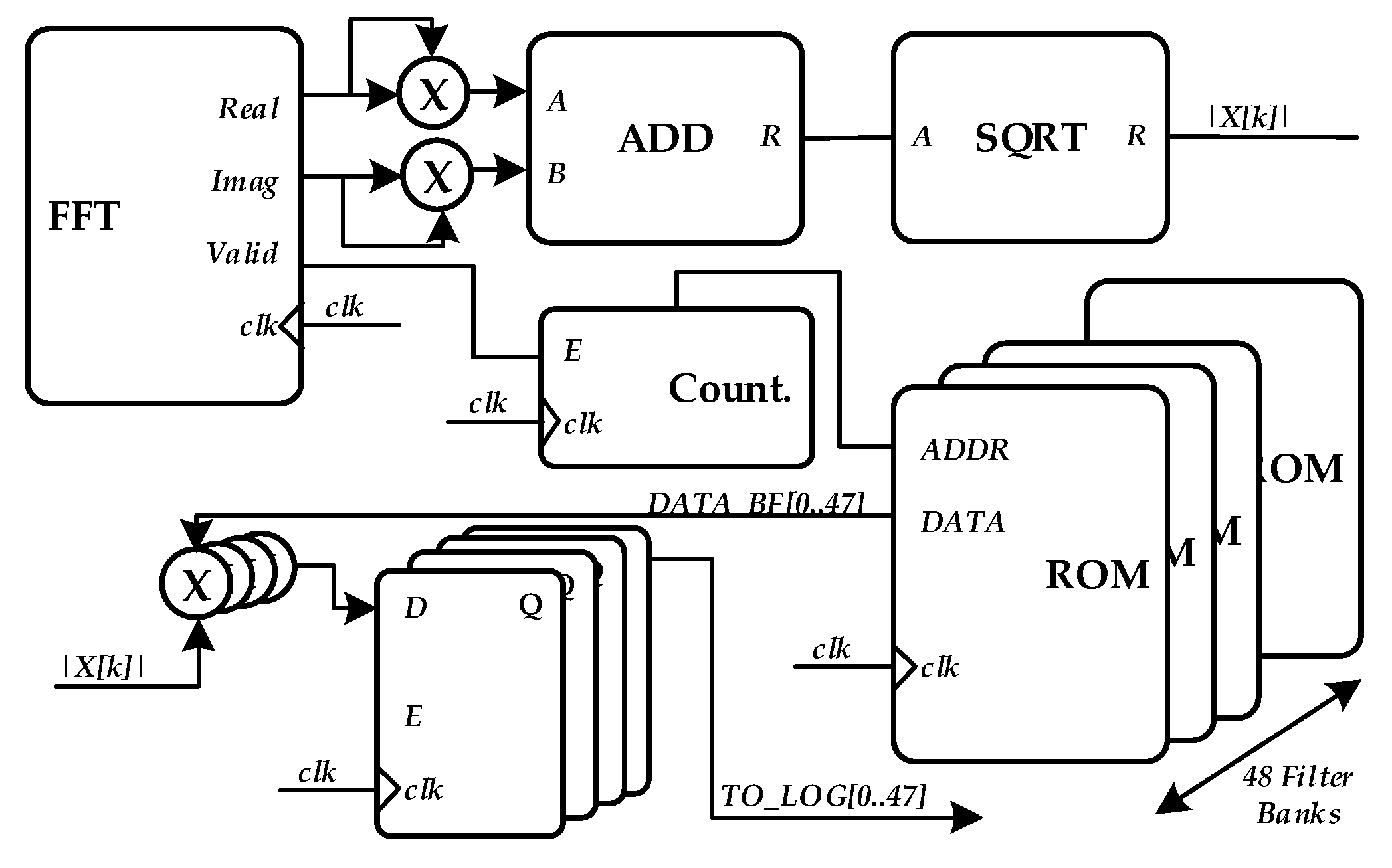

3.2. Algorithm Description

4. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

Abbreviations

| FPGA | Field Programmable Gate Array |

| VHDL | VHSIC Hardware Description Language |

| GTM | Grup de Recerca en Tecnologies Mèdia |

| ARM | Advanced RISC Machines |

| MCU | Microcontrollers |

| DSP | Digital Signal Processor |

| CLB | Configurable Logic Blocks |

| MCB | Memory Control Blocks |

| DCM | Digital Clock Managers |

| GTCC | Gammatones Coefficients |

| FFT | Fast Fourier Transform |

| ROM | Read Only Memory |

| RAM | Random Access Memory |

References

- Crocco, M.; Cristiani, M.; Trucco, A.; Murino, V. Audio Surveillance: A Systematic Review. J. ACM Comput. Surveys 2016, 48, 52. [Google Scholar] [CrossRef]

- Guyot, P.; Valero, X.; Pinquier, J.; Alías, F. Two-step detection of water sound events for the diagnostic and monitoring of dementia. In Proceedings of the 2013 IEEE International Conference on Multimedia and Expo (ICME), San Jose, CA, USA, 15–19 July 2013. [Google Scholar]

- Valero, X.; Alías, F. Hierarchical Classification of Environmental Noise Sources by Considering the Acoustic Signature of Vehicle Pass-bys. Arch. Acoust. 2012, 37, 423–434. [Google Scholar] [CrossRef]

- Valero, X.; Oldoni, D.; Alías, F.; Botteldooren, D. Support Vector Machines and Self-Organizing Maps for the recognition of sound events in urban soundscapes. In Proceedings of the Inter-Noise 2012, New York, NY, USA, 19–22 August 2012. [Google Scholar]

- Valero, X.; Alías, F. Gammatone Wavelet Features for Sound Classification in Surveillance Applications. In Proceedings of the 20th European Signal Processing Conference (EUSIPCO 2012), Bucharest, Romania, 27–31 August 2012. [Google Scholar]

- Sevillano, X.; Socoró, J.C.; Alías, F.; Belucci, P.; Peruzzi, L.; Radaelli, S.; Coppi, P.; Nencini, L.; Cerniglia, A.; Bisceglie, A.; et al. DYNAMAP—Development of low cost sensors networks for real time noise mapping. Noise Mapp. 2016, 3, 172–189. [Google Scholar] [CrossRef]

- Socoró, J.C.; Ribera, G.; Sevillano, X.; Alías, F. Development of an Anomalous Noise Event Detection Algorithm for dynamic road traffic noise mapping. In Proceedings of the 22nd International Congress on Sound and Vibration (ICSV22), Florence, Italy, 12–16 July 2015. [Google Scholar]

- JETSON TK1. NVIDIA. Available online: http://www.nvidia.com/object/jetson-tk1-embedded-dev-kit. html (accessed on 15 May 2016).

- Teng, A.; Blanco, A.; Van, G.; Reilly, N. Market Share Analysis: Microcontrollers, Worldwide, 2014. Gartner Inc. Available online: https://www.gartner.com/doc/3048717/ market-share-analysis-microcontrollers-worldwide (accessed on 26 May 2015).

- Smallest and Lowest Power Cortex Processors—Optimized for Discrete Processing and Microcontrollers. ARM Ltd. Available online: http://www.arm.com/products/processors/cortex-m/index.php (accessed on 15 May 2016).

- Maksimovic´, M.; Vujovic´, V.; Davidovic´, N.; Miloševic´, V.; Perišic´, B. Raspberry Pi as Internet of Things Hardware: Performances and Constraints. In Proceedings of the 1st International Conference on Electrical, Electronic and Computing Engineering (IcETRAN 2014), Vrnjačka Banja, Serbia, 2–5 June 2014. [Google Scholar]

- UM0585. STMicroelectronics. Available online: http://users.ece.utexas.edu/~valvano/EE345M/UM0585. pdf#page6 (accessed on 12 June 2010).

- Fergenson, D. Basys 3 Artix-7 FPGA Trainer Board: Recommended for Introductory Users. Digilent Inc. Available online: http://store.digilentinc.com/basys-3-artix-7-fpga-trainer-board-recommended-for-introductory-users/ (accessed on 6 January 2016).

| FFT (ASM) | 24 MHz Cycle Count | 24 MHz Time (µs) | 48 MHz Cycle Count | 48 MHz Time (µs) | 72 MHz Cycle Count | 72 MHz Time (µs) |

|---|---|---|---|---|---|---|

| FFT-64 | 3847 | 160 | 4025 | 84 | 4764 | 66 |

| FFT-256 | 21,039 | 876 | 22,176 | 462 | 26,065 | 362 |

| FFT-1024 | 100,180 | 4174 | 102,057 | 2126 | 127,318 | 1768 |

| FIR-32 | 3516 | 146.5 | 3525 | 73.4 | 3727 | 5176 |

| Basys-3 | Slices | Logic Cells | Bloc RAM | DSPs | Price |

|---|---|---|---|---|---|

| XC7A35T-1CPG236C | 33,280 | 33,280 | 1800 kbit | 90 | 150 $ |

| Basys-3 | LUT | FF | BRAM | DSP |

|---|---|---|---|---|

| FFT | 709 | 1385 | 4 | 4 |

| 48 Filter Banks | 0 | 0 | 48 | 0 |

| Square Root | 783 | 0 | 0 | 0 |

| Total | 7949 | 24,800 | 11 | 25 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2016 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hervás, M.; Alsina-Pagès, R.M. An FPGA Platform Proposal for Real-Time Acoustic Event Detection: Optimum Platform Implementation for Audio Recognition with Time Restrictions. Proceedings 2017, 1, 2. https://doi.org/10.3390/ecsa-3-S2001

Hervás M, Alsina-Pagès RM. An FPGA Platform Proposal for Real-Time Acoustic Event Detection: Optimum Platform Implementation for Audio Recognition with Time Restrictions. Proceedings. 2017; 1(2):2. https://doi.org/10.3390/ecsa-3-S2001

Chicago/Turabian StyleHervás, Marcos, and Rosa Ma Alsina-Pagès. 2017. "An FPGA Platform Proposal for Real-Time Acoustic Event Detection: Optimum Platform Implementation for Audio Recognition with Time Restrictions" Proceedings 1, no. 2: 2. https://doi.org/10.3390/ecsa-3-S2001