High-Performance IGZO Nanowire-Based Field-Effect Transistors with Random-Network Channels by Electrospun PVP Nanofiber Template Transfer

Abstract

:1. Introduction

2. Experimental

2.1. Preparation of the IGZO Precursor Solution and Electrospinning of IGZO Nanofibers (NFs)

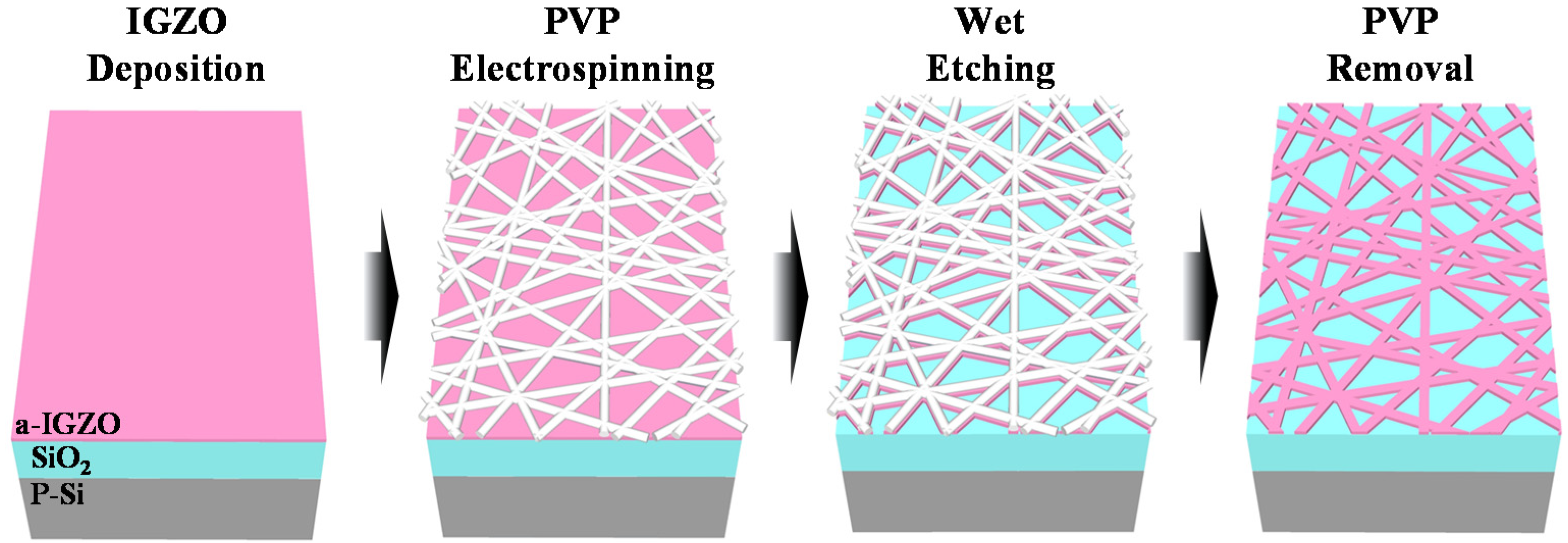

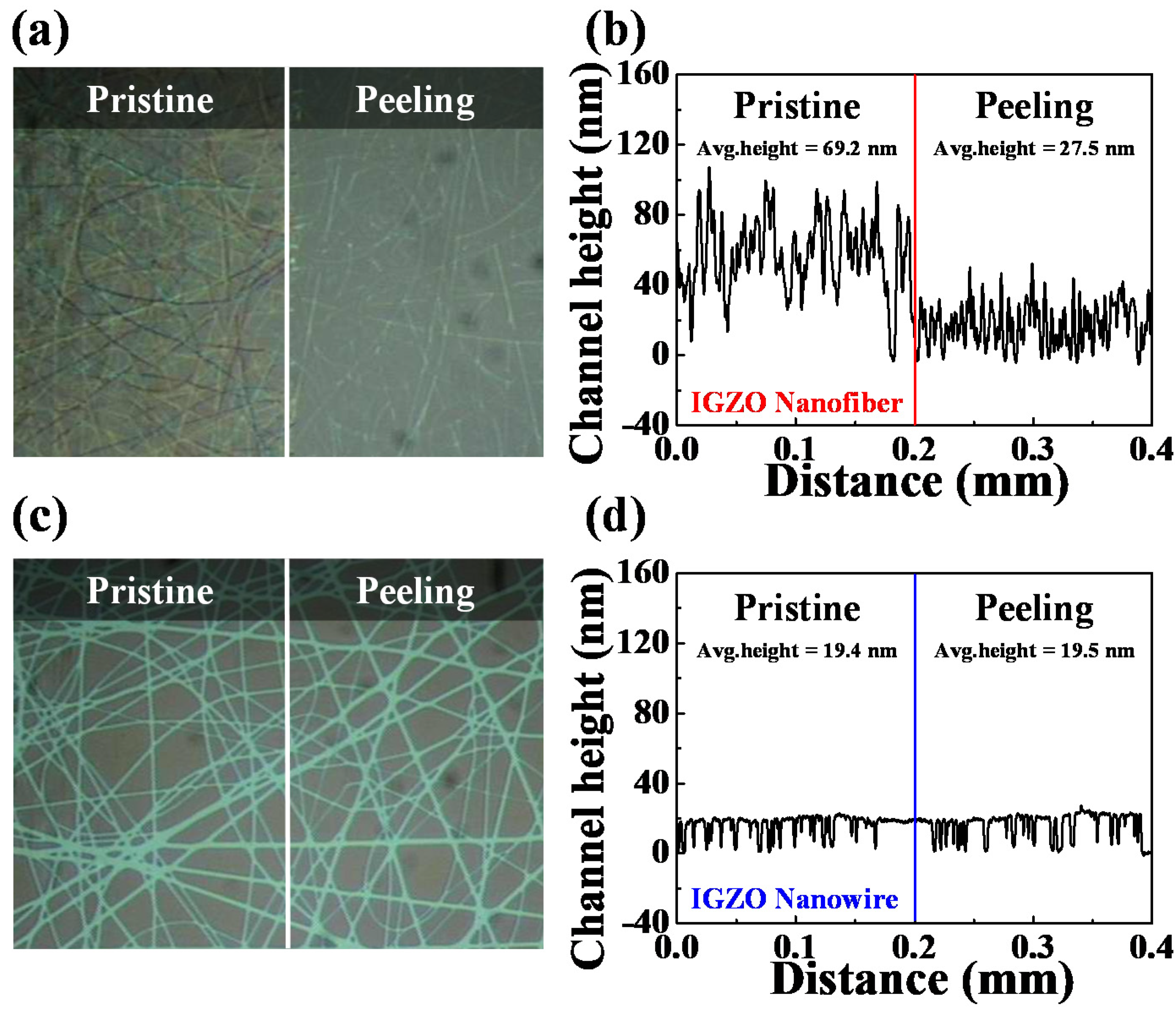

2.2. Formation of IGZO Nanowires (NWs)

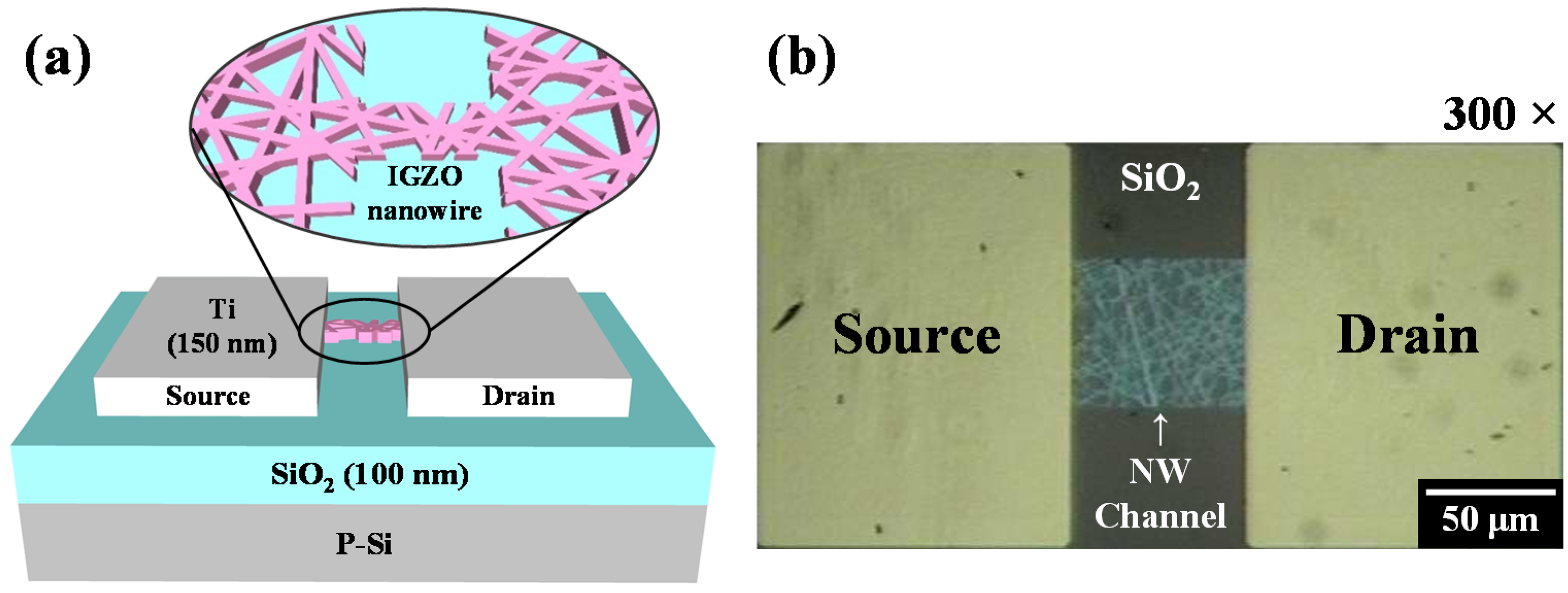

2.3. Fabrication of IGZO NF- and IGZO NW-Based FETs

2.4. Characterization

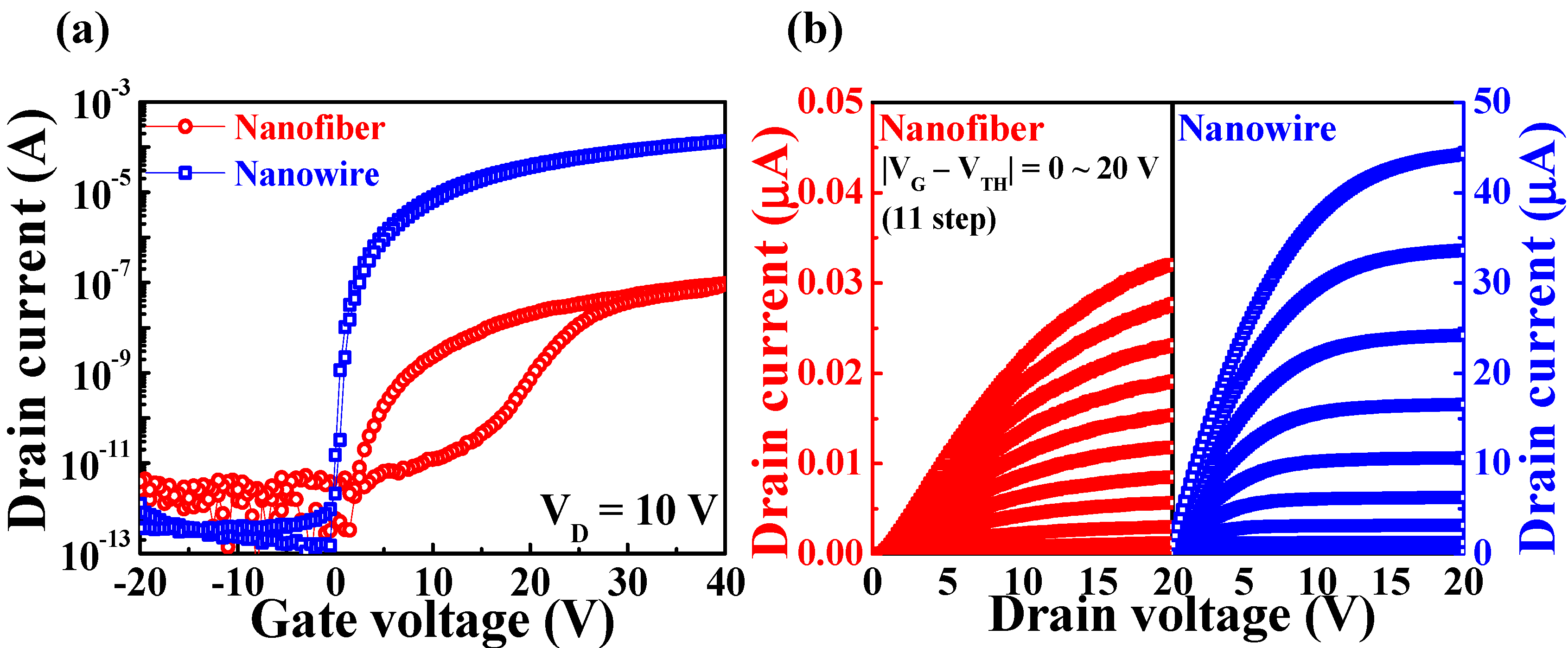

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Zhu, H. Semiconductor nanowire MOSFETs and applications. In Nanowires New Insights; Khan, M., Ed.; IntechOpen: London, UK, 2017; p. 101. [Google Scholar]

- Zhang, C.; Yan, Y.; Zhao, Y.S.; Yao, J. Synthesis and applications of organic nanorods, nanowires and nanotubes. Annu. Rep. Prog. Chem. Sect. C Phys. Chem. 2013, 109, 211–239. [Google Scholar] [CrossRef]

- Hayden, O.; Agarwal, R.; Lu, W. Semiconductor nanowire devices. Nano Today 2008, 3, 12–22. [Google Scholar] [CrossRef]

- Hobbs, R.G.; Petkov, N.; Holmes, J.D. Semiconductor nanowire fabrication by bottom-up and top-down paradigms. Chem. Mater. 2012, 24, 1975–1991. [Google Scholar] [CrossRef] [Green Version]

- Lin, J.C.; Huang, B.R.; Yang, Y.K. IGZO nanoparticle-modified silicon nanowires as extended-gate field-effect transistor pH sensors. Sens. Actuators B 2013, 184, 27–32. [Google Scholar] [CrossRef]

- Larrieu, G.; Han, X.L. Vertical nanowire array-based field effect transistors for ultimate scaling. Nanoscale 2013, 5, 2437–2441. [Google Scholar] [CrossRef]

- Kim, Y.G.; Tak, Y.J.; Kim, H.J.; Kim, W.G.; Yoo, H.; Kim, H.J. Facile fabrication of wire-type indium gallium zinc oxide thin-film transistors applicable to ultrasensitive flexible sensors. Sci. Rep. 2018, 8, 5546. [Google Scholar] [CrossRef]

- Lee, S.; Jeong, D.; Mativenga, M.; Jang, J. Highly robust bendable oxide thin-film transistors on polyimide substrates via mesh and strip patterning of device layers. Adv. Funct. Mater. 2018, 27, 1700437. [Google Scholar] [CrossRef]

- Bourdillon, A.J.; Boothroyd, C.B.; Williams, G.P.; Vladimirsky, Y. Near field X-ray lithography simulations for printing fine bridges. J. Phys. D Appl. Phys. 2003, 36, 2471. [Google Scholar] [CrossRef]

- Lin, H.C.; Stehlin, F.; Soppera, O.; Zan, H.W.; Li, C.H.; Wieder, F.; Ponche, A.; Berling, D.; Yeh, B.H.; Wang, K.H. Deep ultraviolet laser direct write for patterning sol-gel InGaZnO semiconducting micro/nanowires and improving field-effect mobility. Sci. Rep. 2015, 5, 10490. [Google Scholar] [CrossRef] [Green Version]

- Misra, S.; Yu, L.; Foldyna, M.; i Cabarrocas, P.R. High efficiency and stable hydrogenated amorphous silicon radial junction solar cells built on VLS-grown silicon nanowires. Sol. Energy Mater. Sol. Cells 2013, 118, 90–95. [Google Scholar] [CrossRef]

- Zhang, B.; Cui, T. An ultrasensitive and low-cost graphene sensor based on layer-by-layer nano self-assembly. Appl. Phys. Lett. 2011, 98, 073116. [Google Scholar] [CrossRef]

- Scappucci, G.; Capellini, G.; Johnston, B.; Klesse, W.M.; Miwa, J.A.; Simmons, M.Y. A complete fabrication route for atomic-scale, donor-based devices in single-crystal germanium. Nano Lett. 2011, 11, 2272–2279. [Google Scholar] [CrossRef] [PubMed]

- Yuan, J.J.; Zhu, P.X.; Fukazawa, N.; Jin, R.H. Synthesis of nanofiber-based silica networks mediated by organized poly(ethylene imine): Structure, properties, and mechanism. Adv. Funct. Mater. 2006, 16, 2205–2212. [Google Scholar] [CrossRef]

- Wang, B.; Thukral, A.; Xie, Z.; Liu, L.; Zhang, X.; Huang, W.; Yu, X.; Yu, C.; Marks, T.J.; Facchetti, A. Flexible and stretchable metal oxide nanofiber networks for multimodal and monolithically integrated wearable electronics. Nat. Commun. 2020, 11, 2405. [Google Scholar] [CrossRef]

- Cho, S.K.; Cho, W.J. Performance enhancement of electrospun IGZO-nanofiber-based field-effect transistors with high-k gate dielectrics through microwave annealing and postcalcination oxygen plasma treatment. Nanomaterials 2020, 10, 1804. [Google Scholar] [CrossRef]

- Vander Wal, R.L.; Ticich, T.M.; Curtis, V.E. Substrate–support interactions in metal-catalyzed carbon nanofiber growth. Carbon 2001, 39, 2277–2289. [Google Scholar] [CrossRef]

- An, G.H.; Lee, E.H.; Ahn, H.J. Ruthenium and ruthenium oxide nanofiber supports for enhanced activity of platinum electrocatalysts in the methanol oxidation reaction. Phys. Chem. Chem. Phys. 2016, 18, 14859–14866. [Google Scholar] [CrossRef] [PubMed]

- Kamiya, T.; Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2010, 2, 15–22. [Google Scholar] [CrossRef] [Green Version]

- Fuh, C.S.; Liu, P.T.; Teng, L.F.; Huang, S.W.; Lee, Y.J.; Shieh, H.P.D.; Sze, S.M. Effects of microwave annealing on nitrogenated amorphous In-Ga-Zn-O thin-film transistor for low thermal budget process application. IEEE Electron Device Lett. 2013, 34, 1157–1159. [Google Scholar] [CrossRef]

- Cho, S.K.; Cho, W.J. Microwave-assisted calcination of electrospun indium–gallium–zinc oxide nanofibers for high-performance field-effect transistors. RSC Adv. 2020, 10, 38351–38356. [Google Scholar] [CrossRef]

- Munir, M.M.; Widiyandari, H.; Iskandar, F.; Okuyama, K. Patterned indium tin oxide nanofiber films and their electrical and optical performance. Nanotechnology 2008, 19, 375601. [Google Scholar] [CrossRef]

- Yarin, A.L.; Koombhongse, S.; Reneker, D.H. Bending instability in electrospinning of nanofibers. J. Appl. Phys. 2001, 89, 3018–3026. [Google Scholar] [CrossRef] [Green Version]

- Cui, Y.; Meng, Y.; Wang, Z.; Wang, C.; Liu, G.; Martins, R.; Fortunato, E.; Shan, F. High performance electronic devices based on nanofibers via a crosslinking welding process. Nanoscale 2018, 10, 19427–19434. [Google Scholar] [CrossRef] [PubMed]

- Meng, Y.; Lou, K.; Qi, R.; Guo, Z.; Shin, B.; Liu, G.; Shan, F. Nature-inspired capillary-driven welding process for boosting metal-oxide nanofiber electronics. ACS Appl. Mater. Interfaces 2018, 10, 20703–20711. [Google Scholar] [CrossRef] [PubMed]

- Li, J.; Liang, J.; Jian, X.; Hu, W.; Li, J.; Pei, Q. A flexible and transparent thin film heater based on a silver nanowire/heat-resistant polymer composite. Macromol. Mater. Eng. 2014, 299, 1403–1409. [Google Scholar] [CrossRef]

- Yin, S.; Zhu, W.; Deng, Y.; Peng, Y.; Shen, S.; Tu, Y. Enhanced electrical conductivity and reliability for flexible copper thin-film electrode by introducing aluminum buffer layer. Mater. Des. 2017, 116, 524–530. [Google Scholar] [CrossRef]

- Han, Y.H.; Won, J.Y.; Yoo, H.S.; Kim, J.H.; Choi, R.; Jeong, J.K. High performance metal oxide field-effect transistors with a reverse offset printed Cu source/drain electrode. ACS Appl. Mater. Interfaces 2016, 8, 1156–1163. [Google Scholar] [CrossRef]

- Hong, E.K.; Cho, W.J. Effect of microwave annealing on SOI MOSFETs: Post-metal annealing with low thermal budget. Microelectron. Reliab. 2018, 80, 306–311. [Google Scholar] [CrossRef]

- Liao, W.; Wei, W.; Tong, Y.; Chim, W.K.; Zhu, C. Low-frequency noise in layered ReS2 field effect transistors on HfO2 and its application for pH sensing. ACS Appl. Mater. Interfaces 2018, 10, 7248–7255. [Google Scholar] [CrossRef]

- Wu, Q.; Wang, J.; Cao, J.; Lu, C.; Yang, G.; Shi, X.; Chuai, X.; Gong, Y.; Su, Y.; Zhao, Y.; et al. Photoelectric plasticity in oxide thin film transistors with tunable synaptic functions. Adv. Electron. Mater. 2018, 4, 1800556. [Google Scholar] [CrossRef]

- Hoshino, K.; Hong, D.; Chiang, H.Q.; Wager, J.F. Constant-voltage-bias stress testing of a-IGZO thin-film transistors. IEEE Trans. Electron Devices 2009, 56, 1365–1370. [Google Scholar] [CrossRef]

- Chen, M.; Nam, H.; Rokni, H.; Wi, S.; Yoon, J.S.; Chen, P.; Kurabayashi, K.; Lu, W.; Liang, X. Nanoimprint-assisted shear exfoliation (NASE) for producing multilayer MoS2 structures as field-effect transistor channel arrays. ACS Nano 2015, 9, 8773–8785. [Google Scholar] [CrossRef] [PubMed]

- Jun, L.; Chen, Q.; Fu, W.; Yang, Y.; Zhu, W.; Zhang, J. Electrospun Yb-doped In2O3 nanofiber field-effect transistors for highly sensitive ethanol sensors. ACS Appl. Mater. Interfaces 2020, 12, 38425–38434. [Google Scholar] [CrossRef] [PubMed]

- Janotti, A.; Van de Walle, C.G. Native point defects in ZnO. Phys. Rev. B 2007, 76, 165202. [Google Scholar] [CrossRef]

- Kang, M.S.; Cho, W.J. Improvement of on/off current ratio of amorphous In–Ga–Zn–O thin-film transistor with off-planed source/drain electrodes. J. Nanosci. Nanotechnol. 2019, 19, 1345–1349. [Google Scholar] [CrossRef]

- Billah, M.M.; Chowdhury, M.D.H.; Mativenga, M.; Um, J.G.; Mruthyunjaya, R.K.; Heiler, G.N.; Tredwell, T.J.; Jang, J. Analysis of improved performance under negative bias illumination stress of dual gate driving a-IGZO TFT by TCAD simulation. IEEE Electron Device Lett. 2016, 37, 735–738. [Google Scholar] [CrossRef]

- Baek, G.; Abe, K.; Kuo, A.; Kumomi, H.; Kanicki, J. Electrical properties and stability of dual-gate coplanar homojunction DC sputtered amorphous indium–gallium–zinc–oxide thin-film transistors and its application to AM-OLEDs. IEEE Trans. Electron Devices 2011, 58, 4344–4353. [Google Scholar] [CrossRef]

- Yoon, S.J.; Seong, N.J.; Choi, K.; Shin, W.C.; Yoon, S.M. Investigations on the bias temperature stabilities of oxide thin film transistors using In–Ga–Zn–O channels prepared by atomic layer deposition. RSC Adv. 2018, 8, 25014–25020. [Google Scholar] [CrossRef] [Green Version]

| Channel | μFE (cm2 V−1 s−1) | SS (V/dec) | Ion/Ioff | VTH (V) | VH (V) | |||

|---|---|---|---|---|---|---|---|---|

| Avg. | RSD | Avg. | RSD | Avg. | SD | |||

| Nanofibers | 0.16 | 0.38 | 1.62 | 0.23 | 6.28 × 104 | 9.87 | 1.31 | 7.25 |

| Nanowires | 11.81 | 0.29 | 0.32 | 0.12 | 7.39 × 108 | 0.52 | 0.13 | 0.45 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, K.-W.; Cho, W.-J. High-Performance IGZO Nanowire-Based Field-Effect Transistors with Random-Network Channels by Electrospun PVP Nanofiber Template Transfer. Polymers 2022, 14, 651. https://doi.org/10.3390/polym14030651

Park K-W, Cho W-J. High-Performance IGZO Nanowire-Based Field-Effect Transistors with Random-Network Channels by Electrospun PVP Nanofiber Template Transfer. Polymers. 2022; 14(3):651. https://doi.org/10.3390/polym14030651

Chicago/Turabian StylePark, Ki-Woong, and Won-Ju Cho. 2022. "High-Performance IGZO Nanowire-Based Field-Effect Transistors with Random-Network Channels by Electrospun PVP Nanofiber Template Transfer" Polymers 14, no. 3: 651. https://doi.org/10.3390/polym14030651

APA StylePark, K.-W., & Cho, W.-J. (2022). High-Performance IGZO Nanowire-Based Field-Effect Transistors with Random-Network Channels by Electrospun PVP Nanofiber Template Transfer. Polymers, 14(3), 651. https://doi.org/10.3390/polym14030651