Introducing Electrode Contact by Controlled Micro-Alloying in Few-Layered GaTe Field Effect Transistors

Abstract

1. Introduction

2. Materials and Methods

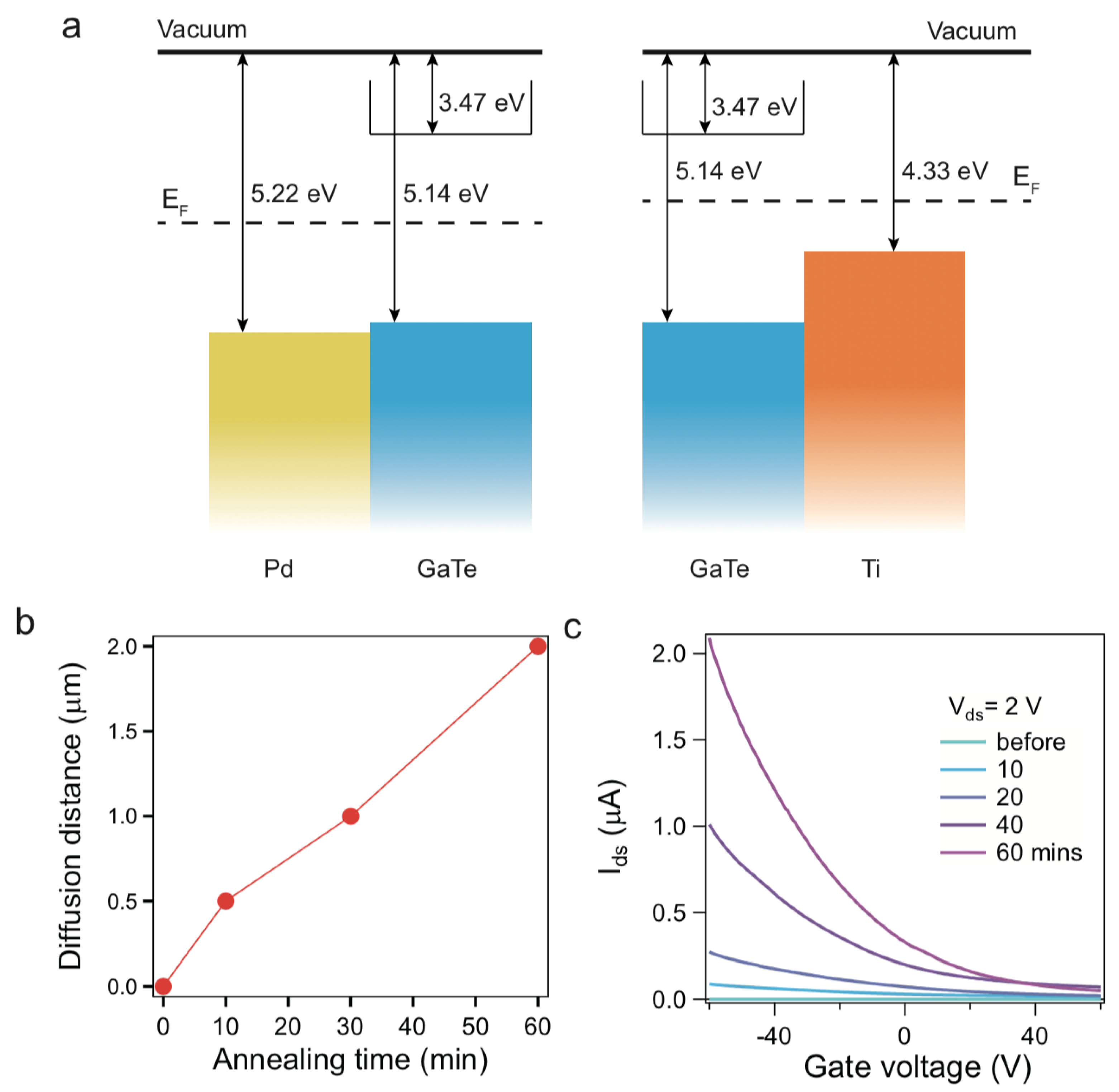

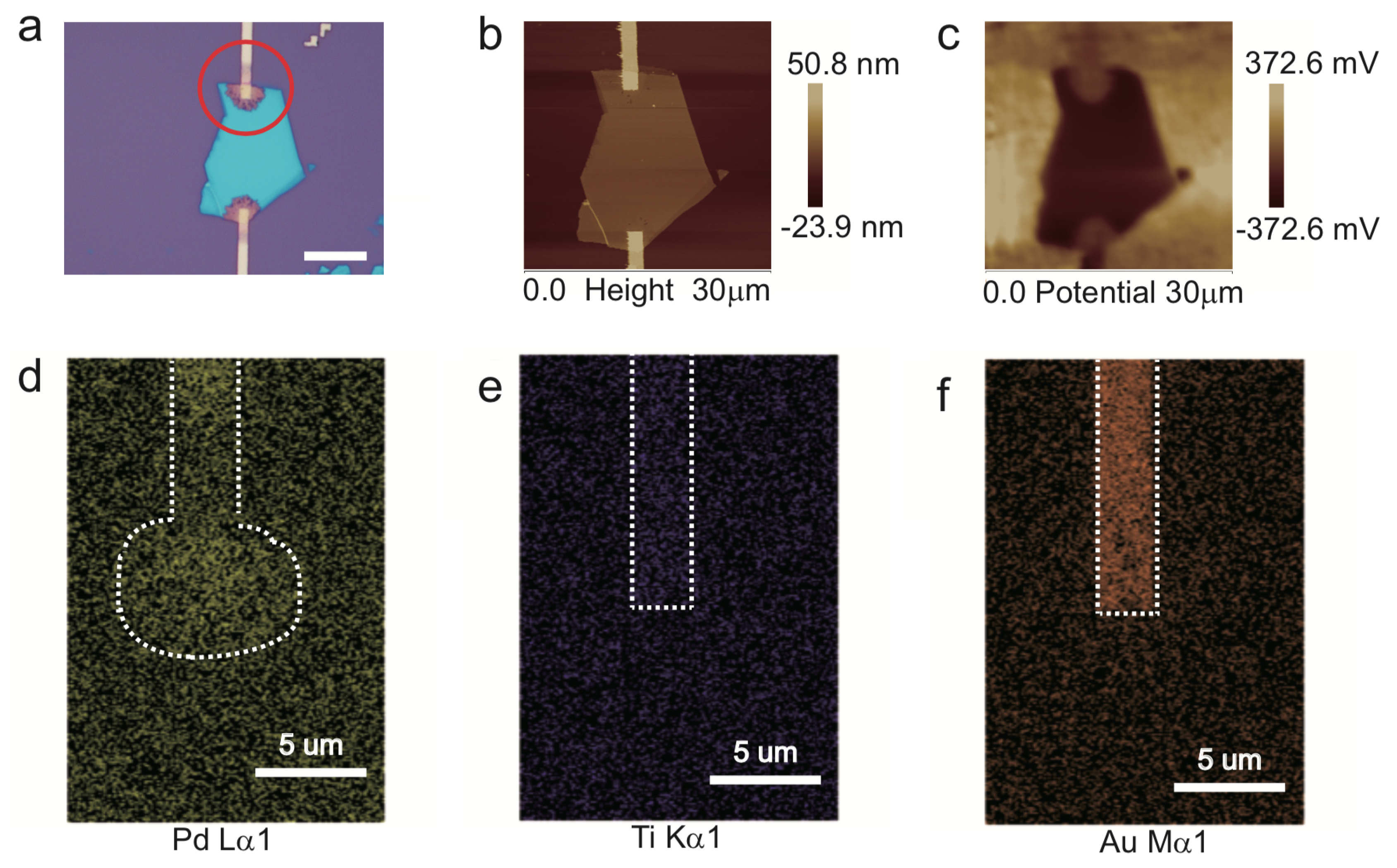

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Novoselov, K.; Mishchenko, A.; Carvalho, A.; Neto, A.C. 2D materials and van der Waals heterostructures. Science 2016, 353, aac9439. [Google Scholar] [CrossRef] [PubMed]

- Liu, Y.; Weiss, N.O.; Duan, X.; Cheng, H.C.; Huang, Y.; Duan, X. Van der Waals heterostructures and devices. Nat. Rev. Mater. 2016, 1, 1–17. [Google Scholar] [CrossRef]

- Geim, A.K.; Grigorieva, I.V. Van der Waals heterostructures. Nature 2013, 499, 419–425. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Dong, B.; Sun, X.; Wang, H.; Yang, T.; Yu, G.; Han, Z.V. Perspectives on exfoliated two-dimensional spintronics. J. Semicond. 2019, 40, 081508. [Google Scholar] [CrossRef]

- Dayen, J.F.; Ray, S.J.; Karis, O.; Vera-Marun, I.J.; Kamalakar, M.V. Two-dimensional van der Waals spinterfaces and magnetic-interfaces. Appl. Phys. Rev. 2020, 7, 011303. [Google Scholar] [CrossRef]

- Lin, X.; Yang, W.; Wang, K.L.; Zhao, W. Two-dimensional spintronics for low-power electronics. Nat. Electron. 2019, 2, 274–283. [Google Scholar] [CrossRef]

- Zhang, Z.; Lin, P.; Liao, Q.; Kang, Z.; Si, H.; Zhang, Y. Graphene-Based Mixed-Dimensional van der Waals Heterostructures for Advanced Optoelectronics. Adv. Mater. 2019, 31, 1806411. [Google Scholar] [CrossRef]

- Hantanasirisakul, K.; Gogotsi, Y. Electronic and optical properties of 2D transition metal carbides and nitrides (MXenes). Adv. Mater. 2018, 30, 1804779. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, T.; Ding, M.; Dong, B.; Li, Y.; Chen, M.; Li, X.; Huang, J.; Wang, H.; Zhao, X.; et al. Electric-field control of magnetism in a few-layered van der Waals ferromagnetic semiconductor. Nat. Nanotechnol. 2018, 13, 554–559. [Google Scholar] [CrossRef]

- Liao, M.; Zhu, Y.; Zhang, J.; Zhong, R.; Schneeloch, J.; Gu, G.; Jiang, K.; Zhang, D.; Ma, X.; Xue, Q.K. Superconductor–Insulator Transitions in Exfoliated Bi2Sr2CaCu2O8+δ Flakes. Nano Lett. 2018, 18, 5660–5665. [Google Scholar] [CrossRef]

- Liu, F.; Shimotani, H.; Shang, H.; Kanagasekaran, T.; Zolyomi, V.; Drummond, N.; Fal’ko, V.I.; Tanigaki, K. High-sensitivity photodetectors based on multilayer GaTe flakes. ACS Nano 2014, 8, 752–760. [Google Scholar] [CrossRef] [PubMed]

- Wang, H.; Chen, M.L.; Zhu, M.; Wang, Y.; Dong, B.; Sun, X.; Zhang, X.; Cao, S.; Li, X.; Huang, J.; et al. Gate tunable giant anisotropic resistance in ultra-thin GaTe. Nat. Commun. 2019, 10, 1–8. [Google Scholar] [CrossRef] [PubMed]

- Leao, C.R.; Lordi, V. Ab initio guided optimization of GaTe for radiation detection applications. Phys. Rev. B 2011, 84, 165206. [Google Scholar] [CrossRef]

- Zhao, Q.; Wang, T.; Miao, Y.; Ma, F.; Xie, Y.; Ma, X.; Gu, Y.; Li, J.; He, J.; Chen, B.; et al. Thickness-induced structural phase transformation of layered gallium telluride. Phys. Chem. Chem. Phys. 2016, 18, 18719–18726. [Google Scholar] [CrossRef]

- Kang, J.; Sangwan, V.K.; Lee, H.S.; Liu, X.; Hersam, M.C. Solution-Processed Layered Gallium Telluride Thin-Film Photodetectors. ACS Photonics 2018, 5, 3996–4002. [Google Scholar] [CrossRef]

- Fonseca, J.J.; Tongay, S.; Topsakal, M.; Chew, A.R.; Lin, A.J.; Ko, C.; Luce, A.V.; Salleo, A.; Wu, J.; Dubon, O.D. Bandgap restructuring of the layered semiconductor gallium telluride in air. Adv. Mater. 2016, 28, 6465–6470. [Google Scholar] [CrossRef]

- Tung, R.T. The physics and chemistry of the Schottky barrier height. Appl. Phys. Rev. 2014, 1, 011304. [Google Scholar]

- Hu, P.; Zhang, J.; Yoon, M.; Qiao, X.F.; Zhang, X.; Feng, W.; Tan, P.; Zheng, W.; Liu, J.; Wang, X.; et al. Highly sensitive phototransistors based on two-dimensional GaTe nanosheets with direct bandgap. Nano Res. 2014, 7, 694–703. [Google Scholar] [CrossRef]

- Wang, Z.; Safdar, M.; Mirza, M.; Xu, K.; Wang, Q.; Huang, Y.; Wang, F.; Zhan, X.; He, J. High-performance flexible photodetectors based on GaTe nanosheets. Nanoscale 2015, 7, 7252–7258. [Google Scholar] [CrossRef]

- Wang, J.; Yao, Q.; Huang, C.W.; Zou, X.; Liao, L.; Chen, S.; Fan, Z.; Zhang, K.; Wu, W.; Xiao, X.; et al. High Mobility MoS2 transistor with low Schottky barrier contact by using atomic thick h-BN as a tunneling layer. Adv. Mater. 2016, 28, 8302–8308. [Google Scholar] [CrossRef]

- Pisoni, R.; Kormányos, A.; Brooks, M.; Lei, Z.; Back, P.; Eich, M.; Overweg, H.; Lee, Y.; Rickhaus, P.; Watanabe, K.; et al. Interactions and magnetotransport through spin-valley coupled Landau levels in monolayer MoS2. Phys. Rev. Lett. 2018, 121, 247701. [Google Scholar] [CrossRef] [PubMed]

- Xu, S.; Shen, J.; Long, G.; Wu, Z.; Bao, Z.q.; Liu, C.C.; Xiao, X.; Han, T.; Lin, J.; Wu, Y.; et al. Odd-integer quantum Hall states and giant spin susceptibility in p-type few-layer WSe2. Phys. Rev. Lett. 2017, 118, 067702. [Google Scholar] [CrossRef] [PubMed]

- Xu, S.; Wu, Z.; Lu, H.; Han, Y.; Long, G.; Chen, X.; Han, T.; Ye, W.; Wu, Y.; Lin, J.; et al. Universal low-temperature Ohmic contacts for quantum transport in transition metal dichalcogenides. 2D Materials 2016, 3, 021007. [Google Scholar] [CrossRef]

- Cho, S.; Kim, S.; Kim, J.H.; Zhao, J.; Seok, J.; Keum, D.H.; Baik, J.; Choe, D.H.; Chang, K.J.; Suenaga, K.; et al. Phase patterning for ohmic homojunction contact in MoTe2. Science 2015, 349, 625–628. [Google Scholar] [CrossRef]

- Li, X.X.; Fan, Z.Q.; Liu, P.Z.; Chen, M.L.; Liu, X.; Jia, C.K.; Sun, D.M.; Jiang, X.W.; Han, Z.; Bouchiat, V.; et al. Gate-controlled reversible rectifying behaviour in tunnel contacted atomically-thin MoS2 transistor. Nat. Commun. 2017, 8, 1–7. [Google Scholar] [CrossRef]

- Das, S.; Chen, H.Y.; Penumatcha, A.V.; Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 2013, 13, 100–105. [Google Scholar] [CrossRef]

- Fallahazad, B.; Movva, H.C.; Kim, K.; Larentis, S.; Taniguchi, T.; Watanabe, K.; Banerjee, S.K.; Tutuc, E. Shubnikov–de Haas oscillations of high-mobility holes in monolayer and bilayer WSe2: Landau level degeneracy, effective mass, and negative compressibility. Phys. Rev. Lett. 2016, 116, 086601. [Google Scholar] [CrossRef]

- Cui, X.; Shih, E.M.; Jauregui, L.A.; Chae, S.H.; Kim, Y.D.; Li, B.; Seo, D.; Pistunova, K.; Yin, J.; Park, J.H.; et al. Low-temperature ohmic contact to monolayer MoS2 by van der Waals bonded Co/h-BN electrodes. Nano Lett. 2017, 17, 4781–4786. [Google Scholar] [CrossRef]

- Cui, X.; Lee, G.H.; Kim, Y.D.; Arefe, G.; Huang, P.Y.; Lee, C.H.; Chenet, D.A.; Zhang, X.; Wang, L.; Ye, F.; et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 2015, 10, 534. [Google Scholar] [CrossRef]

- Kappera, R.; Voiry, D.; Yalcin, S.E.; Branch, B.; Gupta, G.; Mohite, A.D.; Chhowalla, M. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors. Nat. Mater. 2014, 13, 1128–1134. [Google Scholar] [CrossRef]

- Chuang, H.J.; Tan, X.; Ghimire, N.J.; Perera, M.M.; Chamlagain, B.; Cheng, M.M.C.; Yan, J.; Mandrus, D.; Tomanek, D.; Zhou, Z. High mobility WSe2 p-and n-type field-effect transistors contacted by highly doped graphene for low-resistance contacts. Nano Lett. 2014, 14, 3594–3601. [Google Scholar] [CrossRef] [PubMed]

- Lin, J.; Han, T.; Piot, B.A.; Wu, Z.; Xu, S.; Long, G.; An, L.; Cheung, P.; Zheng, P.P.; Plochocka, P.; et al. Determining interaction enhanced valley susceptibility in spin-valley-locked MoS2. Nano Lett. 2019, 19, 1736–1742. [Google Scholar] [CrossRef] [PubMed]

- Braslau, N. Alloyed ohmic contacts to GaAs. J. Vac. Sci. Technol. 1981, 19, 803–807. [Google Scholar] [CrossRef]

- Bahir, G.; Merz, J.; Abelson, J.R.; Sigmon, T. Rapid thermal alloyed ohmic contact on InP. J. Electron. Mater. 1987, 16, 257–262. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xia, X.; Sun, X.; Wang, H.; Li, X. Introducing Electrode Contact by Controlled Micro-Alloying in Few-Layered GaTe Field Effect Transistors. Crystals 2020, 10, 144. https://doi.org/10.3390/cryst10030144

Xia X, Sun X, Wang H, Li X. Introducing Electrode Contact by Controlled Micro-Alloying in Few-Layered GaTe Field Effect Transistors. Crystals. 2020; 10(3):144. https://doi.org/10.3390/cryst10030144

Chicago/Turabian StyleXia, Xiuxin, Xingdan Sun, Hanwen Wang, and Xiaoxi Li. 2020. "Introducing Electrode Contact by Controlled Micro-Alloying in Few-Layered GaTe Field Effect Transistors" Crystals 10, no. 3: 144. https://doi.org/10.3390/cryst10030144

APA StyleXia, X., Sun, X., Wang, H., & Li, X. (2020). Introducing Electrode Contact by Controlled Micro-Alloying in Few-Layered GaTe Field Effect Transistors. Crystals, 10(3), 144. https://doi.org/10.3390/cryst10030144