A Compact Digital Pixel Sensor (DPS) Using 2T-DRAM

Abstract

:1. Introduction

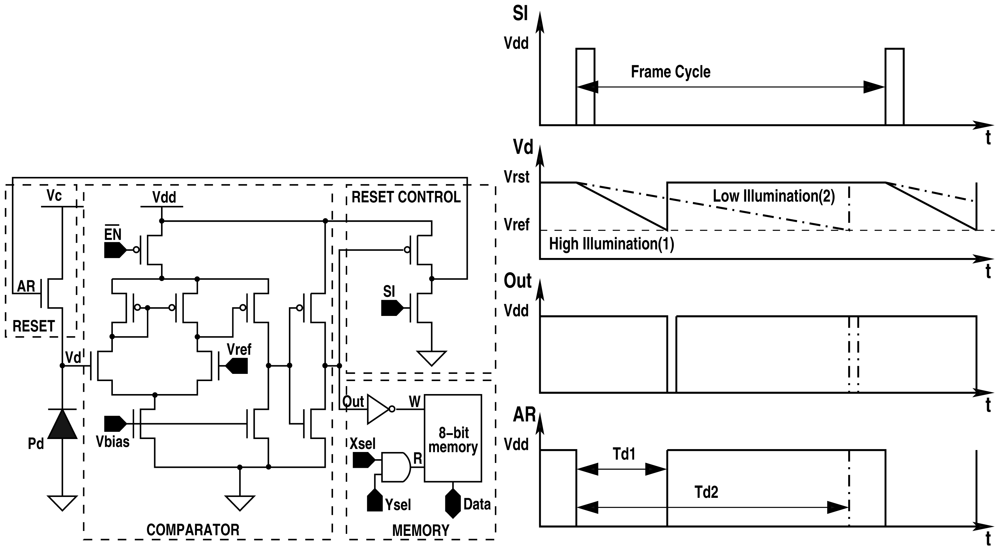

2. Time-Domain PWM DPS

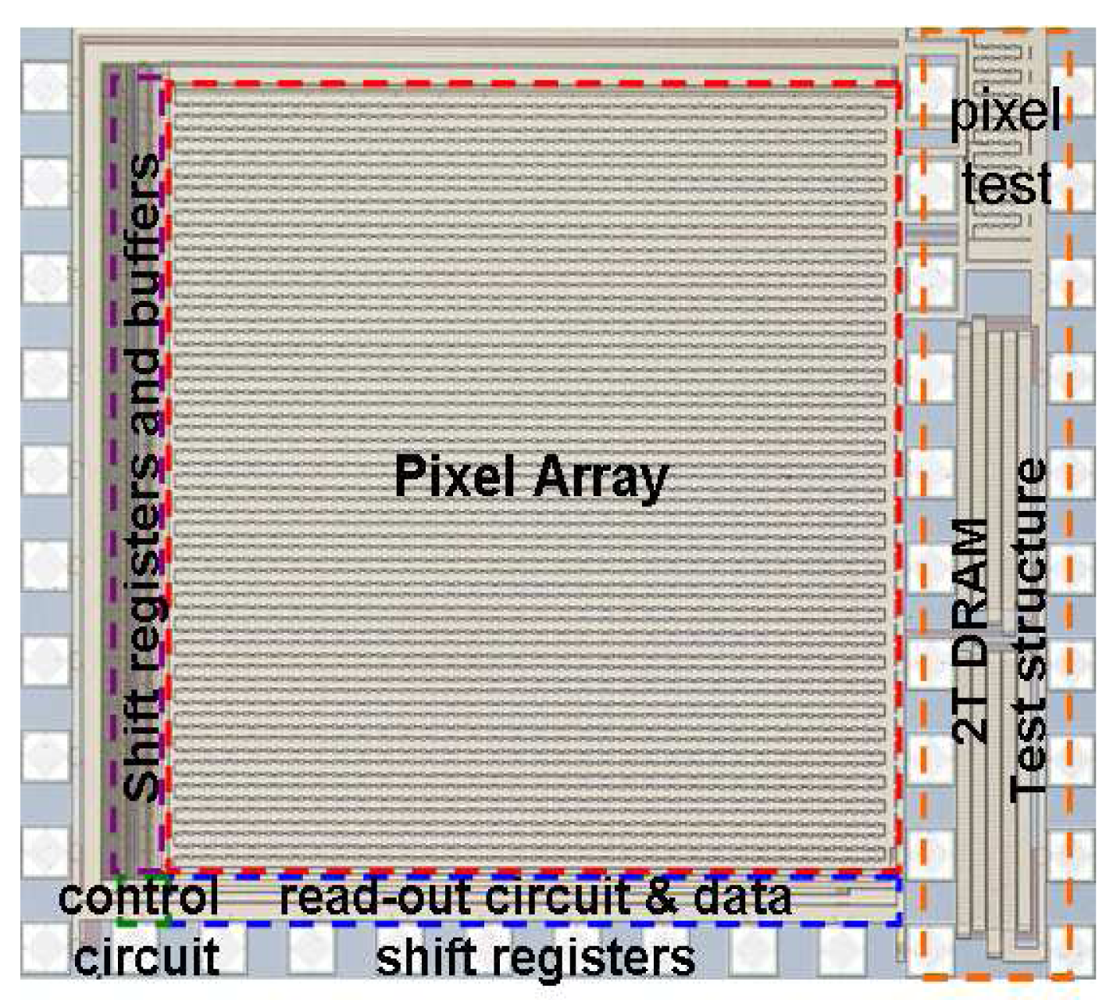

2.1. Conventional Architecture

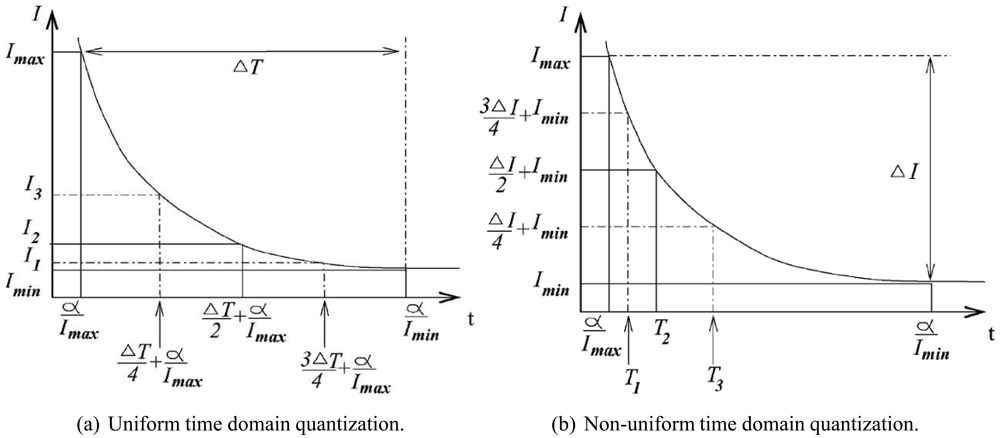

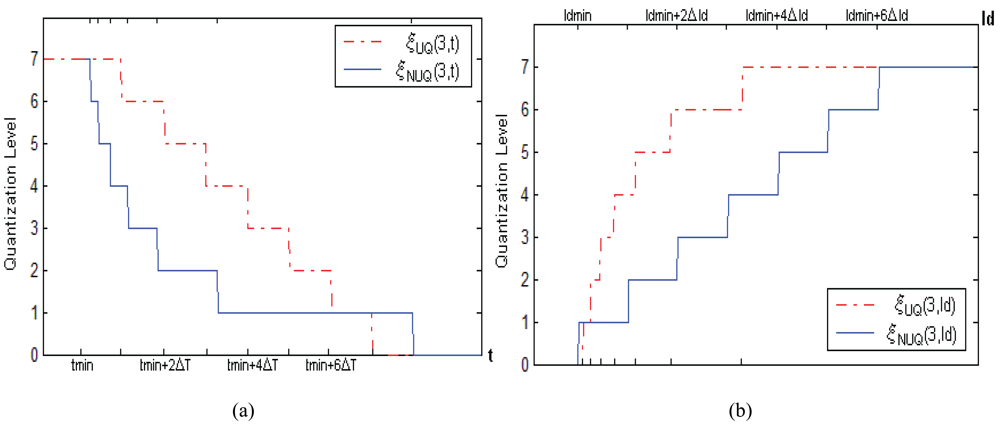

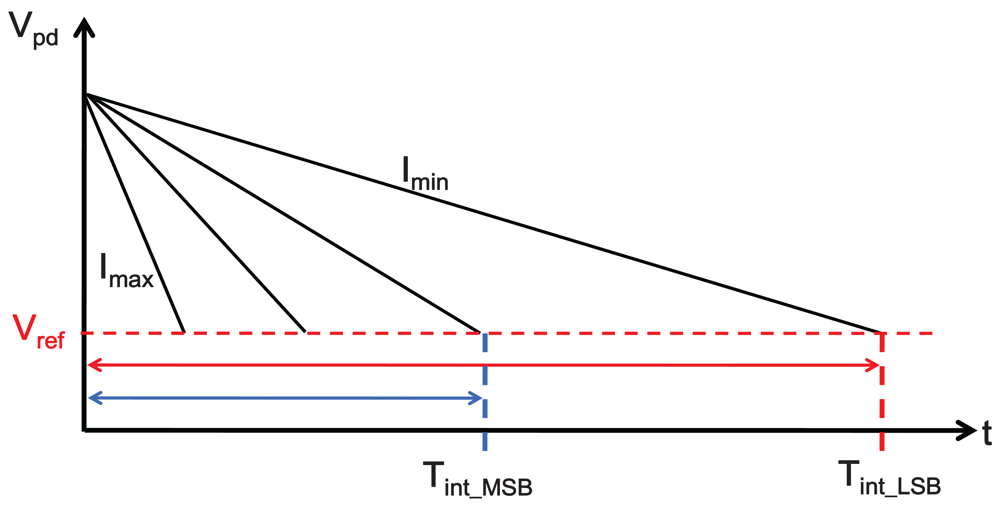

2.2. Conversion Time Analysis

2.2.1. Uniform Time-Domain Quantization

2.2.2. Non-Uniform Time-Domain Quantization

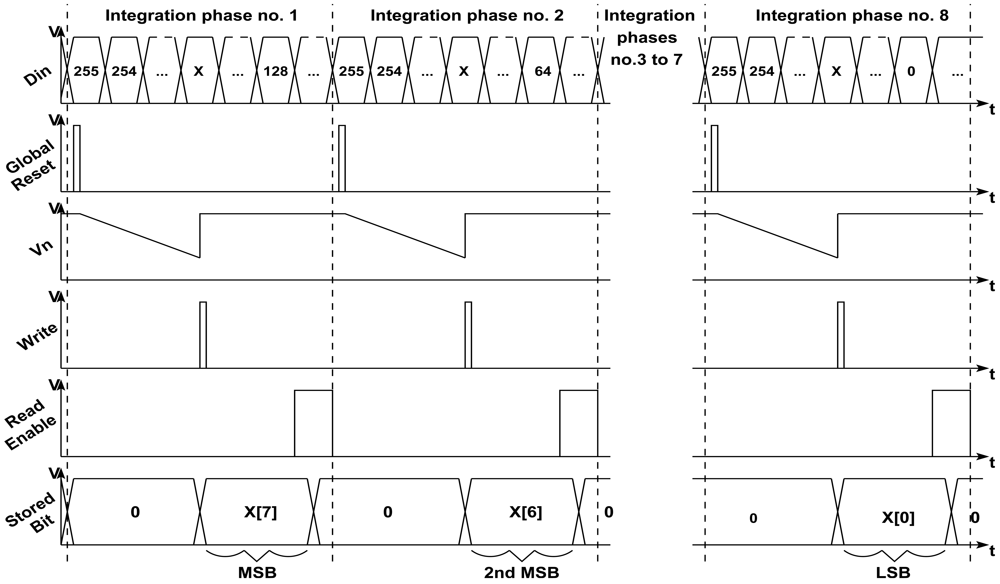

3. The Proposed Multi-Reset Integration (MRI) Scheme

3.1. MRI Concept

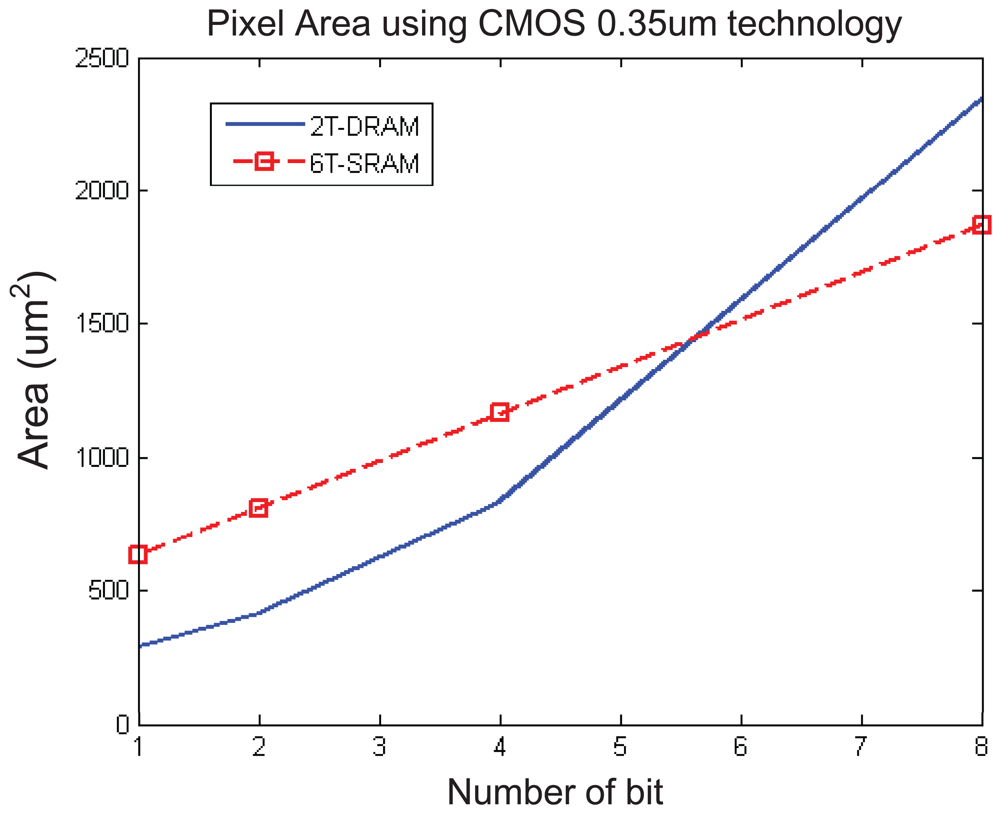

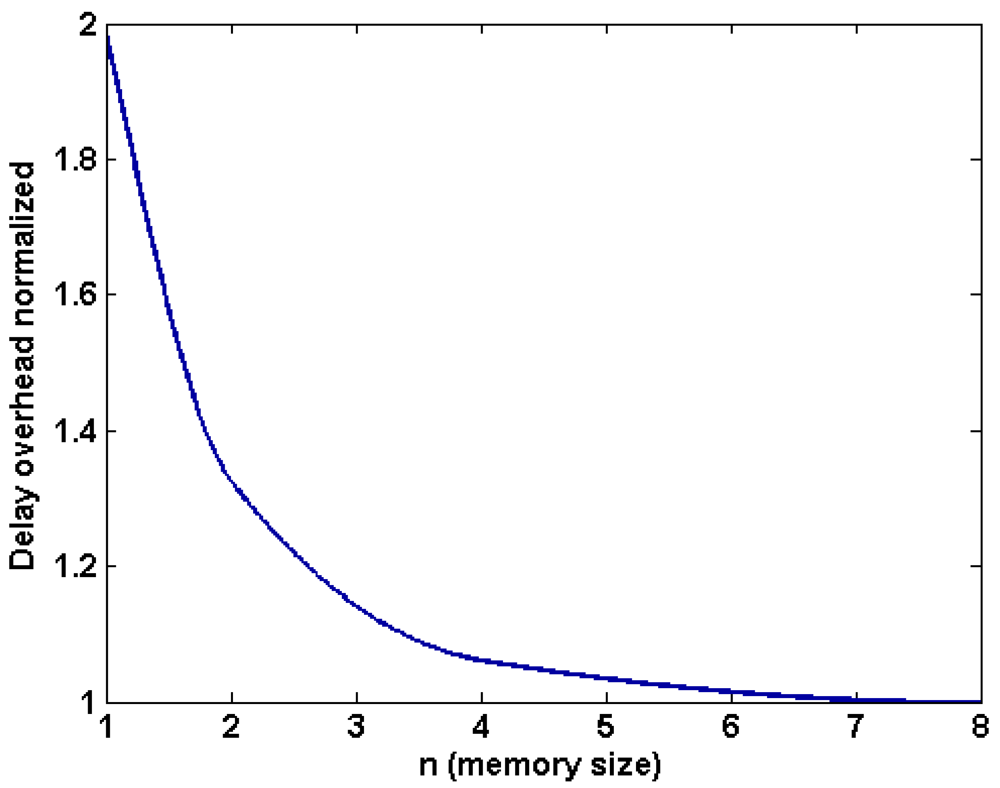

3.2. Trade-off Analysis

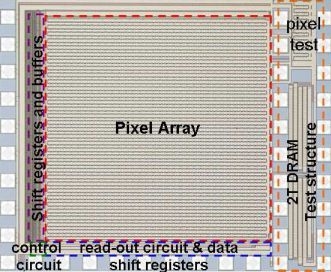

4. MRI-Based Digital Pixel Sensor

4.1. Overall Architecture

4.2. Pixel Circuit

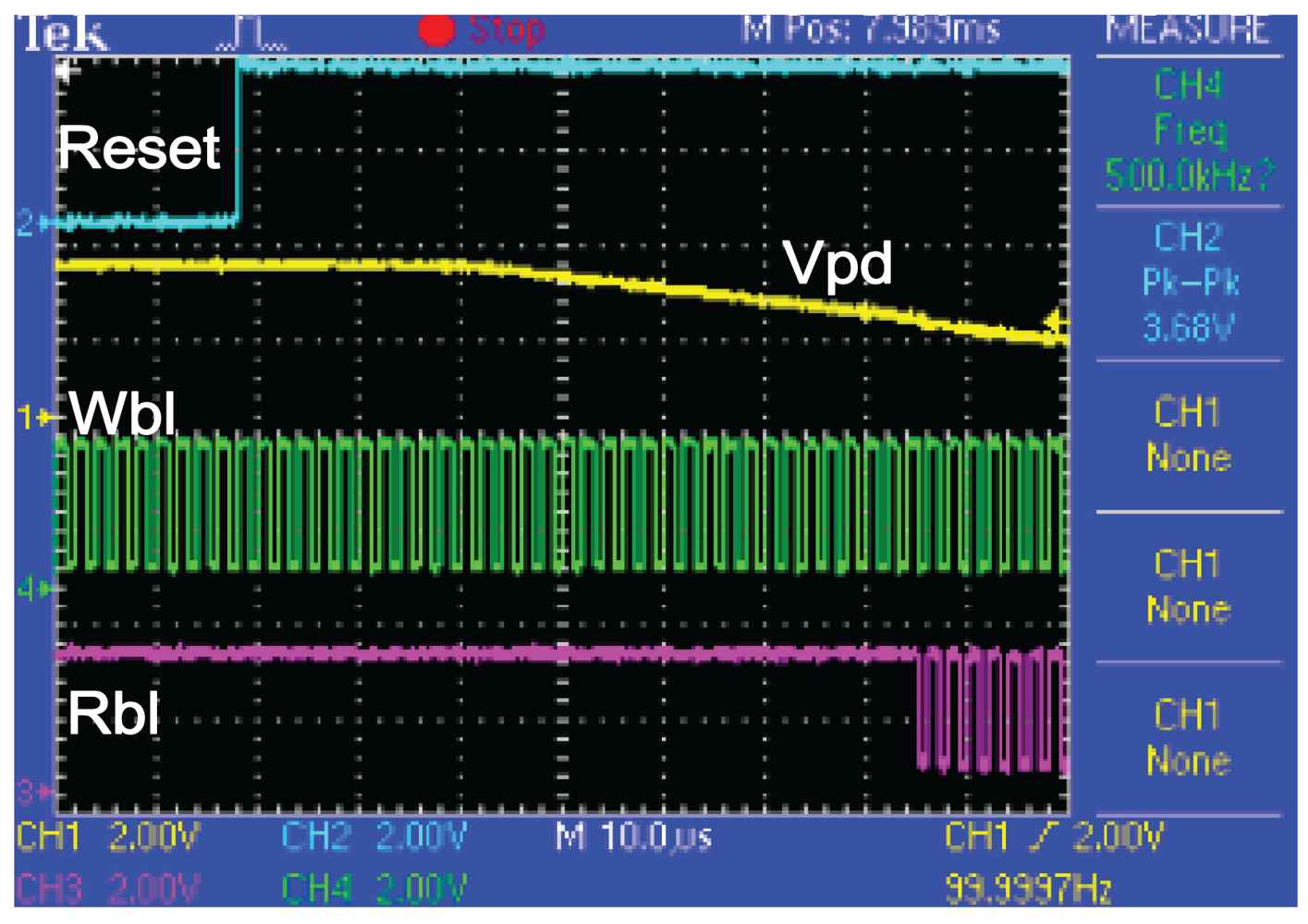

4.3. 2T DRAM Implementation

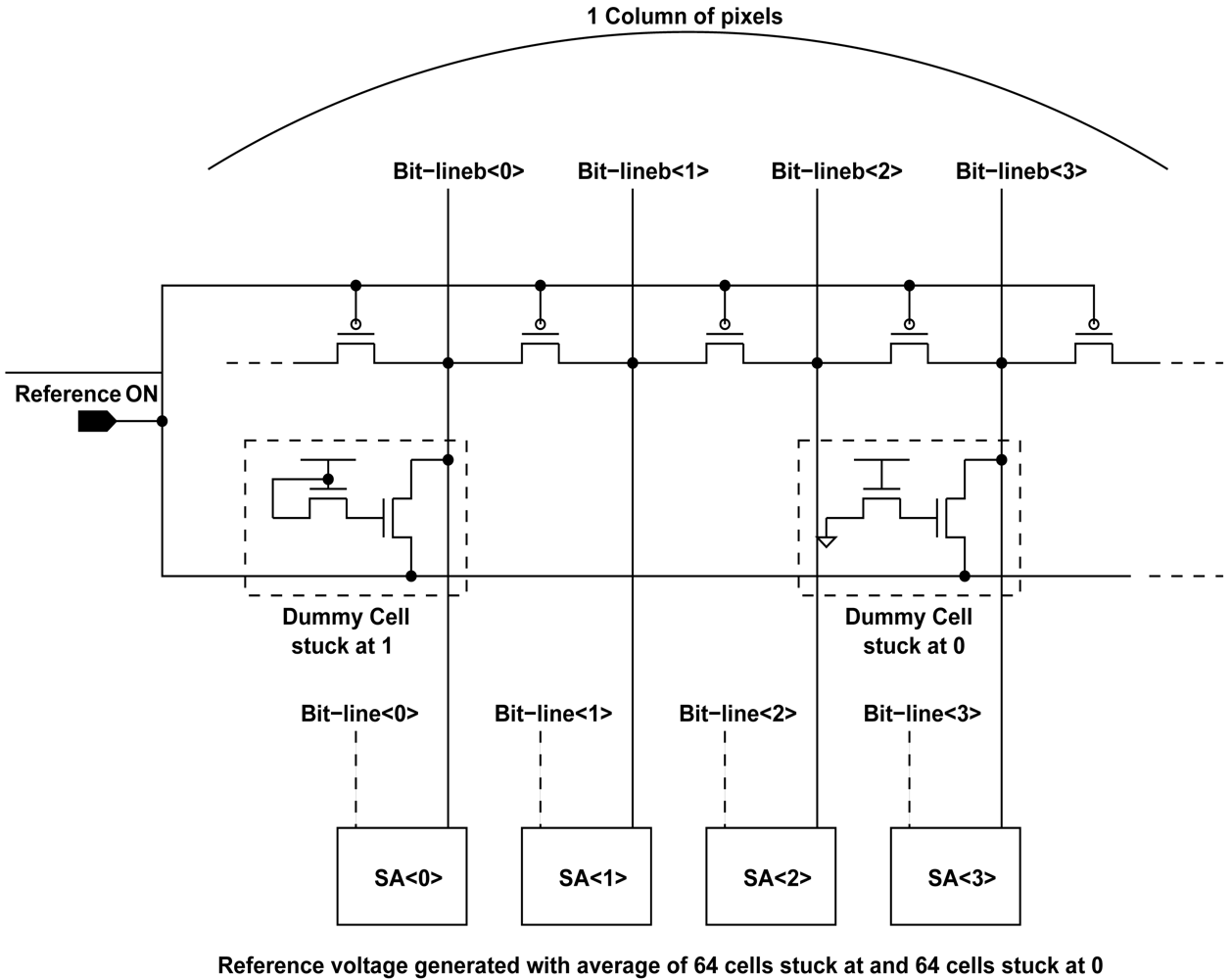

4.4. Differential Sensing Scheme and Voltage Generation

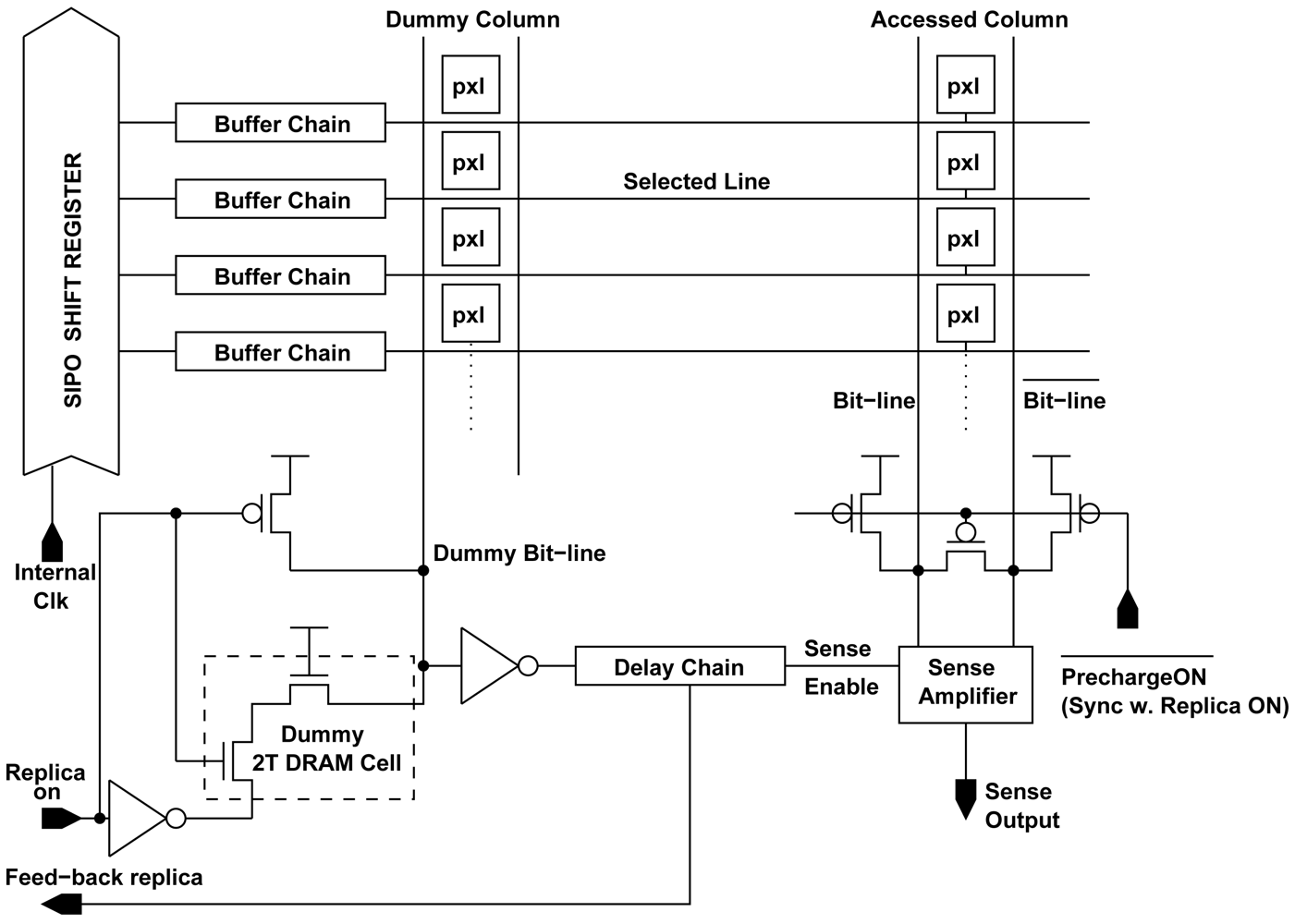

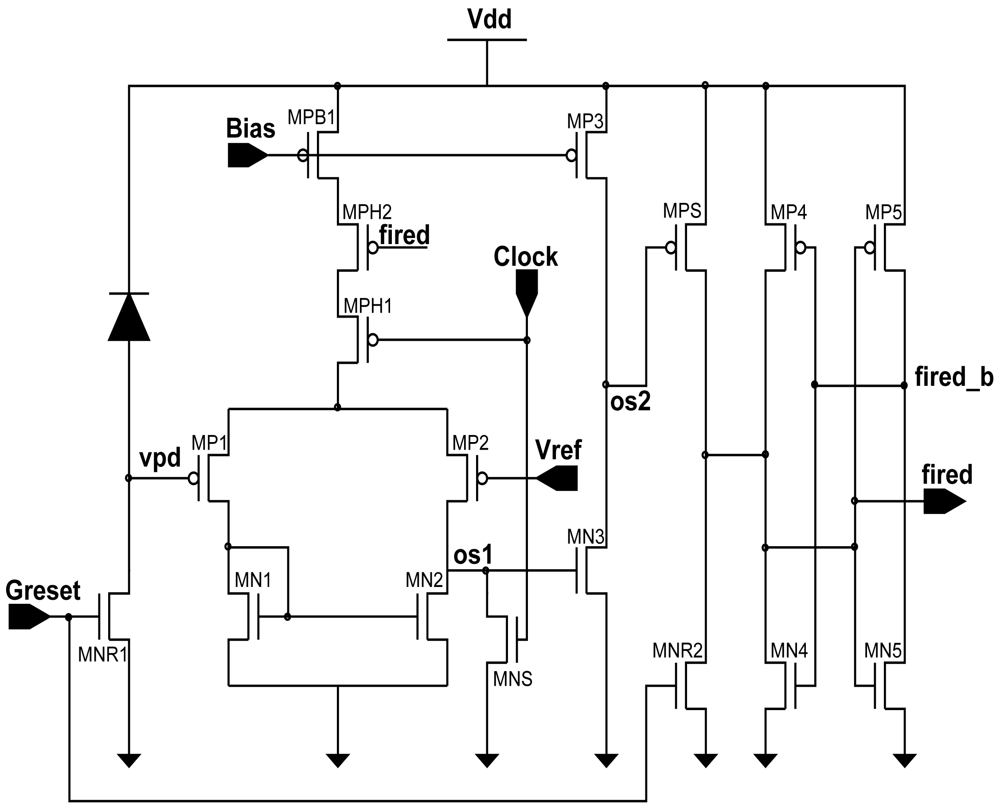

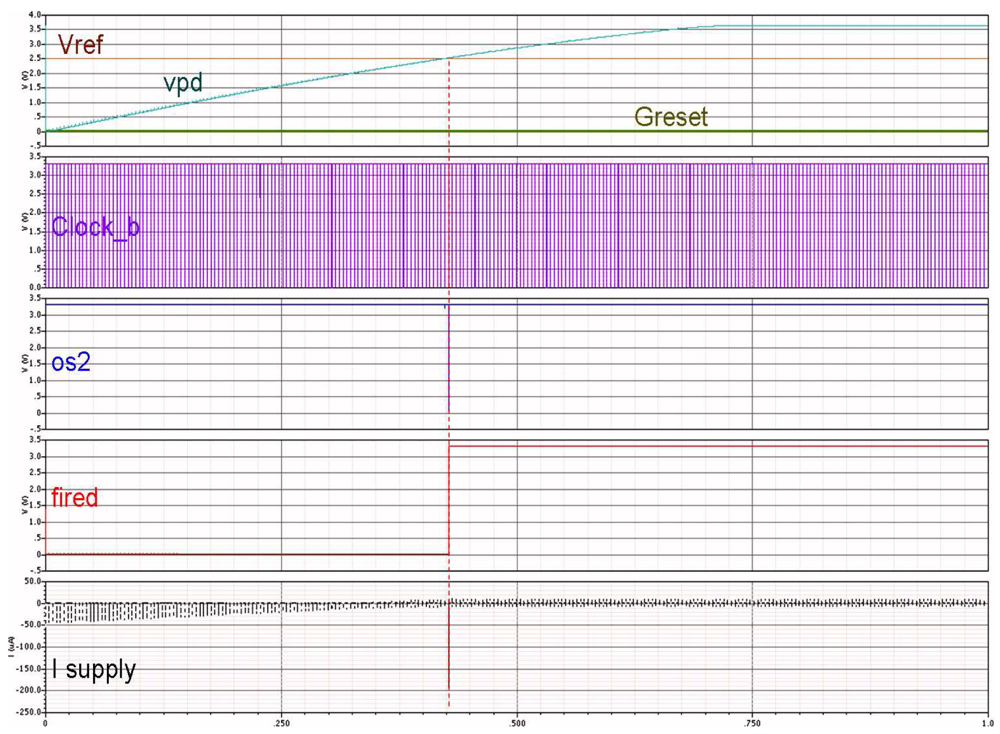

4.5. Read and Refresh Circuit

5. Power Analysis and Power Reduction Techniques

5.1. Power Consumption Analysis

5.2. Power Reduction Techniques

6. Hardware and Measurement Results

7. Conclusions

Supplementary Material

jlpea-01-00077-s001.pdf

| Average Power at 30 f/s | Average Energy per Frame at 30 f/s | |

|---|---|---|

| Array (Pixels) | 13.9 mW | 13.9 μJ (3.4 nJ/pixel) |

| Scan shift register | 800 nW | 23 nJ |

| Write buffers | 24 μW | 24 nJ |

| Scan register for line selection | 10 nW | 0.3 nJ |

| Precharge and sense amplifiers | 430 nW | 13 nJ |

| This Work | [7] | [2] (Conventional) | [4] | |

|---|---|---|---|---|

| Technology | 0.35 μm | 0.35 μm | 0.35 μm | 0.35 μm |

| Supply voltage | 3.3 V | 3.3 V | 3.3 V | 3.3 V |

| Pixel area | 22 μm × 22 μm | 30 μm × 26 μm | 45 μm × 45μm | 50 μm × 50 μm |

| Fill factor | 20% | 16% | 12% | 20% |

| Pixel current | 1 μA | N/A | 1.6 μA | N/A |

| Transistor count | 25 | 32 | 91 | 38 |

| Resolution | 4/8 bits | 4/8 bits | 8 bits | 4/8 bits |

| Frame/second | 33 | 300 | 33 * | 33 * |

Acknowledgments

References

- Kim, D.; Han, G. A 200 μs Processing Time Smart Image Sensor for an Eye Tracker Using Pixel-Level Analog Image Processing. IEEE J. Solid-State Circuits 2009, 44, 2581–2590. [Google Scholar]

- Bermak, A.; Kitchen, A. A Novel Adaptative Logarithmic Digital Pixel Sensor. IEEE Photonics Technol. Lett. 2006, 18, 2147–2149. [Google Scholar]

- Chen, S.; Bermak, A.; Boussaid, F. A Compact Reconfigurable Counter Memory for Spiking Pixels. IEEE Electron Device Lett. 2006, 27, 255–257. [Google Scholar]

- Bermak, A.; Yung, Y.F. A DPS Array with Programmable Resolution and Reconfigurable Conversion Time. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2006, 18, 15–22. [Google Scholar]

- Chen, S.; Bermak, A. Arbitrated Time to First Spike CMOS Image Sensor with On-Chip Histogram Equalization. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2007, 18, 346–357. [Google Scholar]

- Zhang, M.; Bermak, A. Compressive Acquisition CMOS IMage Sensor: From the Algorithm to Hardware Implementation. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2007, 18, 490–500. [Google Scholar]

- Campos, F.S.; Marinov, O.; Faramarzpour, N.; Saffih, F.; Jamal Deen, M.; Swart, J.W. A multisampling time-domain CMOS imager with synchronous readout circuit. Analog Integr. Circuits Signal Process. 2008, 44, 151–159. [Google Scholar]

- Leomant, S.; Wu, X.; Bermak, A. A Single Bit Memory per Pixel Time Domain DPS using Multi-Reset Integration Scheme. Proceedings The IEEE International Symposium on Circuits and Systems (ISCAS), Paris, France, 30 May–2 June 2010; pp. 353–356.

- Somasekhar, D.; Ye, Y.D.; Aseron, P.; Lu, S.L.; Khellah, M.M.; Howard, J.; Ruhl, G.; Karnik, T.; Borkar, S.; De, V.K.; Keshavarzi, A. 2 GHz 2 Mb 2T Gain Cell Memory Macro With 128 GBytes/sec Bandwidth in a 65 nm Logic Process Technology. IEEE J. Solid State Circuits 2009, 44, 174–185. [Google Scholar]

- Amrutur, B.S.; Horowitz, M.A. A Replica Technique for Wordline and Sense Control in Low-Power SRAM's. IEEE J. Solid State Circuits 1998, 33, 1208–1219. [Google Scholar]

© 2011 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Zhang, X.; Leomant, S.; Lau, K.L.; Bermak, A. A Compact Digital Pixel Sensor (DPS) Using 2T-DRAM. J. Low Power Electron. Appl. 2011, 1, 77-96. https://doi.org/10.3390/jlpea1010077

Zhang X, Leomant S, Lau KL, Bermak A. A Compact Digital Pixel Sensor (DPS) Using 2T-DRAM. Journal of Low Power Electronics and Applications. 2011; 1(1):77-96. https://doi.org/10.3390/jlpea1010077

Chicago/Turabian StyleZhang, Xiaoxiao, Sylvain Leomant, Ka Lai Lau, and Amine Bermak. 2011. "A Compact Digital Pixel Sensor (DPS) Using 2T-DRAM" Journal of Low Power Electronics and Applications 1, no. 1: 77-96. https://doi.org/10.3390/jlpea1010077