Multi-Threshold NULL Convention Logic (MTNCL): An Ultra-Low Power Asynchronous Circuit Design Methodology

Abstract

:1. Introduction

2. Previous Work

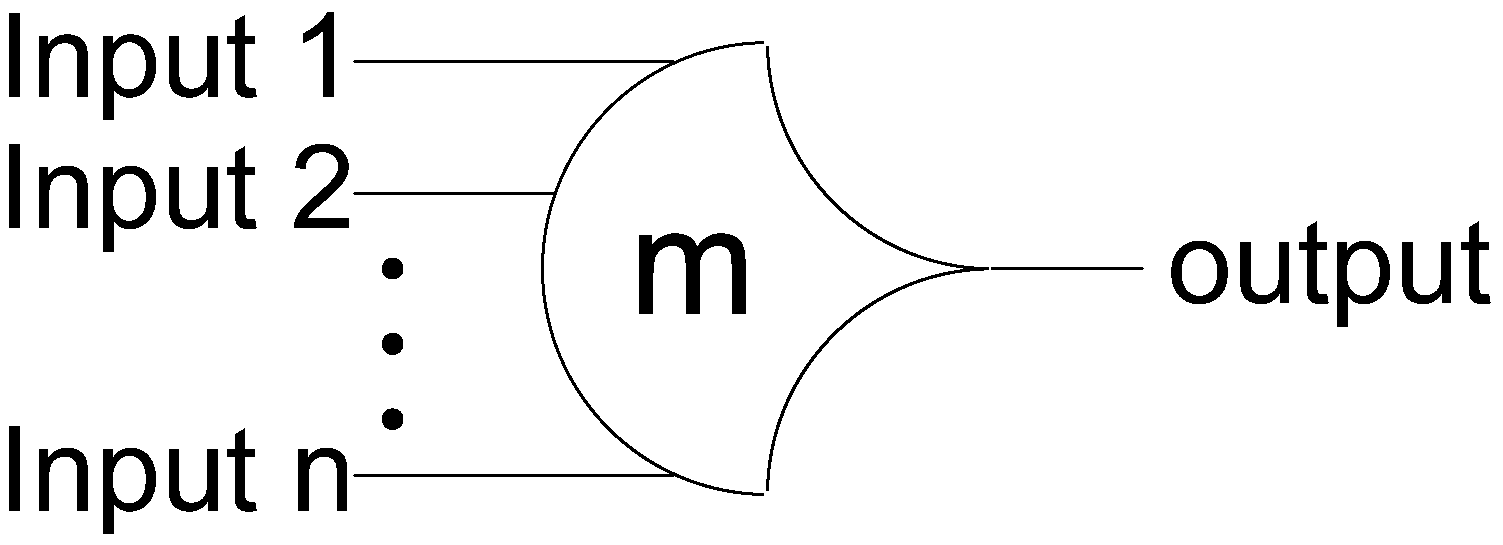

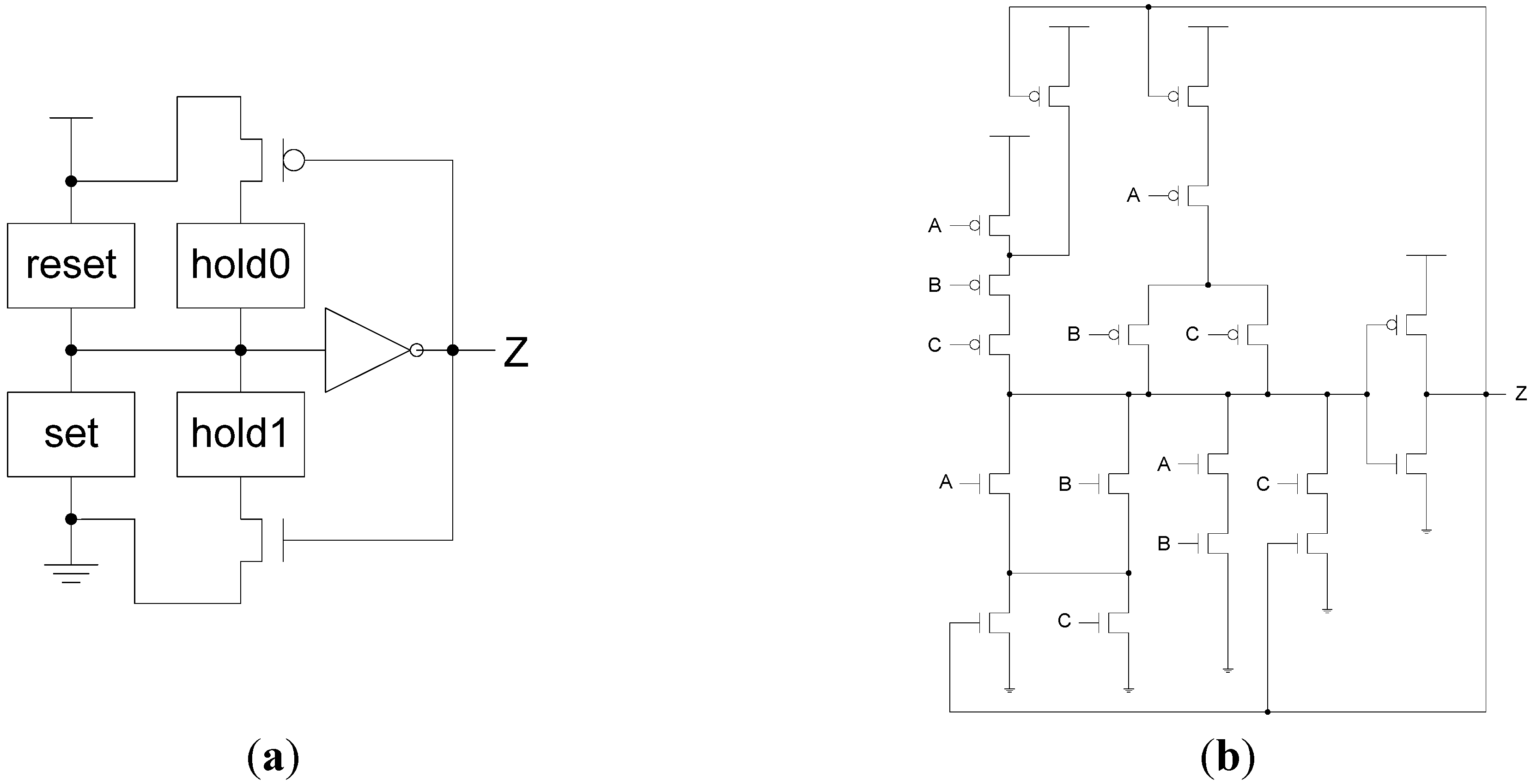

2.1. Introduction to NCL

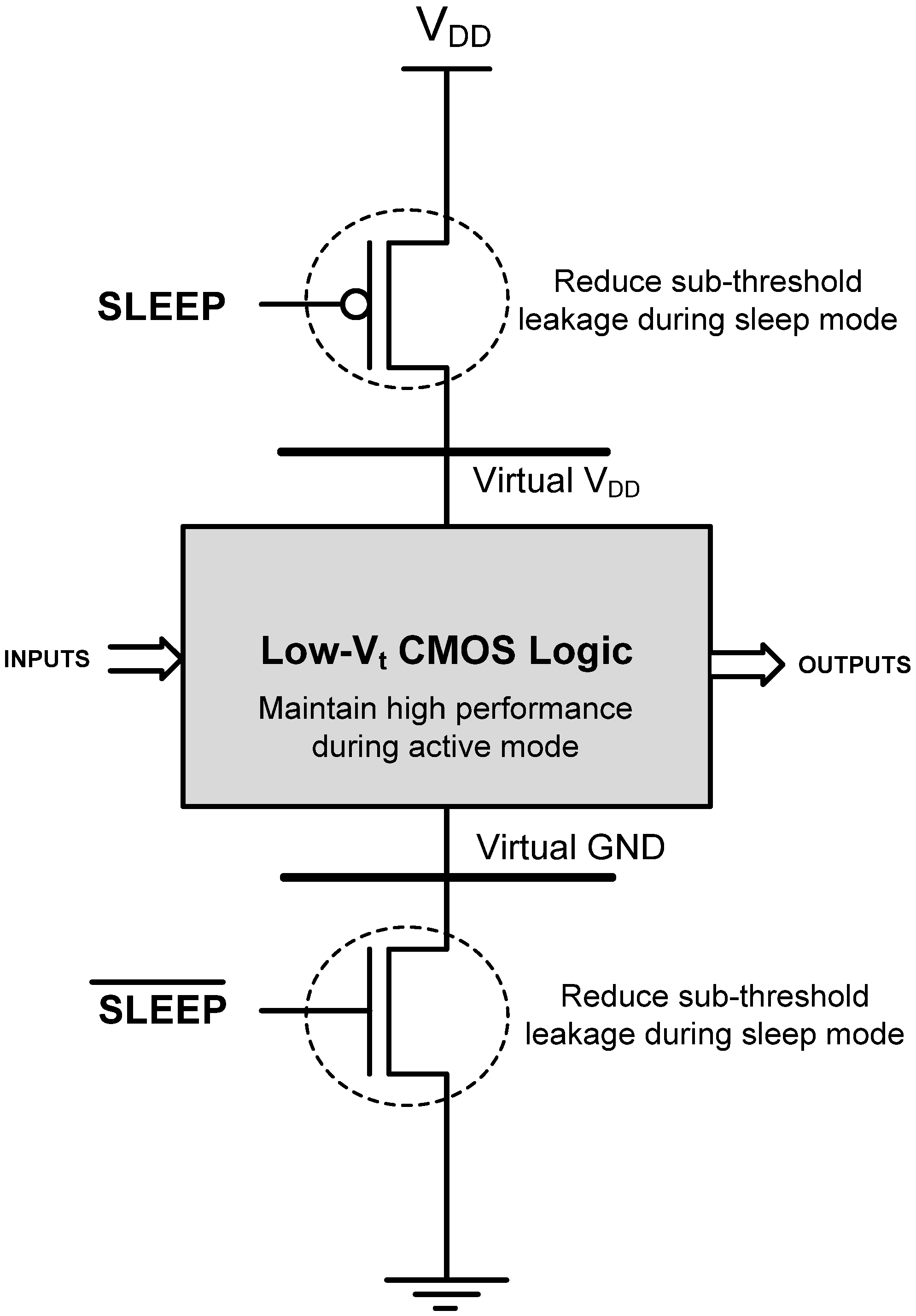

2.2. Introduction to MTCMOS

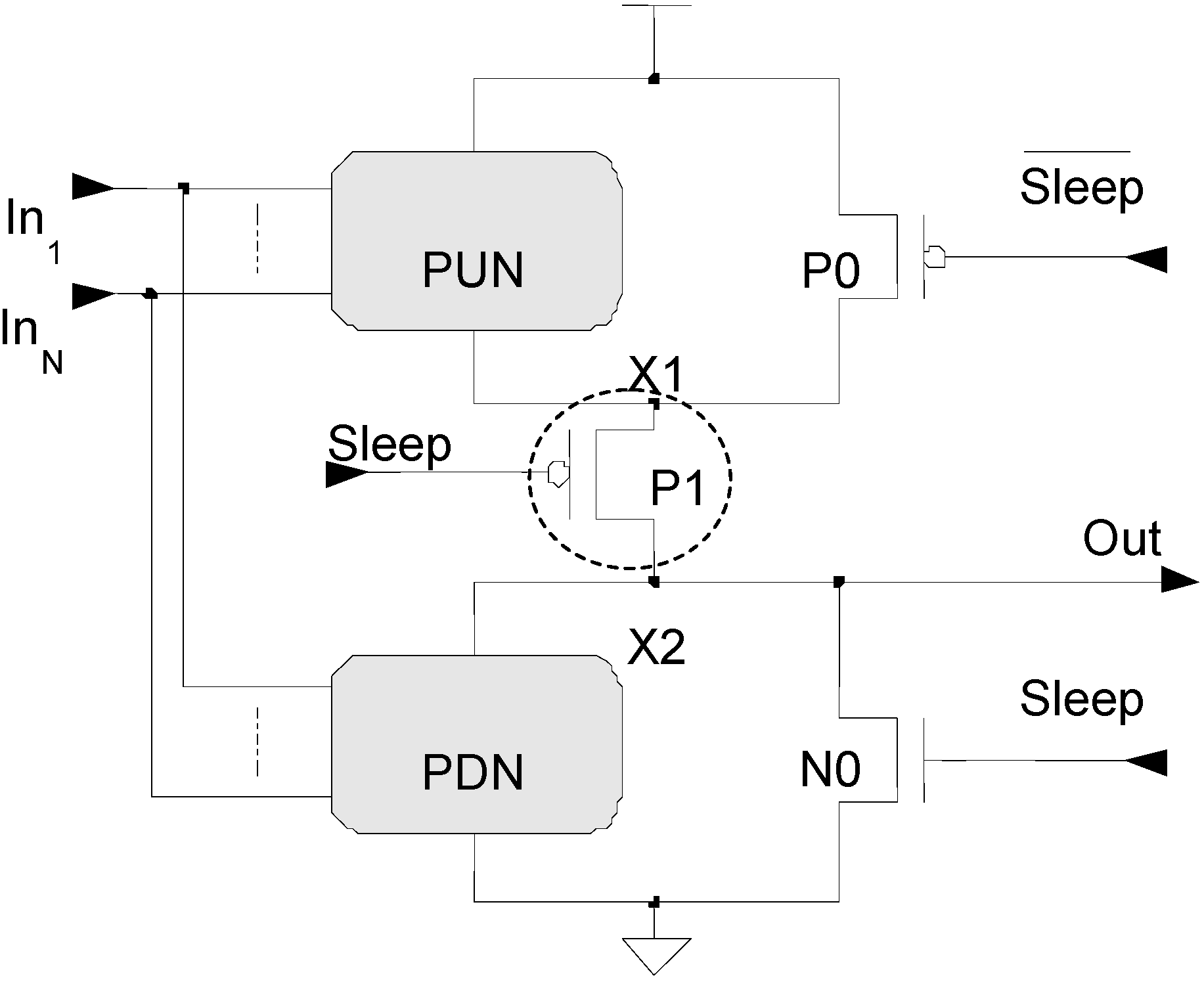

2.3. Introduction to MTNCL

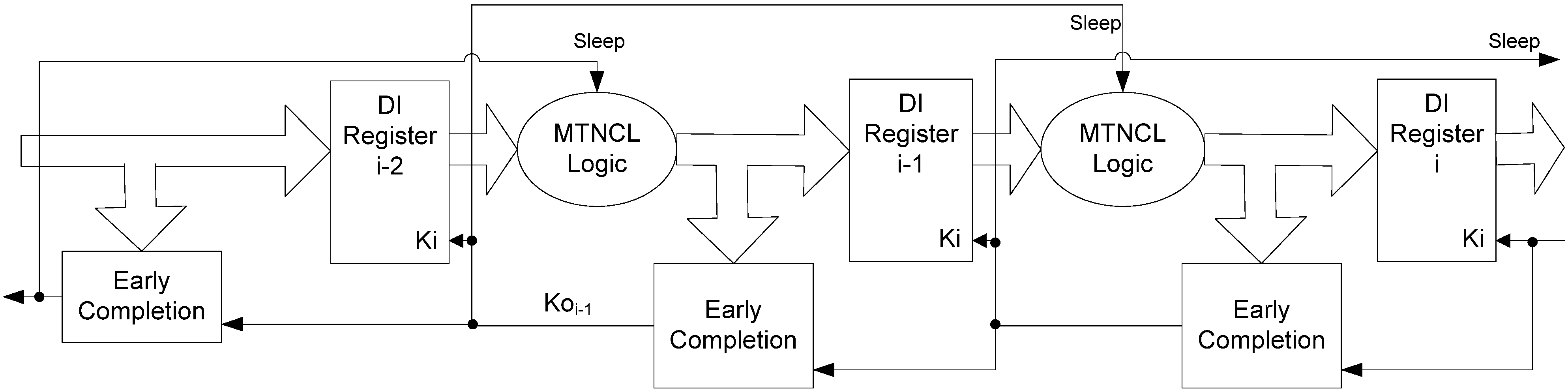

2.3.1. Early-Completion Input-Incomplete (ECII) MTNCL Architecture

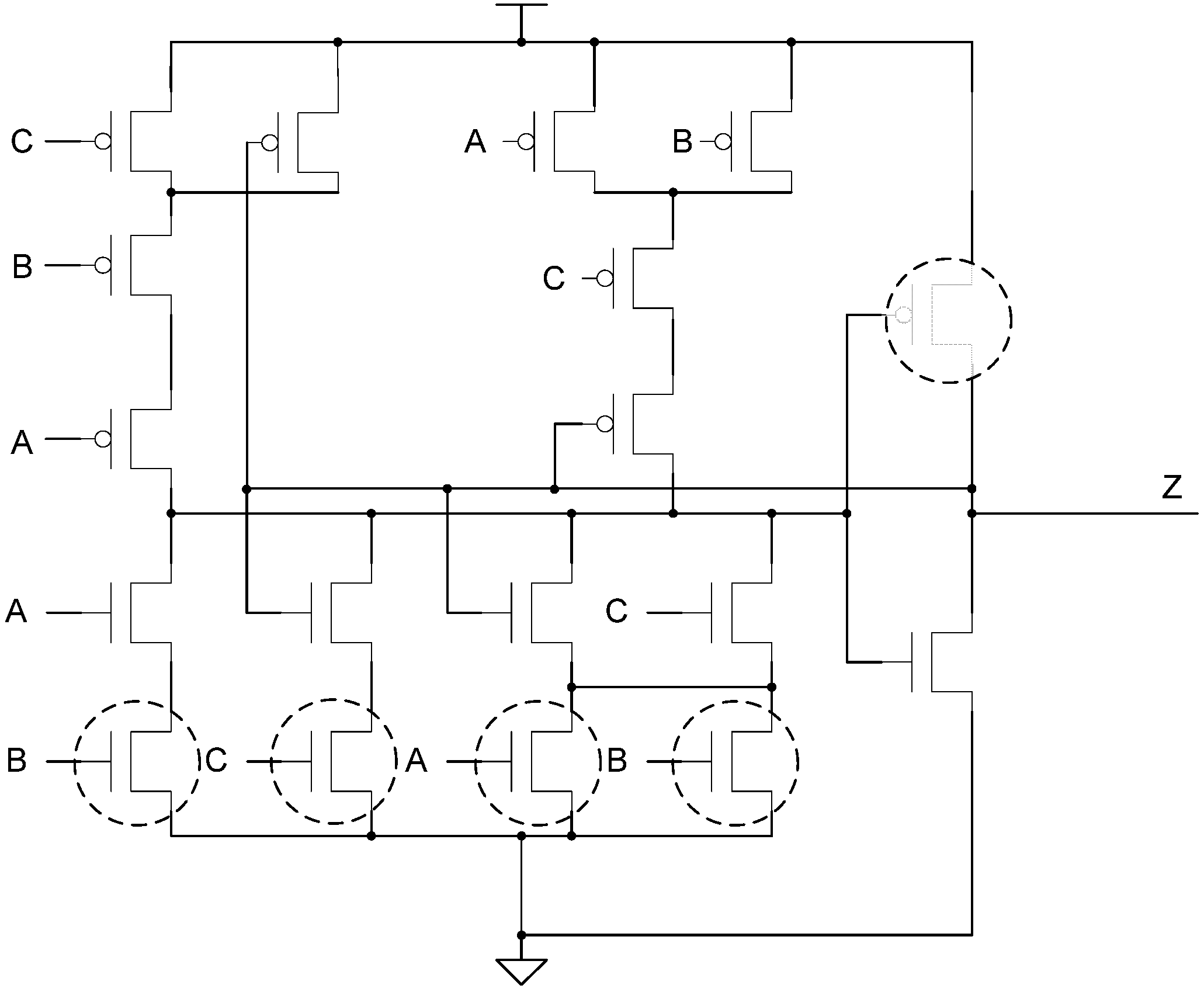

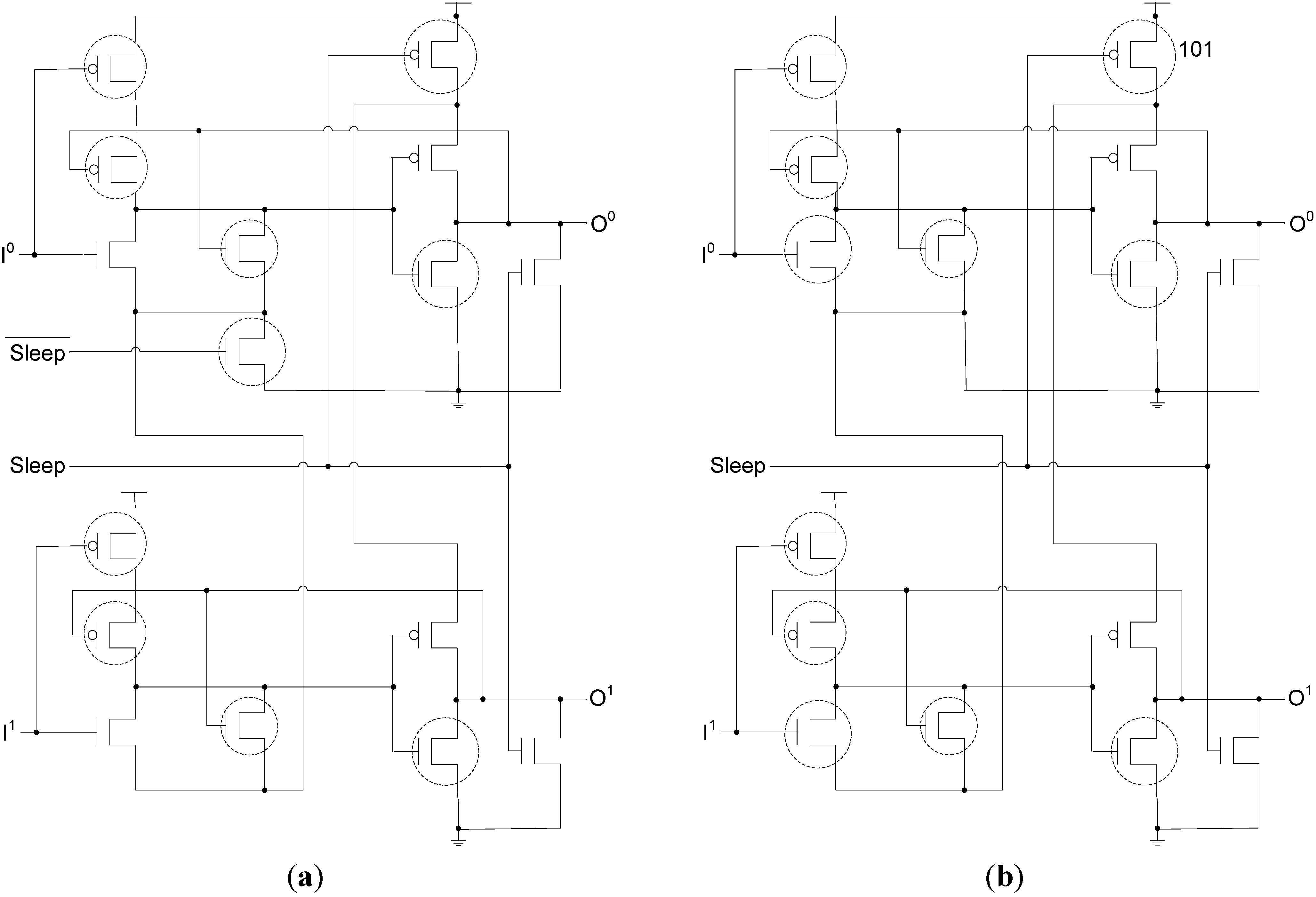

2.3.2. MTNCL Threshold Gate Design for ECII Architecture

2.3.3. MTNCL Threshold Gate Design for ECII Architecture

2.3.4. Bit-Wise MTNCL

3. MTNCL Enhancements

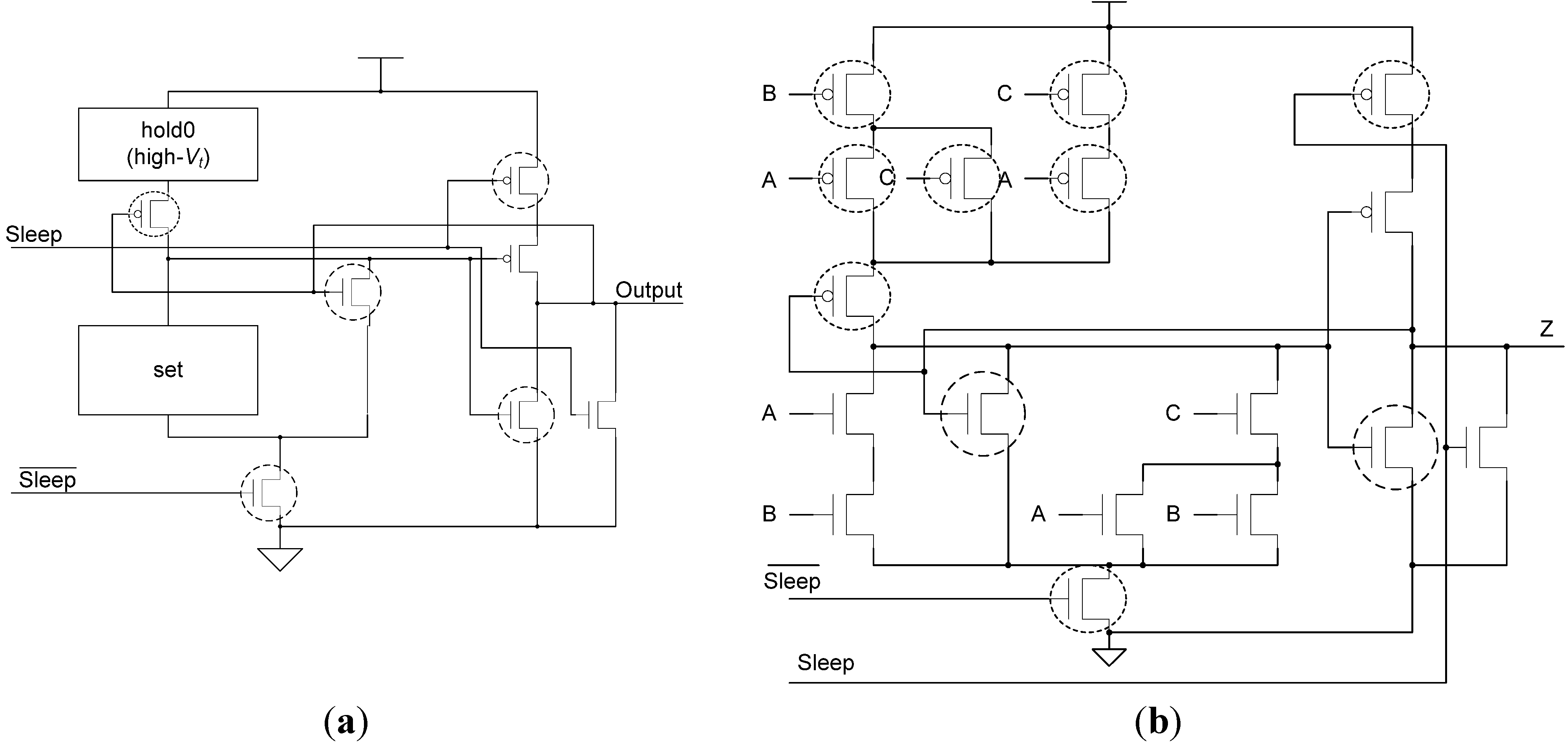

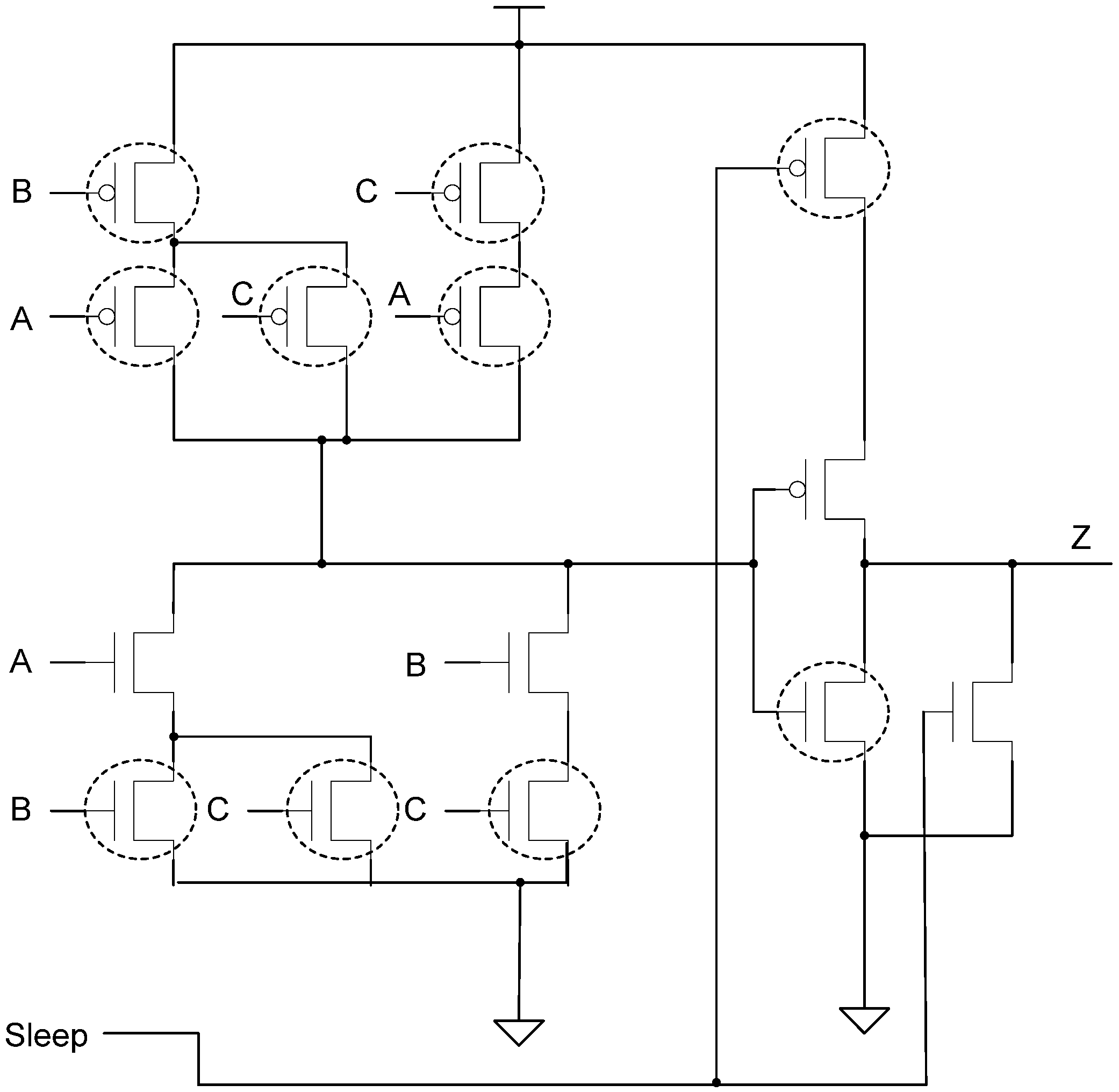

3.1. New SMTNCL1 Gate

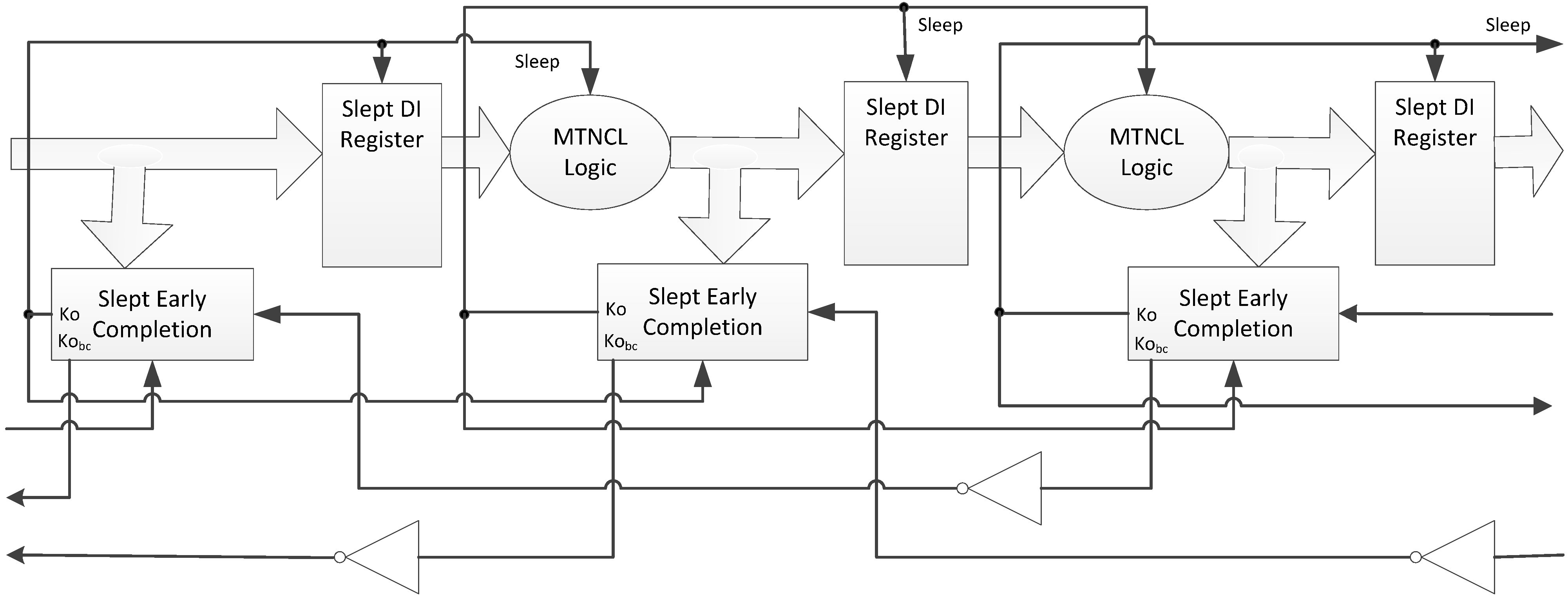

3.2. Sleep Completion and Registration Logic

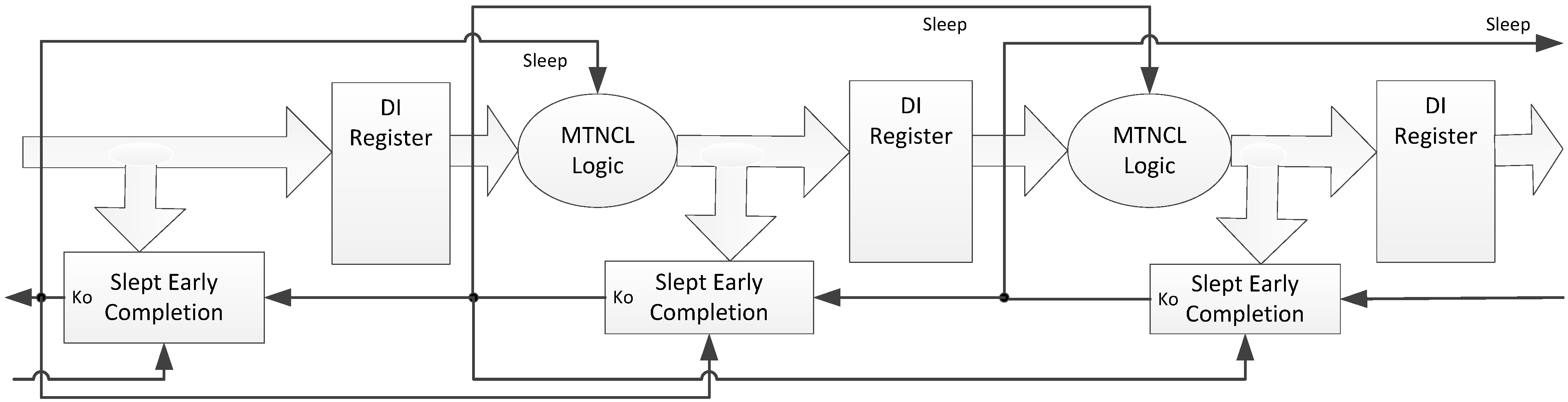

3.3. Combine SECRII with BWMTNCL

3.4. Safe SECRII Architecture

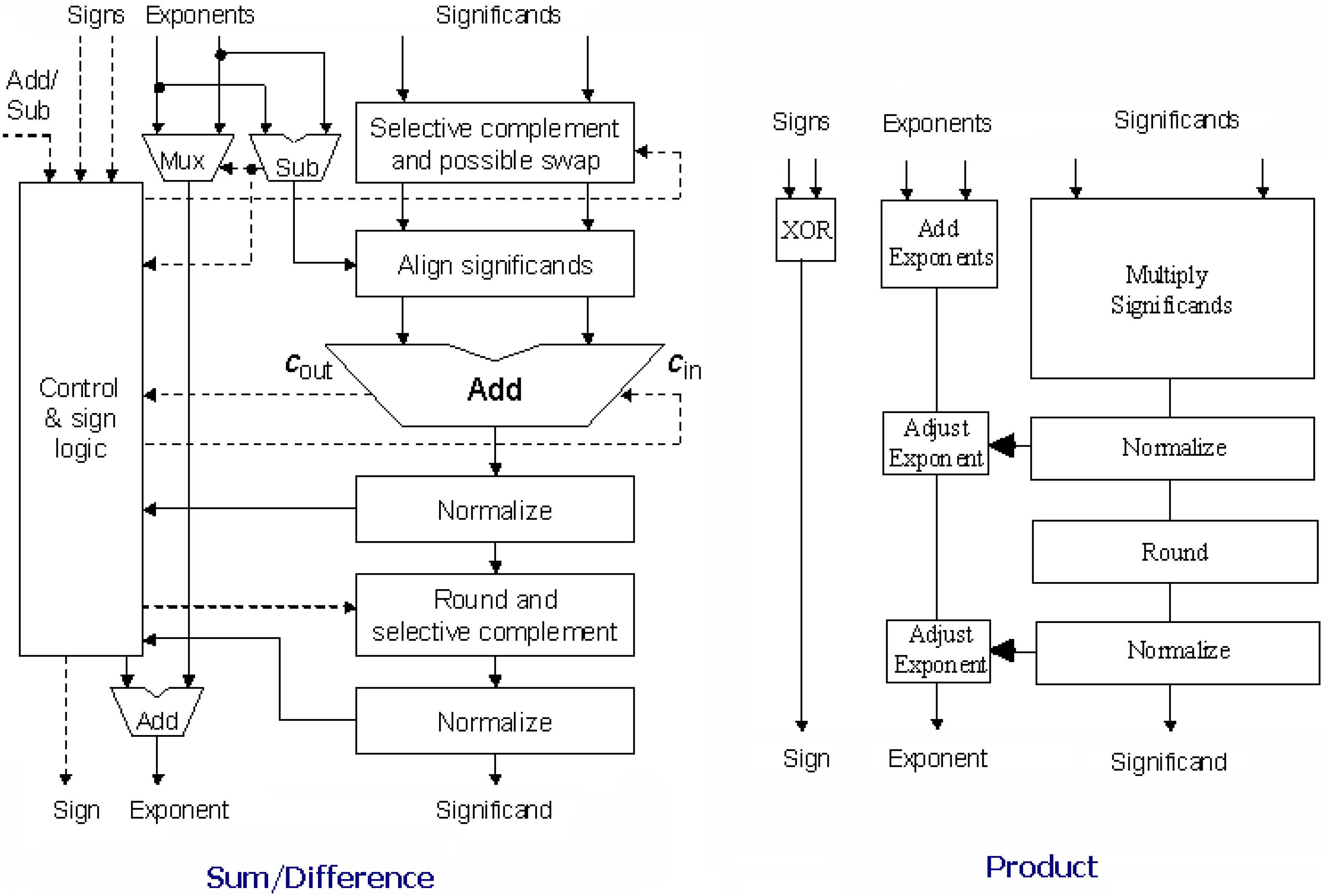

4. Simulation Results

| Circuit Type | # Transistors | TDD (ns) | Energy/Operation (pJ) | Idle Power (nW) | |||

|---|---|---|---|---|---|---|---|

| add/sub. | Mult. | add/sub. | Mult. | add/sub. | Mult. | ||

| NCL Low-Vt | 158059 | 14.1 | 14.4 | 27.4 | 23.7 | 12,300 | 12,300 |

| NCL High-Vt | 158059 | 32.7 | 33.4 | 28.5 | 25.1 | 208.0 | 208.0 |

| BWMTNCL | 158059 | 17.9 | 16.2 | 27.1 | 23.7 | 190.7 | 190.7 |

| SMTCNL with FECII | 111506 | 11.6 | 15.3 | 14.9 | 27.5 | 115.9 | 115.9 |

| Original SMTNCL1 with ECII | 130476 | 12.5 | 16.7 | 16.0 | 27.8 | 140.8 | 140.8 |

| New SMTNCL1 with ECII | 119706 | 12.1 | 15.7 | 14.7 | 26.1 | 121.9 | 121.9 |

| SMTNCL1 with SECII | 119244 | 10.7 | 15.4 | 14.6 | 26.0 | 121.1 | 121.1 |

| SMTNCL with SECRII | 96640 | 11.1 | 14.8 | 13.5 | 25.3 | 111.2 | 111.2 |

| SMTNCL with SECRII w/o nsleep | 90041 | 10.0 | 13.9 | 12.1 | 21.8 | 112.1 | 112.1 |

| SMTNCL with SECRII w/o nsleep (safe architecture) | 90049 | 13.4 | 16.6 | 12.3 | 22.3 | 113 | 113 |

| MTCMOS Synchronous | 104571 | 10.0 | 13.9 | 124.3 | 124.7 | 156,000 | 132,000 |

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Mutoh, S.; Douseki, T.; Matsuya, Y.; Aoki, T.; Shigematsu, S.; Yamada, J. 1-V Power Supply High-Speed Digital Circuit Technology with Multithreshold-Voltage CMOS. IEEE J. Solid-State Circuits 1995, 30, 847–854. [Google Scholar] [CrossRef]

- Fant, K.M.; Brandt, S.A. NULL Convention Logic: A Complete and Consistent Logic for Asynchronous Digital Circuit Synthesis. In Proceedings of the International Conference on Application Specific Systems, Architectures and Processors, Chicago, IL, USA, 19–21 August 1996; pp. 261–273.

- Sobelman, G.E.; Fant, K.M. CMOS Circuit Design of Threshold Gates with Hysteresis. In Proceedings of the 1998 IEEE International Symposium on Circuits and Systems (II), Monterey, CA, USA, 31 May–3 June 1998; pp. 61–65.

- Muller, D.E. Asynchronous Logics and Application to Information Processing. In Switching Theory in Space Technology; Stanford University Press: Redwood City, CA, USA, 1963; pp. 289–297. [Google Scholar]

- Parsan, F.A.; Smith, S.C. CMOS Implementation of Static Threshold Gates with Hysteresis: A New Approach. In Proceedings of the IFIP/IEEE International Conference on VLSI-SoC, Santa Cruz, CA, USA, 7–10 October 2012; pp. 41–45.

- Parsan, F.A.; Smith, S.C. CMOS Implementation Comparison of NCL Gates. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Boise, ID, USA, 5–8 August 2012; pp. 394–397.

- Smith, S.C.; DeMara, R.F.; Yuan, J.S.; Hagedorn, M.; Ferguson, D. Delay-Insensitive Gate-Level Pipelining. Elsevier’s Integ. VLSI J. 2001, 30, 103–131. [Google Scholar] [CrossRef]

- Smith, S.C.; DeMara, R.F.; Yuan, J.S.; Ferguson, D.; Lamb, D. Optimization of NULL Convention Self-Timed Circuits. Integr. VLSI J. 2004, 37, 135–165. [Google Scholar] [CrossRef]

- Seitz, C.L. System Timing. In Introduction to VLSI Systems; Addison-Wesley: Boston, MA, USA, 1980; pp. 218–262. [Google Scholar]

- Kondratyev, A.; Neukom, L.; Roig, O.; Taubin, A.; Fant, K. Checking Delay-Insensitivity: 104 Gates and Beyond. In Proceedings of the Eighth International Symposium on Asynchronous Circuits and Systems, Manchester, UK, 8–11 April 2002; pp. 149–157.

- Martin, A.J. Programming in VLSI: From Communicating Processes to Delay-Insensitive Circuits. In Developments in Concurrency and Communication; UT Year of Programming Institute on Concurrent Programming, Addison-Wesley: Boston, MA, USA, 1990; pp. 1–64. [Google Scholar]

- Van Berkel, K. Beware the Isochronic Fork. Integr. VLSI J. 1992, 13, 103–128. [Google Scholar] [CrossRef]

- Kao, J.T.; Chandrakasan, A.P. Dual-Threshold Voltage Techniques for Low-Power Digital Circuits. IEEE J. Solid-State Circuits 2000, 35, 1009–1018. [Google Scholar] [CrossRef]

- Lakshmikanthan, P.; Sahni, K.; Nunez, A. Design of Ultra-Low Power Combinational Standard Library Cells Using a Novel Leakage Reduction Methodology. In Proceedings of the IEEE International SoC Conference, Taipei, Taiwan, 24–27 September 2006; pp. 93–94.

- Bailey, A.D.; Di, J.; Smith, S.C.; Mantooth, H.A. Ultra-Low Power Delay-Insensitive Circuit Design. In Proceedings of IEEE Midwest Symposium on Circuits and Systems, Knoxville, TN, USA, 10–13 August 2008; pp. 503–506.

- Bailey, A.D.; Al Zahrani, A.; Fu, G.; Di, J.; Smith, S.C. Multi-Threshold Asynchronous Circuit Design for Ultra-Low Power. J. Low Power Electron. 2008, 4, 337–348. [Google Scholar] [CrossRef]

- Alzahrani, A.; Bailey, A.D.; Fu, G.; Di, J. Glitch-Free Design for Multi-Threshold CMOS NCL Circuits. In Proceedings of the ACM 2009 Great Lakes Symposium on VLSI, Boston, MA, USA, 10–12 May 2009.

- Smith, S.C.; Di, J. Designing Asynchronous Circuits using NULL Convention Logic (NCL); Synthesis Lectures on Digital Circuits and Systems; Morgan & Claypool Publishers: San Rafael, CA, USA, 2009; Volume 4. [Google Scholar] [CrossRef]

- Zhou, L.; Smith, S.C.; Di, J. An Ultra-Low Power Bit-Wise MTNCL: An Ultra-Low Power Bit-Wise Pipelined Asynchronous Circuit Design Methodology. In Proceedings of the IEEE Midwest Symposium on Circuits and Systems, Seattle, WA, USA, 1–4 August 2010; pp. 217–220.

- Smith, S.C. Speedup of Self-Timed Digital Systems Using Early Completion. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, Pittsburgh, PA, USA, 25–26 April 2002; pp. 107–113.

- Reese, R.B. UNCLE User Manual. Available online: http://www.ece.msstate.edu/~reese/uncle/UNCLE.pdf (accessed on April 2015).

- Parhami, B. Computer Arithmetic Algorithms and Hardware Designs; Oxford University Press: New York, NY, USA, 2000. [Google Scholar]

- Thian, R. Multi-Threshold CMOS Circuit Design Methodology from 2D to 3D. Master’s Thesis, Computer Science and Computer Engineering Department, University of Arkansas, Fayetteville, AR, USA, December 2010. [Google Scholar]

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, L.; Parameswaran, R.; Parsan, F.A.; Smith, S.C.; Di, J. Multi-Threshold NULL Convention Logic (MTNCL): An Ultra-Low Power Asynchronous Circuit Design Methodology. J. Low Power Electron. Appl. 2015, 5, 81-100. https://doi.org/10.3390/jlpea5020081

Zhou L, Parameswaran R, Parsan FA, Smith SC, Di J. Multi-Threshold NULL Convention Logic (MTNCL): An Ultra-Low Power Asynchronous Circuit Design Methodology. Journal of Low Power Electronics and Applications. 2015; 5(2):81-100. https://doi.org/10.3390/jlpea5020081

Chicago/Turabian StyleZhou, Liang, Ravi Parameswaran, Farhad A. Parsan, Scott C. Smith, and Jia Di. 2015. "Multi-Threshold NULL Convention Logic (MTNCL): An Ultra-Low Power Asynchronous Circuit Design Methodology" Journal of Low Power Electronics and Applications 5, no. 2: 81-100. https://doi.org/10.3390/jlpea5020081

APA StyleZhou, L., Parameswaran, R., Parsan, F. A., Smith, S. C., & Di, J. (2015). Multi-Threshold NULL Convention Logic (MTNCL): An Ultra-Low Power Asynchronous Circuit Design Methodology. Journal of Low Power Electronics and Applications, 5(2), 81-100. https://doi.org/10.3390/jlpea5020081