1. Introduction

Supply voltage reduction, as a direct consequence of the process technologies’ scaling, is further enforced by battery-operated biomedical implant devices, such as pacemakers, cardiac defibrillators and neural recording integrated circuits, to make their operating supply compatible with human body potentials [

1,

2], in the range of few hundreds of mVs. Therefore, designing analogue-to-digital converters (ADCs) operating at a very low supply voltage is inevitable for the measurement of various electrophysiological signals (e.g., ECGs, EEGs,

etc.).

Pacemakers need to sense the cardiac signals, which mainly are situated in very low frequencies from nearly DC to several hundred hertz [

3,

4,

5,

6,

7]. The cardiac signals are sensed by the low-noise amplifier, amplified by a gain stage; the undesired interferences are filtered out, and then, the detected analog signal is digitized by a back-end ADC. The ADC architecture and circuit design play a key role in maintaining ultra-low-power efficiency while providing a high conversion accuracy (or resolution). ADC resolutions from eight bit to 13 bit have been reported previously [

5,

6,

7]. The low frequency noise, including flicker noise, needs to be treated properly in the circuit implementation.

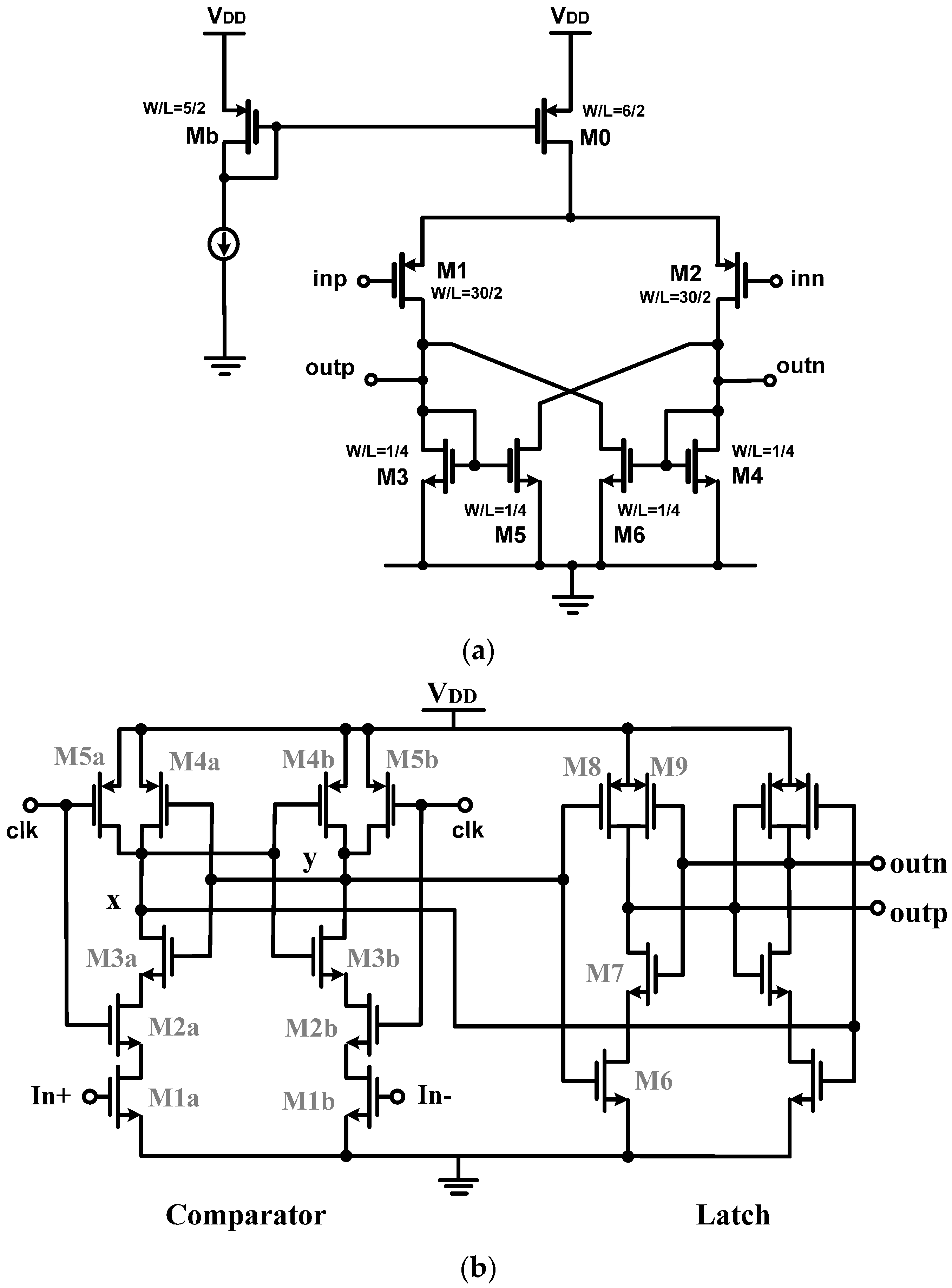

There are two critical factors that can determine the lowest operating power supply of the traditional sigma-delta (ΔΣ) modulators: operational transconductance amplifiers (OTAs) in the integrators and the adequate driving voltage of the switching transistors [

8,

9,

10,

11,

12,

13,

14]. The conventional analog circuit topologies are no longer practical in ultra-low-voltage operations (below 0.6 V), and also, stacking more than two transistors is impossible due to the limited overdrive and voltage headroom. The inverter is the simplest amplifier, which can sustain a supply voltage of less than the sum of the absolute threshold voltages of the NMOS and PMOS transistors [

12], also known as a Class-C inverter. The DC gain and gain-bandwidth product (GBW) of the CMOS inverter degrade significantly at supplies far below the nominal V

TN + |V

TP| = 0.62 V and need to be enhanced for a robust and high-performance modulator design. Chae and Han [

12] proposed an inverter-based ΔΣ modulator using a cascode inverter for boosting the DC gain. In this paper, we present a fully-differential second-order feedforward ΔΣ modulator for ultra-low-voltage low-power biomedical applications, which uses a novel gain-enhanced inverter-based, current mirror amplifier to replace the OTA in the integrators. Moreover, a clock boosting scheme is used to sufficiently drive the switching transistors. While all transistors operate at gate voltage less than 300 mV, the effective gate voltage of the switches is 600 mV with the aid of a charge pump clock doubler [

13]. The single-bit quantizer, including the preamplifier, dynamic comparator and latch, was designed in a deep sub-threshold regime, providing very high power efficiency.

The rest of the paper is organized as follows:

Section 2 describes the proposed gain-enhanced inverter-based amplifier and its advantages and drawbacks.

Section 3 discusses the modulator architecture and its low-voltage and low-power design considerations.

Section 4 presents the modulator circuit design.

Section 5 discusses the simulation results. In

Section 6, the proposed modulator is compared to the reported state-of-the-art ultra-low-voltage modulators. Conclusions are drawn in

Section 7.

2. Proposed Gain-Enhanced Inverter-Based OTA

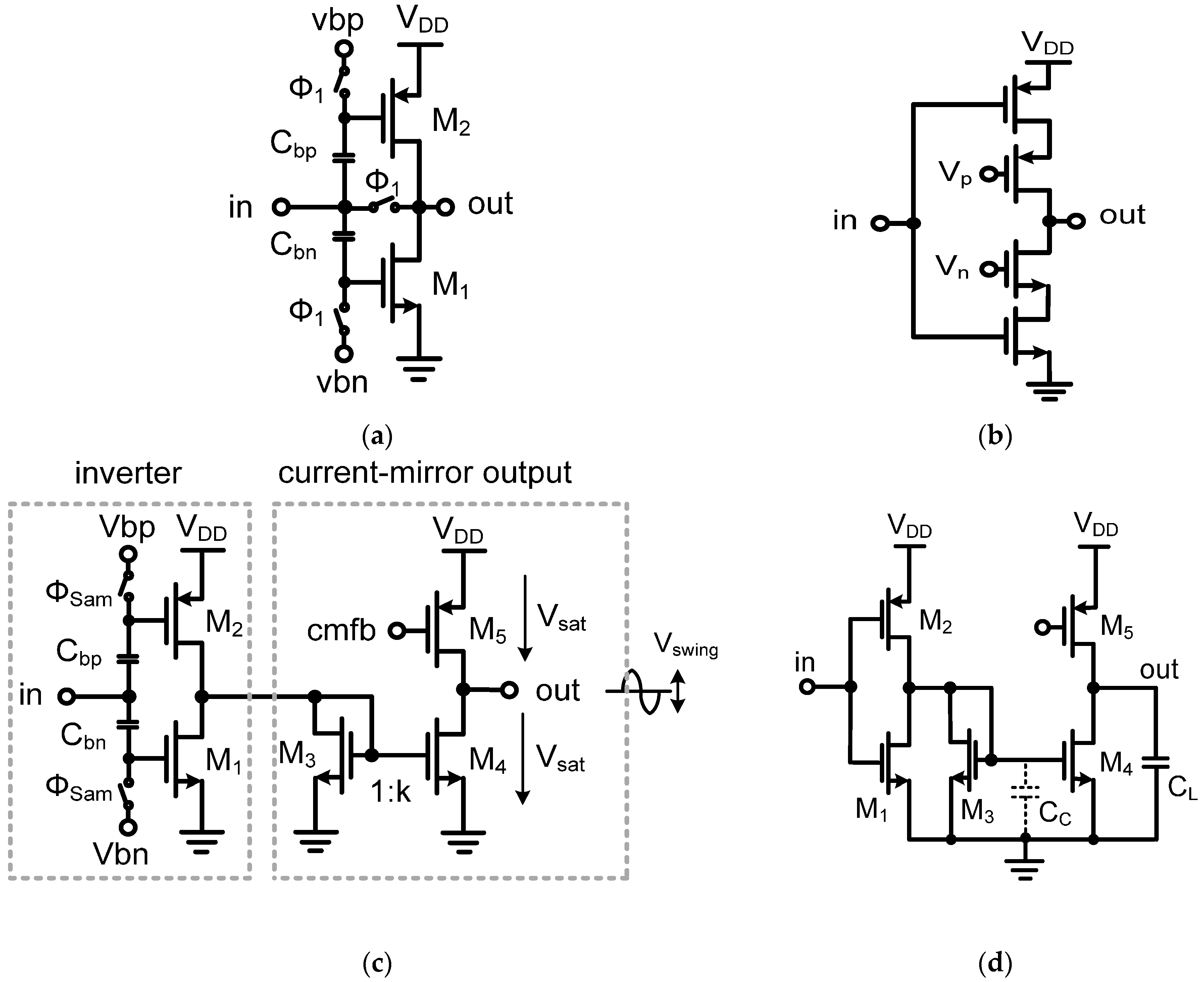

A novel inverter-based amplifier is proposed for ultra-low-voltage applications, which is composed of a Class-C inverter and a current mirror output stage.

Figure 1 shows the schematics of the basic CMOS inverter, the cascode inverter and the proposed inverter-based, current mirror OTA (

Figure 1c).

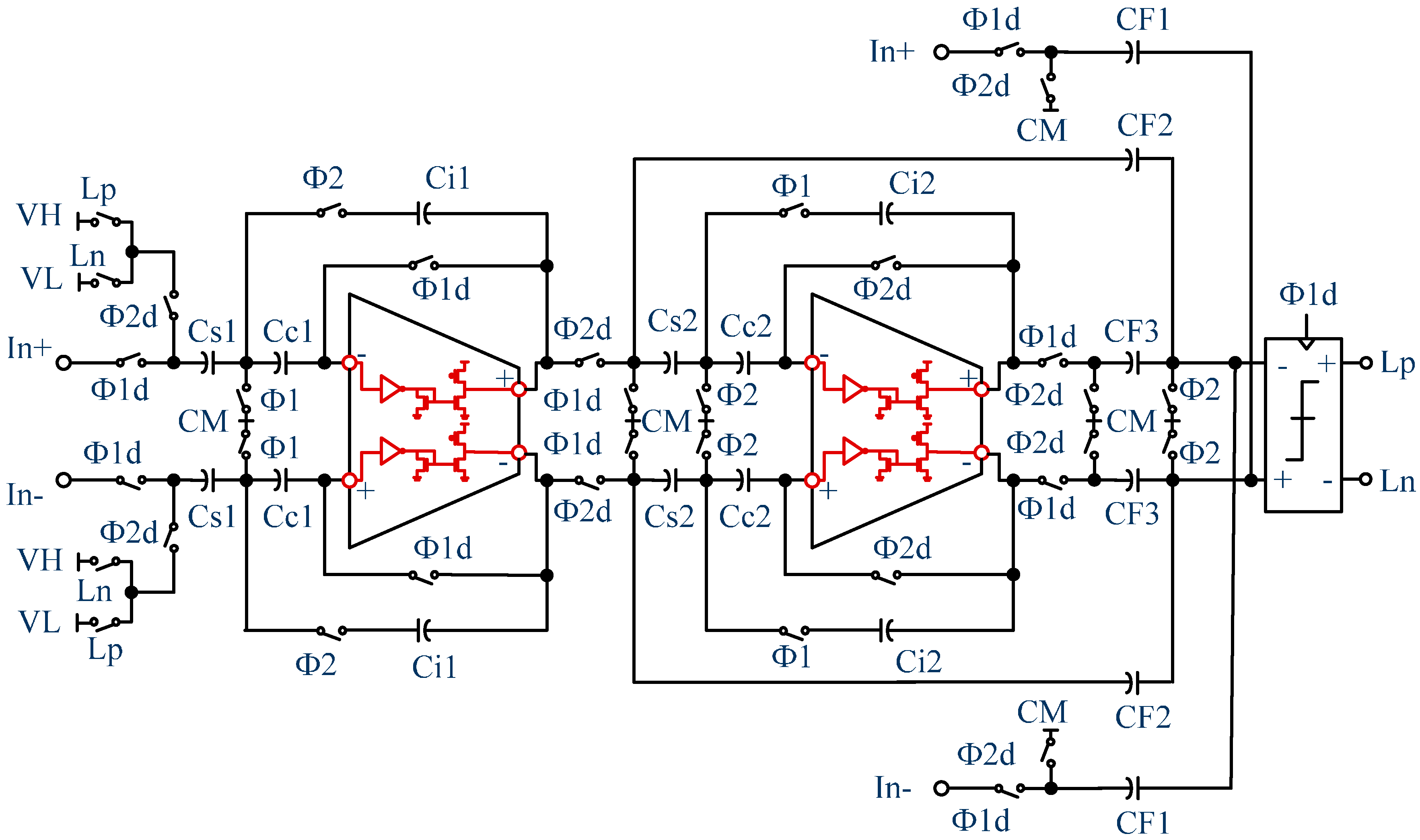

A switched-capacitor (SC) biasing scheme using floating capacitors

Cbp and

Cbn (

Figure 1c) is used to define the operating point of the inverter M

1–M

2. These capacitors are periodically refreshed by the bias voltages

Vbn and

Vbp during the sampling phase Ф

Sam (Ф

Sam = Ф

1d in the first integrator; Ф

Sam = Ф

2d in the second integrator) and work as floating batteries between the input and the gates of the transistors. It is worth mentioning that the pre-charging

Vbn and

Vbp occurs simultaneously with sampling the signal onto

CS1 (

CS2) and the inverter offset onto

CC1 (

CC2) in phase Ф

Sam (

Figure 4). The sampling clock speed is low (

i.e., 256 kHz), so initially, the

Cbp =

Cbn = 0.5 pF are charged in the early phase of Ф

Sam (

Cbp =

Cbn <<

CCi), and then, the amplifier is placed in the unity feedback configuration for offset sampling when its biasing was set appropriately. The

Vbp and

Vbn are generated using a constant-

gm biasing circuit followed by a level shifter to eliminate the

Vsat problem as in [

15], which provides wider overdrive voltage and, in turn, a smaller transistor width. At the output stage, an energy-efficient SC common-mode feedback (CMFB) circuit is employed [

8], which derives the gate of PMOS transistor M

5, in order to set the output CM level at the middle of the supply voltage for the maximum output swing.

The DC gain and GBW of the CMOS inverter degrade significantly at supplies far below the nominal V

TN + |V

TP|, which need to be enhanced for a robust and high-performance modulator design. The aim of the proposed technique is to boost the gain and GBW simultaneously by mirroring a small fraction (~10%) of the bias current of the inverter M

1–M

2 through transistor M

3 to the output. The factor

k is the current ratio of the current mirror M

3–M

4 and is defined as (W/L)

M4/(W/L)

M3. The approximate gain and GBW of the proposed amplifier shown in

Figure 1c can be determined from its small-signal model using sub-threshold current as:

where

gmi and

gdsi represent the transconductance and output conductance of the

i-th transistor, respectively.

Rout is the total output resistance, which is equal to (

gds4 +

gds5)

−1.

CL is the total load capacitor for the frequency compensation.

n and

VT are the sub-threshold parameters. We consider

α =

ID3/

ID2 as the ratio of the currents of M

3 and M

2. In addition, it can be shown that the term

gm4/(

gm3 + gds1 +

gds2 +

gds3) is approximately equal to

k. A large device size of M

1–M

2 has to be prevented, as it creates large parasitic capacitors, which can limit the amplifier speed.

To explain the gain-enhancement technique, the DC gain of the basic inverter (

Figure 1a) and the proposed amplifier (

Figure 1c) given by Equation (1) can be written in the following forms in Equations (3) and (6):

VT is the thermal voltage; n is the non-ideality factor; and λ is the channel length modulation coefficient. A0 is the intrinsic gain achieved by an inverter in the sub-threshold regime. In deep submicron technologies, by shrinking the transistor length, the effect of channel length modulation becomes more important. As a consequence, the output resistance and, thus, the DC gain of the inverter are normally low.

In

Figure 1c, the bias current of the diode-connected device (

i.e.,

ID3) is equal to

α ID2, where

α in this design is approximately 0.1. The M

1 transistor then shunts the rest of the current to the ground. Assuming M

1 carries (1 −

α) ×

ID2, from Equation (1), the gain of the proposed OTA can be expressed as:

Now, the biasing current of M

4 is:

Finally, the enhanced gain of the OTA is given by:

From Equation (6), it can be seen that the gain is enhanced (1/α − 0.5)-times. The gain increase can be adjusted by the

α factor during the design. With

α = 0.1 in this design, the gain can be enhanced 9.5-times directly from Equation (6). With

α =

ID3/

ID2 as the ratio of the currents in M

3 and M

2, the current mismatch can affect the gain enhancement (

Section 2.2). In typical corner simulation from a 0.3 V supply, the

α factor is about 0.12, which corresponds to a gain enhancement of eight-times, whereas in the worst-case corner, it is approximately 0.13, corresponding to a gain enhancement of seven-times.

Figure 2a shows the variations of the DC gain with respect to the supply voltage (

VDD) for the basic inverter shown in

Figure 1a and the gain-enhanced inverter shown in

Figure 1c.

Figure 2b,c also shows the variations of the GBW as a function of the

VDD for both the basic inverter and the gain-enhanced inverter. For PMOS transistor M

2, the overdrive voltage (

i.e.,

VDD −

Vbp − |

VTP|) depends on

VDD and increases by increasing

VDD. Similarly, for NMOS device M

1, the overdrive voltage (

i.e.,

Vbn −

VTN) is enhanced linearly with

VDD to accommodate a wider input linear range in this analysis.

For VDDs far below VTN + |VTP|, the DC gain and GBW degrade significantly. A large device size in M1–M2 has to be avoided, as this creates large parasitic capacitances, which can limit the OTA performance. The aim of this work is to enhance the gain and GBW simultaneously by mirroring a small fraction of the bias current of the inverter M1–M2 to the output stage (with α ~ 10% and k = 8).

Shown in

Figure 2, with the current mirror gain-enhancement technique, the simulated DC gain and GBW increase to 40 dB and 1.9 MHz from 22 dB and 0.38 MHz, respectively, from a 0.3 V supply and a 3 pF load capacitance in a typical (TT) process corner, at 27 °C. The phase margin is 66 °C. The transistors sizes of the developed inverter-based current mirror amplifier are summarized in

Table 1. The DC gain gets worse in FS (fast NMOS, slow PMOS) and SF (slow NMOS, fast PMOS) process corners (

i.e., 37 dB at

VDD = 0.3 V), whereas its deviation is trivial for FF and SS corners (

i.e., 39 dB at

VDD = 0.3 V).

In practice, the gain enhancement can be restricted by several factors: phase margin, matching of bias currents between the M1 and M3 transistors and thermal noise. These factors are discussed below.

2.1. Frequency Response and Internal Parasitic Pole

Using the gain-enhancement technique increases the impedance of the internal node at the gate of the diode-connected M

3. The total parasitic capacitance at this node is represented by

CP in

Figure 1d. The parasitic non-dominant pole due to the impedance 1/

gm3 of the transistor M

3 operating in the sub-threshold regime and the parasitic capacitor

CP can be expressed as:

where

CP is approximately

Cgs3 +

Cgs4. To maintain a reasonably safe phase margin, the

Pnd has to be placed more than three-times the unity GBW given by Equation (2). Thus, the following criteria for

α can be derived with respect to

CP/

CL and

k:

Recalling (1/

α − 0.5) in Equation (6) as the gain-enhancement factor, Equation (8) represents the maximum gain-enhancement that can be achieved by the proposed technique. The larger the

CL/

CP, the greater is the gain enhancement and the phase margin, but this costs more power. The dominant pole in this design is set by

CL, which can be expressed by:

2.2. Bias Current Matching

As described earlier, the ratio of the bias currents of transistors M3 and M2, defined as α = ID3/ID2, plays an important role for enhancing the amplifier gain given by Equation (6). Practically, the matching between ID3 = α ID2 and ID1 = (1 − α) ID2 determines the real α factor and, thus, the gain enhancement. To ensure good matching between those currents, the gate bias voltages of M1–M2 both are generated from the same reference current source using current mirrors. For good matching, transistors should be sized properly.

2.3. Thermal Noise

A drawback of the gain-enhanced, inverter-based amplifier, as compared to the basic CMOS inverter, is that it exhibits more input-referred thermal noise, related to the

gm3 of the device M

3. Since the correlated double-sampling (CDS) technique, as an auto-zeroing technique, is used in the corresponding integrator, the low frequency flicker noise is attenuated at the cost of an increased white noise floor due to the noise folding accompanied by the sampling [

16]. The foldover thermal noise of the integrator is the dominant source of the noise, in which the thermal noise is amplified by a factor GBW/

fS, with sampling frequency

fS [

16]. As a result, the input-referred noise power of the Class-C inverter and the gain-enhanced inverter shown in

Figure 1c, denoted by

GE-

inv, can be expressed, respectively, as:

where the noise of the gain-enhanced amplifier has an additional term corresponding to

gm3. Therefore, M

3 has to be sized carefully, such that the thermal noise is minimized and the non-dominant pole,

i.e.,

gm3/2π

CP with

CP the parasitic capacitance at the gate of M

3 and M

4, is placed more than 3× the GBW for a reasonably safe phase margin.

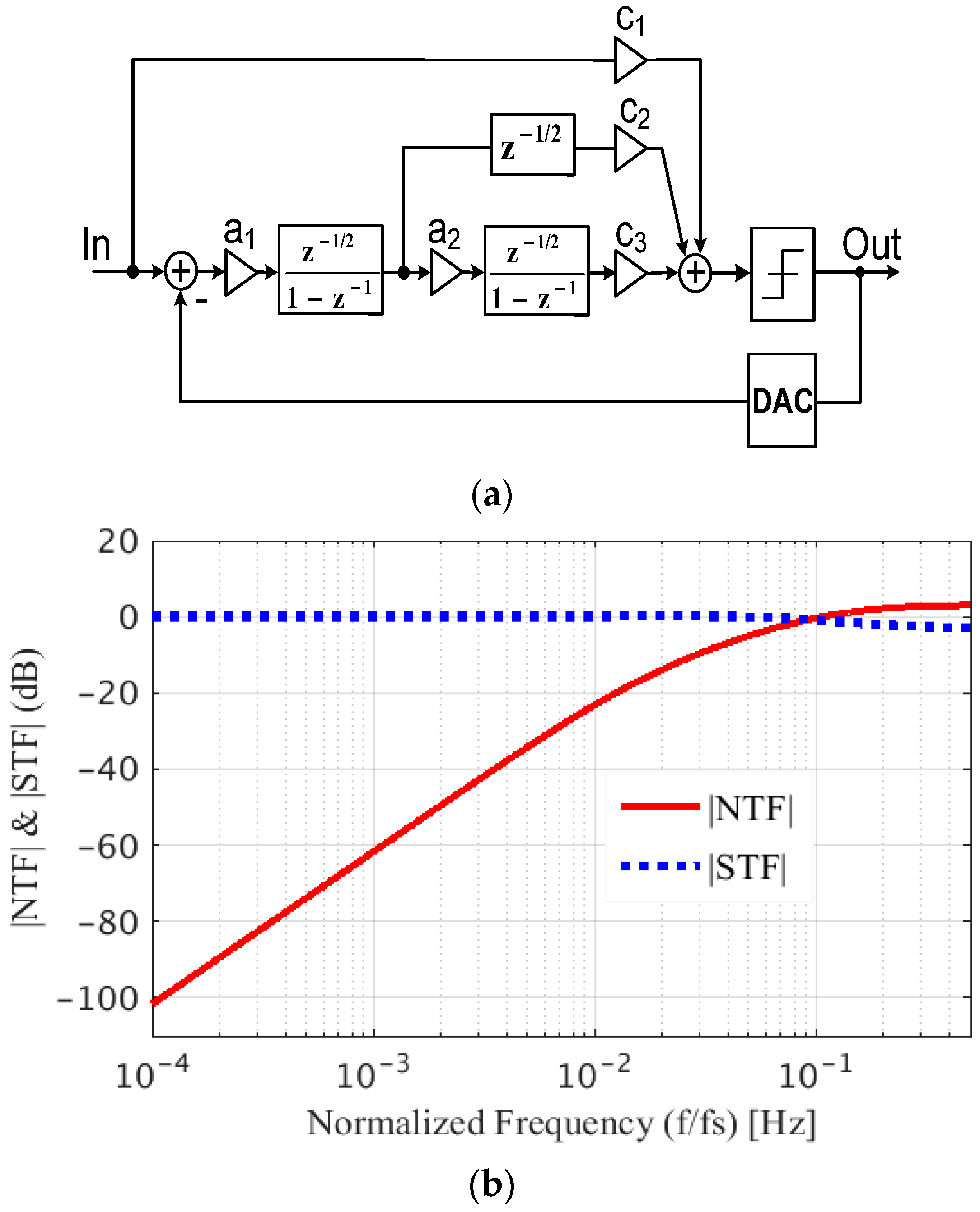

3. Modulator Architecture

Output swing is of great importance in ultra-low-voltage low-power designs, which directly determines the modulator dynamic range (DR) and, ultimately, the power consumption. The minimum swing

Vswing that the amplifier shown in

Figure 1c can still operate with imposes a hard limit equal to 2

Vsat +

Vswing for the supply voltage scaling, with saturation voltage

Vsat. The limited voltage swing is therefore translated into the demanding requirement of a low-swing loop topology. Compared to the traditional feedback topology, the full input-feedforward architecture suggests the integrators to process only the quantization error, thereby reducing the integrators’ swing considerably [

17]. This is beneficial for the amplifiers’ relaxed requirements for slew-rate.

Figure 3a shows the input-feedforward loop architecture for a second-order modulator. Half-cycle delay integrators are adopted in this structure to realize the CDS scheme for the inverter’s offset cancellation. The loop coefficients were optimized with behavioral simulations as (

a1 a2 c1 c2 c3) = (0.1 0.6 1 7 1). The coefficients are determined from the loop stability constraint, the maximum linear swing of the integrators and the required SNR.

Figure 3b depicts the magnitude of the signal transfer function (STF) and the noise transfer function (NTF) of the target modulator. As expected, the STF is unity, and the NTF has a 40 dB/dec noise suppression in the baseband.

The single-bit quantizer is inherently linear. A multi-bit quantizer is not preferable for the low power and moderate resolution in this application, because the internal DAC becomes nonlinear, requiring dynamic element matching (DEM) or other complementary techniques for DAC linearization, which increase the hardware complexity and, thus, the total power consumption.

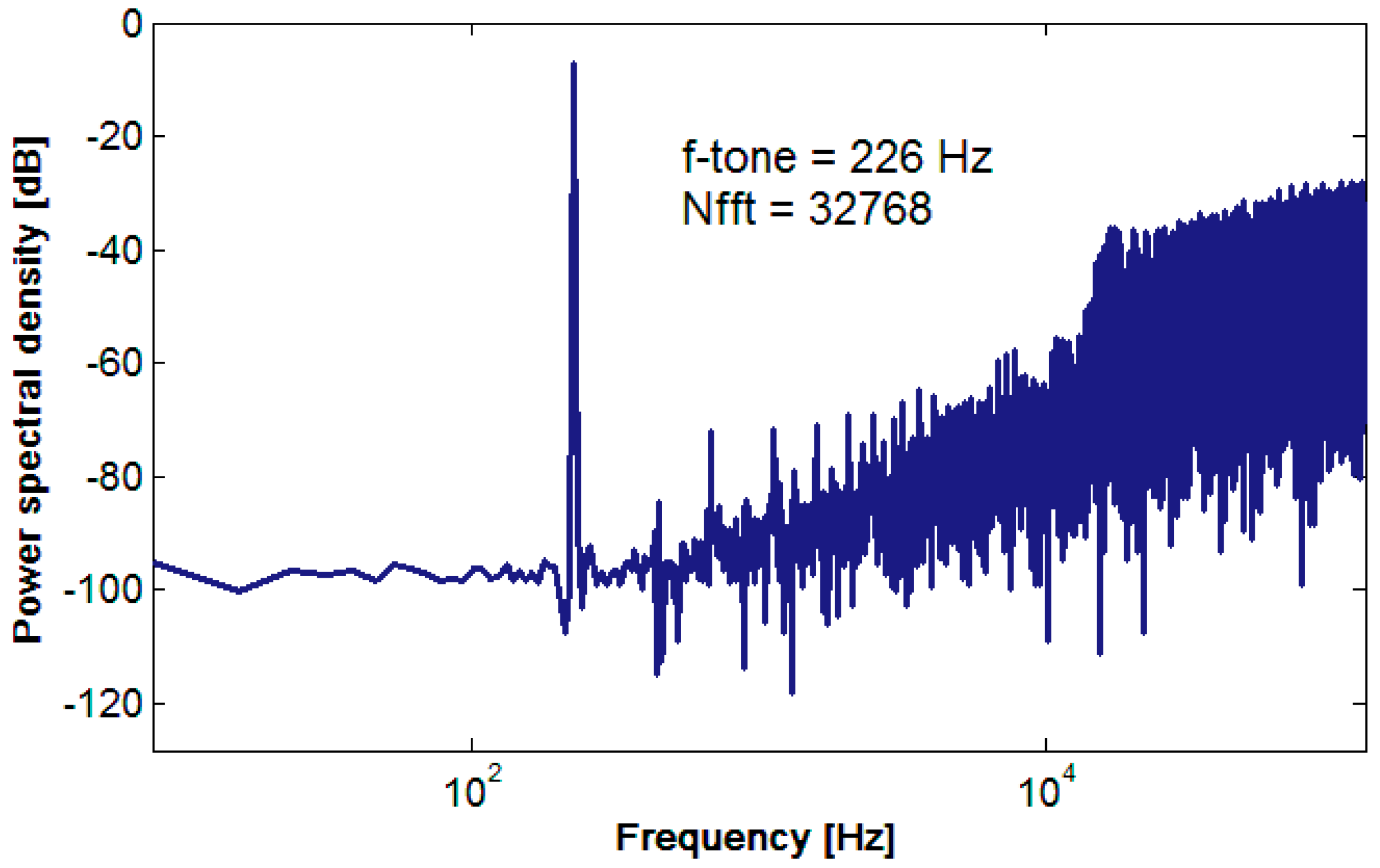

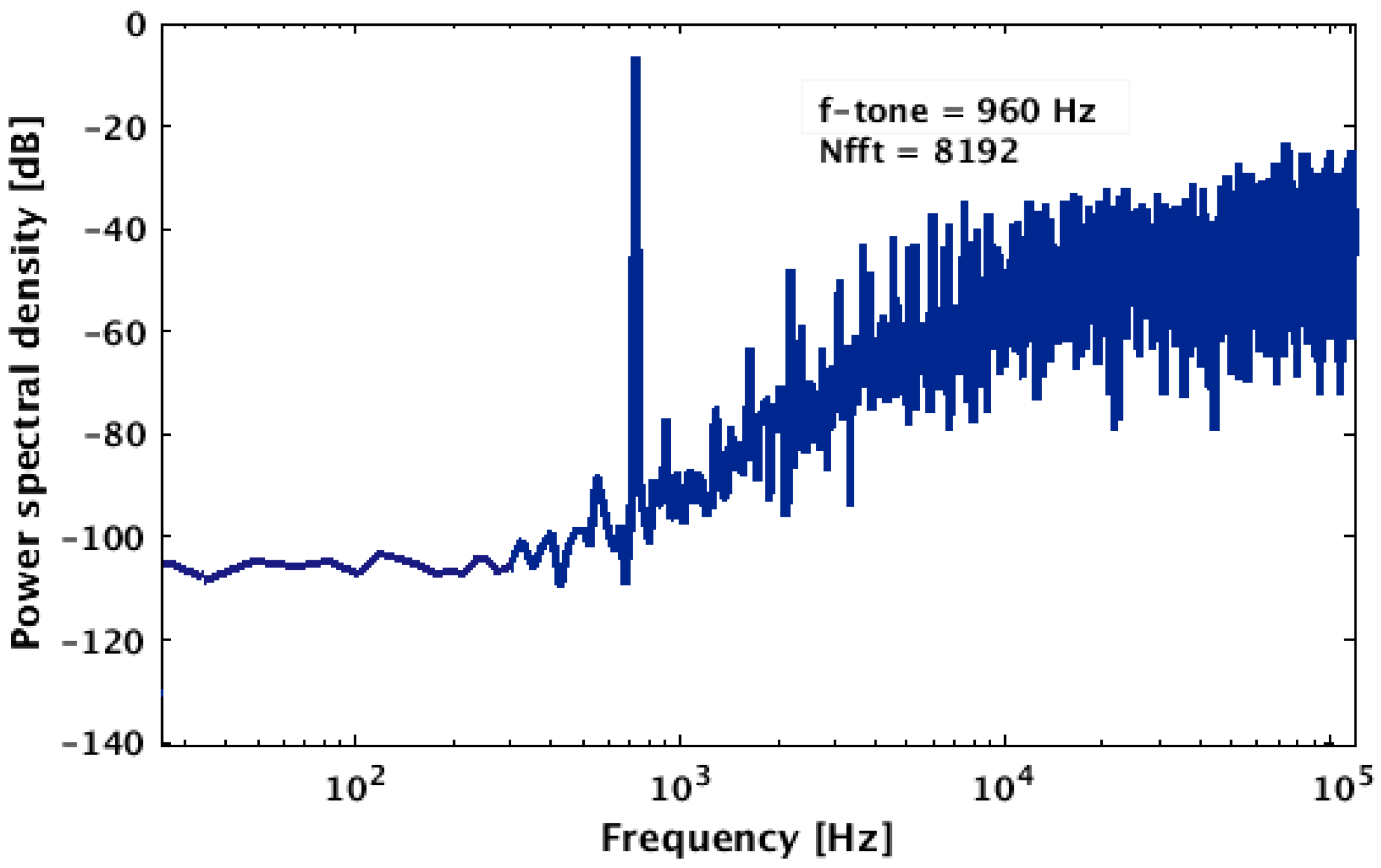

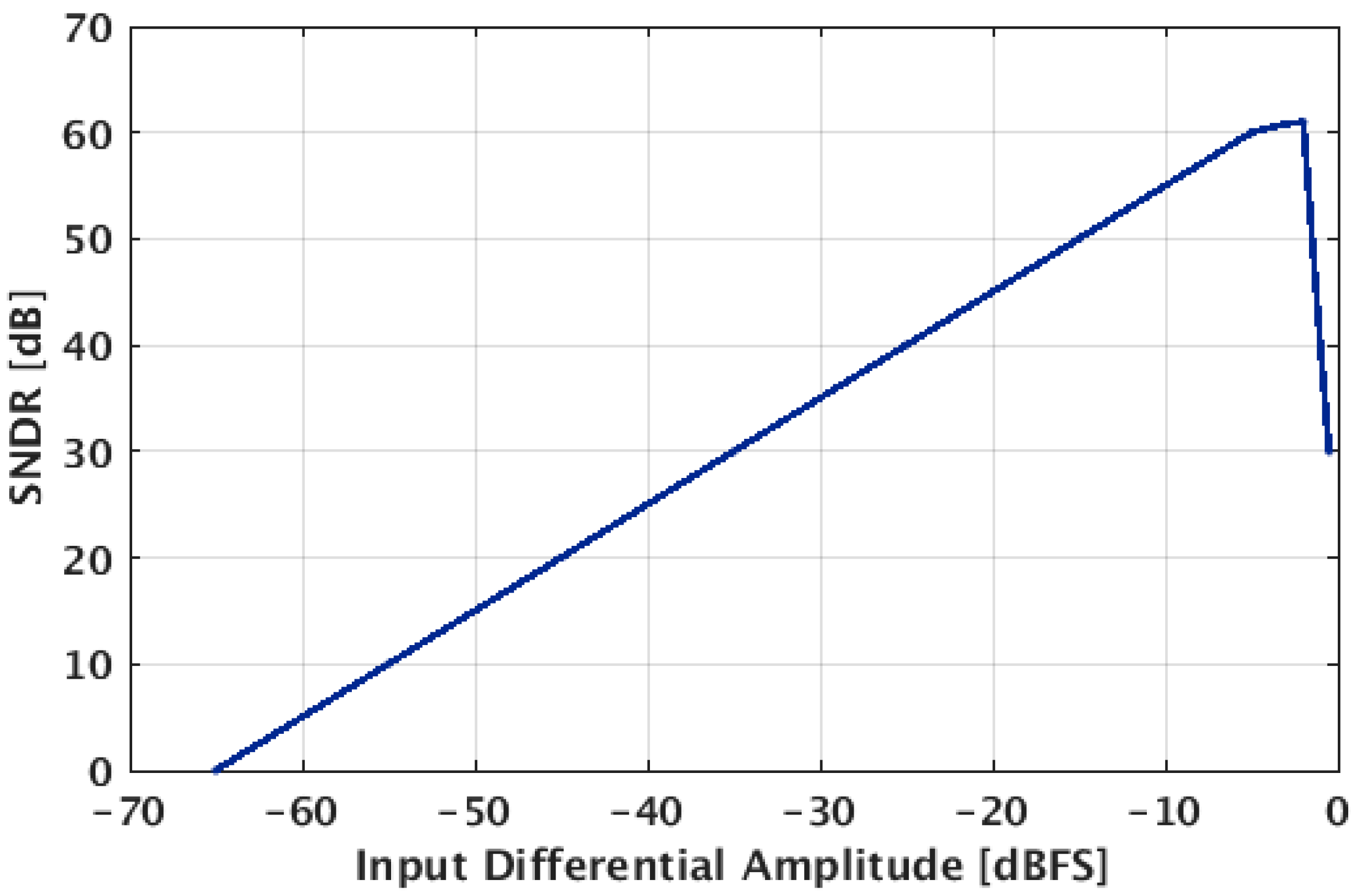

6. Comparison of the Power Efficiency

The performance of the presented modulator in

Section 4 and

Section 5 is compared to previous state-of-the-art low-voltage modulators in

Table 4. Two commonly-used FOMs are employed, which are defined below:

The FOM

1 favors high-resolution ADCs, whereas the FOM

2 favors high-DR ADCs. These FOM definitions disregard

VDD, the threshold voltage of the corresponding technology, and the available swing. According to the FOM definitions given above, the designed inverter-based, second-order modulator achieves 0.46 pJ/conversion-step and 156 dB, respectively, which are comparable to the other state-of-the-art modulators operating with supply voltages below 0.4 V. Among others, the passive modulator in [

2] operating at a 0.5 V supply consumes the lowest power (only 250 nW) while gaining moderate resolution (65 dB SNDR) and 72 dB DR. It looks attractive when using both FOM definitions given by Equations (12) and (13).

The modulator design in the ultra-low voltage domain (below 0.5 V) is becoming more and more challenging due to the limited available signal swing and switch overdrive voltage. The output swing of an OTA directly determines the integrators’ swing, which indeed defines the modulator reference voltage. As a consequence, the maximum input signal,

Vin.max, that determines the DR of the ADC at a given input-referred noise floor

Pn is limited by the reference voltage or the integrators’ swing. The DR can be derived as:

where

PD is the input-referred distortion. To maintain the same DR in lower supply voltages, the noise floor and distortion power have to be decreased, requiring higher power consumption [

21]. Generally speaking, for a better power efficiency, it is not desirable to reduce the supply voltage, because the analog power increases. However, specific applications, such as body implants (e.g., cardiac pacemakers, cochlear implants,

etc.), demand ultra-low-voltage operation in the order of human body potentials.

It should be noted that the threshold voltage does not scale at the same proportion as the supply voltage, which limits the available overdrive voltage of the operating switches in SC designs. For fair comparisons of the modulators listed in

Table 4, in addition to the commonly-used FOM

1 and FOM

2, the proposed FOM

3 takes into account the

VDD, as well.

In fact, the most effective comparison among different modulators is when we consider the threshold voltage in addition to the supply voltage,

VDD, because the available voltage headroom for analog blocks and the overdrive voltage for the switching transistors (

i.e.,

VGS −

VTH) depend directly on

VTH. Therefore, for a fair comparison, we need to consider the term

VDD −

VTH in the numerator of the FOM

3 given by Equation (15), rather than merely

VDD. For simplicity, we assume all technologies used in

Table 4 have the same

VTH. According to FOM

3 and considering operating

VDD, the proposed modulator achieves a competitive figure of merit of 0.139 pJ.V/conversion-step.