All-Digital Time-Domain CMOS Smart Temperature Sensor with On-Chip Linearity Enhancement

Abstract

:1. Introduction

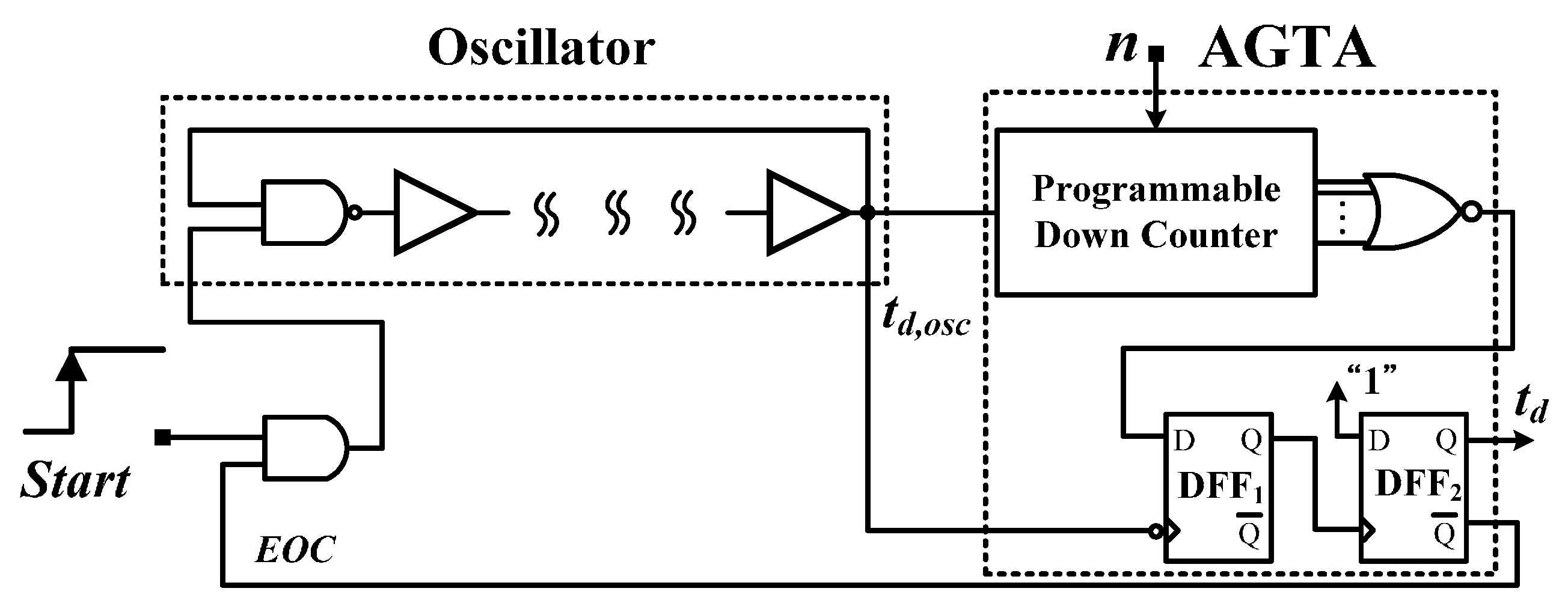

2. Circuit Description

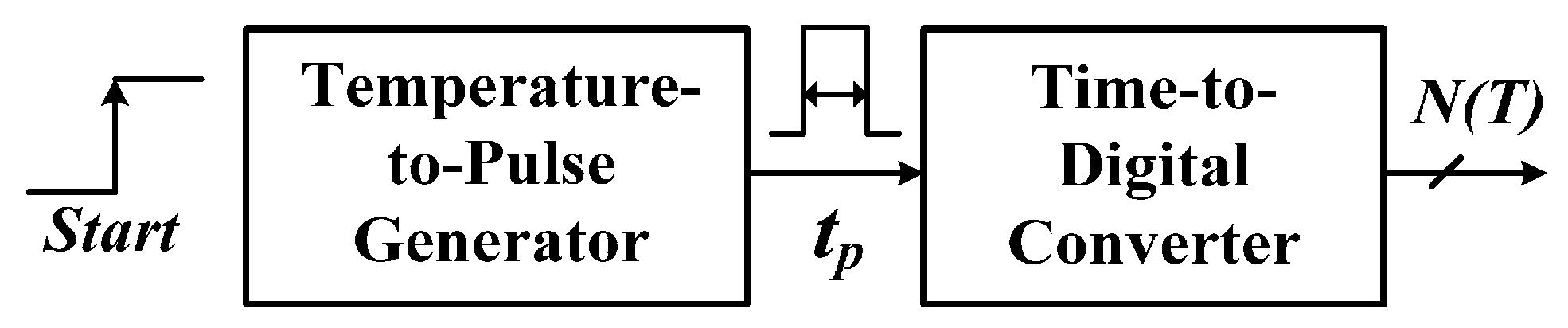

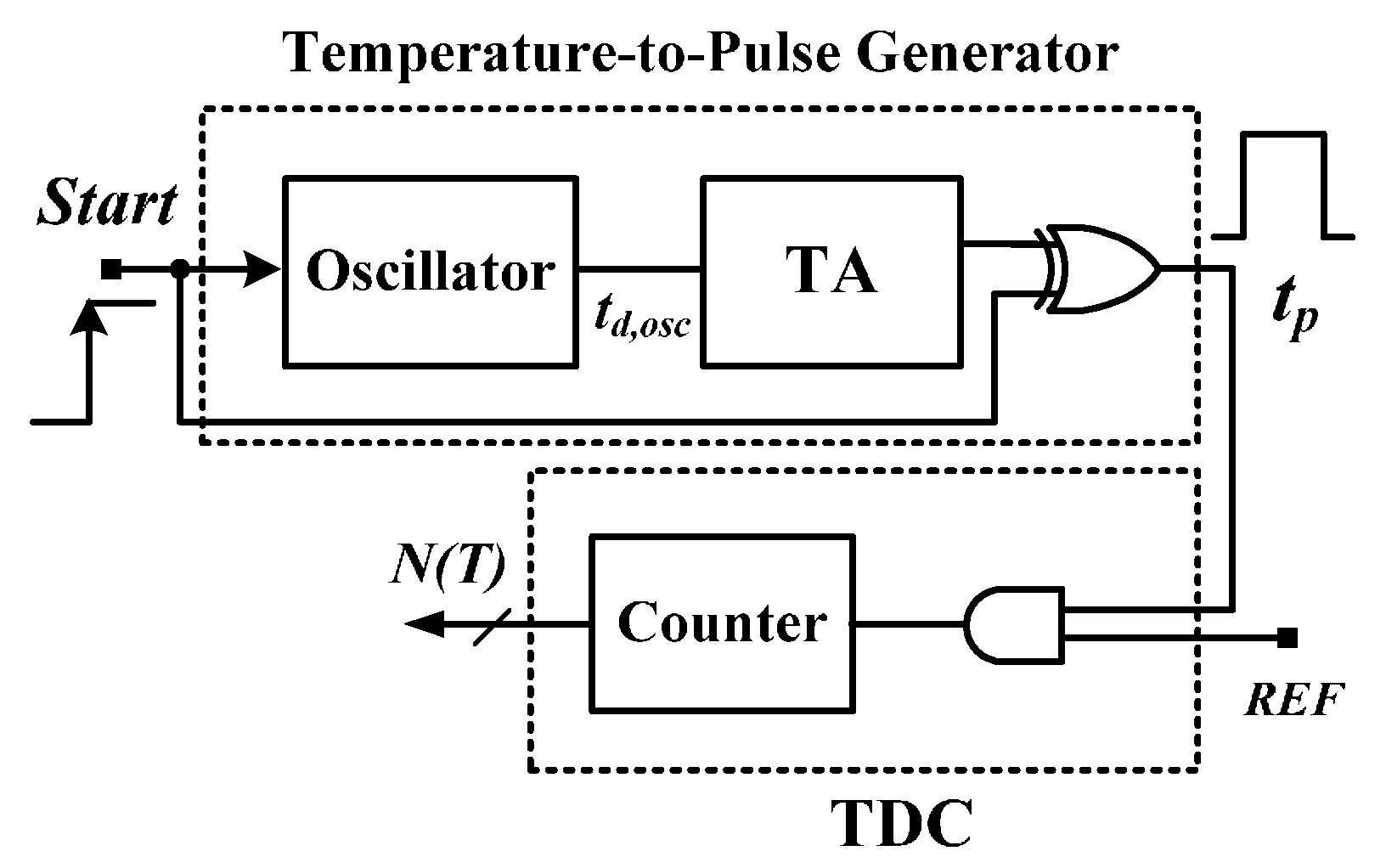

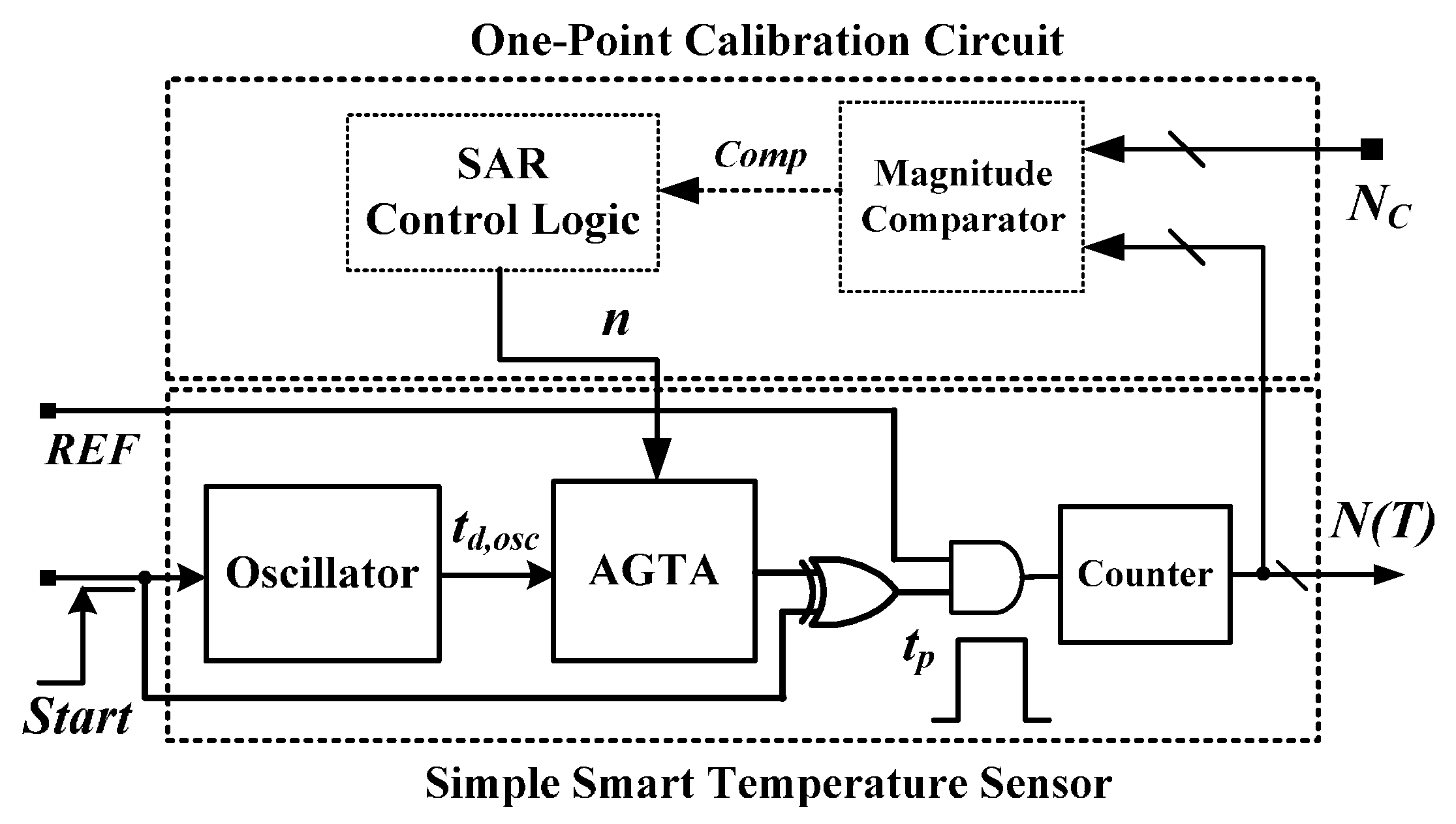

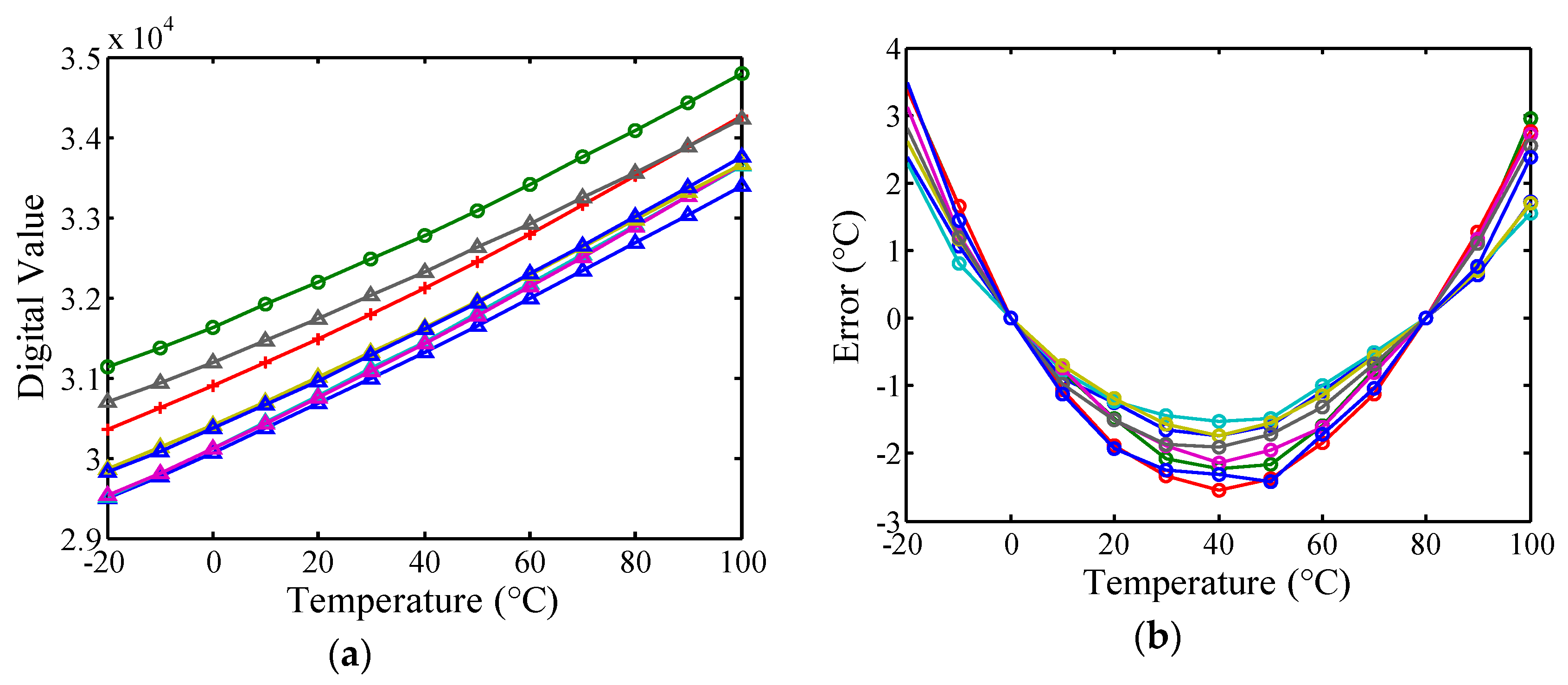

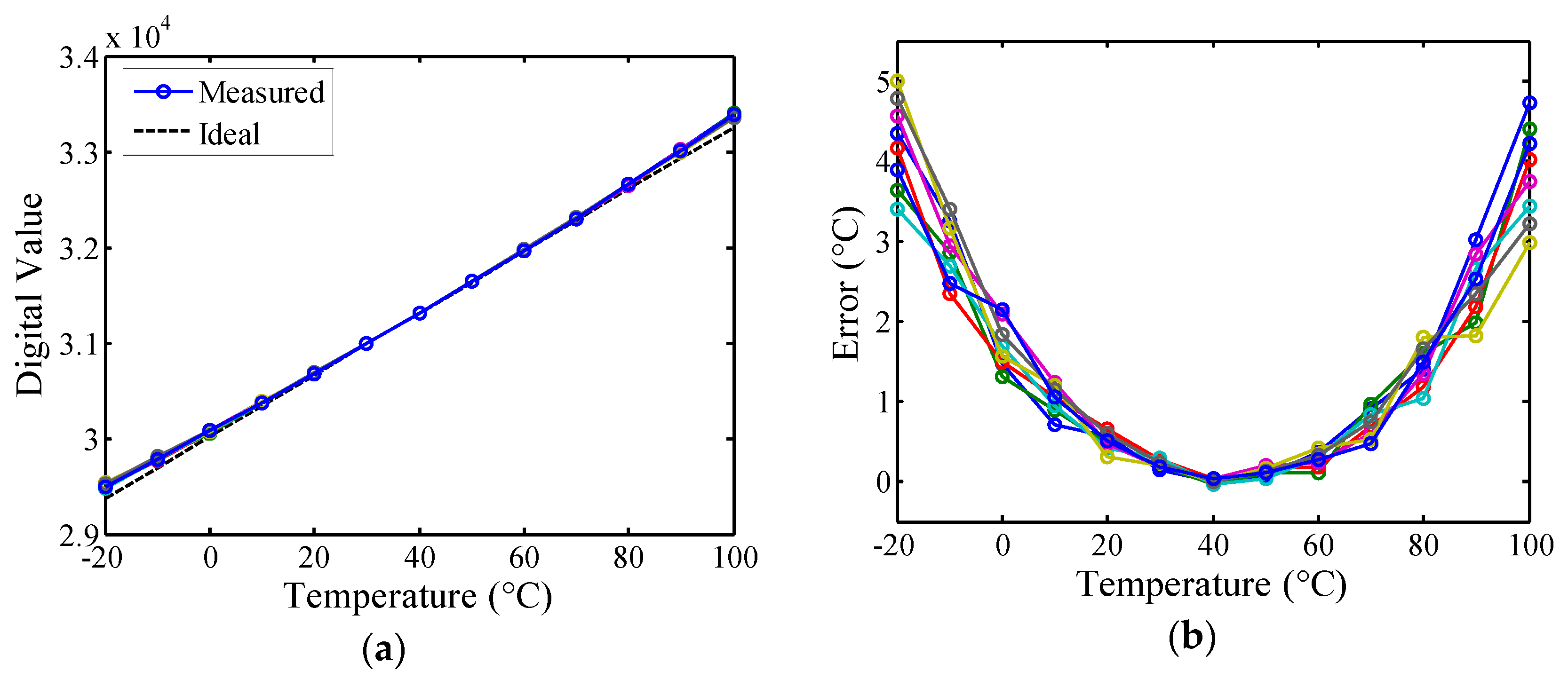

2.1. Inverter-Based Smart Temperature Sensor and One-Point Calibration Technique

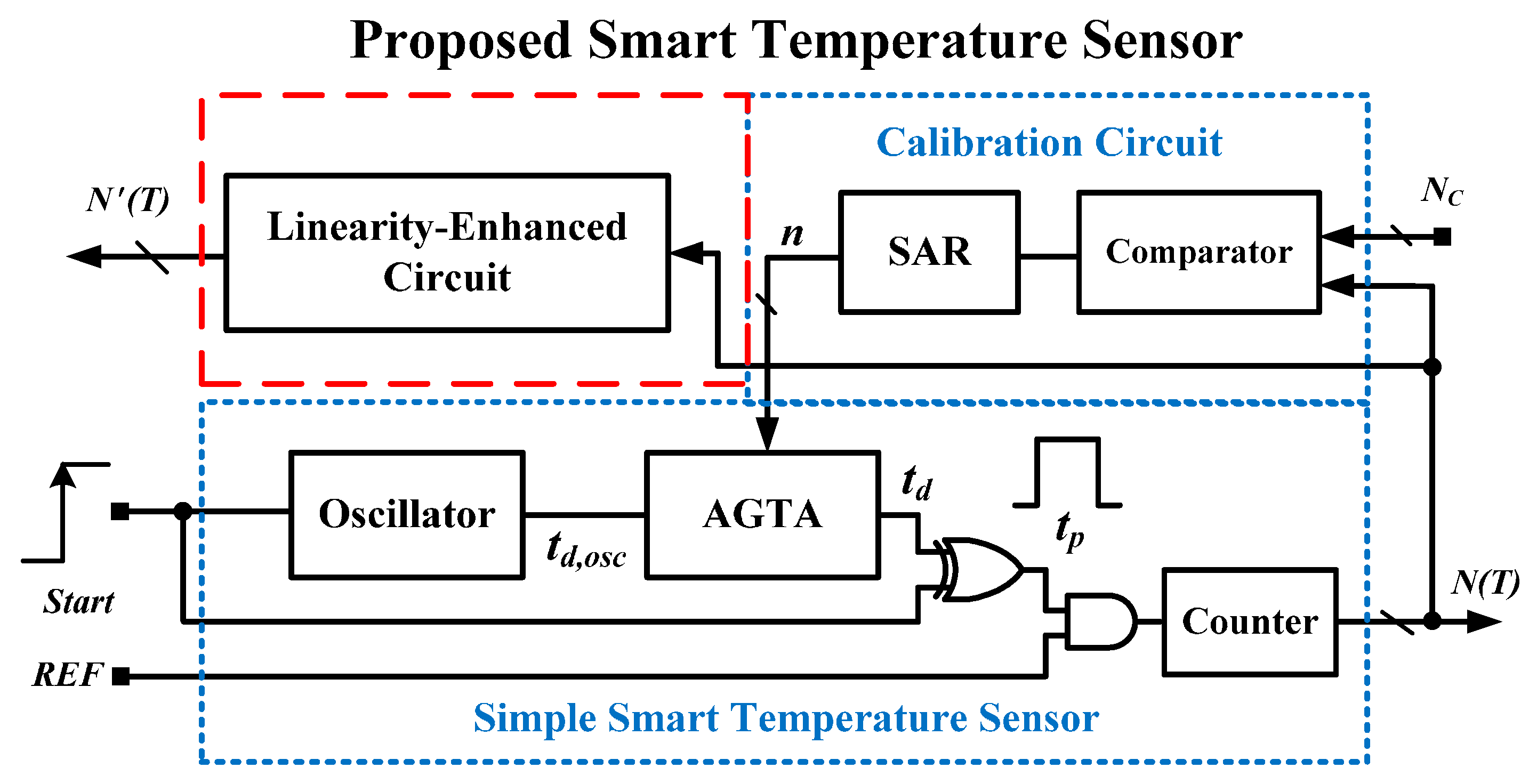

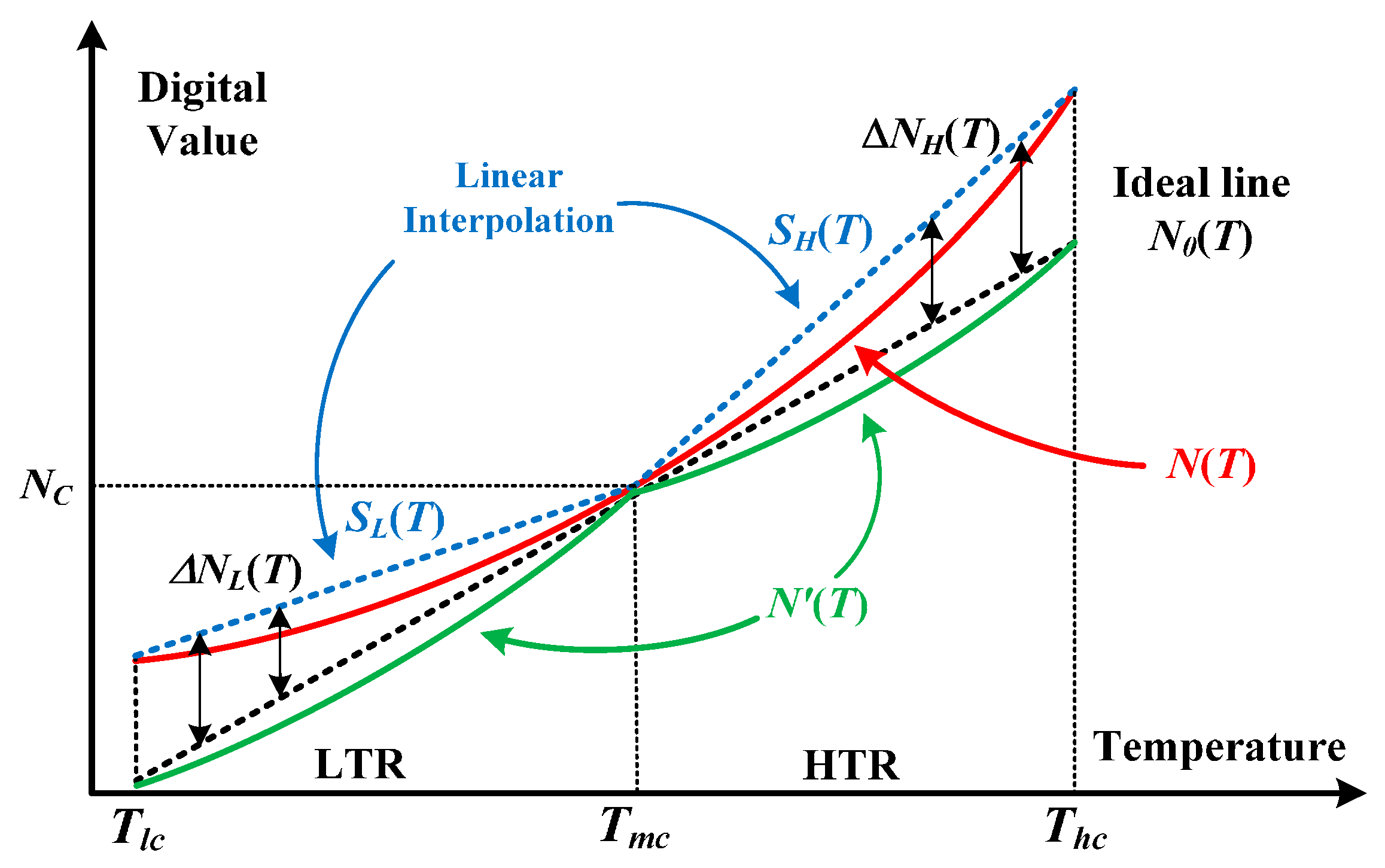

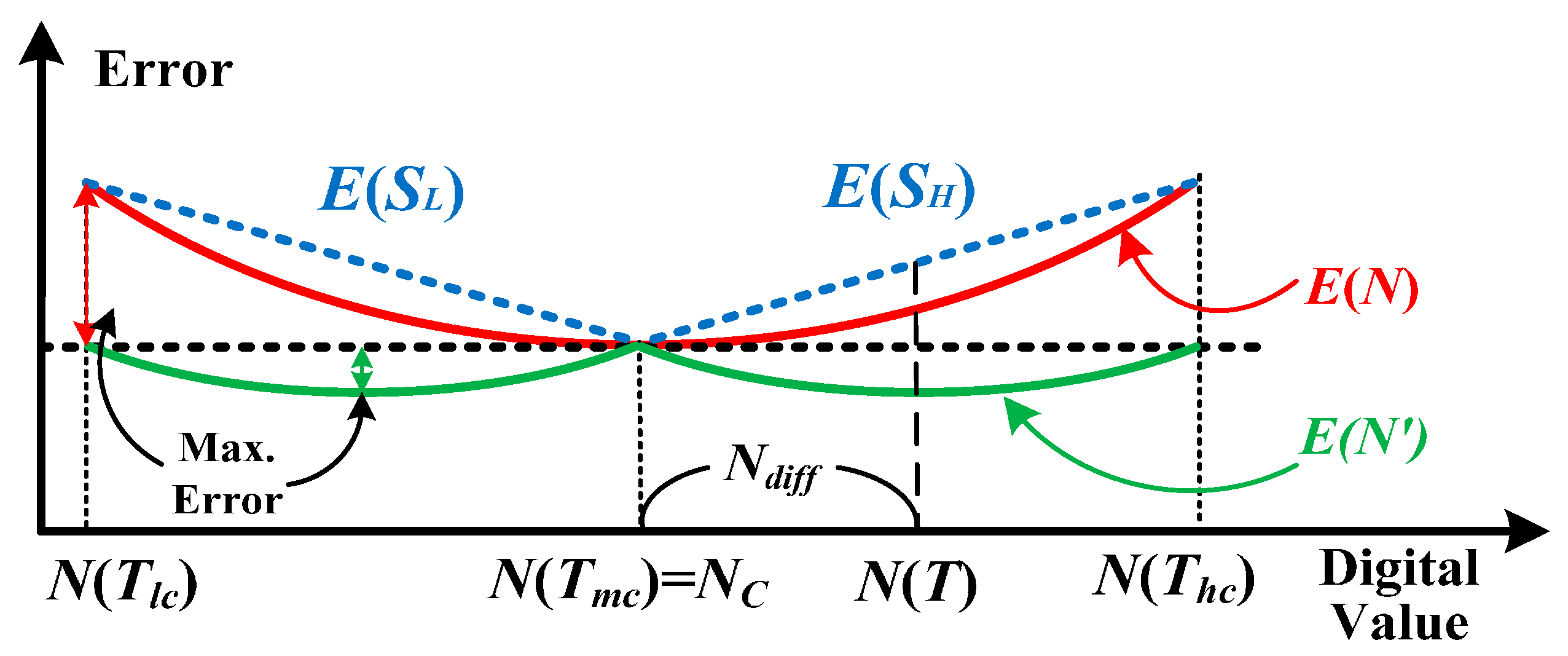

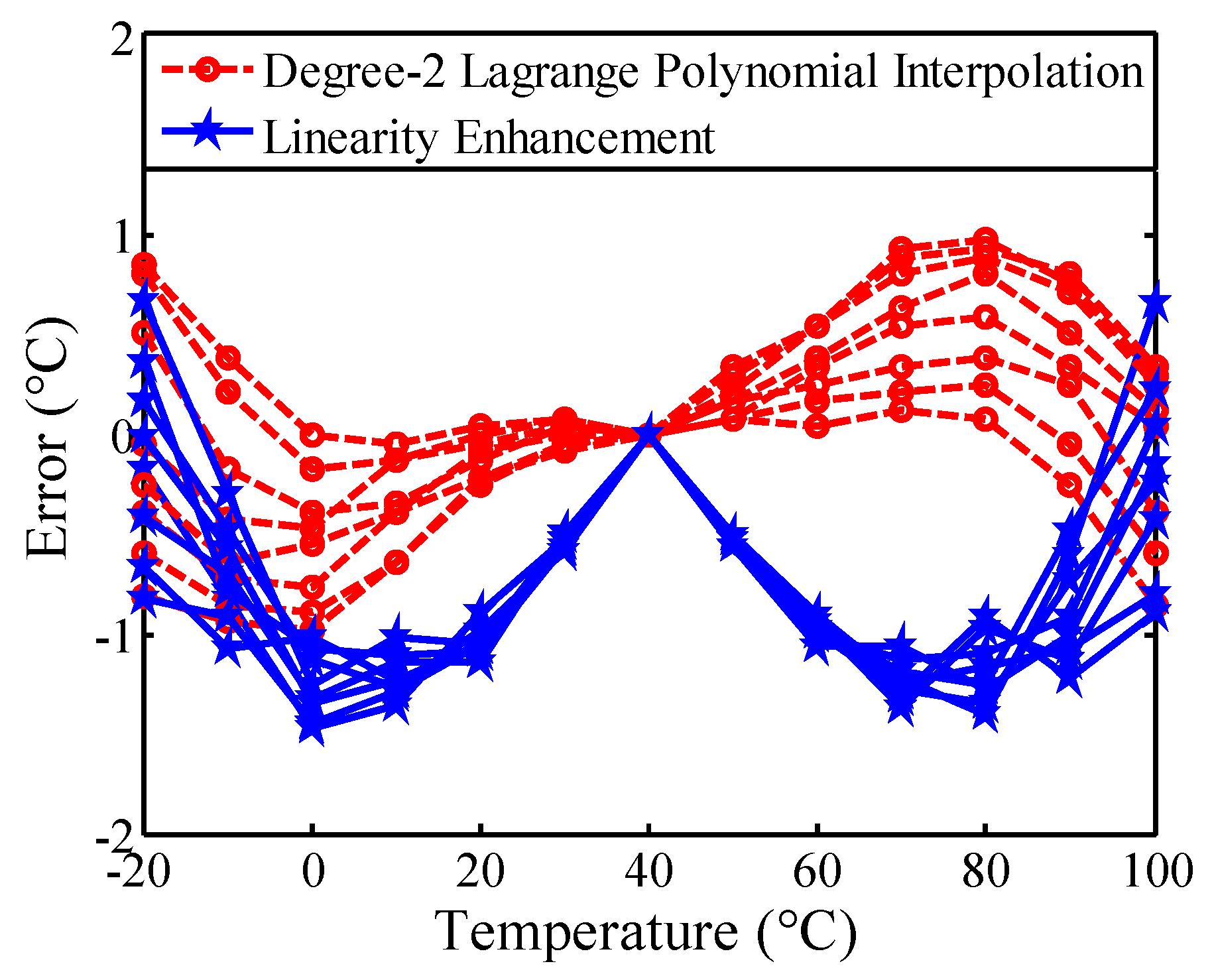

2.2. Proposed All-Digital On-Chip Linearity Enhancement Technique

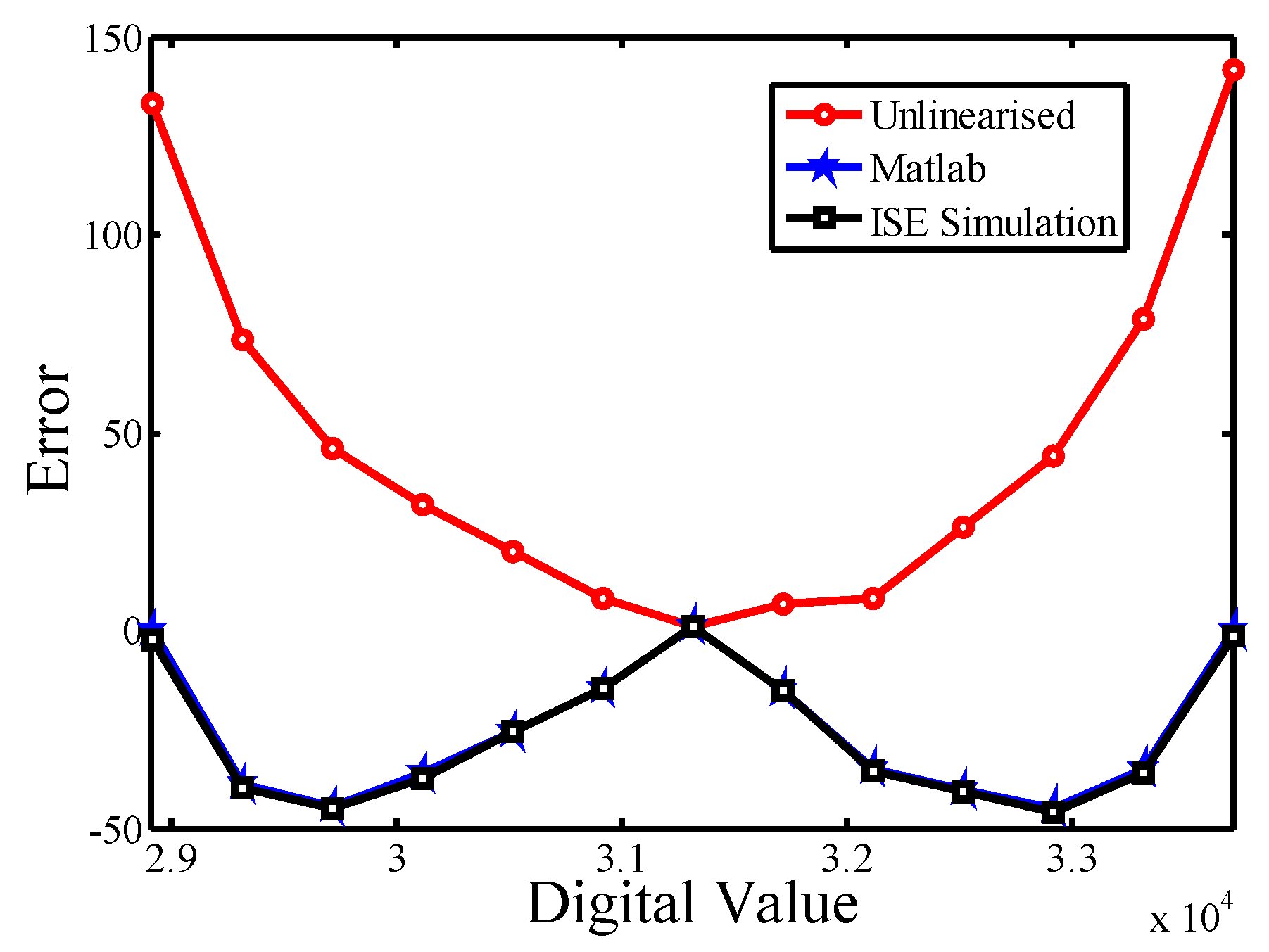

3. Experimental Results

| Sensor | Resolution (°C) | Error (°C) | Calibration | Area (Slices) | Range (°C) | Technology (µm) |

|---|---|---|---|---|---|---|

| Simple | 0.028 ~ 0.033 | −2.5 ~ 3.5 | Two-point | 50 | −20 ~ 100 | 0.09 |

| Calibrated (Unlinearized) | 0.03 | 0 ~ 5 | One-point | 75 | −20 ~ 100 | 0.09 |

| Linearized | 0.03 | −1.6 ~ 0.9 | One-point | 118 | −20 ~ 100 | 0.09 |

4. Conclusions

| Sensor | Type | Resolution (°C) | Error (°C) | Calibration | Power Consumption (µW) | Area (mm2) | Range (°C) | Technology (µm) |

|---|---|---|---|---|---|---|---|---|

| [9] | Analog | 0.12 ~ 0.16 | −0.7~0.9 | Two-point | 9 @5 Hz | 0.175 | 0~100 | 0.35 |

| [10] | Analog | 0.3 | −1.6~3.0 | Two-point | 0.22 @100 Hz | 0.05 | 0~100 | 0.18 |

| [11] | Analog | 0.3 | −0.8~1 | Two-point | 0.4 @1k Hz | 0.032 | 0~100 | 0.18 |

| [12] | Digital | 0.058 | −1.5~0.8 | Two-point | 8.4 @2 Hz | 140 LEs | 0~75 | 0.22/0.18 |

| [13] | Digital | 0.133 | −0.7~0.6 #1 | One-point | 175 @1k Hz | 48 Les #2 | 0~100 | 0.22/0.18 |

| [14] | Digital | 0.139 | −5.1~3.4 | One-point | 150 @10k Hz | 0.01 | 0~60 | 0.065 |

| [15] | Analog | 0.043 | −2.7~2.9 | One-point | 400 @366k Hz | 0.0066 | −40~110 | 0.065 |

| [16] | Analog | 0.18 | ±1.5 | One-point | 500 @ 465k Hz | 0.008 | 0~110 | 0.065 |

| [17] | Analog | 0.088 ~ 0.093 | −0.25~0.35 | Two-point | 36.7 @10 Hz | 0.6 | 0~90 | 0.35 |

| [18] | Analog | 0.043 ~ 0.047 | −0.2~1.2 | Two-point | 23 @10 Hz | 0.07 | −40~120 | 0.35 |

| This work | Digital | 0.03 | −1.6~0.9 | One-point | 95 @1k Hz | 118 Slices | −20~100 | 0.09 |

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Duarte, D.E.; Geannopoulos, G.; Mughal, U.; Wong, K.L.; Taylor, G. Temperature Sensor Design in a High Volume Manufacturing 65 nm CMOS Digital Process. In Proceedings of the 2007 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 16–19 September 2007; pp. 221–224.

- Lakdawala, H.; Li, Y.W.; Raychowdhury, A.; Taylor, G.; Soumyanath, K. A 1.05 V 1.6 mW 0.45 °C 3σ Resolution ΣΔ Based Temperature Sensor with Parasitic-Resistance Compensation in 32 nm Digital CMOS Process. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 340–341.

- Shor, J.S.; Luria, K. Miniaturized BJT-Based Thermal Sensor for Microprocessors in 32- and 22-nm Technologies. IEEE J. Solid State Circuits 2013, 48, 2860–2867. [Google Scholar] [CrossRef]

- Krummenacher, P.; Oguey, H. Smart Temperature Sensor in CMOS technology. Sens. Actuators A Phys. 1990, 22, 636–638. [Google Scholar] [CrossRef]

- Meijer, G.C.M.; Wang, G.; Fruett, F. Temperature Sensors and Voltage References Implemented in CMOS Technology. IEEE Sens. J. 2001, 1, 225–234. [Google Scholar] [CrossRef]

- Pertijs, M.A.P.; Makinwa, K.A.A.; Huijsing, J.H. A CMOS Smart Temperature Sensor with a 3σ Inaccuracy of ±0.1 °C from −55 °C to 125 °C. IEEE J. Solid State Circuits 2005, 40, 2805–2815. [Google Scholar] [CrossRef]

- Lin, C.-W.; Lin, S.-F. A linear CMOS Temperature Sensor with an Inaccuracy of ±0.15 °C. IEICE Electron. Expr. 2012, 9, 1556–1561. [Google Scholar] [CrossRef]

- Sebastiano, F.; Breems, L.J.; Makinwa, K.A.A.; Drago, S.; Leenaerts, D.M.W.; Nauta, B. A 1.2-V 10-μW NPN-Based Temperature Sensor in 65-nm CMOS with an Inaccuracy of 0.2 °C (3σ) from −70 °C to 125 °C. IEEE J. Solid State Circuits 2010, 45, 2591–2601. [Google Scholar] [CrossRef]

- Chen, P.; Chen, C.-C.; Lu, W-.F.; Tsai, C-.C. A Time-to-Digital-Converter-Based CMOS Smart Temperature Sensor. IEEE J. Solid State Circuits 2005, 40, 1642–1648. [Google Scholar] [CrossRef]

- Lin, Y.-S.; Sylvester, D.; Blaauw, D. An Ultra Low Power 1 V, 220 nW Temperature Sensor for Passive Wireless Applications. In Proceedings of the 2008 IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 21–24 September 2008; pp. 507–510.

- Law, M.K.; Bermak, A. A 405-nW CMOS Temperature Sensor Based on Linear MOS Operation. IEEE Trans. Circuit Syst. II 2009, 56, 891–895. [Google Scholar] [CrossRef]

- Chen, P.; Shie, M.-C.; Zheng, Z.-Y.; Zheng, Z.-F.; Chu, C.-Y. A fully Digital Time-Domain Smart Temperature Sensor Realized with 140 FPGA Logic Elements. IEEE Trans. Circuit Syst. I 2007, 54, 2661–2668. [Google Scholar]

- Chen, P.; Chen, S.-C.; Shen, Y.-S.; Peng, Y.-J. All-Digital Time-Domain Smart Temperature Sensor with an Inter-Batch Inaccuracy of 0.7 ~ 0.6 °C after One-Point Calibration. IEEE Trans. Circuit Syst. I 2011, 58, 913–920. [Google Scholar] [CrossRef]

- Chung, C.-C.; Yang, C.-R. An Autocalibrated All-Digital Temperature Sensor for On-Chip Thermal Monitoring. IEEE Trans. Circuit Syst. II 2011, 58, 105–109. [Google Scholar] [CrossRef]

- Kim, K.; Lee, H.; Kim, C. 366-Ks/s 1.09-nJ 0.0013-mm2 Frequency-to-Digital Converter Based CMOS Temperature Sensor Utilizing Multiphase Clock. IEEE Trans. VLSI Syst. 2013, 21, 1950–1954. [Google Scholar] [CrossRef]

- Hwang, S.; Koo, J.; Kim, K.; Lee, H.; Kim, C. A 0.008 mm2 500 μW 469 kS/s frequency-to-digital converter based CMOS Temperature Sensor with Process Variation Compensation. IEEE Trans. Circuit Syst. I 2013, 60, 2241–2248. [Google Scholar] [CrossRef]

- Chen, P.; Chen, C.-C.; Peng, Y.-H.; Wang, K.-M.; Wang, Y.-S. A Time-Domain SAR Smart Temperature Sensor with Curvature Compensation and a 3σ Inaccuracy of −0.4 °C ~ + 0.6 °C over a 0 °C to 90 °C Range. IEEE J. Solid State Circuits 2010, 45, 600–609. [Google Scholar] [CrossRef]

- Chen, C.-C.; Chen, H.-W. A Linearization Time-Domain CMOS Smart Temperature Sensor Using a Curvature Compensation Oscillator. Sensors 2013, 13, 11439–11452. [Google Scholar] [CrossRef] [PubMed]

- Chen, C.-C.; Chen, C.-L.; Lin, Y. All-Digital Linearity-Enhanced Technique for Time-Domain Temperature Sensors. Procedia Eng. 2014, 87, 1247–1250. [Google Scholar]

- Demassa, T.A.; Ciccone, Z. Digital Integrated Circuits; John Wiley & Sons, Inc.: New York, NY, USA, 1996. [Google Scholar]

- Filanovsky, I.M.; Allam, A. Mutual Compensation of Mobility and Threshold Voltage Temperature Effects with Applications in CMOS Circuits. IEEE Trans. Circuits Syst. I 2001, 48, 876–884. [Google Scholar] [CrossRef]

- Hazewinkel, M. Lagrange Interpolation Formula; Encyclopedia of Mathematics; Springer: Berlin, Germany, 2001. [Google Scholar]

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, C.-C.; Chen, C.-L.; Lin, Y. All-Digital Time-Domain CMOS Smart Temperature Sensor with On-Chip Linearity Enhancement. Sensors 2016, 16, 176. https://doi.org/10.3390/s16020176

Chen C-C, Chen C-L, Lin Y. All-Digital Time-Domain CMOS Smart Temperature Sensor with On-Chip Linearity Enhancement. Sensors. 2016; 16(2):176. https://doi.org/10.3390/s16020176

Chicago/Turabian StyleChen, Chun-Chi, Chao-Lieh Chen, and Yi Lin. 2016. "All-Digital Time-Domain CMOS Smart Temperature Sensor with On-Chip Linearity Enhancement" Sensors 16, no. 2: 176. https://doi.org/10.3390/s16020176

APA StyleChen, C.-C., Chen, C.-L., & Lin, Y. (2016). All-Digital Time-Domain CMOS Smart Temperature Sensor with On-Chip Linearity Enhancement. Sensors, 16(2), 176. https://doi.org/10.3390/s16020176