1. Introduction

Recently, human-computer interface applications have gained significant attention. Many major global companies have developed various individualized bio-signal measuring applications. Biopotential detection devices enable continuous monitoring of various physiological information from a user; therefore, the biopotential detection circuits can be utilized in fields like medical, entertainment, and sports fields [

1,

2]. In addition, with integrated circuit (IC) process development, researches in highly miniaturized and low power consumption biopotential detection circuits have rapidly grown.

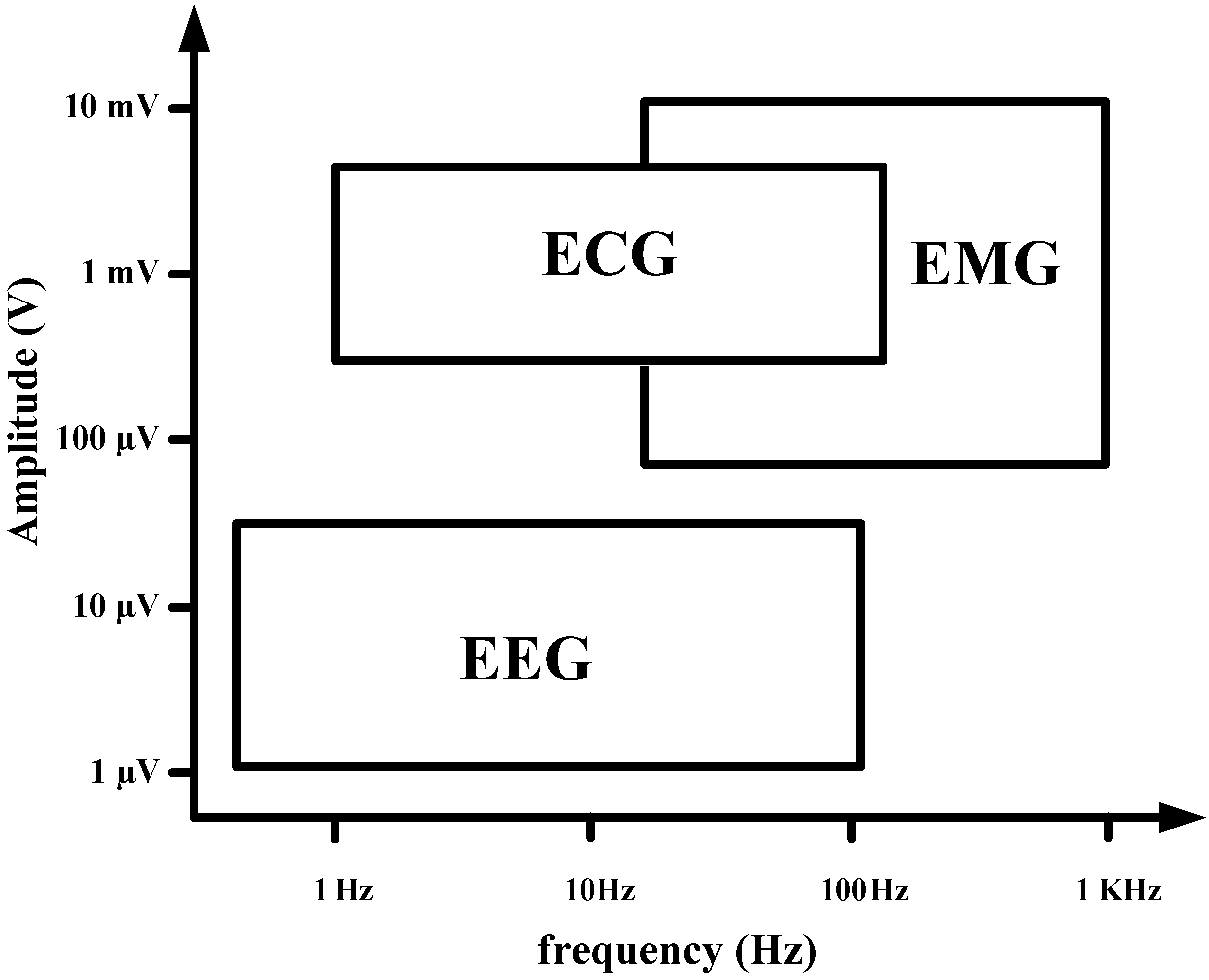

Most biopotential circuits commonly suffer from degraded performance because of the flicker noise in the bio-signal band, offset due to process variation, skin-to-electrode offset, and motion artifact signals from different body and cable motions during signal recording. In particular, biopotentials such as electroencephalogram (EEG), electrocardiogram (ECG), and electromyogram (EMG) have low-frequency (< 300 Hz) features that include flicker noise band, as shown in

Figure 1.

Figure 1.

Amplitude and frequency band of bio-signal.

Figure 1.

Amplitude and frequency band of bio-signal.

DC components are not included in most biopotential signals; thus, the biopotential detection circuit generally adopts an AC-coupled input stage. The AC-coupled input stage with first-order high-pass characteristics can be simply implemented using capacitor pairs.

To effectively attenuate the unwanted components out of the biopotential signal band, a higher order high-pass filter (HPF) with a sub-Hz cut-off frequency is required. The HPF can be realized using very large resistors of a few GΩ using MOS-bipolar devices [

3]. The sub-Hz low-frequency artifact signals such as respiration are simultaneously recorded with the bio-signal, and degrade the signal quality. A higher-order HPF is one of the effective solutions to attenuate these low frequency artifact signals. In addition, many bio-signal detection circuits were reported to overcome external offsets caused by polarization of the skin-electrode interface, and internal offsets caused by process variations [

4,

5,

6]. For a comfortable connection between circuit and body, dry electrode rather than wet electrode is used in recent biopotential measuring device. The dry electrodes, however, have much higher output impedance than wet electrodes; thus an input stage with a much higher input impedance (larger than a few GΩ) is required for a high-quality biopotential acquisition.

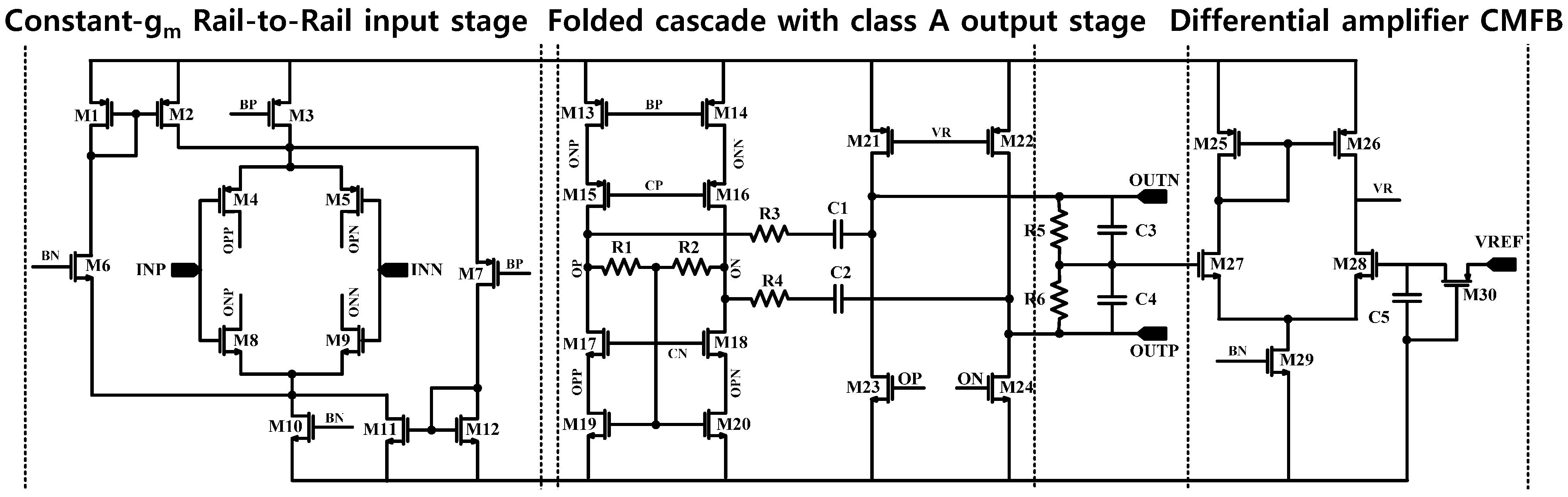

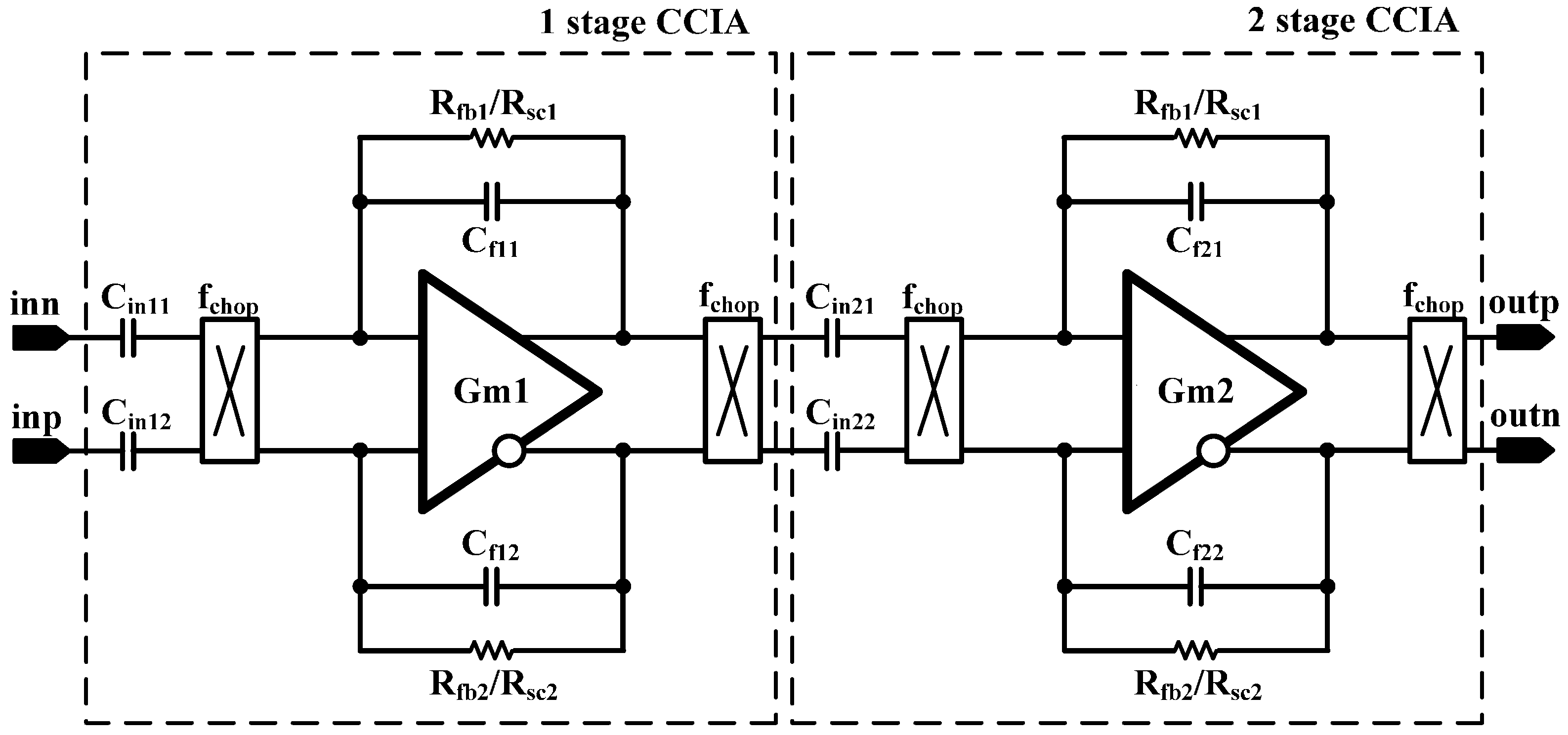

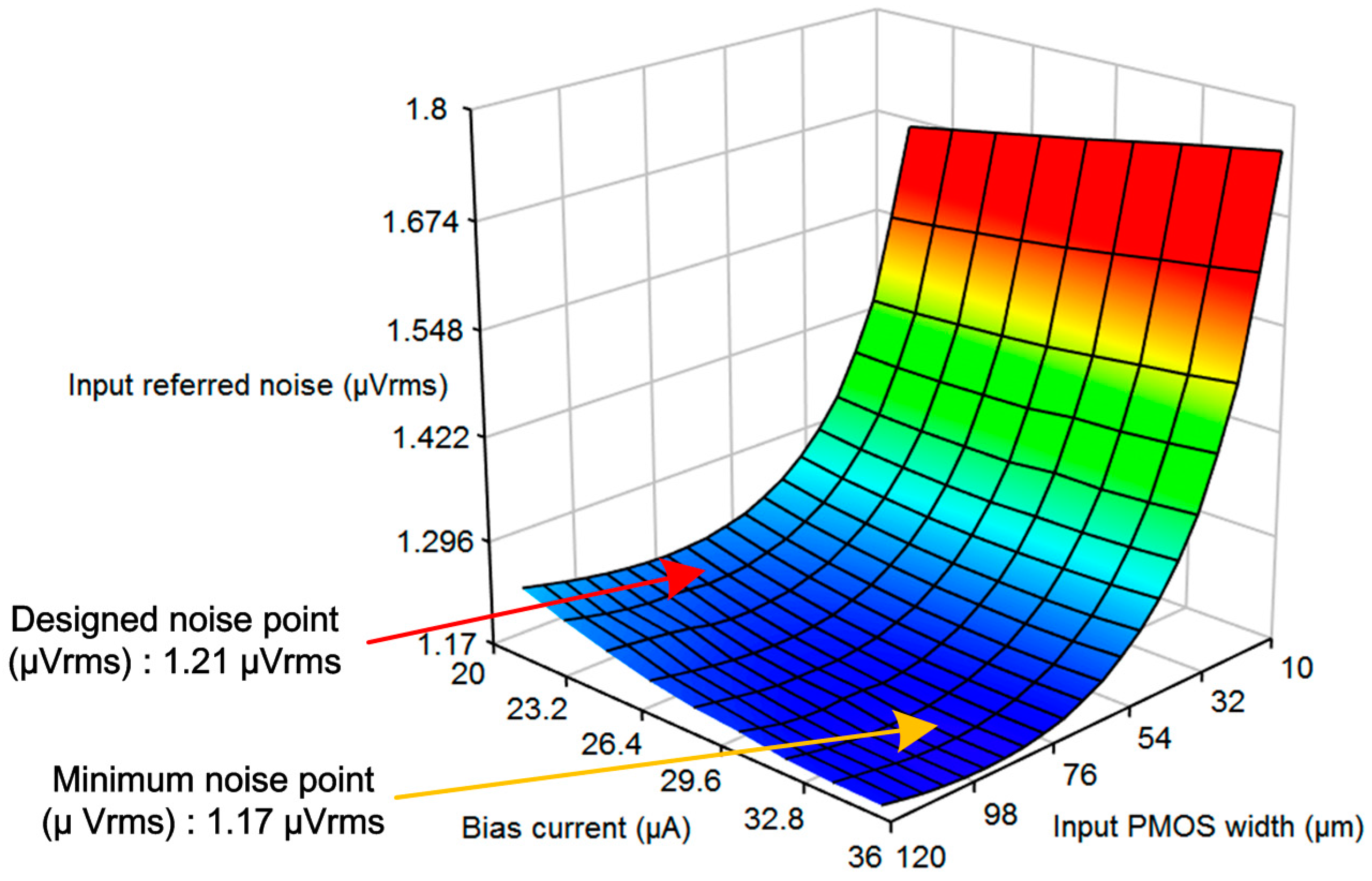

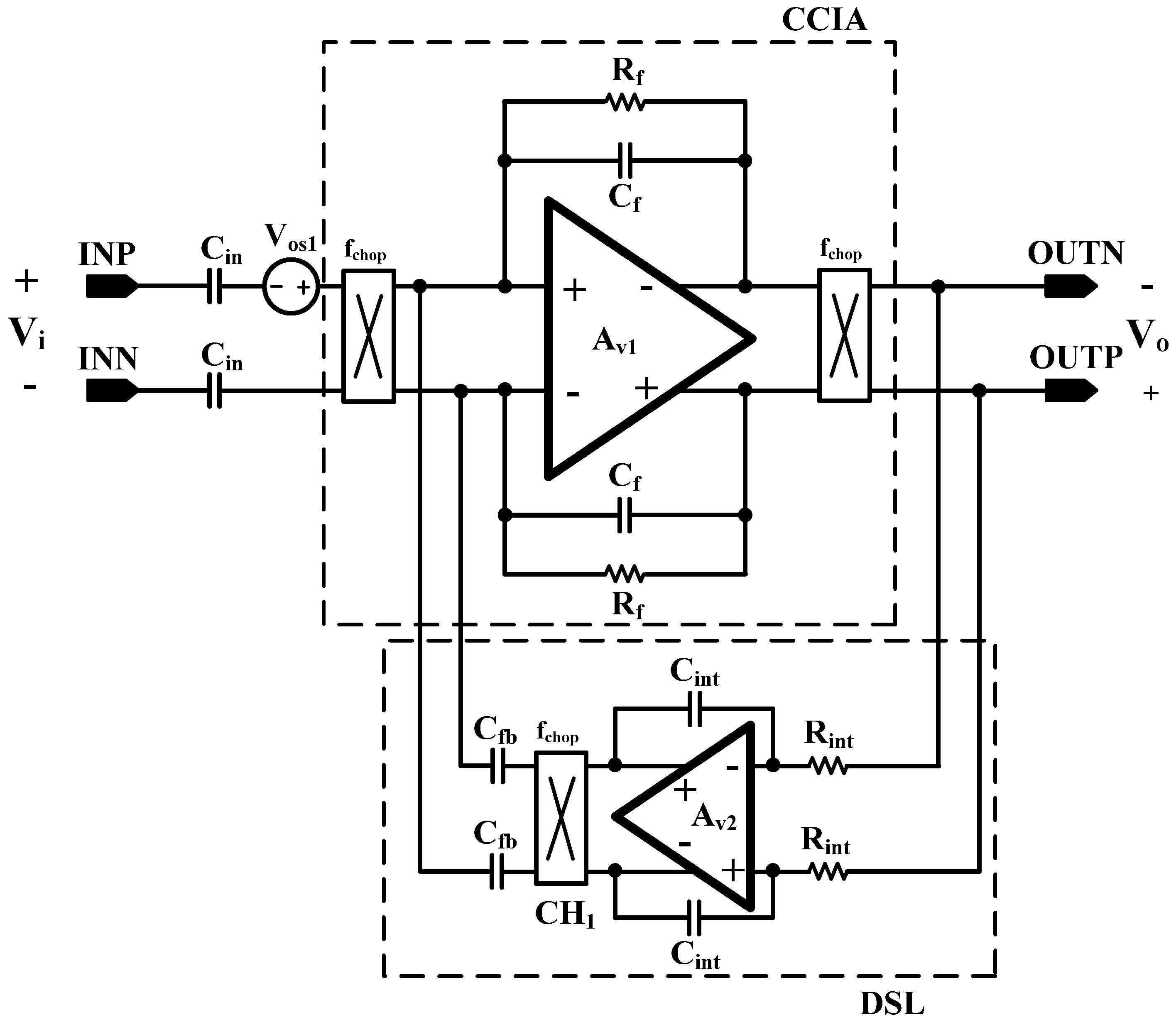

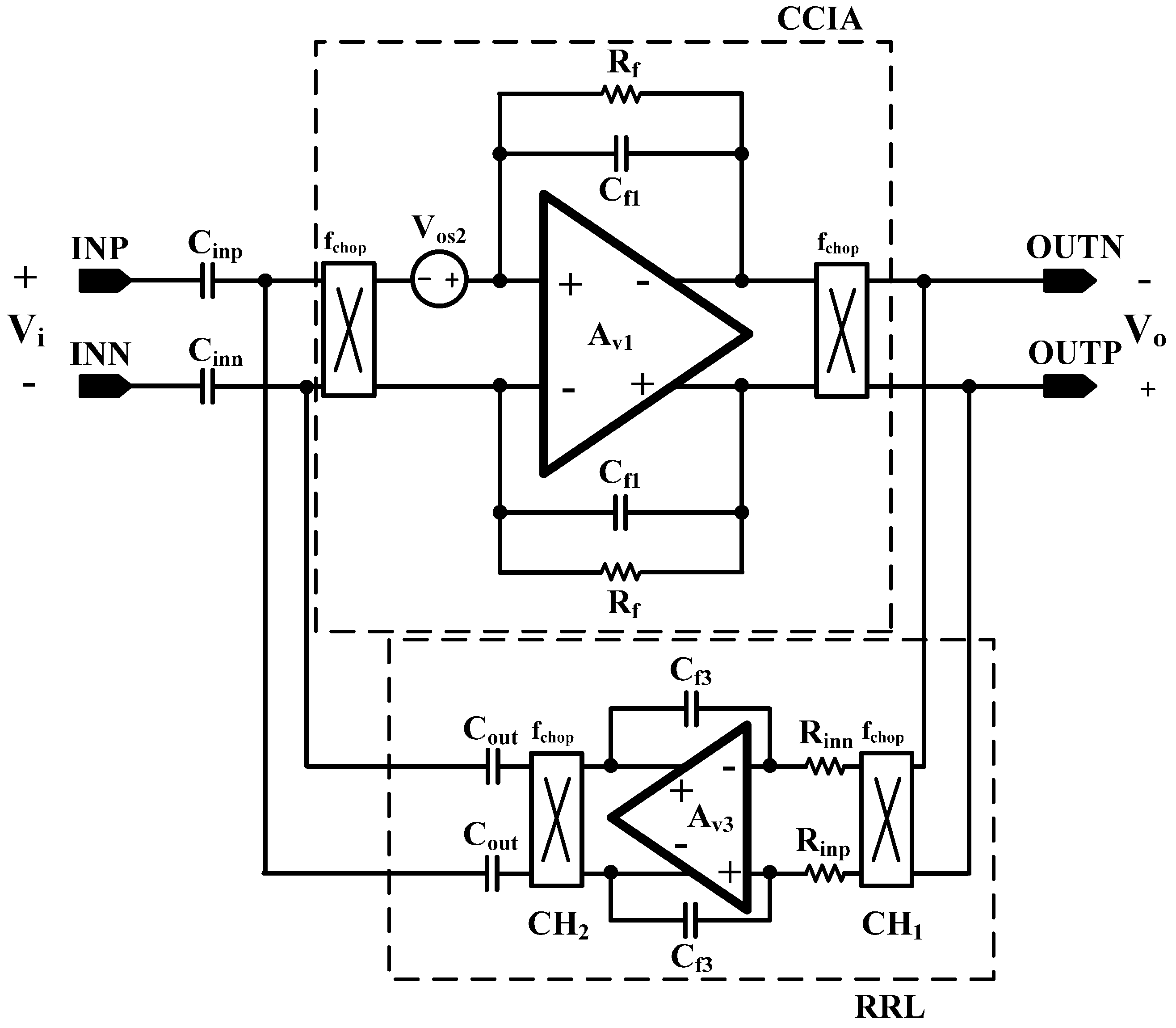

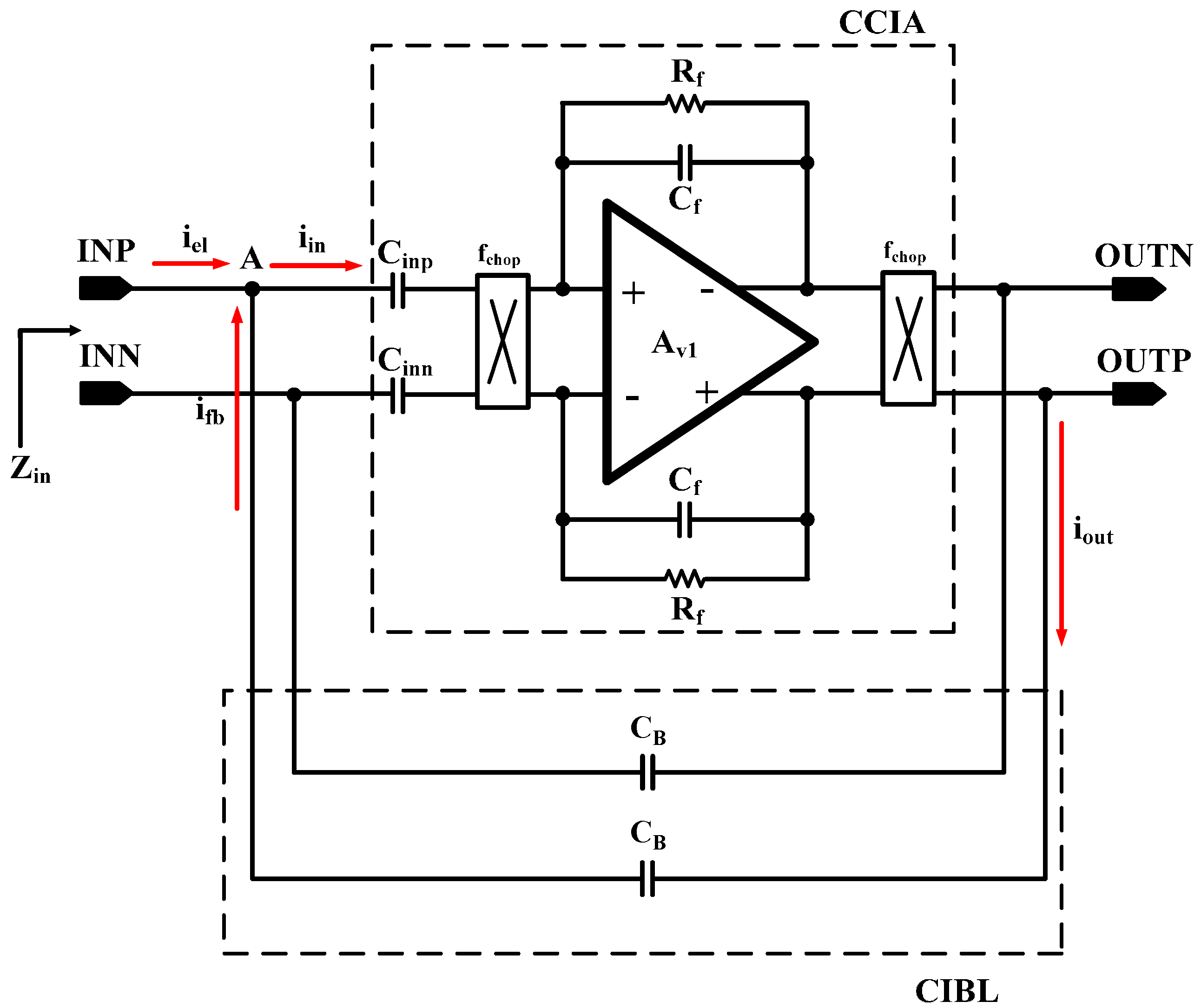

The overall architecture of the proposed AFE IC is shown in

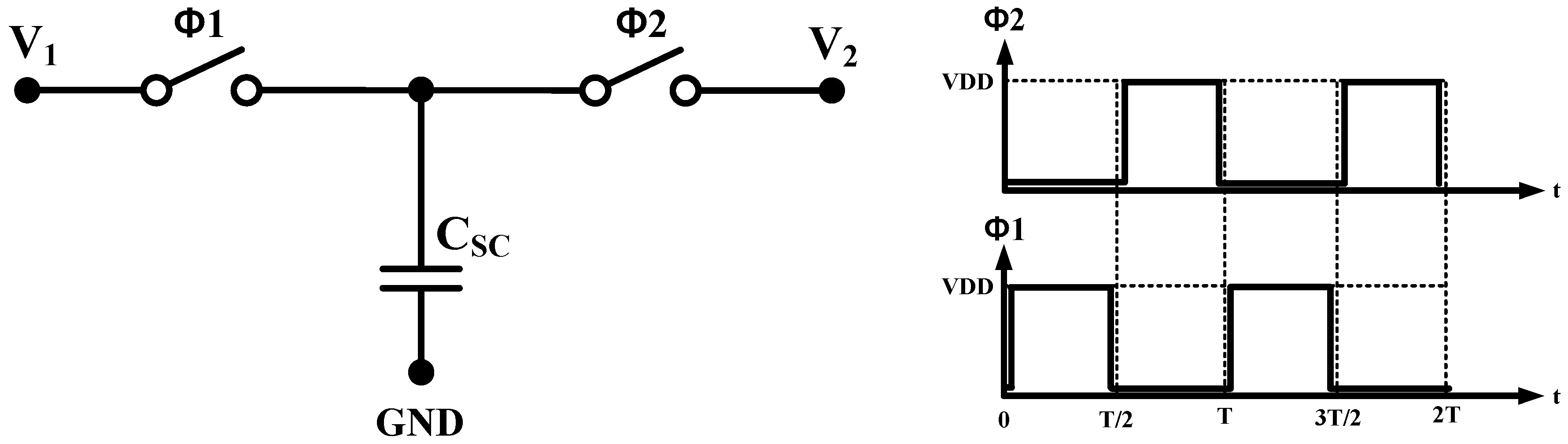

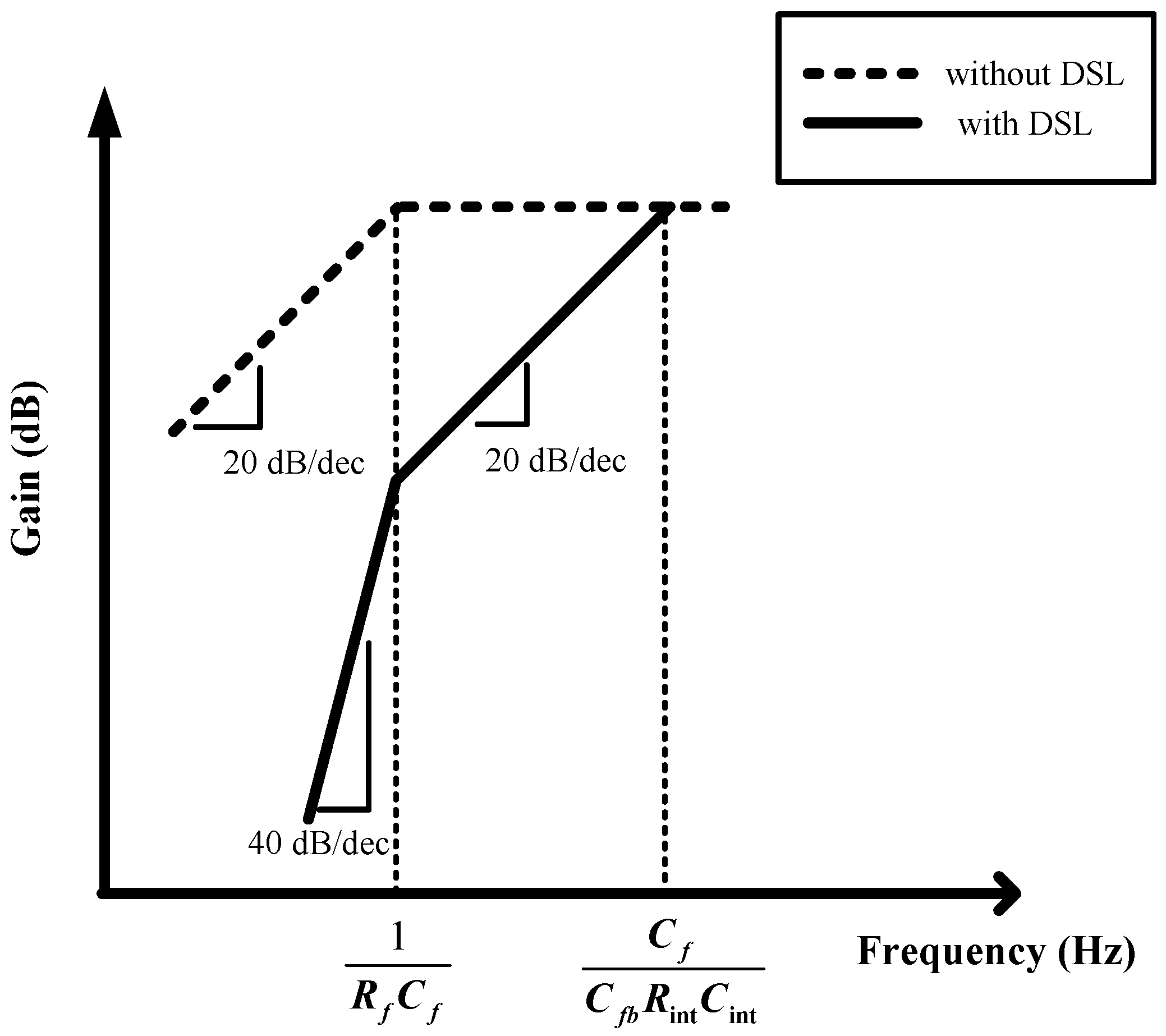

Figure 2. The proposed AFE adopts a multiple-offset compensation circuit to reduce both the internal and external offsets. The AFE consists of a two-stage capacitively coupled instrumentation amplifier (CCIA) with multiple offset compensation circuits at each stage. The default gain of a single CCIA is 36 dB. The single CCIA has a first-order HPF and DC servo loop (DSL), which generates additional poles; thus, a second-order HPF can be implemented in each CCIA stage. Previous studies on DSL required external capacitors [

6]. In this design, DSL is fully integrated without external components using a differential Miller integrator with pseudoresistors and frequency shifting choppers. Chopper stabilization (CHS) is adopted for achieving sub-µV input referred noise (IRN). The operation of CHS in the CCIA, however, can generate a ripple voltage due to the offset, which is generated by a component mismatch. The mismatch can be suppressed by adding a ripple rejection loop (RRL). Previous RRLs were implemented using large coupling capacitors [

5]. In this design, the RRL is implemented using a differential Miller integrator with pseudoresistors and frequency shifting choppers; thus, the circuit area is reduced because the large coupling capacitors can be eliminated. Insufficient input impedance is enhanced by a capacitive impedance boosting loop (CIBL). The previously reported active impedance boosting sub-circuit using positive feedback requires additional power consumption [

4]. The CIBL in this design is implemented using a passive capacitor, and does not require additional power consumption. The CIBL also increases the CMRR, even under input electrode mismatch conditions. The IRN is minimized by an iterative noise optimization design procedure. Out-of-band biosignals are attenuated by a fourth-order BPF. This BPF consists of a fourth-order high-pass filter (HPF) followed by a cascaded two-stage CCIA, and a fourth-order Sallen-key low-pass filter (LPF) followed by a two-stage CCIA. The presented AFE is designed to be fully integrated and is fabricated using a standard 0.18-µm complementary metal oxide semiconductor (CMOS) process.

Figure 2.

Architecture of a simplified biopotential acquisition circuit.

Figure 2.

Architecture of a simplified biopotential acquisition circuit.

3. Experimental Results

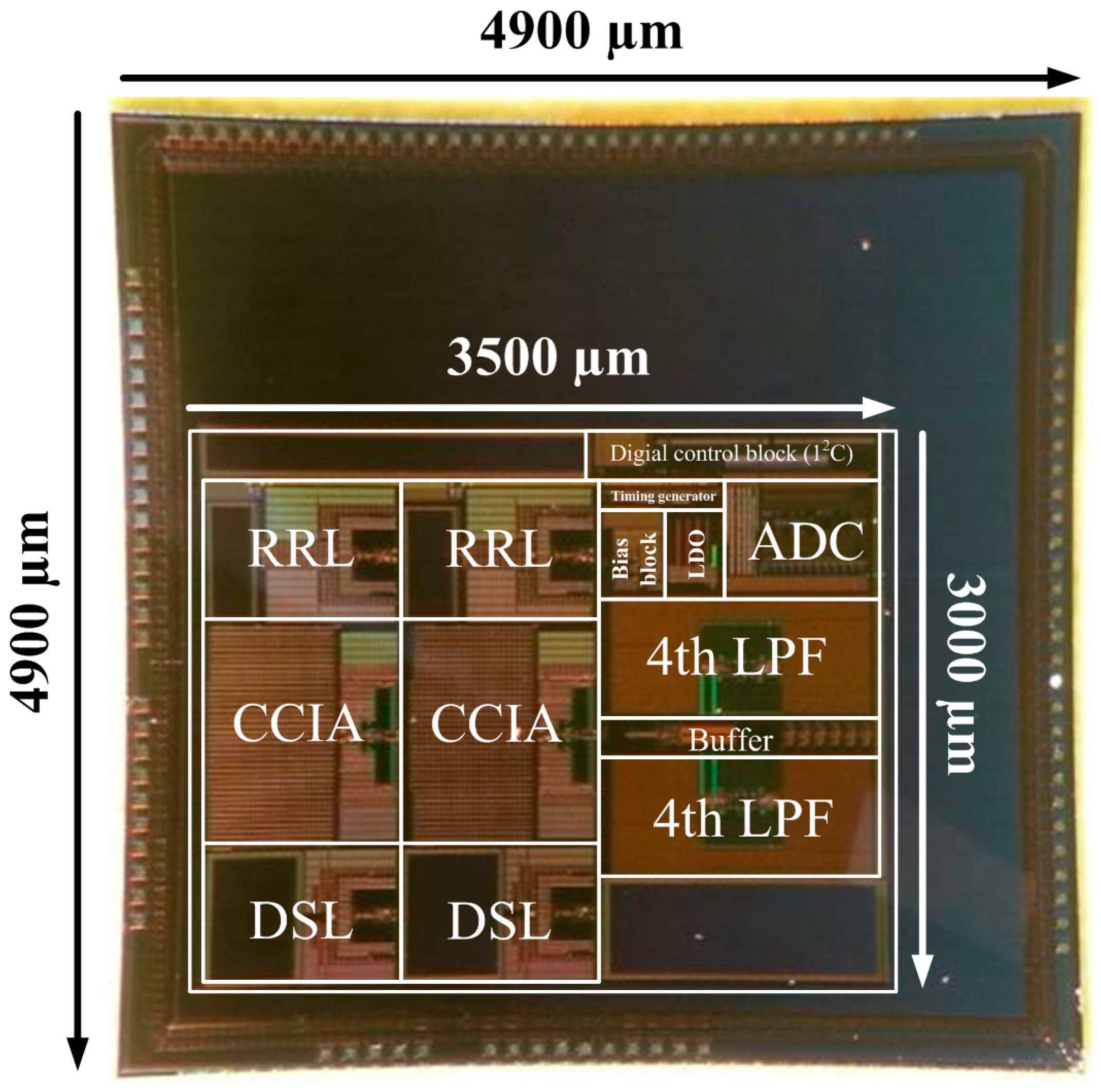

Figure 12 shows a die photograph of the biopotential acquisition AFE IC. The IC is fabricated using a 1P6M 0.18 µm process. The core chip size of the biopotential acquisition AFE without I/O pads is 10.5 mm

2. The AFE IC is fully integrated and does not require external components.

Figure 12.

Microphotograph of the biopotential AFE IC.

Figure 12.

Microphotograph of the biopotential AFE IC.

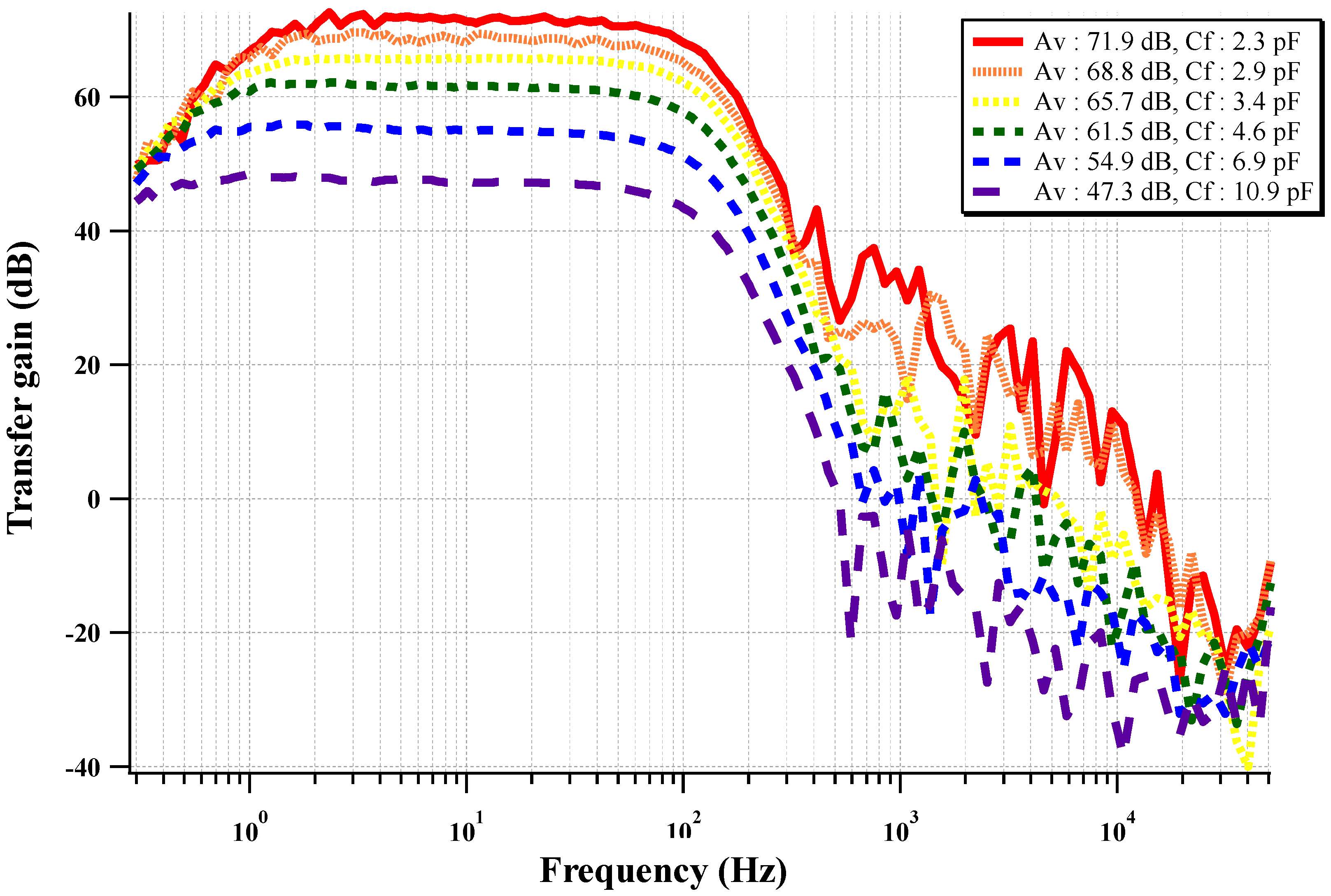

The measured frequency response of the circuit is shown in

Figure 13. The frequency response of the biopotential acquisition readout is a band-pass feature with a pass band of 1 to 100 Hz. The pass-band at the high frequency cut-off can be adjusted using a programmable resistor in the low-pass filter. The gain of the CCIA can be programmed with four-bit programmable feedback capacitors (Cf). The pass-band gain is programmable from 47.3 dB to 71.9 dB with four-bit resolution.

Figure 13.

Measured frequency response of the two-stage CCIA with a varying feedback gain control capacitor.

Figure 13.

Measured frequency response of the two-stage CCIA with a varying feedback gain control capacitor.

Figure 14 shows the frequency response when the DSL is activated. When the DSL at each CCIA is activated, the fourth-order HPF with 80 dB/dec slope is observed. The fourth-order LPF effectively attenuates the out-band components with a −80 dB/dec slope.

Figure 14.

Measured frequency response of the DSL activation.

Figure 14.

Measured frequency response of the DSL activation.

Figure 15 shows the effect of the RRL. The sinusoidal 1 mV signal at 50 Hz is used for the input source. The gain setting of the two-stage CCIA is 67 dB. The output ripple signal is decreased 84% by activating the RRL. The RRL operates as a notch filter at the chopper frequency and relaxes the requirements of the LPF in the output stage.

Figure 15.

Measured time domain output with the RRL.

Figure 15.

Measured time domain output with the RRL.

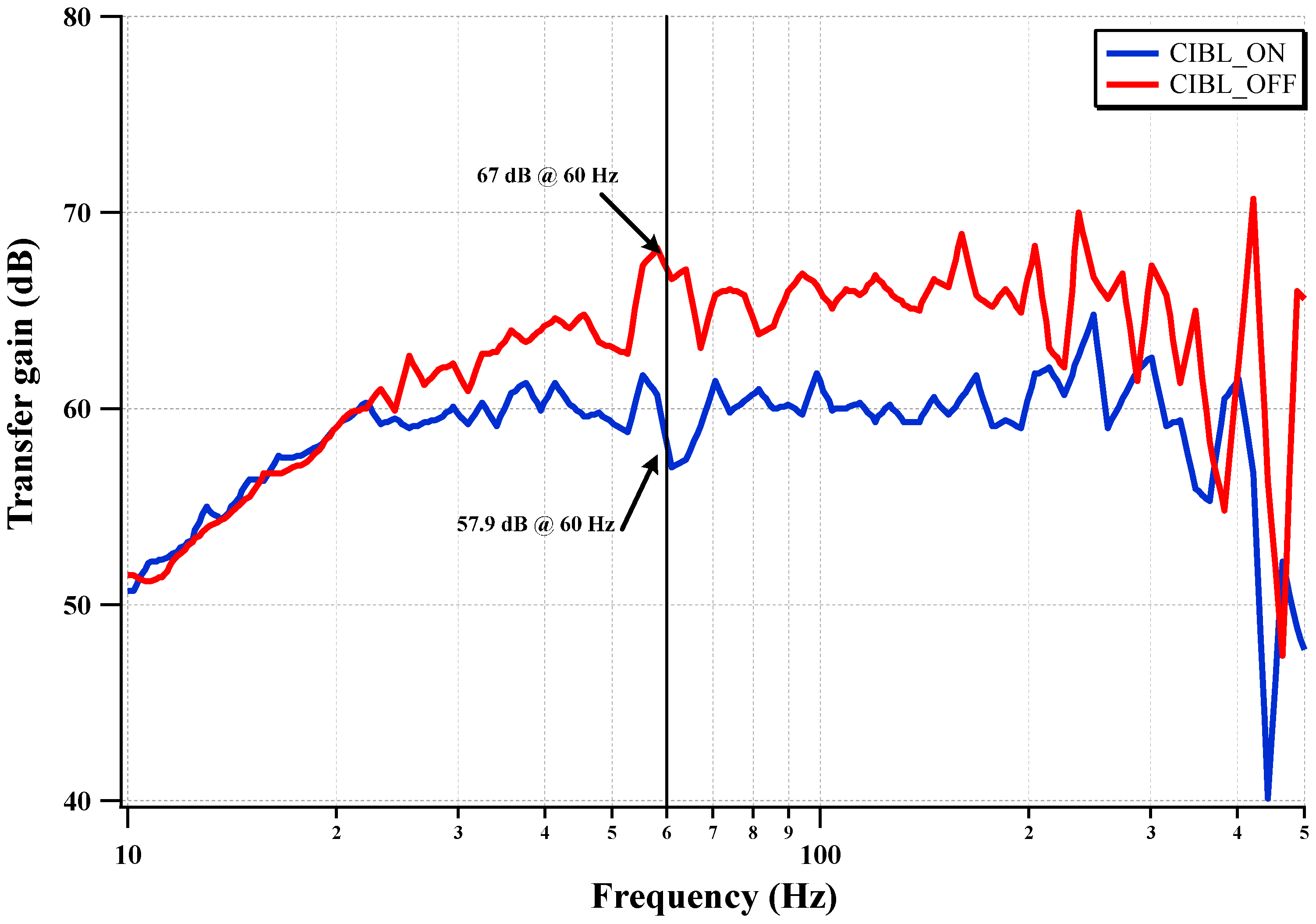

The measured CMRR of the IC with CIBL activation is shown in

Figure 16. The CIBL activation enhances the CMRR, even under electrode mismatch conditions, by boosting the input impedance. The two differential input electrodes are modeled using a 47 kΩ resistor and a 47 nanofarads capacitor in a parallel connection. The worst mismatch condition is assumed to be one electrode directly connected to the input terminal and the other electrode connected with the electrode model of a 47 kΩ resistor in parallel with a 47 nanofarads capacitor. The CMRR is improved from 57.9 dB to 67 dB (9.1 dB improvement) by activating the CIBL. The CMRR at 60 Hz is increased from 57.9 dB to 67 dB under the input electrode mismatch condition.

Figure 16.

Measured CMRR with the CIBL.

Figure 16.

Measured CMRR with the CIBL.

The measured IRN in the band-width from 1 Hz to 100 Hz is shown in

Figure 17. The integrated IRN in the band-width from 1 Hz to 100 Hz is 0.94 μV

RMS, when the DSL, RRL, and CIBL are activated.

Figure 17.

Measured IRN in band-width from 1 Hz to 100 Hz.

Figure 17.

Measured IRN in band-width from 1 Hz to 100 Hz.

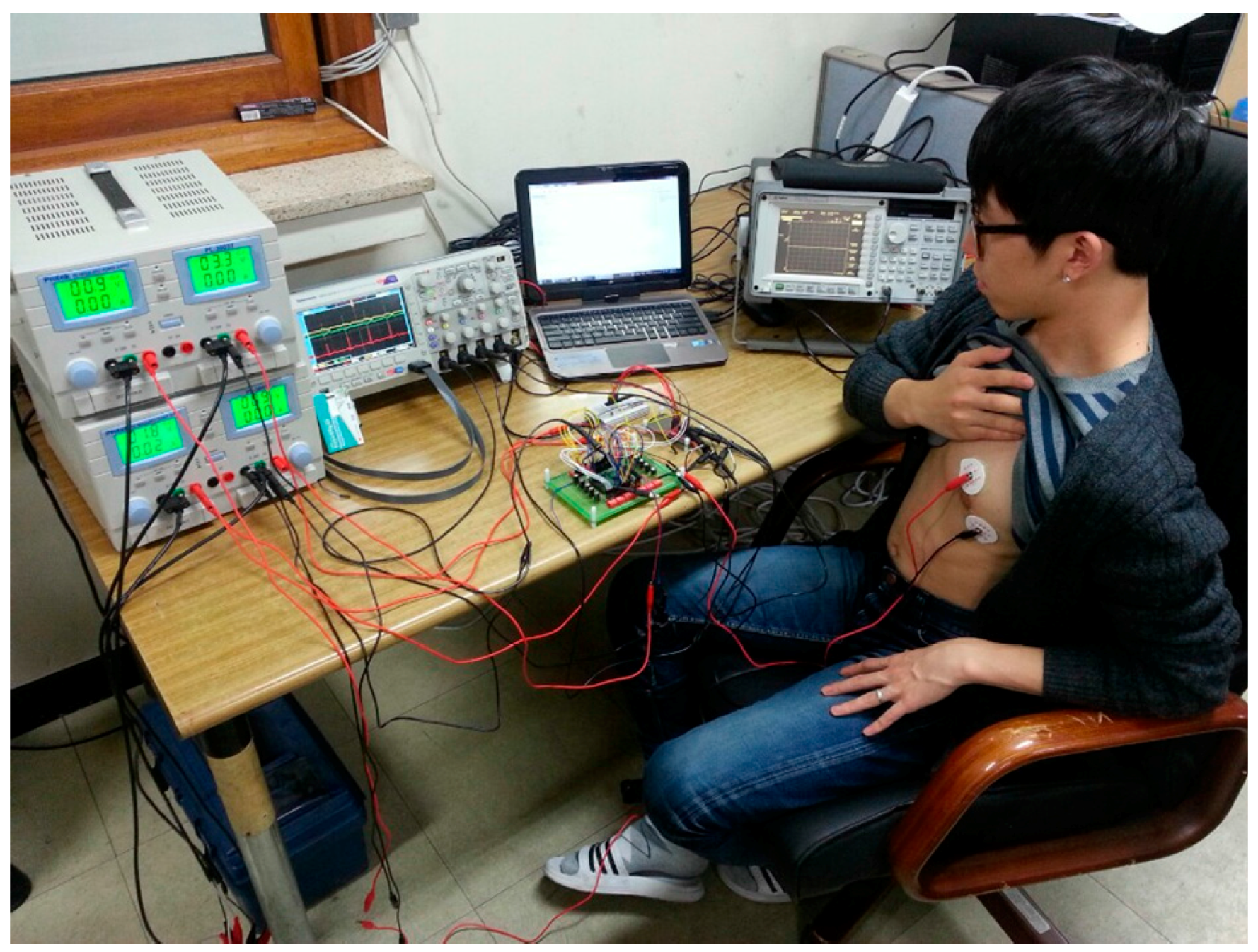

To evaluate the biopotential recording capability of the fabricated IC, an ECG signal was acquired from the human body, as shown in

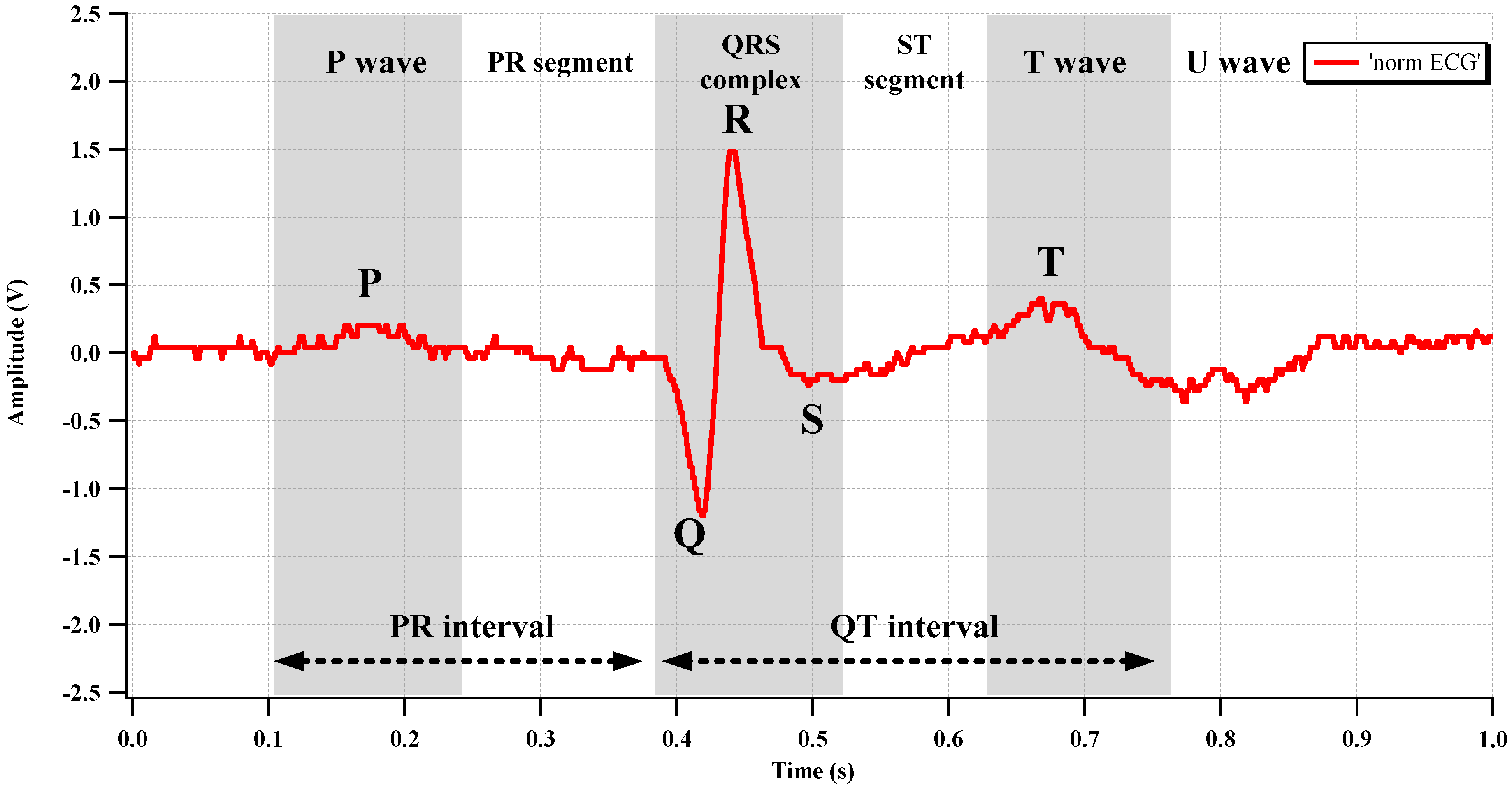

Figure 18. Two electrodes, which are connected to the CCIA input port, were attached to the left breast near the heart. The AFE gain is set to 67.1 dB. The differential output of the recorded ECG is shown in

Figure 19. The typical P-Q-R-S-T regions are clearly distinguishable.

Figure 18.

ECG signal measurement environment.

Figure 18.

ECG signal measurement environment.

Figure 19.

Measured ECG waveform.

Figure 19.

Measured ECG waveform.

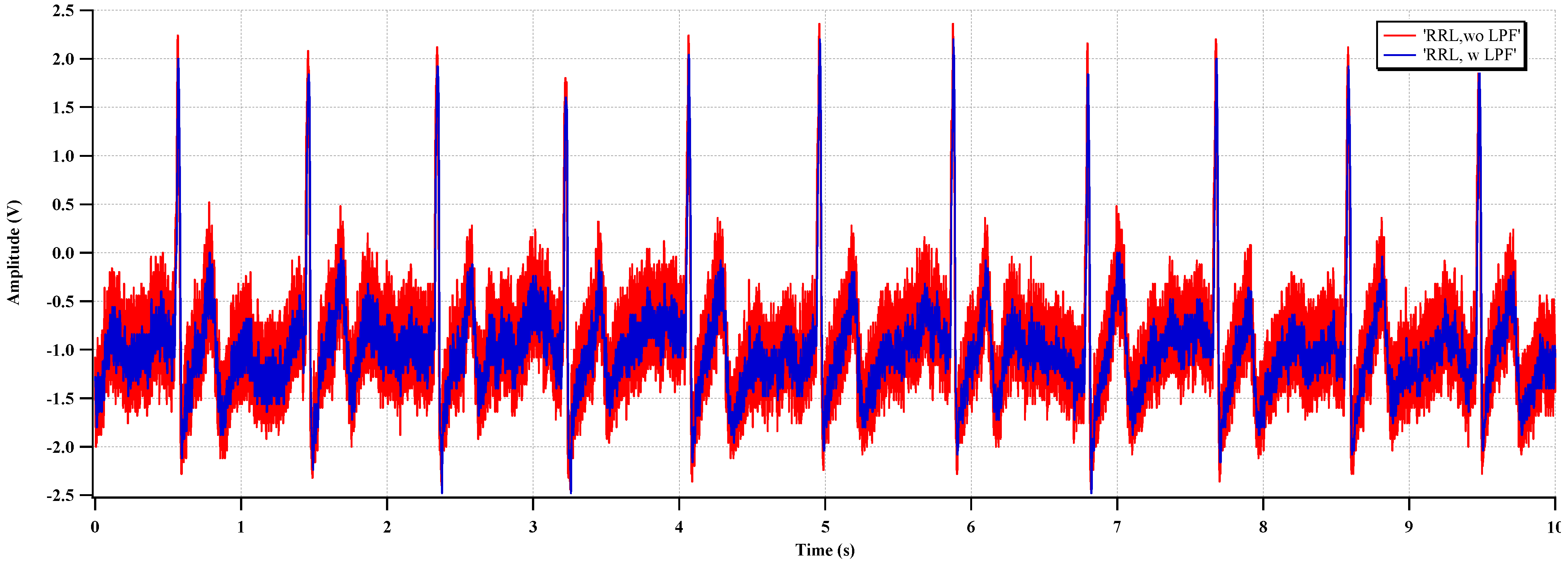

The measured ECG waveforms with RRL and CIBL are shown in

Figure 20 and

Figure 21, respectively. In

Figure 20, the high-frequency noise (ripple) is reduced, and a clear ECG waveform can be acquired, even without the LPF. In

Figure 21, the common-mode noise, mainly 60-Hz interference, is reduced, and a clearer waveform is achieved by activating the CIBL.

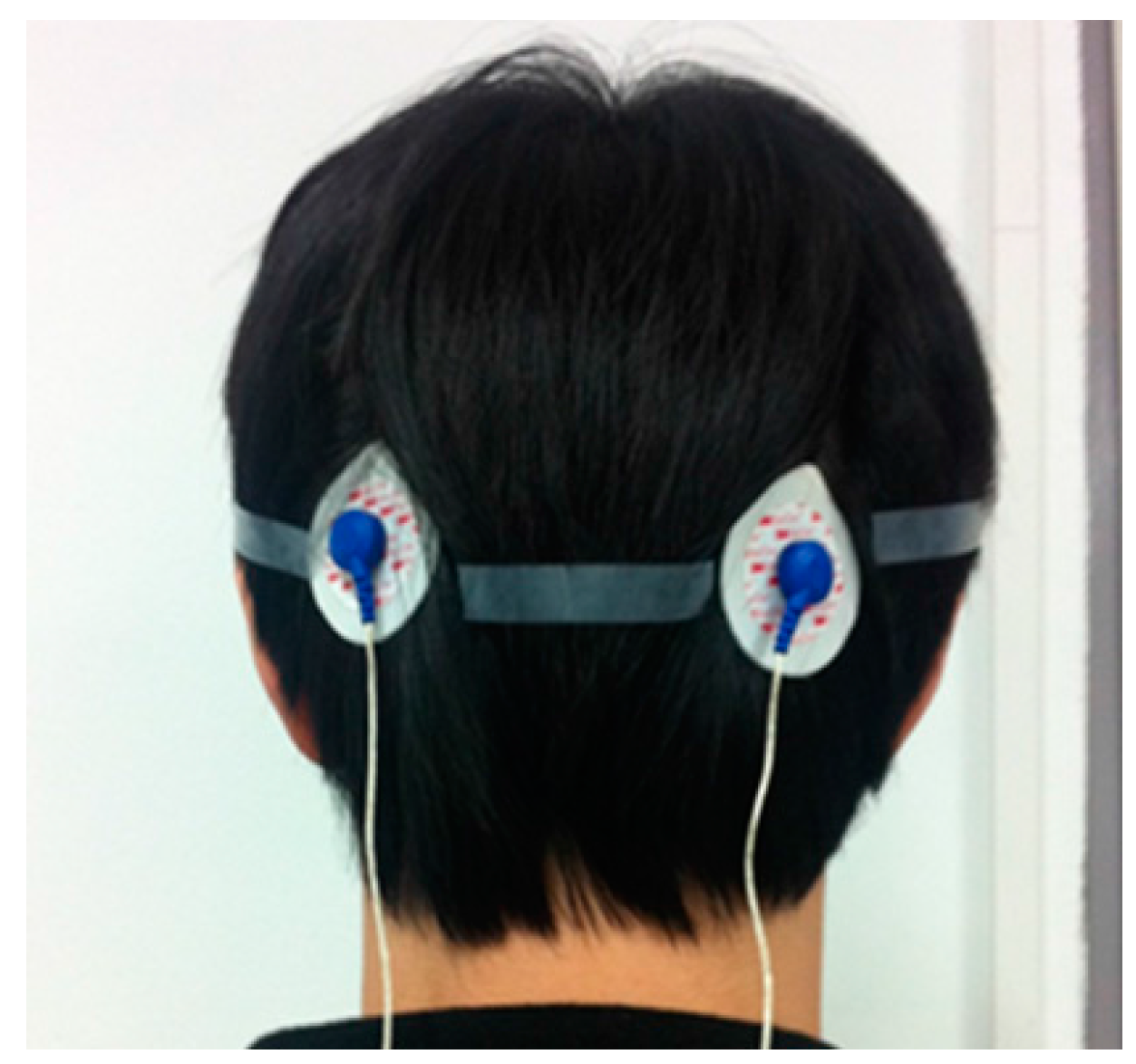

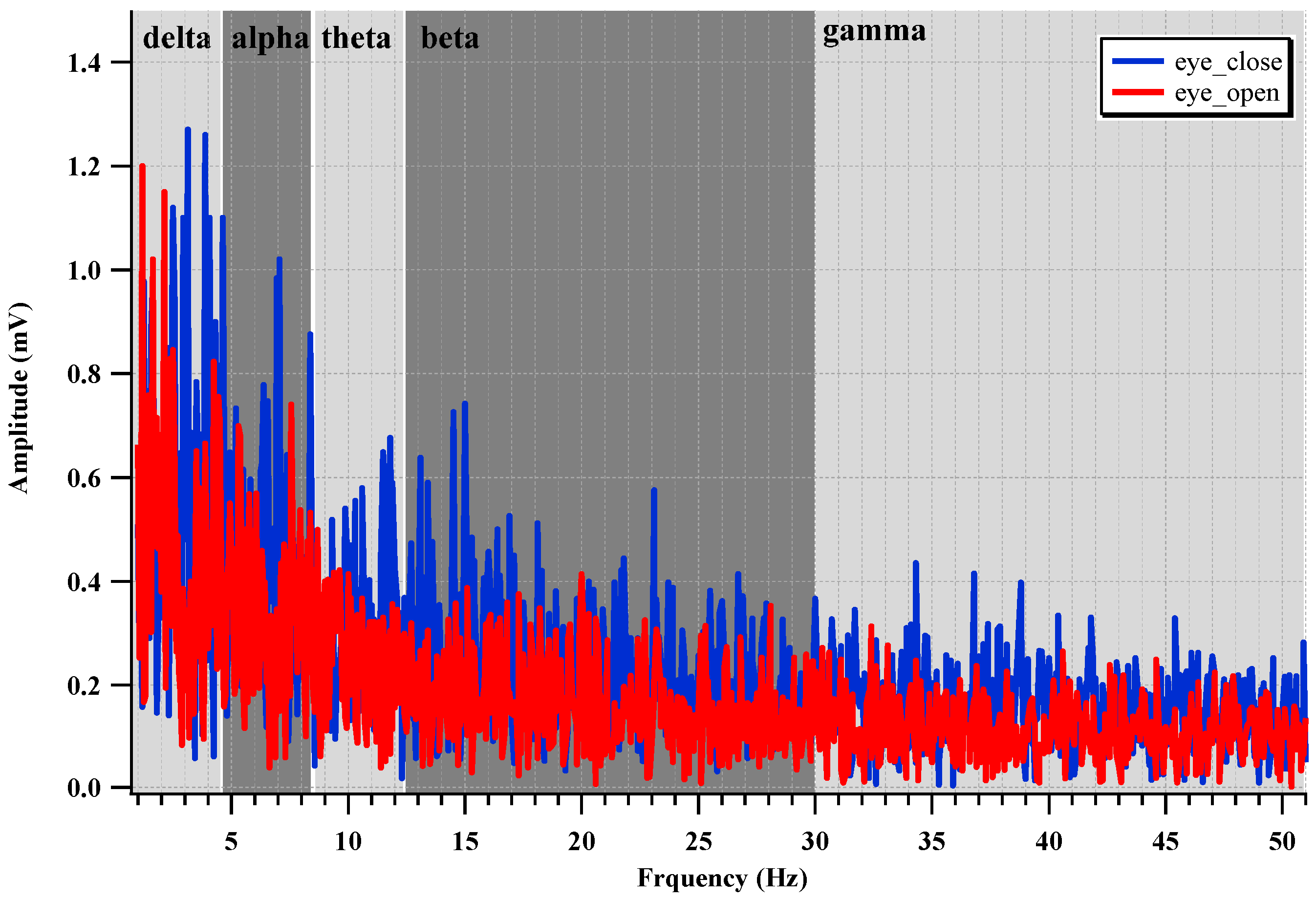

To evaluate the EEG recording performance of the fabricated IC, two electrodes are attached to the backside of the head, which is near the visual cortex, as shown in

Figure 22. The alpha suppression phenomenon, which means that the alpha wave is suppressed when the eyes are opened, is measured. The measured EEG spectrum is shown in

Figure 23. The average power when the eyes were open decreases by 61.2% compared with that when the eyes were closed.

Figure 20.

Measured ECG with RRL activation.

Figure 20.

Measured ECG with RRL activation.

Figure 21.

Measured ECG with CIBL activation.

Figure 21.

Measured ECG with CIBL activation.

Figure 22.

EEG signal measurement environment.

Figure 22.

EEG signal measurement environment.

Figure 23.

Measured EEG spectrum.

Figure 23.

Measured EEG spectrum.

4. Conclusions

The biopotential AFE IC with DSL, RRL, and CIBL is presented. The performance comparisons to previous research are summarized in

Table 1 [

5,

6,

7,

8,

9,

10]. To compare the noise and power performance to previous researches, the noise efficiency factor (NEF) is used [

11], as expressed in Equation (6):

where

Vrms,in is the input-referred RMS noise,

Itotal is the total supply current,

Ut is the thermal voltage

kT/q, and

BW is the band-width of amplifier. The IC includes the two-stage chopper-stabilized CCIA to achieve low input referred noise. The CIBL is designed to enhance the input impedance and the CMRR. The DSL is designed to reduce the external offset and to implement additional HPF. The RRL is designed to reduce the chopper induced ripple. The IC is fabricated using a 0.18 µm 1P6M CMOS process. The core chip size of the IC without I/O pads is 10.5 mm

2. The IC is fully integrated, and can be operated as a stand-alone biopotential measurement system with robust signal acquisition capability.

Table 1.

Performance comparisons.

Table 1.

Performance comparisons.

| | This Work | Reference No. |

|---|

| [5] | [6] | [7] | [8] | [9] | [10] |

|---|

| Process (μm) | 0.18 | 65n | 0.5 | 0.35 | 0.18 | 0.8 | 0.5 |

| VDD (V) | 3.3 | 1 | 3 | 1.5 | 0.4 | 1.8 | 3 |

| Current (μA) | 3.8 | 1.8 | 20 | 0.18 | 0.226 | 1.2 | 485 |

| Ripple reduction | Yes | Yes | No | No | No | No | No |

| DC servo loop | Yes | Yes | Yes (external capacitor) | No | No | No | No |

| Input impedance boosting | Yes | Yes | No | No | No | No | No |

| Passband (Hz) | 0.5–100 (programmable) | / | 0.5–150 | 20–280 | 0.5–100 | 0.5–250 | 0.3–150 |

| Gain (dB) | 71.9 (programmable) | 40 | 60 | 40 | 40–70 | 45.5 | 80 |

| CMRR (dB) | 102 (wo/mismatch)

67 (w/mismatch) | 134 | 110 | 74 | 120 | 100 | 110 |

| Noise (μV) (100 Hz BW) | 0.94 | 0.6 | 0.574 | 2.3 | 0.88 | 0.93 | 0.73 |

| NEF | 7.17 | 3.3 | 9.2 | / | 4.7 | 4.9 | 59 |