1. Introduction

Graphene is a promising two-dimensional material exhibiting exceptionally high crystal and electronic qualities, which has fascinated researchers for decades. The richness of its electronic and optical properties include, but are not limited to, its high residual carrier concentration, mobility, Fermi velocity, high thermal conductivity, its perfect 2D body, optical transparency, and high mechanical stability [

1,

2,

3,

4,

5], which have already revealed a cornucopia of potential engineering and application. Numerous research groups have seen graphene as a descendant of Silicon for analog devices, though the roadblock of graphene—its zero bandgap [

6]—made it incapable of switching off field effect transistors (FETs) and, thus, inappropriate for logic devices.

An important metric for a radio frequency transistor’s performance measurement is its current gain cutoff frequency,

fT. The cutoff frequency inversely depends on source/drain resistance, which is composed of contact resistance and access resistance, and their minimization ensures

fT increment. The detrimental effect of access resistance on a graphene FET is much more prominent compared to that on other FETs. In addition to that, handing this access resistance in graphene field-effect transistors (GFETs) is much more challenging compared to other FETs. That is the reason why access resistance is getting a great deal of attention in GFETs, which prompted us to work on a viable way to reduce it. For example, the typical access resistance of silicon metal oxide field effect transistor (Si-MOSFET) is ~150 ohm-um [

7], on the other hand, this quantity, for GFETs, is ~350 ohm-um and is 80% of the total device resistance [

8]. In addition to this, in Si-MOSFET, the access region is highly doped by ion implantation in order to reduce access resistance [

9], whereas, this type of high energy doping scheme is not viable for GFETs, where single or a few layer graphene form the device’s access region. Techniques to reduce GFET contact resistance have been proposed and reported by numerous groups [

10,

11,

12,

13,

14,

15]. Reduction of access resistance for enhanced performance in graphene FETs [

16,

17,

18,

19,

20], in III-N high electron mobility transistors (HEMTs) [

21], and in GaAs/AlGaAs HEMTs [

22], have also been reported. In this work, we have proposed, studied, and extensively analyzed a GFET with hybrid contacts capable of simultaneously reducing the access resistance and contact resistance of the device. The capacitive coupled part of the contact reduces the contact resistance and provides a low resistance path for the high frequency signal. In addition, the extension towards the gate reduces the access region length and the associated resistance—the access resistance. The approaching capacitive extension towards the gate might introduce additional parasitic capacitance; however, the cumulative aiding effect of contact and access resistance reduction on high frequency performance is more significant and prominent than the detrimental effect of additional parasitic capacitances. The elimination of the access region by using a sophisticated fabrication method, e.g., a self-aligned process, could be a better way to handle access resistance; however, the proposed method offers a promising viable alternative, where complex/sophisticated lithographic techniques with smaller tolerances need to be avoided.

2. Theory

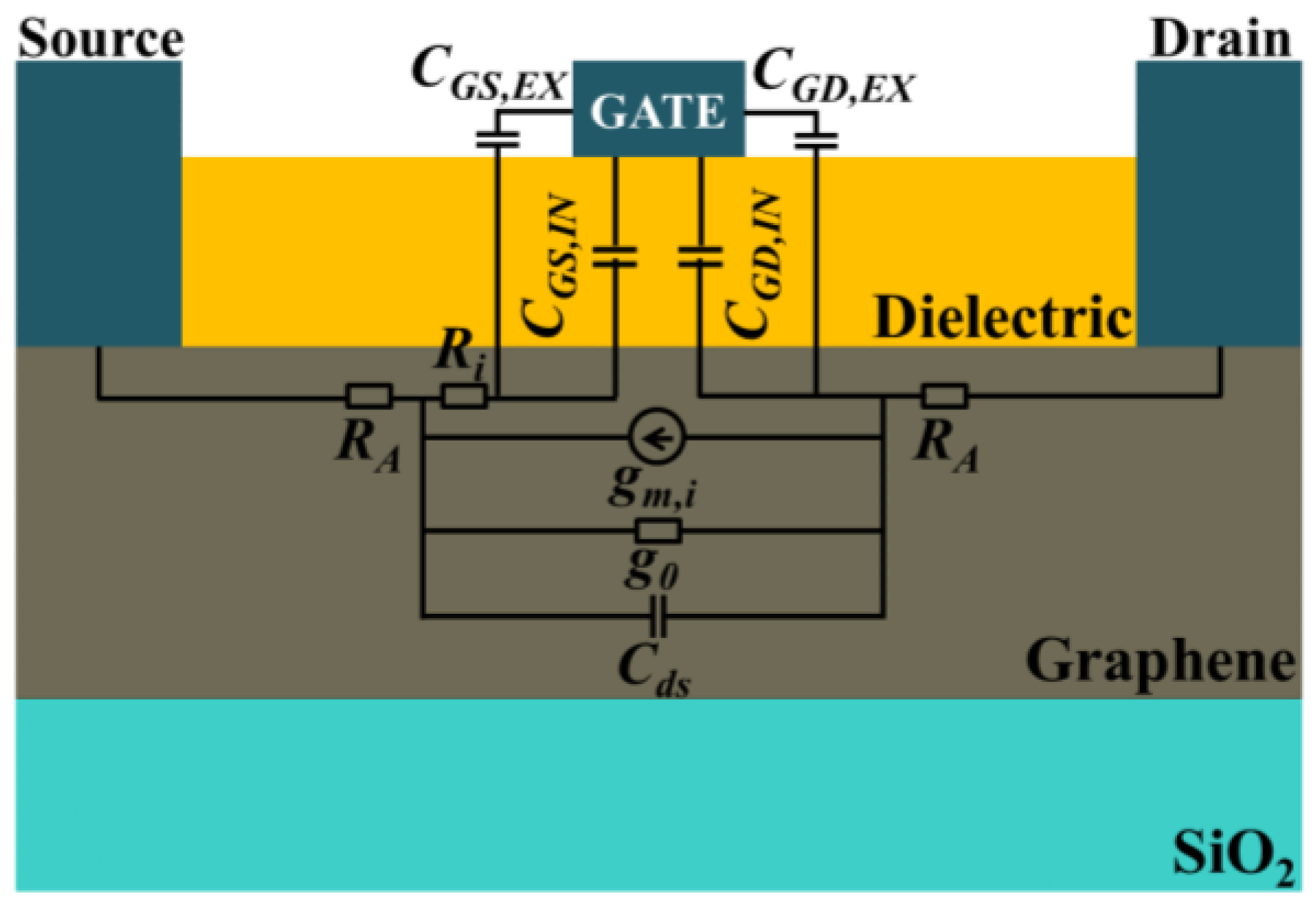

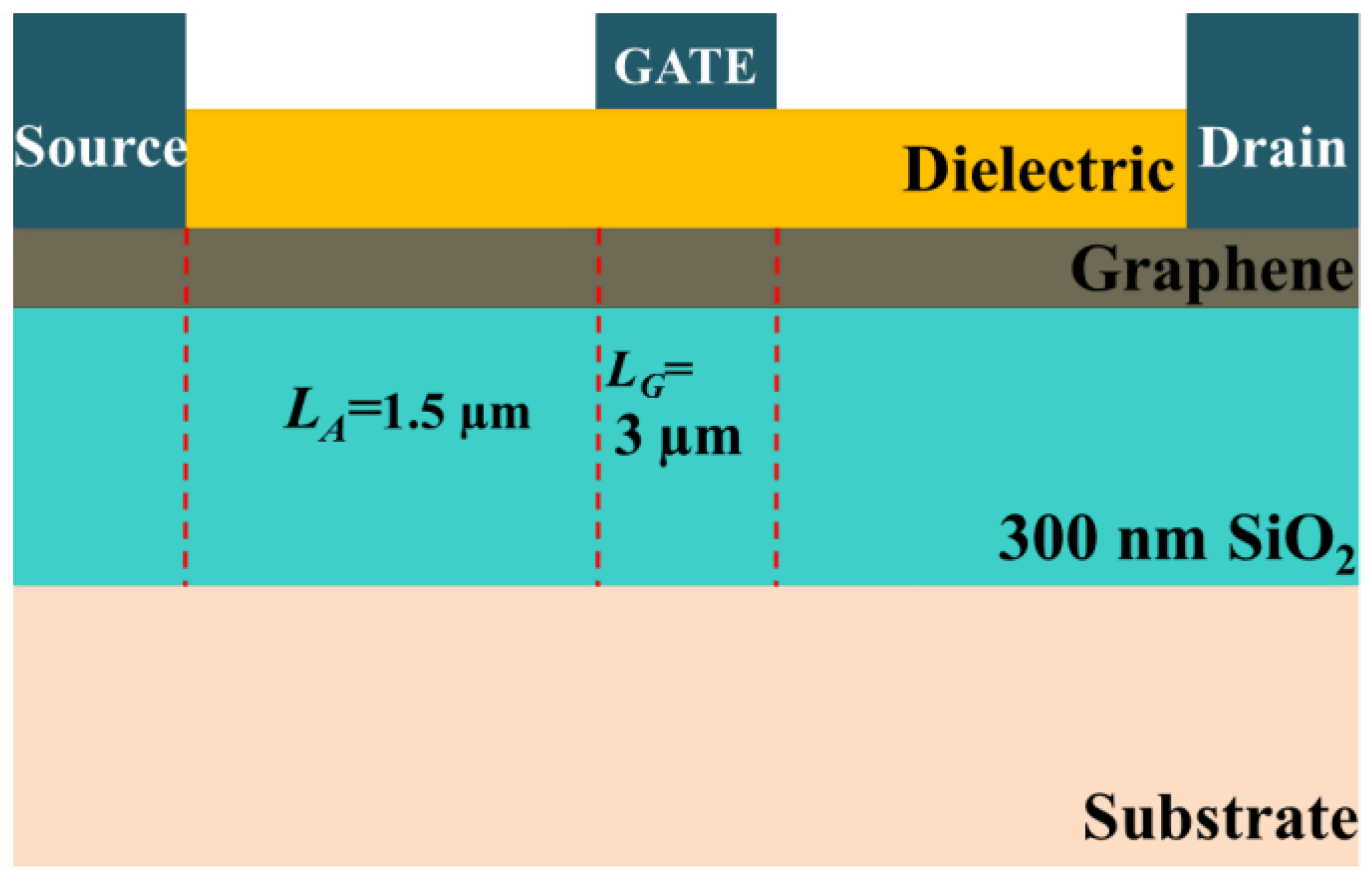

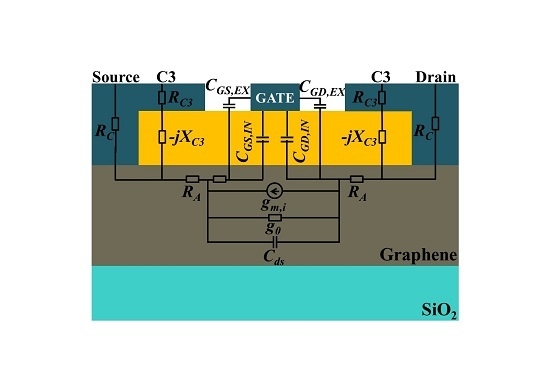

The small signal equivalent circuit of a conventional three-terminal GFET, overlaid on the device schematic, is shown in

Figure 1.

The time that it takes the charge carriers to travel from the source to the drain is called the delay time, and can be divided into two parts: transit delay and parasitic delay. The intrinsic and extrinsic gate to source/drain capacitances are responsible for the transit delay and can be expressed as [

23,

24]:

On the other hand, parasitic resistances and capacitances cause a parasitic delay, as their names suggest, and can be expressed as [

23]:

where

g0 =

1/RSD is the output conductance,

RSD is the drain to source resistance,

RS and

RD are the source and drain resistance consisting of ohmic contact resistance,

RC and source/drain access resistance,

RA in series:

where

LA is the access region length (

LGS and

LGD), μ is the carrier mobility,

q is electronic charge,

n0 is the residual carrier density in graphene, and

W is the device width. For simplicity, the effects of graphene doping, due to contacts and the gradient in carriers of the access region, have not been included; however, the effect is well explained in Reference [

25]. In a common emitter configuration, the input terminal of a FET is the gate and the output terminal is the drain. As it is a FET, the input current in direct current (DC) is zero. As a result, the current gain for DC is theoretically infinite, h21 = i

out/i

in = i

out/0 =

. The reactance of gate to channel capacitance is inversely dependent on frequency, and with increasing frequency, the reactance decreases. As a result, the input alternating current (AC) current also increases with frequency, which results in a decrease of current gain. The frequency at which, current gain drops to unity is called the current gain cut-off frequency, and can be related to the total delay time in the device, as follows:

After substituting Equations (1) and (2) into Equation (4) and rearranging, the current gain cut-off frequency,

fT of the GFET can be related to the small signal equivalent circuit parameters, as follows:

where,

RSD is the total channel resistance.

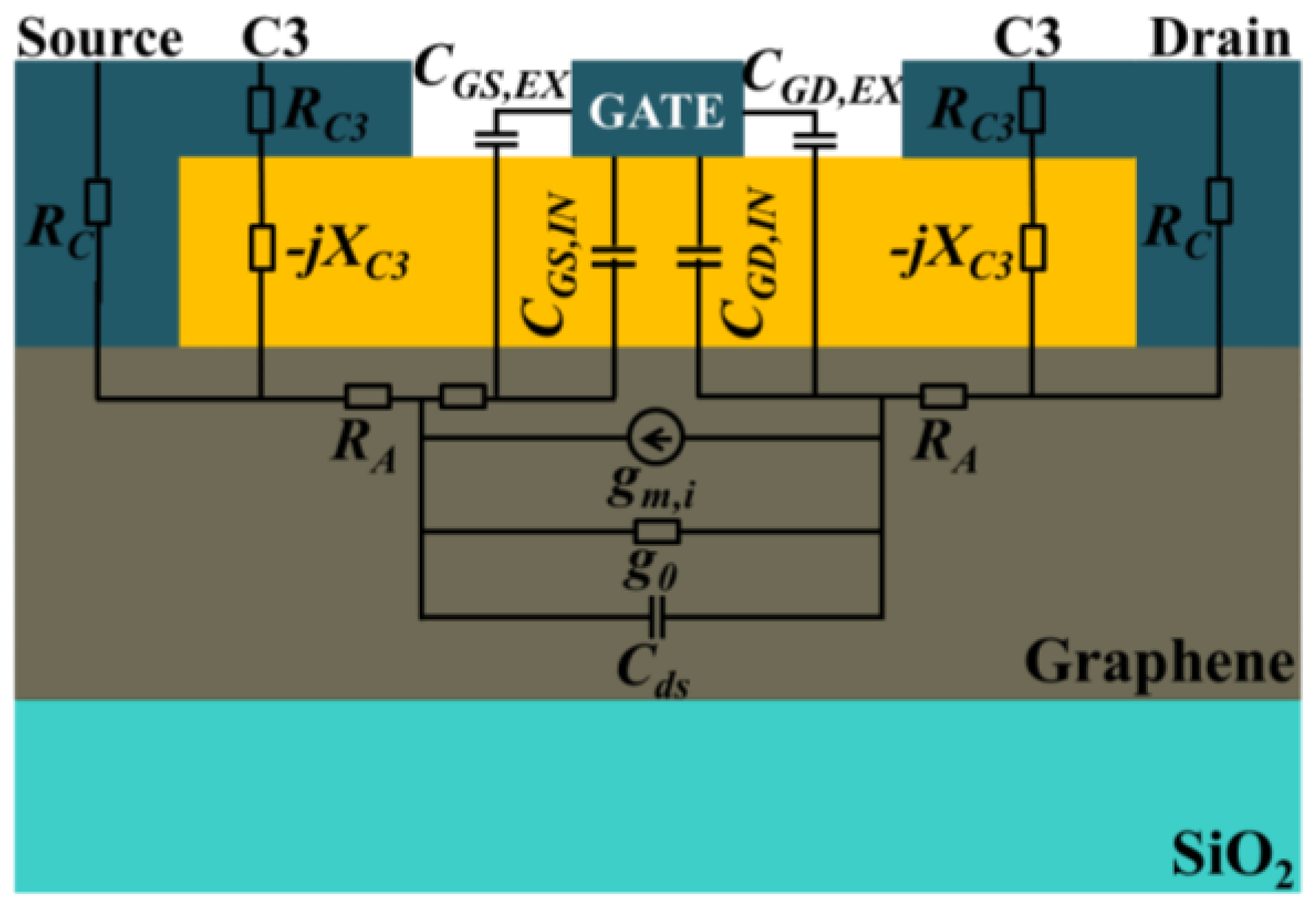

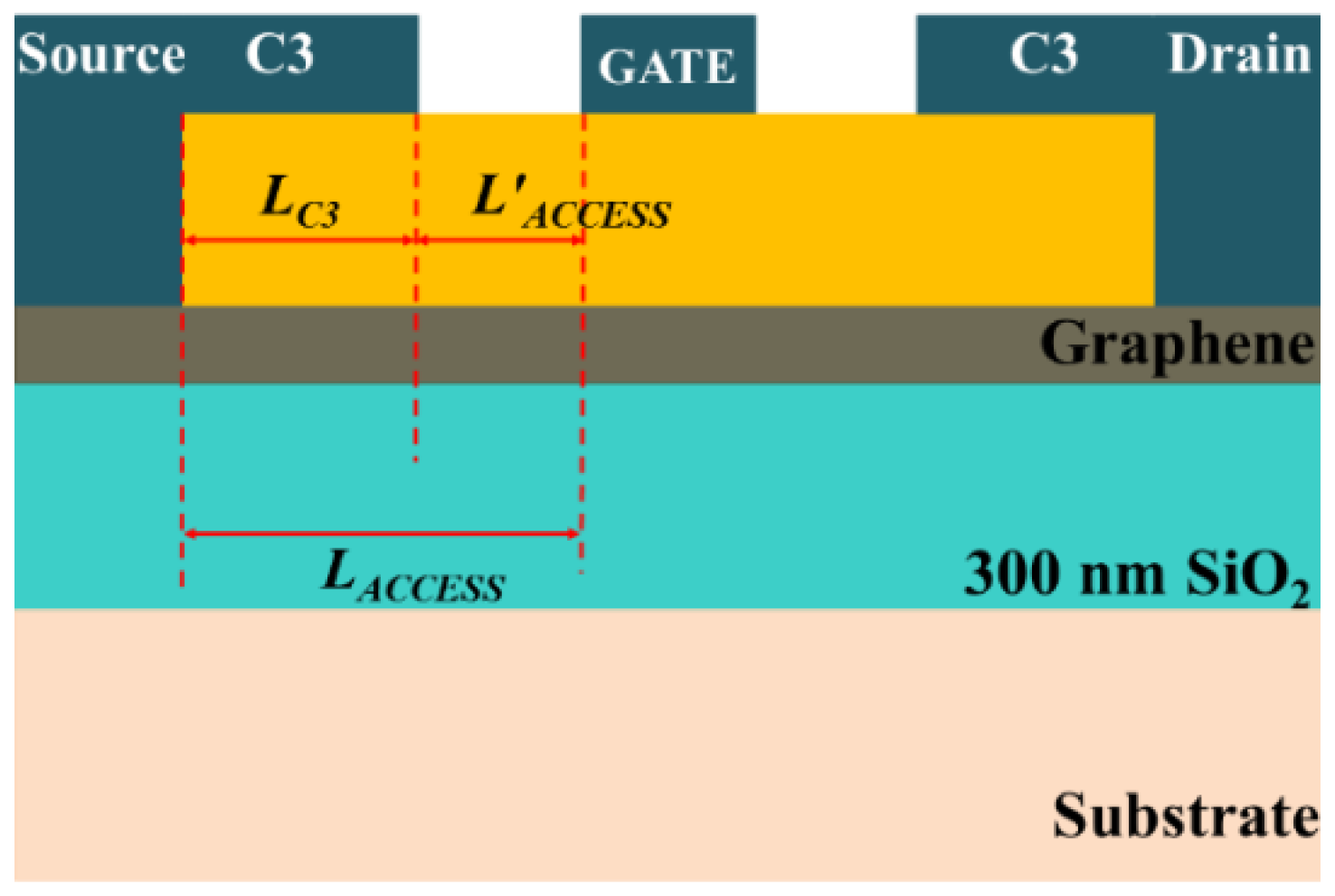

If two capacitively coupled contacts (C3s) are placed on the access regions and connected to the ohmic source/drain, as shown in

Figure 2, C3 will make a path for high frequency RF signal parallel to the ohmic contact. The C3 impedance,

ZC3 =

RC3−

jXC3, consists of real and imaginary parts, and the total contact impedance comes to be

ZC =

RC||

ZC3 =

RC||

(RC3−

jXC3). After rearrangement and simplification,

ZC can be expressed as:

Assuming the length of C3 is

LC3, the access region length of the hybrid contact GFET comes to be

, and the new expression for source/drain impedance and total channel impedance becomes:

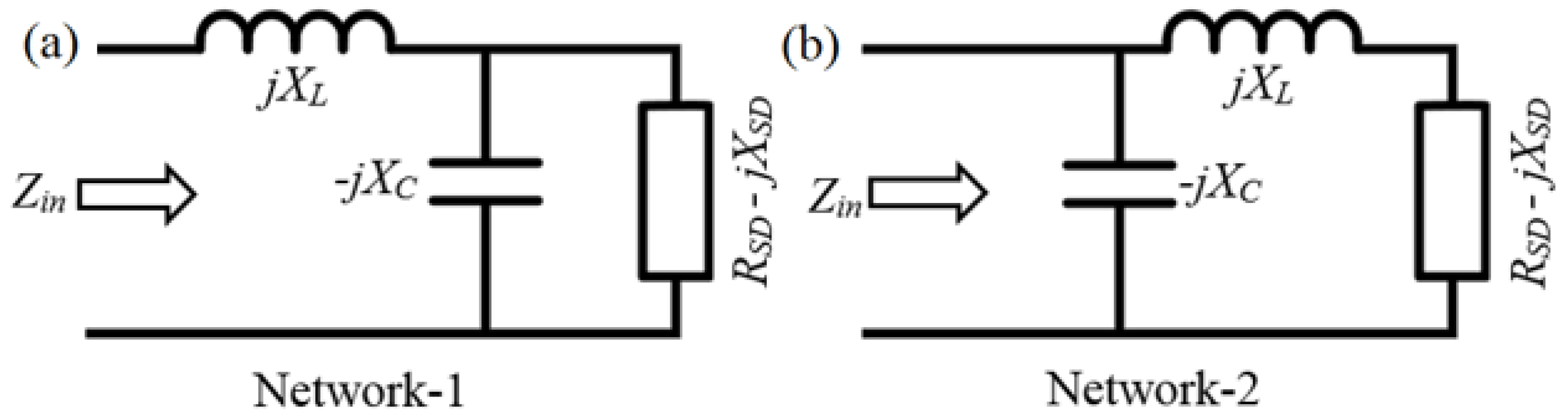

From the Equation (6), we can see that the total channel resistance has a real part, as well as an imaginary part. A simple matching network can be designed for matching and eliminating the imaginary part of the input impedance. An impedance matching network is an additional circuit that consists of a reactive element of such a value that can effectively nullify the opposite signed reactive element of the device, and thus eliminate the effective reactance of the whole system. It can be achieved with only two reactive elements that transform both the real and imaginary parts. A common two reactive element configuration is referred to as an L-section matching network, as shown in

Figure 3a.

Considering network-1, we can quantify the input impedance as:

To match it with a resistance,

R, we consider

Zin =

R, and after equating the real and imaginary parts, we get:

By solving these equations, we can determine the capacitor and inductor values required to nullify the imaginary part of the contact impedance. These two relations are derived for network-1 and are valid if

RSD >

R. On the other hand, if

RSD <

R, network-2, as shown in

Figure 3b, needs to be used, and after following the same procedure, we can estimate

XL and

XCAP as follows:

For devices working on a wide frequency range, a very common technique in RF/mobile communication, named the “frequency transformation technique”, needs to be used, as reported in Reference [

26].

Once the matching network has been used, only the real part of contact resistance

R’c remains, and the new expression of source/drain resistance comes out to be:

One can easily acquire the relation between fT and ZC by plugging this new RS and RD into the fT equation in Equation (5).

C3 can be considered as an RC transmission line and its impedance can be analytically calculated [

27]. If a C3 is placed on top of the gate dielectric, the contact metal and graphene channel, with the in-between dielectric material, form an RC transmission line. The propagation constant, γ, and characteristics impedance,

Z0, of this transmission line can be estimated by the following equations:

where,

Rsh is sheet resistance of the graphene channel,

C is the metal to graphene capacitance per unit area,

W is the width, and

f is the frequency. The C3 impedance can be estimated to be equal to the input impedance of this open-ended transmission line, as follows:

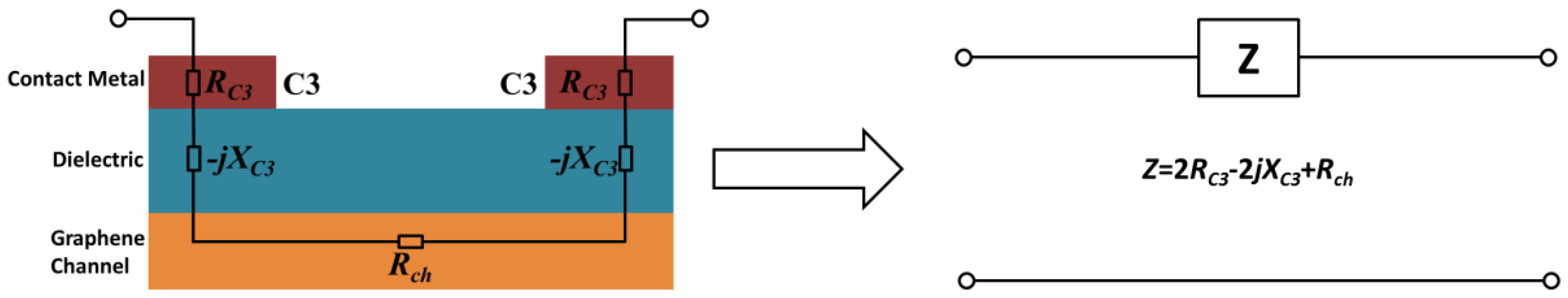

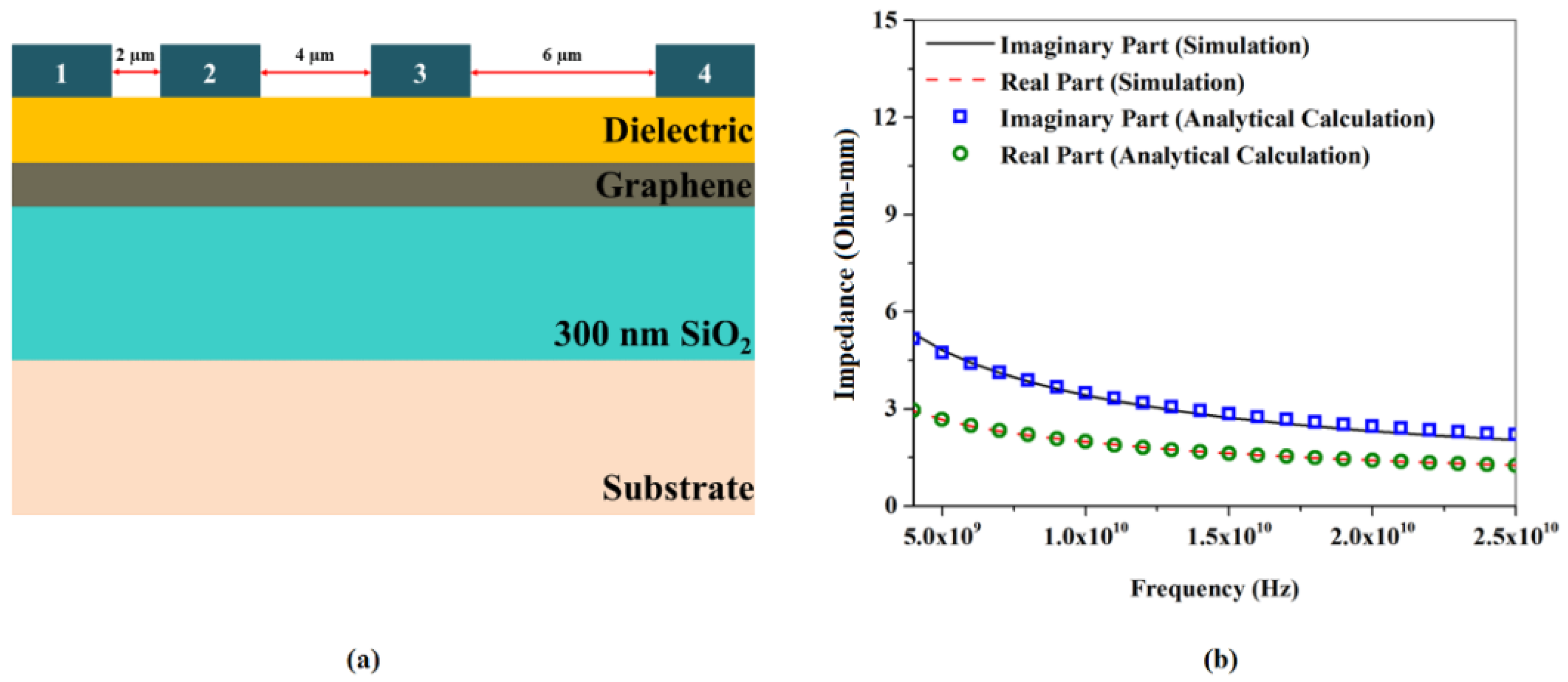

In simulations, the impedance of C3s can be calculated by using RF transmission line method (TLM) structures, with multiple C3s with various in-between distances. Two C3s and the graphene channel in-between is a two-port network, as shown in

Figure 4, and its impedance can be estimated by extracting the two-port S-Parameters and converting them to a B-Parameter [

28]. The real and imaginary parts of the B-parameter are actually the real and imaginary parts of total impedance of the two-port network—two C3 impedances, in addition to the in-between graphene channel resistance.

3. Results and Discussion

We started our analyses by simulating the DC and RF characteristics of a conventional graphene FET, reported in [

29]. This was one of our baseline devices, and we named it GFET-1. The width of this device, as well as that of all other devices simulated in this work, was 100 µm.

The gate length of the baseline GFET-1 was 3 µm, gate dielectric thickness was 24 nm, and the access region length was 1.5 µm, as shown in

Figure 5. Chemical vapor deposition (CVD) graphene with a sheet resistance of 210 Ω/□ and a hole (electron) mobility of 530 cm

2/V·s (336 cm

2/V·s) formed the device channel on 300 nm of SiO

2.

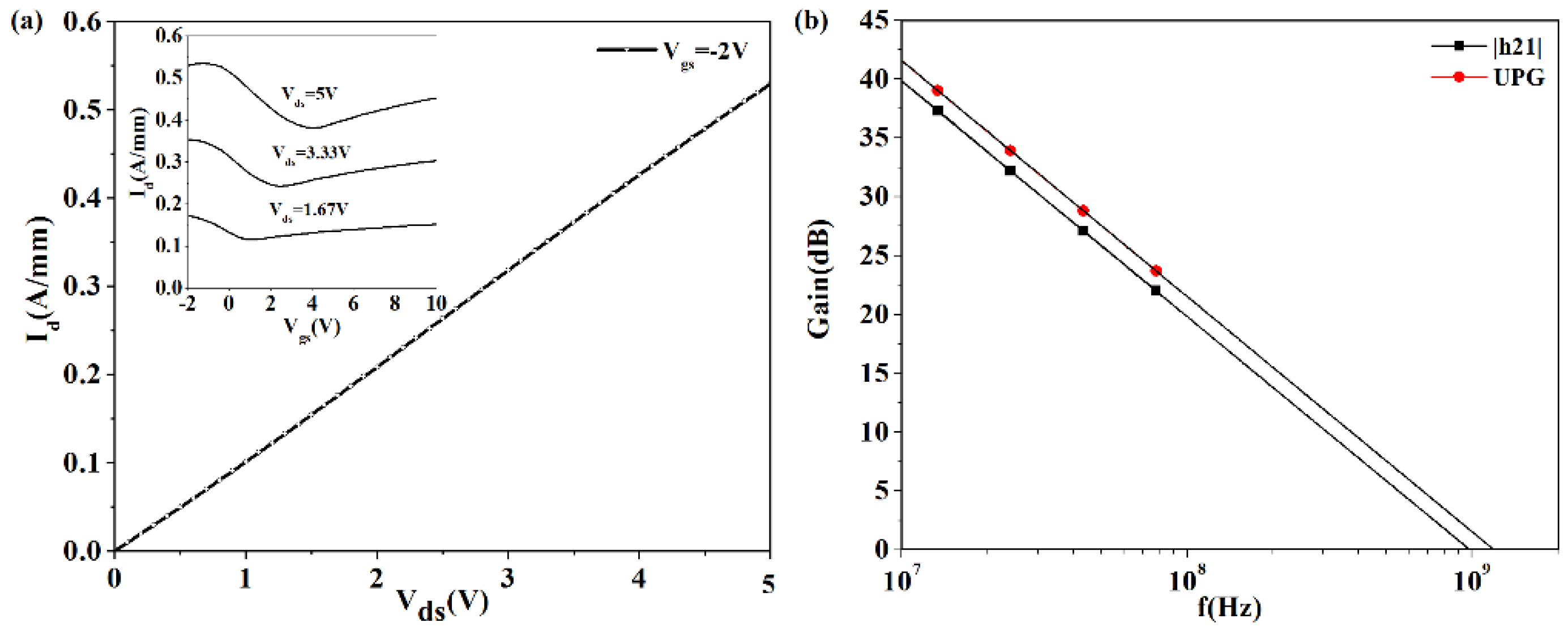

We used a commercially available physically-based numerical technology computer aided design (TCAD) device simulation tool (Silvaco Atlas, Santa Clara, CA, USA) [

30] and a modified material parameter for graphene to simulate and replicate the reported DC and RF characteristics of the baseline GFET-1. The tool solves electromagnetic and transport differential equations to calculate the electrical performance of a device modeled in DC, AC, or in transient modes of operation [

31]. The simulated DC and high frequency characteristics of GFET-1 are shown in

Figure 6. The simulated device characteristics are in a very good agreement with the reported ones [

29], which also validates our method of simulation.

The sheet resistance of the graphene channel extracted from our simulation was 216 Ω/□. We aim to add two C3s to this device and short them to the ohmic contacts to extensively analyze their effects on the device’s high frequency performance.

As a starting point of capacitive impedance simulation, we first simulated a simple capacitor-like structure. It consisted of 30 nm of SiO

2 between two metal contacts, and each metal contact had a contact resistance of 0.7 ohm-mm, as shown in

Figure 7a.

The real and imaginary parts of this capacitive impedance were estimated using simulations, as well as analytical techniques. In

Figure 7b, the real and imaginary parts of the capacitive impedance estimated from simulation and analytical calculations are plotted with respect to frequency. We can see that the results using both methods are in a very good agreement, which validates our simulation technique of estimating capacitive impedance. For further verification, we successfully regenerated the experimental data for III-N RF TLM structures reported in Reference [

27]. To estimate the impedance of the capacitance formed between a C3 and graphene channel with a gate dielectric in-between, we simulated an RF TLM structure on graphene having two C3s with various in-between distances.

The C3s were placed on exactly the same structure as in the baseline GFET-1, consisting of 9 nm of SiO

2 and 15 nm of Al

2O

3 serving as the gate dielectric, deposited on CVD graphene with a carrier mobility the same as that of baseline GFET-1, as shown in

Figure 8a. The impedance between contact 1 and 2, 2 and 3, and 3 and 4 were calculated at a specific single frequency, plotted with respect to distance, and extrapolated up to zero distance to extract the real and imaginary parts of a single C3 impedance at that frequency. This procedure was repeated over the frequency range of 5 GHz to 25 GHz, with a step size of 1 GHz. The real and imaginary parts of C3 impedance, plotted with respect to frequency, are shown in

Figure 8b.

Finally, we simulated the proposed GFET, which has two C3s shorted to the ohmic source/drain contacts of the already simulated baseline GFET-1, as shown in

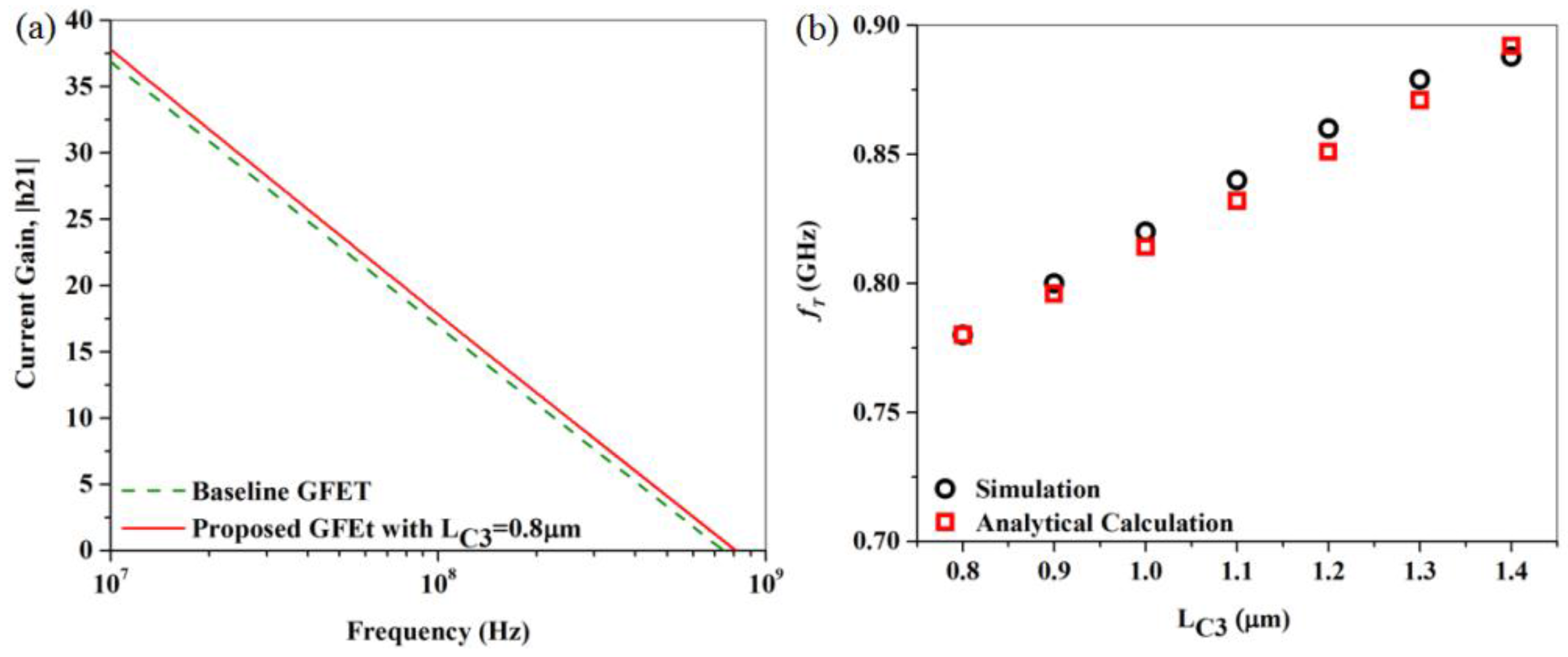

Figure 9. The length of capacitively coupled extension was 0.8 µm in this simulation. The current gain, |h21| of the baseline GFET-1 and the proposed modified version with C3s are plotted with respect to frequency in

Figure 10a. According to the definition, the frequency at which current gain becomes 0 dB is the current gain cut-off frequency,

fT. We can see from

Figure 10a that, for a C3 length of 0.8 µm, the

fT of this proposed GFET reached a value of 0.78 GHz, whereas that of the baseline GFET-1 was 0.74 GHz. In each and every numerical calculation, the gate to source/drain parasitic capacitances have been considered. In addition to that, in analytical calculations, the parasitic capacitances have been estimated using geometric and material parameters. The value of these parasitic capacitances ranged from 3.90 × 10

−13 F to 4.40 × 10

−13 F.

The drain to source voltage, as well as the drain side C3 to source voltage, Vds, was 5.0 V during the frequency domain AC simulation. As the drain bias, as well as the drain side C3 bias, were positive, we considered the GFET electron regime operation so that the drain side C3 bias accumulated more major carriers (electrons) underneath. A gate bias of Vgs = 2 V was used to operate the GFET in the electron regime.

We later gradually increased the length of the C3s. The approaching C3 towards the gate reduced the access region length, as well as access resistance. Additionally, the increment of capacitive coupling area due to the C3 length increment decreased the capacitive impedance. As a result of access resistance decrease, as well as the decrease in capacitive impedance, the

fT of the proposed GFET increased further. The effect of increased C3 length over

fT for this device is shown in

Figure 10b, estimated from both simulations and analytical calculations. As we can see from

Figure 10b, the

fT of this proposed device reached a value of 0.89 GHz for a C3 length of 1.4 μm, whereas it was just 0.78 GHz for a C3 length of 0.8 μm previously. Further incraese of C3 length was studied, and, due to introduction of high parasitic capacitance, it resulted in

fT deterioration.

As the C3 impedance is dependent on frequency and from our results in

Figure 6b, it was found that the real part of C3 impedance is reduced at higher frequencies; we intended to quantify the effect of C3 on RF performance for a shorter channel higher mobility GFETs. To do so, as before, a short channel high mobility GFET, reported in Reference [

23], was chosen as our short channel high mobility baseline, and was named GFET-2. The device had a CVD-grown graphene channel with a carrier mobility of μ = 2234 cm

2/V·s on a sapphire substrate with a gate length of 210 nm, and a source to drain distance of 1.5 μm. We considered the device geometry to be symmetrical and estimated the access region length to be 645 nm on each side of the gate. We simulated the DC and RF characteristics of the baseline GFET-2 as before, and they were in a very good agreement with the reported data [

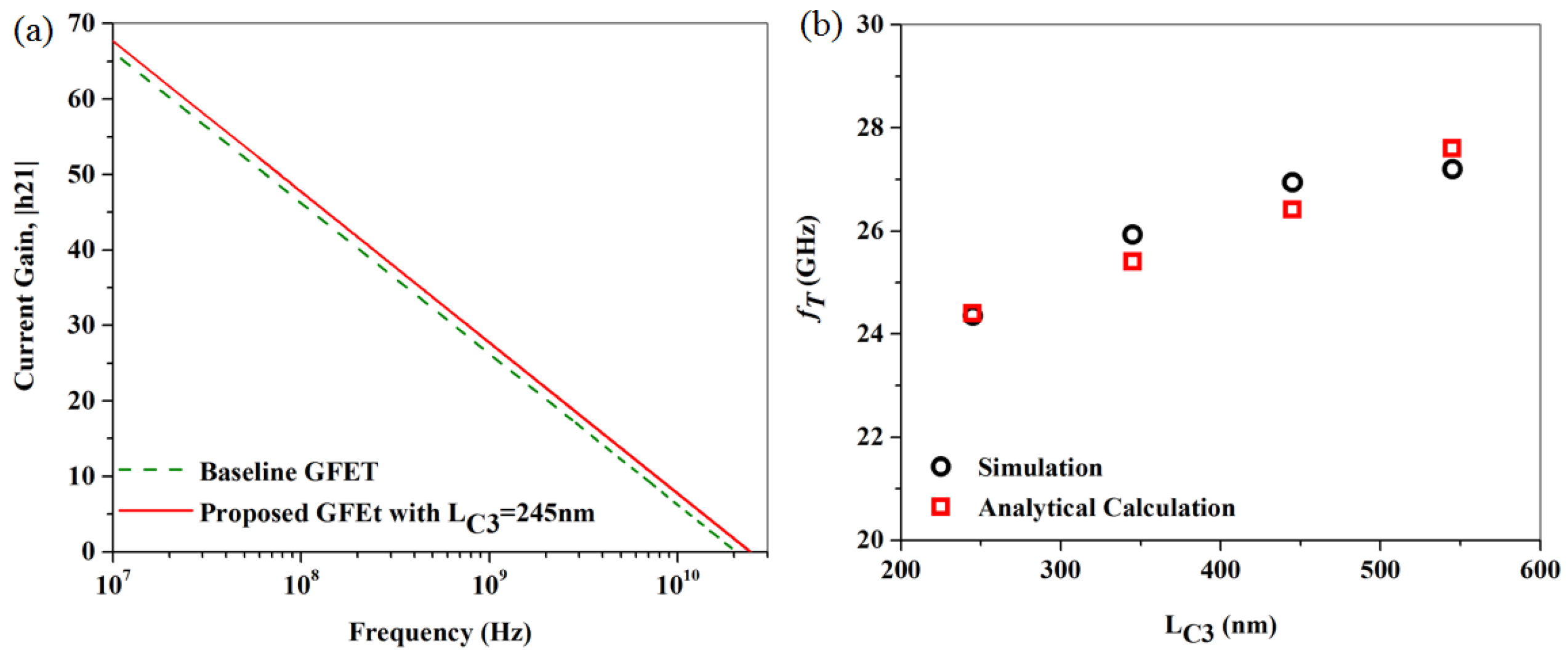

23]. For this simulation, as well as for the following simulations and analytical calculations, the device width was considered to be 100 μm, as before. Later, we simulated our proposed short channel high mobility GFET with a hybrid contact by making a capacitive extension of 245 nm of both the source and the drain towards the gate.

The RF characteristics of the baseline GFET-2 in the electron regime, along with that of the proposed GFET, having a C3 length of 245 nm, are shown in

Figure 11a. From

Figure 11a, we see that the

fT of the baseline reported GFET and the proposed GFET with a 245-nm capacitive extension, are 20.05 GHz and 24.4 GHz, respectively. Later, the C3 length was gradually increase up to 550 nm as shown in

Figure 8b. Due to the increase of the C3 length, the

fT gradually increased and eventually reached a value of 25.9 GHz. As before, further increase of C3 length was studied, and

LC3 = 550 nm was found to be the optimum extension.

In addition to the C3 extension over the access region, we also simulated a GFET with the source to drain distance the same as that of the baseline, but with a longer gate. The new length of the gate was equal to old gate length plus 2LC3, Lg-new = Lg-old + 2LC3. From our simulations, we found that this device does not show any improvement of fT, rather the fT deteriorates compared to the baseline GFET. The reason behind this deterioration is the increase in transit delay. Though the C3 is capacitively coupled to the channel, as the gate contact is, the switching of the device takes place in the gate, not in the C3s. The increase of the gate length increased the transit delay, whereas the equal C3 extension length reduced the parasitic delay.