Role of the Potential Barrier in the Electrical Performance of the Graphene/SiC Interface

Abstract

:1. Introduction

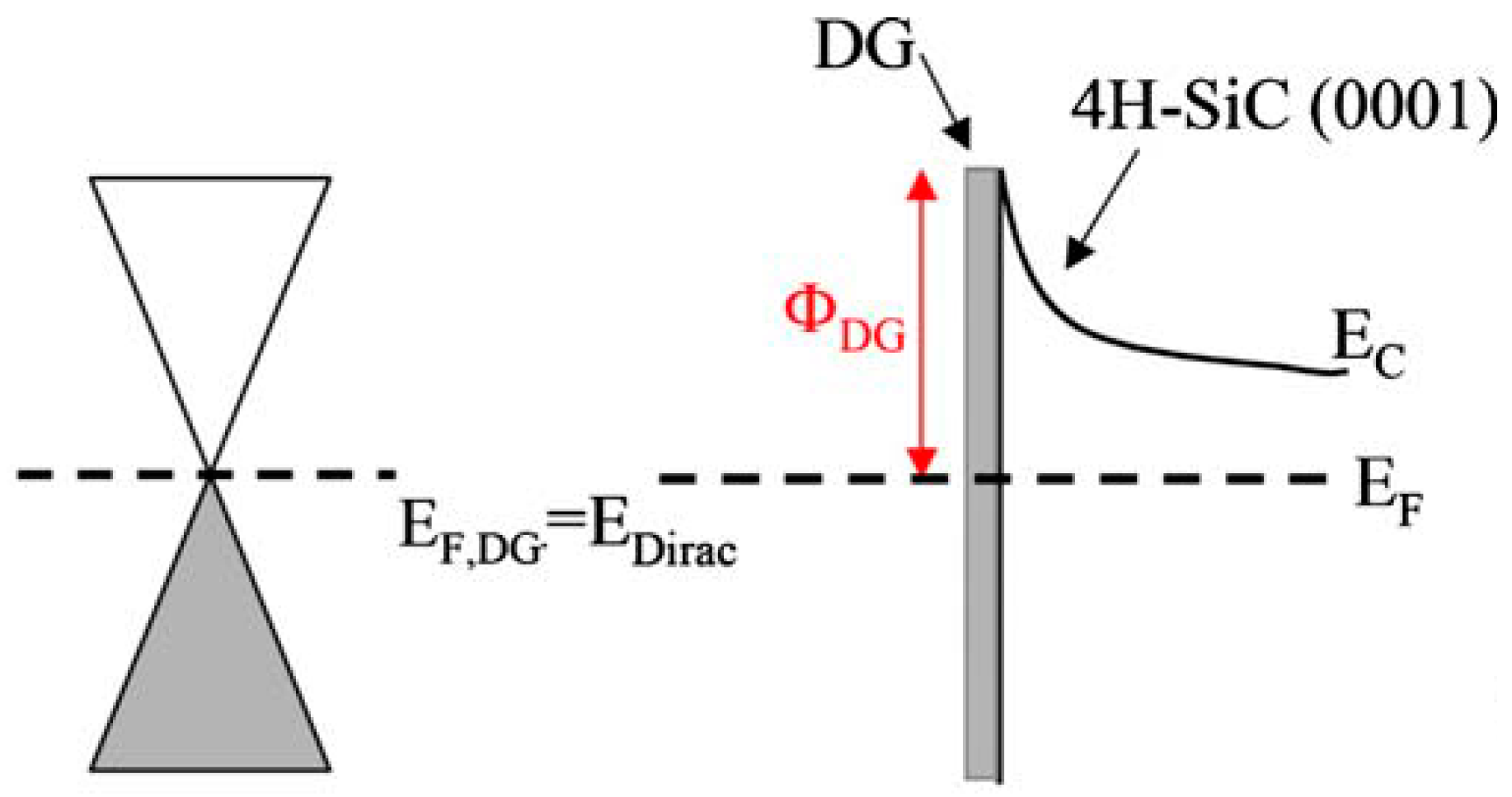

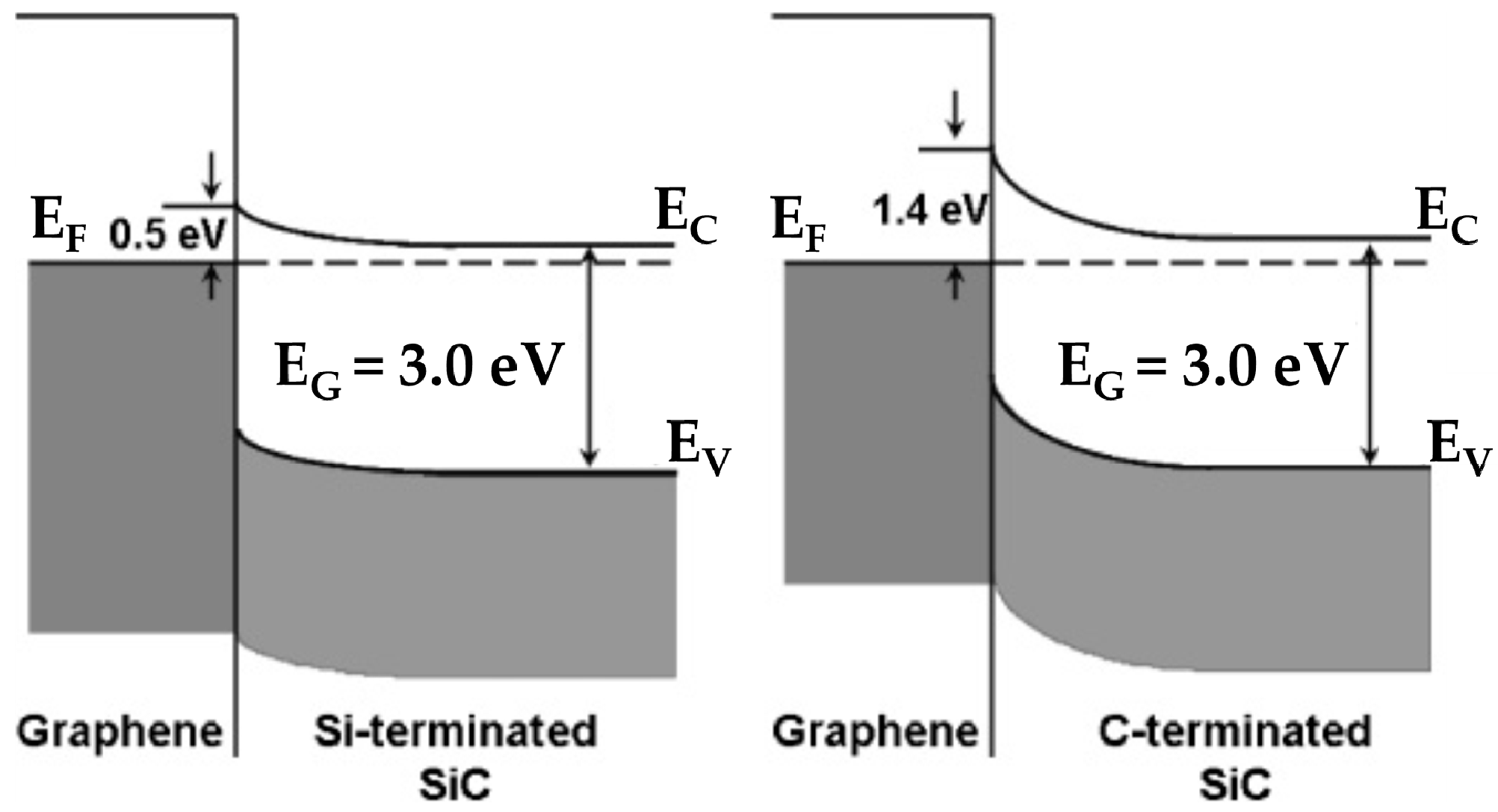

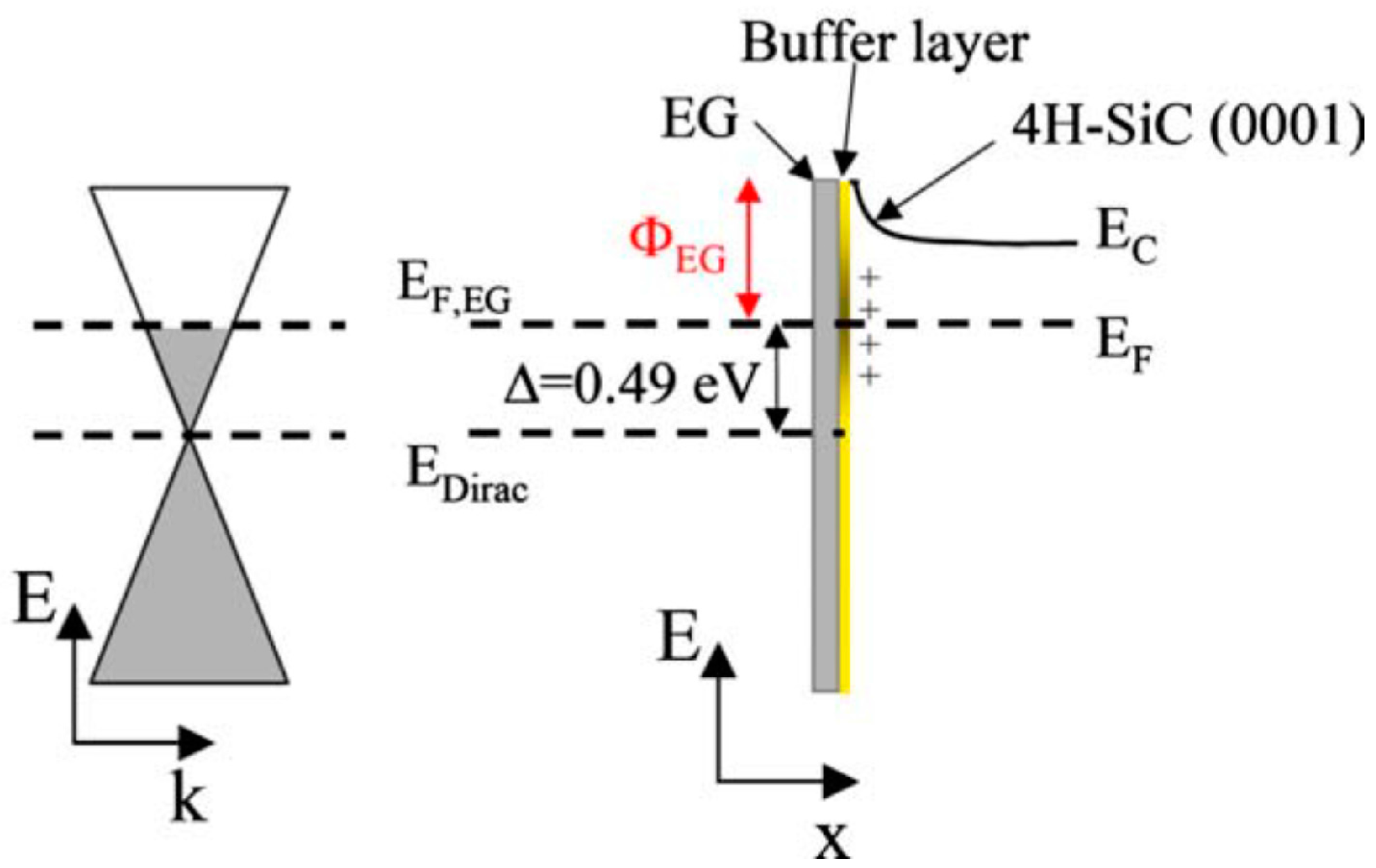

2. Electrical Properties of the Graphene/SiC Interface

- (1)

- The vertical structure for electrical measurements can be prepared by simple mechanical contact between exfoliated graphene and the desired SiC substrate. The starting point of the sample preparation in this case is a mechanical exfoliation of highly-oriented pyrolytic graphite (HOPG) by sticky tape, followed by the application of the exfoliated graphene films onto the SiC surface. From the literature analysis, we know that there are many techniques for the exfoliation of graphite based on common mechanical mechanisms [33].

- (2)

- Graphene formed on the carbon-face SiC by high-temperature thermal decomposition of the SiC substrate can be also chosen as a sample for electrical characterization. Indeed, it has been repeatedly shown that the growth of graphene on the carbon-face SiC substrate does not promote the formation of the buffer layer [34].

- (3)

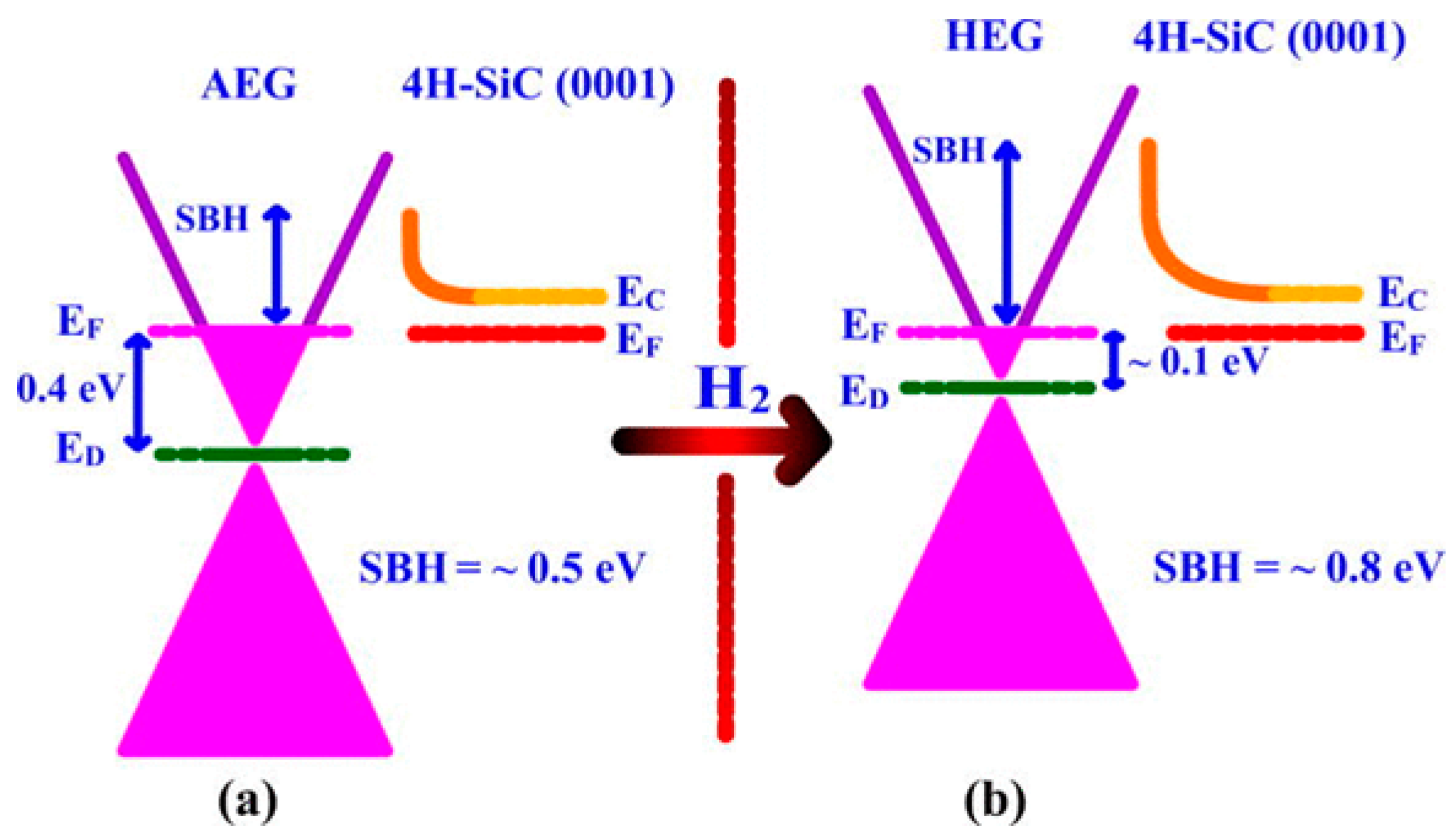

- Another way to avoid the undesirable buffer layer is intercalation of graphene grown on the Si-face SiC substrate by high-temperature Si sublimation. The main scenario for this is to break the covalent bonds between the buffer layer and Si atoms on the SiC surface and to saturate the silicon dangling bonds. Then, the buffer layer can be converted into a new graphene layer with graphene symmetry and typical electronic structure. As was confirmed by experimental studies, H [9,35], Na [36], O [37,38], Li [39], Si [40], Au [12], F [11] and Ge [41] intercalation can transform the buffer layer into a graphene layer with enhanced electrical performance in comparison with untreated monolayer graphene, which exists on the buffer layer. Intercalant species can penetrate into the interface between the buffer layer and the Si-face SiC substrate and create the chemical bonds with topmost Si atoms, thereby causing the transformation of the buffer layer to quasi-free-standing graphene. It is interesting to note that non-metallic (for example, fluorine, oxygen and hydrogen) intercalations are expected to be more effective since they can strongly covalently interact with Si species of the SiC.

3. Experimental Control of the Barrier Height at the Graphene/SiC Interface

- (1)

- If the potential barrier is wide and high (as in the case of stable Schottky diode, formed on the buffer-layer free graphene and SiC), the current is driven by thermal excitation of the electrons and their transfer from the silicon carbide into graphene (thermionic emission).

- (2)

- If the potential barrier at the interface is rather narrow (due to the strong interaction between the buffer layer and the topmost layers of silicon carbide), then current flows due to tunneling through energy barriers regardless of their width and energy height (ohmic contact formation).

- (3)

- In some intermediate cases, epitaxial graphene may consist of sp2-bonded carbon atoms with a small fraction of sp3 hybridized carbon species bound to SiC (less than 30%). It is clear that under such conditions, the currents through the interface are regulated by two competing mechanisms: thermal excitation of carriers and their tunneling through the top of the barrier. In this scenario, a Schottky barrier is high enough to provide rectifying behavior. On the other hand, the leakage current will be increased substantially, thus degrading the performance of the diode.

4. Observations of Uncommon Phenomena at the Graphene/SiC Interface

5. Concluding Remarks

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Emtsev, K.V.; Speck, F.; Seyller, T.; Ley, L.; Riley, J.D. Interaction, growth, and ordering of epitaxial graphene on SiC(0001) surfaces: A comparative photoelectron spectroscopy study. Phys. Rev. B 2008, 77, 155303. [Google Scholar] [CrossRef]

- Emery, J.D.; Detlefs, B.; Karmel, H.J.; Nyakiti, L.O.; Gaskill, D.K.; Hersam, M.C. Chemically Resolved Interface Structure of Epitaxial Graphene on SiC(0001). Phys. Rev. Lett. 2013, 111, 215501. [Google Scholar] [CrossRef] [PubMed]

- Strupinski, W.; Grodecki, K.; Caban, P.; Ciepielewski, P.; Jozwik-Biala, I.; Baranowski, J.M. Formation mechanism of graphene buffer layer on SiC(0001). Carbon 2015, 81, 63. [Google Scholar] [CrossRef]

- Conrad, M.; Wang, F.; Nevius, M.; Jinkins, K.; Celis, A.; Nair, M.N.; Taleb-Ibrahimi, A.; Tejeda, A.; Garreau, Y.; Vlad, A.; et al. Wide Band Gap Semiconductor from a Hidden 2D Incommensurate Graphene Phase. Nano Lett. 2017, 17, 341. [Google Scholar] [CrossRef] [PubMed]

- Stöhr, A.; Forti, S.; Link, S.; Zakharov, A.A.; Kern, K.; Starke, U.; Benia, H.M. Intercalation of graphene on SiC(0001) via ion implantation. Phys. Rev. B 2016, 94, 085431. [Google Scholar] [CrossRef]

- Visikovskiy, A.; Kimoto, S.; Kajiwara, T.; Yoshimura, M.; Iimori, T.; Komori, F.; Tanaka, S. Graphene/SiC(0001) interface structures induced by Si intercalation and their influence on electronic properties of graphene. Phys. Rev. B 2016, 94, 245421. [Google Scholar] [CrossRef]

- Caffrey, N.M.; Johansson, L.I.; Xia, C.; Armiento, R.; Abrikosov, I.A.; Jacobi, C. Structural and electronic properties of Li-intercalated graphene on SiC(0001). Phys. Rev. B 2016, 93, 195421. [Google Scholar] [CrossRef]

- Caffrey, N.M.; Armiento, R.; Yakimova, R.; Abrikosov, I.A. Charge neutrality in epitaxial graphene on 6H-SiC(0001) via nitrogen intercalation. Phys. Rev. B 2015, 92, 081409. [Google Scholar] [CrossRef]

- Riedl, C.; Coletti, C.; Iwasaki, T.; Zakharov, A.A.; Starke, U. Quasi-Free-Standing Epitaxial Graphene on SiC Obtained by Hydrogen Intercalation. Phys. Rev. Lett. 2009, 103, 246804. [Google Scholar] [CrossRef] [PubMed]

- Sandin, A.; Jayasekera, T.; Rowe, J.E.; Kim, K.W.; Nardelli, M.B.; Dougherty, D.B. Multiple coexisting intercalation structures of sodium in epitaxial graphene-SiC interfaces. Phys. Rev. B 2012, 85, 125410. [Google Scholar] [CrossRef]

- Walter, A.; Jeon, K.-J.; Bostwick, A.; Speck, F.; Ostler, M.; Seyller, T.; Moreschini, L.; Kim, Y.S.; Chang, Y.J.; Horn, K.; et al. Highly p-doped epitaxial graphene obtained by fluorine intercalation. Appl. Phys. Lett. 2011, 98, 184102. [Google Scholar] [CrossRef]

- Gierz, I.; Suzuki, T.; Weitz, R.T.; Lee, D.S.; Krauss, B.; Riedl, C.; Starke, U.; Höchst, H.; Smet, J.H.; Ast, C.R.; et al. Electronic decoupling of an epitaxial graphene monolayer by gold intercalation. Phys. Rev. B 2010, 81, 235408. [Google Scholar] [CrossRef]

- Hsu, C.-H.; Ozolins, V.; Chuang, F.-C. First-principles study of Bi and Sb intercalated graphene on SiC(0001) substrate. Surf. Sci. 2013, 616, 149–154. [Google Scholar] [CrossRef]

- Huang, L.; Xu, W.-Y.; Que, Y.-D.; Mao, J.-H.; Meng, L.; Pan, L.-D.; Li, G.; Wang, Y.-L.; Du, S.-X.; Liu, C.; et al. Intercalation of metals and silicon at the interface of epitaxial graphene and its substrates. Chin. Phys. B 2013, 22, 096803. [Google Scholar] [CrossRef]

- Sonde, S.; Giannazzo, F.; Raineri, V.; Yakimova, R.; Huntzinger, J.-R.; Tiberj, A.; Camassel, J. Electrical properties of the graphene/4H-SiC(0001) interface probed by scanning current spectroscopy. Phys. Rev. B 2009, 80, 241406. [Google Scholar] [CrossRef]

- Renault, O.; Pascon, A.M.; Rotella, H.; Kaja, K.; Mathieu, C.; Rault, J.E.; Blaise, P.; Poiroux, T.; Barrett, N.; Fonseca, L.R.C. Charge spill-out and work function of few-layer graphene on SiC(0001). J. Phys. D Appl. Phys. 2014, 47, 295303. [Google Scholar] [CrossRef]

- Červenka, J.; van de Ruit, K.; Flipse, C.F.J. Giant inelastic tunneling in epitaxial graphene mediated by localized states. Phys. Rev. B 2010, 81, 205403. [Google Scholar] [CrossRef]

- Rotenberg, E.; Bostwick, A.; Ohta, T.; McChesney, J.L.; Seyller, T.; Horn, K. Origin of the energy bandgap in epitaxial graphene. Nature Mater. 2008, 7, 258. [Google Scholar] [CrossRef] [PubMed]

- Nevius, M.S.; Conrad, M.; Wang, F.; Celis, A.; Nair, M.N.; Taleb-Ibrahimi, A.; Tejeda, A.; Conrad, E.H. Semiconducting Graphene from Highly Ordered Substrate Interactions. Phys. Rev. B 2015, 115, 136802. [Google Scholar] [CrossRef] [PubMed]

- Nair, M.N.; Palacio, I.; Celis, A.; Zobelli, A.; Gloter, A.; Kubsky, S.; Turmaud, J.-P.; Conrad, M.; Berger, C.; de Heer, W.; et al. Band Gap Opening Induced by the Structural Periodicity in Epitaxial Graphene Buffer Layer. Nano Lett. 2017, 17, 2681–2689. [Google Scholar] [CrossRef] [PubMed]

- Hertel, S.; Waldmann, D.; Jobst, J.; Albert, A.; Albrecht, M.; Reshanov, S.; Schöner, A.; Krieger, M.; Weber, H.B. Tailoring the graphene/silicon carbide interface for monolithic wafer-scale electronics. Nat. Commun. 2012, 3, 957. [Google Scholar] [CrossRef] [PubMed]

- Shtepliuk, I.; Eriksson, J.; Khranovskyy, V.; Iakimov, T.; Lloyd Spetz, A.; Yakimova, R. Monolayer graphene/SiC Schottky barrier diodes with improved barrier height uniformity as a sensing platform for the detection of heavy metals. Beilstein. J. Nanotechnol. 2016, 7, 1800. [Google Scholar] [CrossRef] [PubMed]

- Anderson, T.J.; Hobart, K.D.; Nyakiti, L.O.; Wheeler, V.D.; Myers-Ward, R.L.; Caldwell, J.D.; Bezares, F.J.; Jernigan, G.G.; Tadjer, M.J.; Imhoff, E.A.; et al. Investigation of the Epitaxial Graphene/p-SiC Heterojunction. IEEE Electron. Device Lett. 2012, 33, 1610. [Google Scholar] [CrossRef]

- Mikoushkin, V.M.; Shnitov, V.V.; Lebedev, A.A.; Lebedev, S.P.; Nikonov, S.Y.; Vilkov, O.Y.; Iakimov, T.; Yakimova, R. Size confinement effect in graphene grown on 6H-SiC(0001) substrate. Carbon 2015, 86, 139. [Google Scholar] [CrossRef]

- Xu, Z.; Buehler, M.J. Heat dissipation at a graphene—Substrate interface. J. Phys. Condens. Matter 2012, 24, 475305. [Google Scholar] [CrossRef] [PubMed]

- Hu, M.; Poulikakos, D. Graphene mediated thermal resistance reduction at strongly coupled interfaces. Int. J. Heat Mass Transfer. 2013, 62, 205. [Google Scholar] [CrossRef]

- Li, M.; Zhang, J.; Hu, X.; Yue, Y. Thermal transport across graphene/SiC interface: Effects of atomic bond and crystallinity of substrate. Appl. Phys. A 2015, 119, 415. [Google Scholar] [CrossRef]

- Wang, Z.; Bi, K.; Guan, H.; Wang, J. Thermal Transport between Graphene Sheets and SiC Substrate by Molecular-Dynamical Calculation. J. Mater. 2014, 479808. [Google Scholar] [CrossRef]

- Giesbers, A.J.M.; Uhlířová, K.; Konečný, M.; Peters, E.C.; Burghard, M.; Aarts, J.C.; Flipse, F.J. Interface-Induced Room-Temperature Ferromagnetism in Hydrogenated Epitaxial Graphene. Phys. Rev. Lett. 2013, 111, 166101. [Google Scholar] [CrossRef] [PubMed]

- Zhou, P.; He, D. Modulating doping and interface magnetism of epitaxial graphene on SiC(0001). Chin. Phys. B 2016, 25, 017302. [Google Scholar] [CrossRef]

- Yu, Y.J.; Zhao, Y.; Ryu, S.; Brus, L.E.; Kim, K.S.; Kim, P. Tuning the Graphene Work Function by Electric Field Effect. Nano Lett. 2009, 9, 3430. [Google Scholar] [CrossRef] [PubMed]

- Castro Neto, A.H.; Guinea, F.; Peres, N.M.R.; Novoselov, K.S.; Geim, A.K. The electronic properties of graphene. Rev. Mod. Phys. 2009, 81, 109–162. [Google Scholar] [CrossRef]

- Yi, M.; Shen, Z. A review on mechanical exfoliation for the scalable production of graphene. J. Mater. Chem. A 2015, 3, 11700–11715. [Google Scholar] [CrossRef]

- Hass, J.; Varchon, F.; Millán-Otoya, J.E.; Sprinkle, M.; Sharma, N.; de Heer, W.A.; Berger, C.; First, P.N.; Magaud, L.; Conrad, E.H. Why Multilayer Graphene on 4H’SiC(0001) Behaves Like a Single Sheet of Graphene. Phys. Rev. Lett. 2008, 100, 125504. [Google Scholar] [CrossRef] [PubMed]

- Virojanadara, C.; Zakharov, A.A.; Yakimova, R.; Johansson, L.I. Buffer layer free large area bi-layer graphene on SiC(0001). Surf. Sci. 2010, 604, L4–L7. [Google Scholar] [CrossRef]

- Xia, C.; Watcharinyanon, S.; Zakharov, A.A.; Johansson, L.I.; Yakimova, R.; Virojanadara, C. Detailed studies of Na intercalation on furnace-grown graphene on 6H-SiC(0001). Surf. Sci. 2013, 613, 88–94. [Google Scholar] [CrossRef]

- Kowalski, G.; Tokarczyk, M.; Dąbrowski, P.; Ciepielewski, P.; Możdżonek, M.; Strupiński, W.; Baranowski, J.M. New X-ray insight into oxygen intercalation in epitaxial graphene grown on 4H-SiC(0001). J. Appl. Phys. 2015, 117, 105301. [Google Scholar] [CrossRef]

- Oliveira, M.H., Jr.; Schumann, T.; Fromm, F.; Koch, R.; Ostler, M.; Ramsteiner, M.; Seyller, T.; Lopes, J.M.J.; Riechert, H. Formation of high-quality quasi-free-standing bilayer graphene on SiC(0001) by oxygen intercalation upon annealing in air. Carbon 2013, 52, 83–89. [Google Scholar] [CrossRef]

- Virojanadara, C.; Watcharinyanon, S.; Zakharov, A.A.; Johansson, L.J. Epitaxial graphene on 6H-SiC and Li intercalation. Phys. Rev. B 2010, 82, 205402. [Google Scholar] [CrossRef]

- Xia, C.; Watcharinyanon, S.; Zakharov, A.A.; Yakimova, R.; Hultman, L.; Johansson, L.J.; Virojanadara, C. Si intercalation/deintercalation of graphene on 6H-SiC(0001). Phys. Rev. B 2012, 85, 045418. [Google Scholar] [CrossRef]

- Emtsev, K.V.; Zakharov, A.A.; Coletti, C.; Forti, S.; Starke, U. Ambipolar doping in quasifree epitaxial graphene on SiC(0001) controlled by Ge intercalation. Phys. Rev. B 2011, 84, 125423. [Google Scholar] [CrossRef]

- Chen, W.; Chen, S.; Ni, Z.H.; Huang, H.; Qi, D.C.; Gao, X.Y.; Shen, Z.X.; Wee, A.T.S. Band-Bending at the Graphene–SiC Interfaces: Effect of the Substrate. Jpn. J. Appl. Phys. 2010, 49, 01AH05. [Google Scholar] [CrossRef]

- Tejeda, A.; Taleb-Ibrahimi, A.; de Heer, W.; Berger, C.; Conrad, E.H. Electronic structure of epitaxial graphene grown on the C-face of SiC and its relation to the structure. New J. Phys. 2012, 14, 125007. [Google Scholar] [CrossRef]

- Jayasekera, T.; Xu, S.; Kim, K.W.; Nardelli, M.B. Electronic properties of the graphene/6H-SiC(0001) interface: A first-principles study. Phys. Rev. B 2011, 84, 035442. [Google Scholar] [CrossRef]

- Dharmaraj, P.; Justin Jesuraj, P.; Jeganathan, K. Tuning a Schottky barrier of epitaxial graphene/4H-SiC(0001) by hydrogen intercalation. Appl. Phys. Lett. 2016, 108, 051605. [Google Scholar] [CrossRef]

- Hannon, J.B.; Copel, M.; Tromp, R.M. Direct Measurement of the Growth Mode of Graphene on SiC(0001) and SiC(0001). Phys. Rev. Lett. 2011, 107, 166101. [Google Scholar] [CrossRef] [PubMed]

- Hertel, S.; Finkler, A.; Krieger, M.; Weber, H.B. Graphene Ohmic Contacts to n-type Silicon Carbide (0001). Mater. Sci. Forum 2015, 821–823, 933–936. [Google Scholar] [CrossRef]

- Mammadov, S.; Ristein, J.; Krone, J.; Raidel, C.; Wanke, M.; Wiesmann, V.; Speck, F.; Seyller, T. Work function of graphene multilayers on SiC(0001). 2D Mater. 2017, 4, 015043. [Google Scholar] [CrossRef]

- Tomer, D.; Rajput, S.; Hudy, L.J.; Li, C.H.; Li, L. Tuning a Schottky barrier of epitaxial graphene/4H-SiC(0001) by hydrogen intercalation. Appl. Phys. Lett. 2014, 105, 021607. [Google Scholar] [CrossRef]

- Zhong, H.; Xu, K.; Liu, Z.; Xu, G.; Shi, L.; Fan, Y.; Wang, J.; Ren, G.; Yang, H. Charge transport mechanisms of graphene/semiconductor Schottky barriers: A theoretical and experimental study. J. Appl. Phys. 2014, 115, 013701. [Google Scholar] [CrossRef]

- Rajput, S.; Chen, M.X.; Liu, Y.; Li, Y.Y.; Weinert, M.; Li, L. Spatial fluctuations in barrier height at the graphene-silicon carbide Schottky junction. Nat. Commun. 2013, 4, 2752. [Google Scholar] [CrossRef] [PubMed]

- Seyller, T.; Emtsev, K.V.; Speck, F.; Gao, K.-Y.; Ley, L. Schottky barrier between 6H-SiC and graphite: Implications for metal/SiC contact formation. Appl. Phys. Lett. 2006, 88, 242103. [Google Scholar] [CrossRef]

- Shivaraman, S.; Herman, L.H.; Rana, F.; Park, J.; Spencer, M.G. Schottky barrier inhomogeneities at the interface of few layer epitaxial graphene and silicon carbide. Appl. Phys. Lett. 2012, 100, 183112. [Google Scholar] [CrossRef]

- Sonde, S.; Giannazzo, F.; Raineri, V.; Rimini, E. Investigation of graphene–SiC interface by nanoscale electrical characterization. Phys. Status Solidi B 2010, 247, 912–915. [Google Scholar] [CrossRef]

- Yakimova, R.; Iakimov, T.; Syväjärvi, M. Process for Growth of Graphene. U.S. Patent US9150417B2, 6 October 2015. [Google Scholar]

- Yager, T.; Lartsev, A.; Yakimova, R.; Lara-Avila, S.; Kubatkin, S. Wafer-scale homogeneity of transport properties in epitaxial graphene on SiC. Carbon 2015, 87, 409–414. [Google Scholar] [CrossRef]

- Eriksson, J.; Pearce, R.; Iakimov, T.; Virojanadara, C.; Gogova, D.; Andersson, M.; Syväjärvi, M.; Lloyd Spetz, A.; Yakimova, R. The influence of substrate morphology on thickness uniformity and unintentional doping of epitaxial graphene on SiC. Appl. Phys. Lett. 2012, 100, 241607. [Google Scholar] [CrossRef]

- Yazdi, G.; Vasiliauskas, R.; Iakimov, T.; Zakharov, A.; Syväjärvi, M.; Yakimova, R. Growth of large area monolayer graphene on 3C-SiC and a comparison with other SiC polytypes. Carbon 2013, 57, 477. [Google Scholar] [CrossRef]

- Virojanadara, C.; Syväjarvi, M.; Yakimova, R.; Johansson, L.; Zakharov, A.; Balasubramanian, T. Homogeneous large-area graphene layer growth on 6H-SiC(0001). Phys. Rev. B 2008, 78, 1. [Google Scholar] [CrossRef]

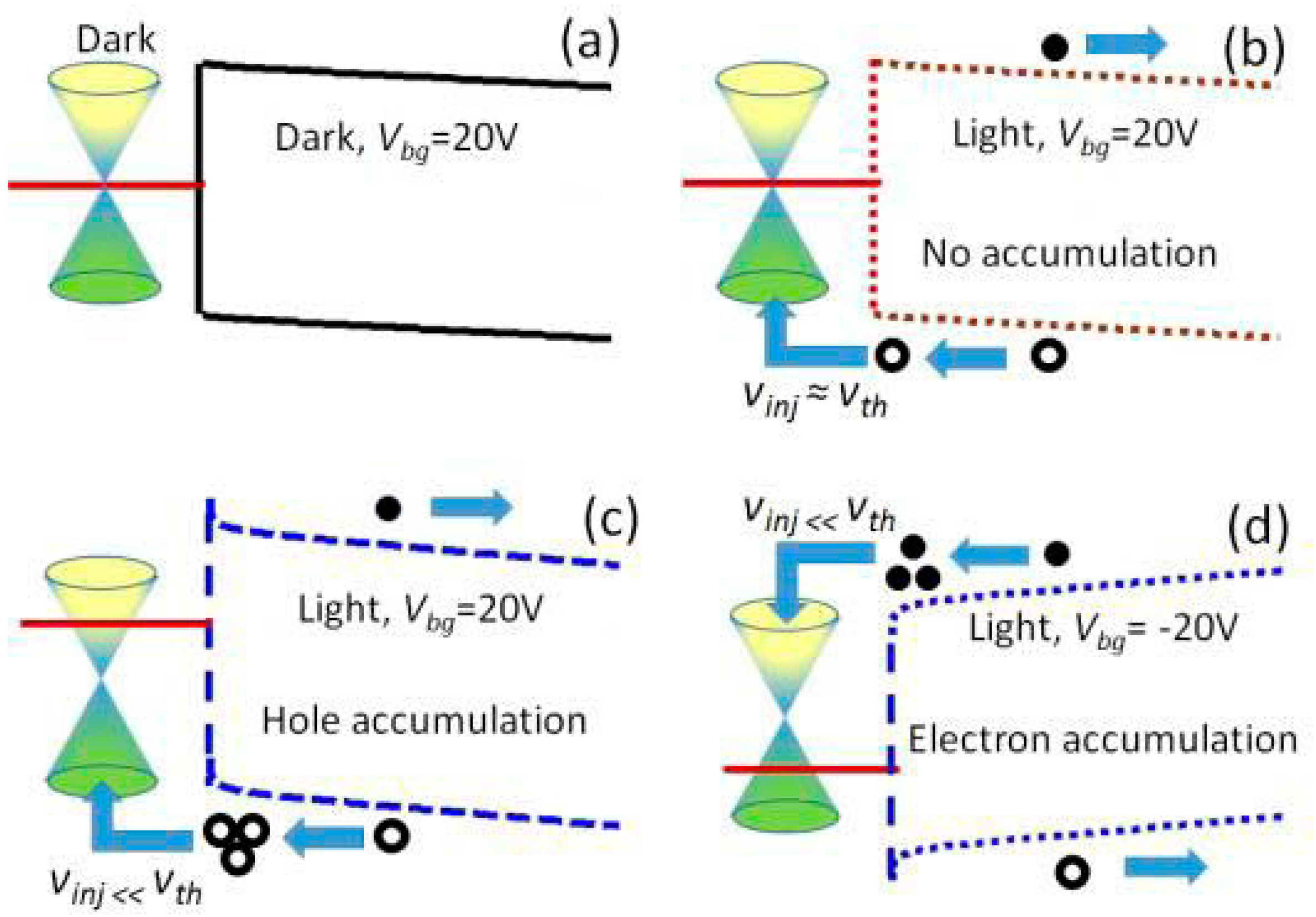

- Butt, N.Z.; Sarker, B.K.; Chen, Y.P.; Alam, M.A. Substrate-Induced Photofield Effect in Graphene Phototransistors. IEEE Trans. Electron. Devices 2015, 62, 3734. [Google Scholar] [CrossRef]

- Anderson, T.J.; Hobart, K.D.; Greenlee, J.D.; Shahin, D.I.; Koehler, A.D.; Tadjer, M.J.; Imhoff, E.A.; Myers-Ward, R.L.; Christou, A.; Kub, F.J. Ultraviolet detector based on graphene/SiC heterojunction. Appl. Phys. Express 2015, 8, 041301. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Wiley: New York, NJ, USA, 2007; pp. 127–172. [Google Scholar]

- Cumpson, P.J.; Seah, M.P. Elastic Scattering Corrections in AES and XPS. II. Estimating Attenuation Lengths and Conditions Required for their Valid Use in Overlayer/Substrate Experiments. Surf. Interface Anal. 1997, 25, 430. [Google Scholar] [CrossRef]

- Johansson, L.I.; Owman, F.; Mårtensson, P. High-resolution core-level study of 6H-SiC(0001). Phys. Rev. B 1996, 53, 13793. [Google Scholar] [CrossRef]

- Tadjer, M.J.; Anderson, T.J.; Hobart, K.D.; Nyakiti, L.O.; Wheeler, V.D.; Myers-Ward, R.L.; Gaskill, D.K.; Eddy, C.R., Jr.; Kub, F.J.; Calle, F. Vertical conduction mechanism of the epitaxial graphene/n-type 4H-SiC heterojunction at cryogenic temperatures. Appl. Phys. Lett. 2012, 100, 193506. [Google Scholar] [CrossRef]

- Dharmaraj, P.; Jeganathan, K.; Parthiban, S.; Kwon, J.Y.; Gautam, S.; Chae, K.H.; Asokan, K. Selective area growth of Bernal bilayer epitaxial graphene on 4H-SiC(0001) substrate by electron-beam irradiation. Appl. Phys. Lett. 2014, 105, 181601. [Google Scholar] [CrossRef]

- Tongay, S.; Lemaitre, M.; Miao, X.; Gila, B.; Appleton, B.R.; Hebard, A.F. Rectification at Graphene-Semiconductor Interfaces: Zero-Gap Semiconductor-Based Diodes. Phys. Rev. X 2012, 2, 011002. [Google Scholar] [CrossRef]

- Giannazzo, F.; Hertel, S.; Albert, A.; La Magna, A.; Roccaforte, F.; Krieger, M.; Weber, H.B. Electrical Nanocharacterization of Epitaxial Graphene/Silicon Carbide Schottky Contacts. Mater. Sci. Forum. 2014, 778–780, 1142–1145. [Google Scholar] [CrossRef]

- Tongay, S.; Schumann, T.; Hebard, A.F. Graphite based Schottky diodes formed on Si, GaAs, and 4H-SiC substrates. Appl. Phys. Lett. 2009, 95, 222103. [Google Scholar] [CrossRef]

- Shtepliuk, I.; Khranovskyy, V.; Yakimova, R. Combining graphene with silicon carbide: Synthesis and properties—A review. Semicond. Sci. Technol. 2016, 31, 113004. [Google Scholar] [CrossRef]

| Junction | Growth Method | Thickness | Barrier Height, eV | Reference |

|---|---|---|---|---|

| Gr/n-4H-SiC | Si sublimation | 1–8 ML | 0.36 ± 0.1 | [15] |

| Gr/n-4H-SiC | Exfoliation | Few ML | 0.85 ± 0.06 | [15] |

| Gr/n-Si-6H-SiC | Thermal decomposition | 2 ML | 0.9 | [21] |

| Gr/n-Si-4H-SiC | Si sublimation | 1 ML | 0.487 ± 0.013 | [22] |

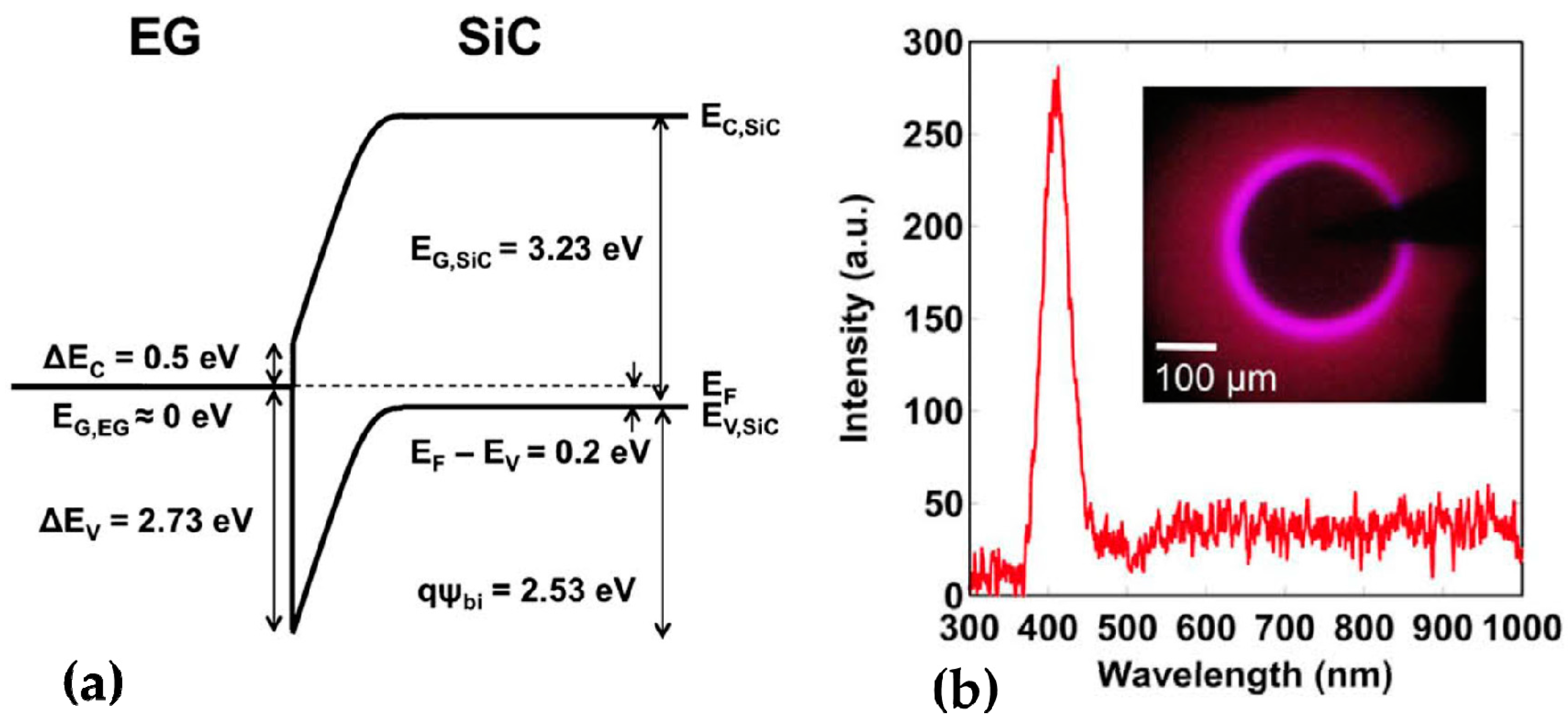

| Gr/p-4H-SiC | Si sublimation | 1 ML | 2.53 | [23] |

| Gr/n-Si-6H-SiC | Si sublimation | 1.6 ML | 2.90 | [24] |

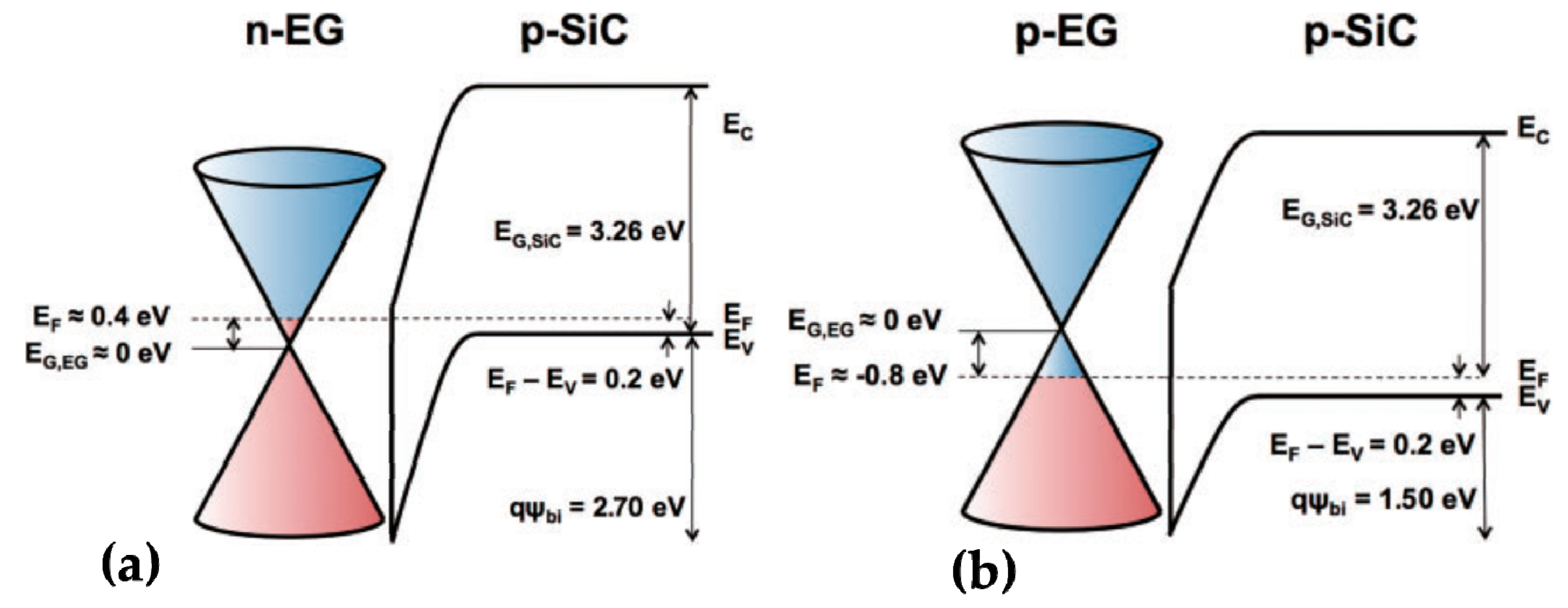

| p-Gr/p-4H-SiC | Si sublimation | 3 ML | 1.5 | [45] |

| Gr/n-Si-4H-SiC | Low energy e-beam irradiation | 1 ML | 0.556 ± 0.05 | [45] |

| Gr/n-Si-4H-SiC | CVD | 1 ML | 1.16 ± 0.16 | [49] |

| Gr/n-C-4H-SiC | CVD | 1 ML | 1.306 ± 0.18 | [49] |

| Gr/n-SiC | Exfoliation | Few ML | 0.28 ± 0.02 | [50] |

| Gr/n-Si-6H-SiC | CVD | 1 ML | 0.35 ± 0.05 | [51] |

| Gr/n-C-4H-SiC | CVD | 1 ML | 0.39 ± 0.04 | [51] |

| Graphite/p-4H-SiC | Solid state graphitization | Multilayer | 2.7 ± 0.1 | [52] |

| Graphite/n-4H-SiC | Solid state graphitization | Multilayer | 0.3 ± 0.1 | [52] |

| Gr/n-Si-4H-SiC | Thermal decomposition | Few ML | 1.066 ± 0.12 | [53] |

| Gr/n-4H-SiC | Exfoliation of HOPG | Multilayer | 0.8 ± 0.1 | [54] |

| n-Gr/p-4H-SiC | Si sublimation | 3 ML | 2.7 | [61] |

| Gr/n-4H-SiC | Si sublimation | Few ML | 0.08 | [65] |

| Gr/n-Si-4H-SiC | Electron-beam irradiation | 2 ML | 0.58 | [66] |

| Gr/n-4H-SiC | CVD | 1 ML | 0.91 | [67] |

| Gr/n-Si-6H-SiC | Thermal decomposition | 2 ML | 1.15–1.45 | [68] |

| HOPG/n-SiC | Van der Waals adherence of cleaved HOPG | Multilayer | 1.15 | [69] |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shtepliuk, I.; Iakimov, T.; Khranovskyy, V.; Eriksson, J.; Giannazzo, F.; Yakimova, R. Role of the Potential Barrier in the Electrical Performance of the Graphene/SiC Interface. Crystals 2017, 7, 162. https://doi.org/10.3390/cryst7060162

Shtepliuk I, Iakimov T, Khranovskyy V, Eriksson J, Giannazzo F, Yakimova R. Role of the Potential Barrier in the Electrical Performance of the Graphene/SiC Interface. Crystals. 2017; 7(6):162. https://doi.org/10.3390/cryst7060162

Chicago/Turabian StyleShtepliuk, Ivan, Tihomir Iakimov, Volodymyr Khranovskyy, Jens Eriksson, Filippo Giannazzo, and Rositsa Yakimova. 2017. "Role of the Potential Barrier in the Electrical Performance of the Graphene/SiC Interface" Crystals 7, no. 6: 162. https://doi.org/10.3390/cryst7060162