A ΣΔ Closed-Loop Interface for a MEMS Accelerometer with Digital Built-In Self-Test Function

Abstract

:1. Introduction

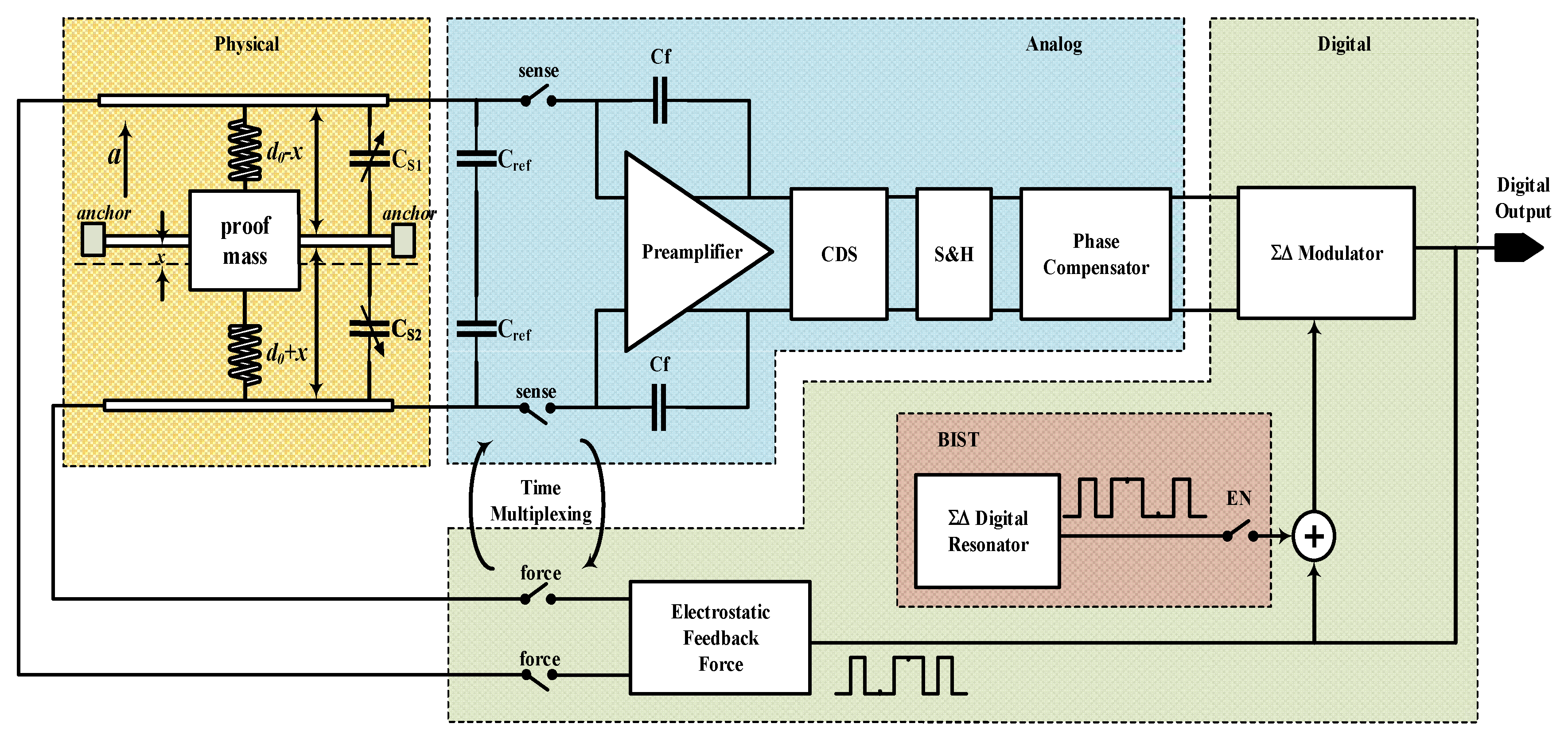

2. System Description and Topology Analysis

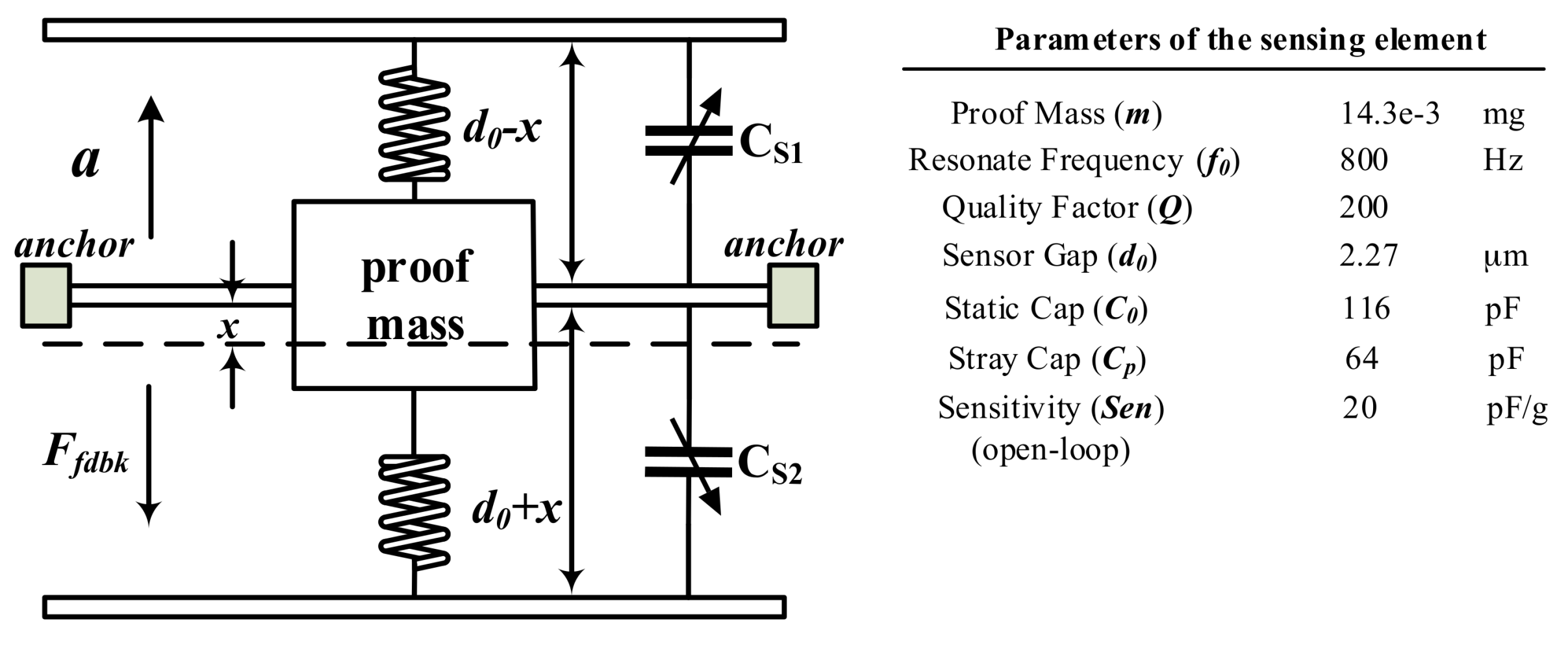

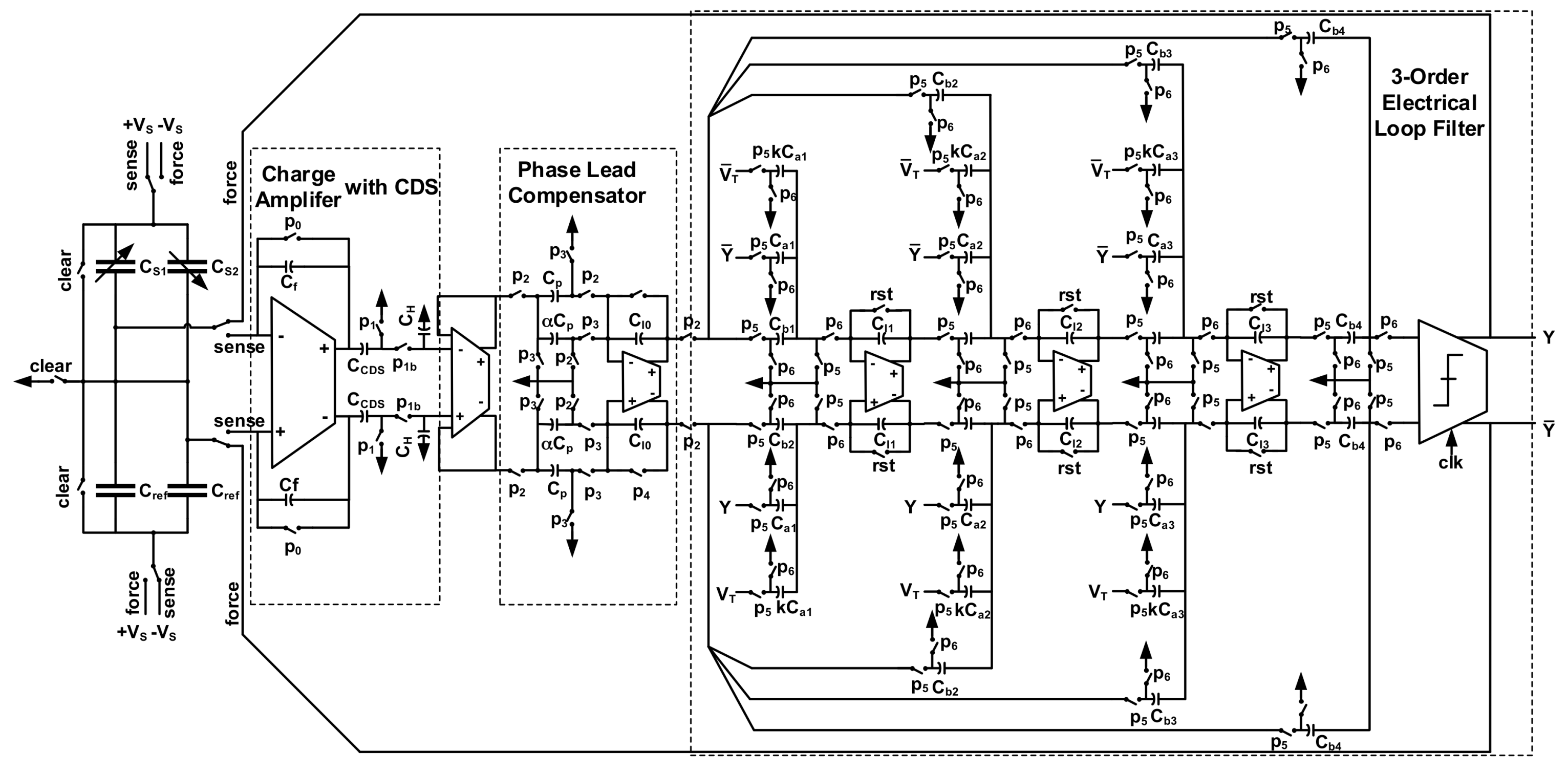

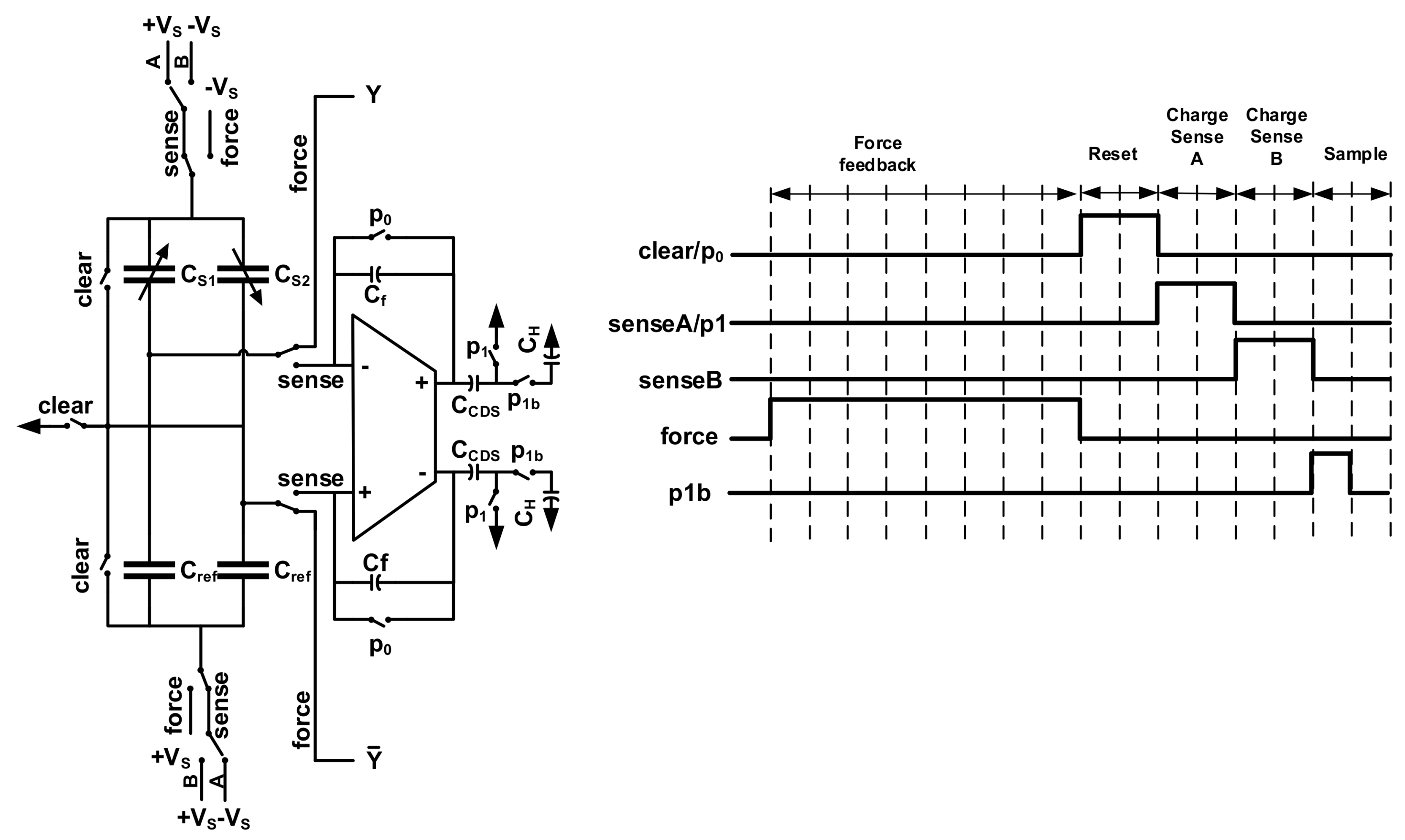

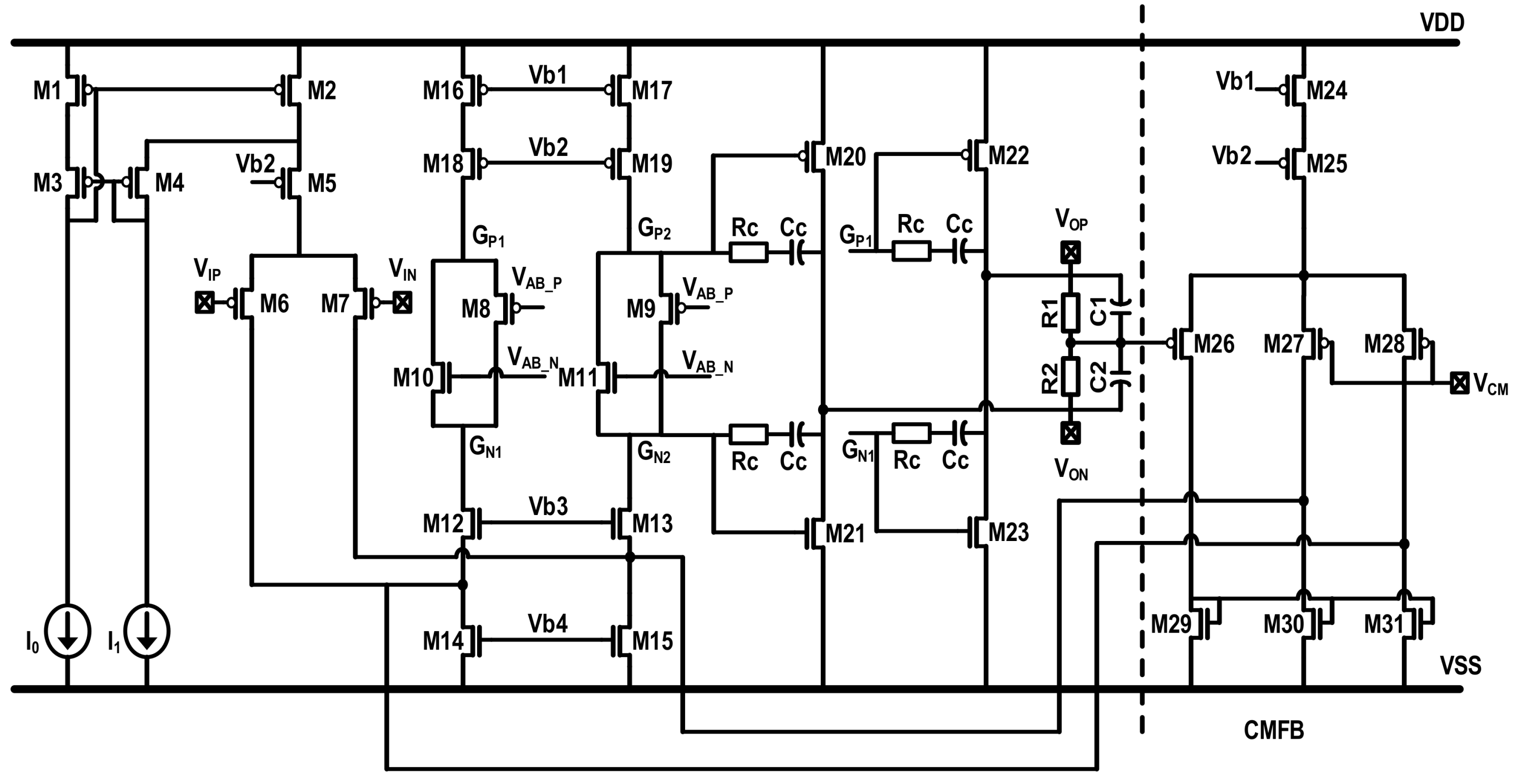

2.1. Sensing Element

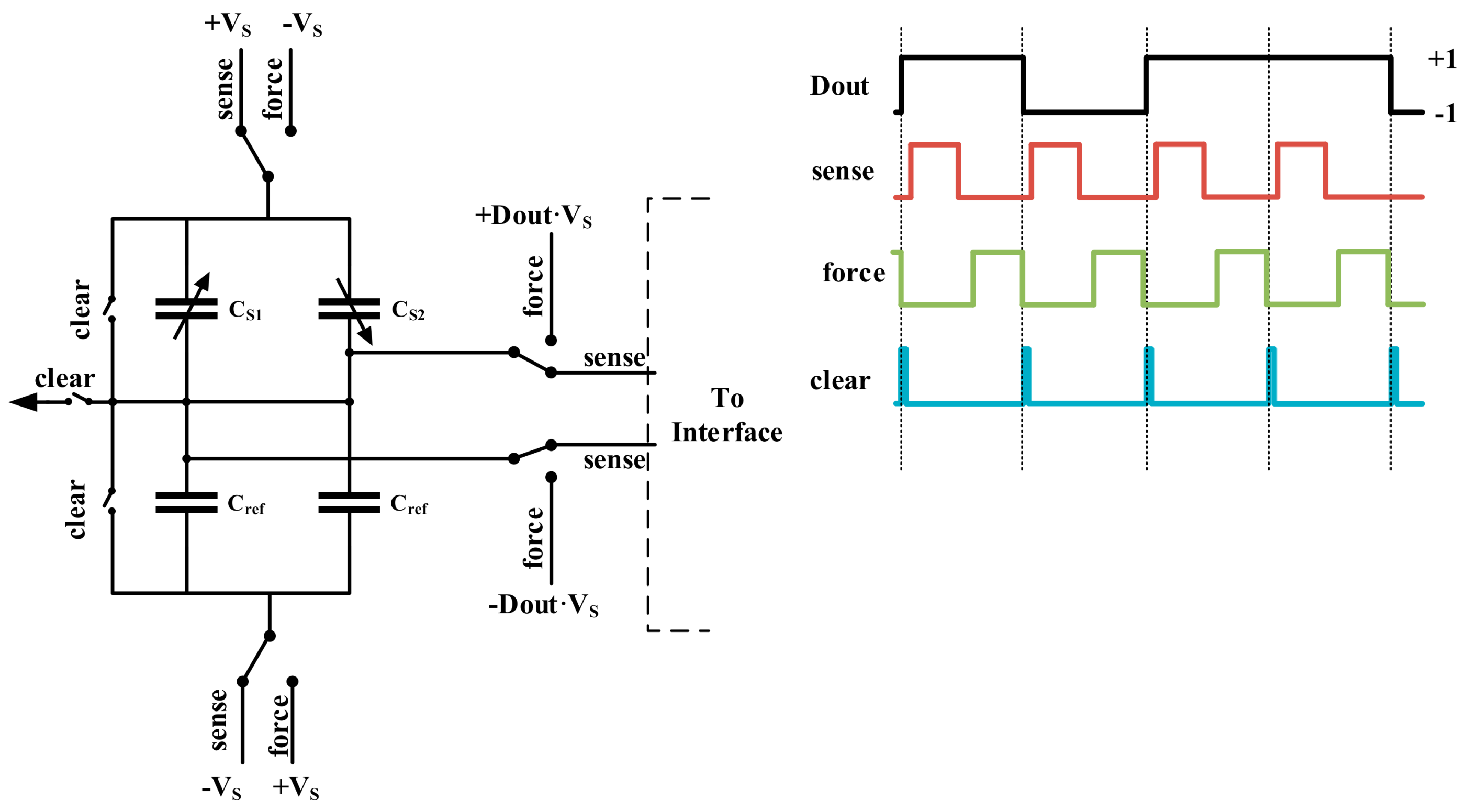

2.2. Electrostatic Feedback Force

- Nonlinearity: the electrostatic force is second-order related to voltage, and is modulated by the displacement x.

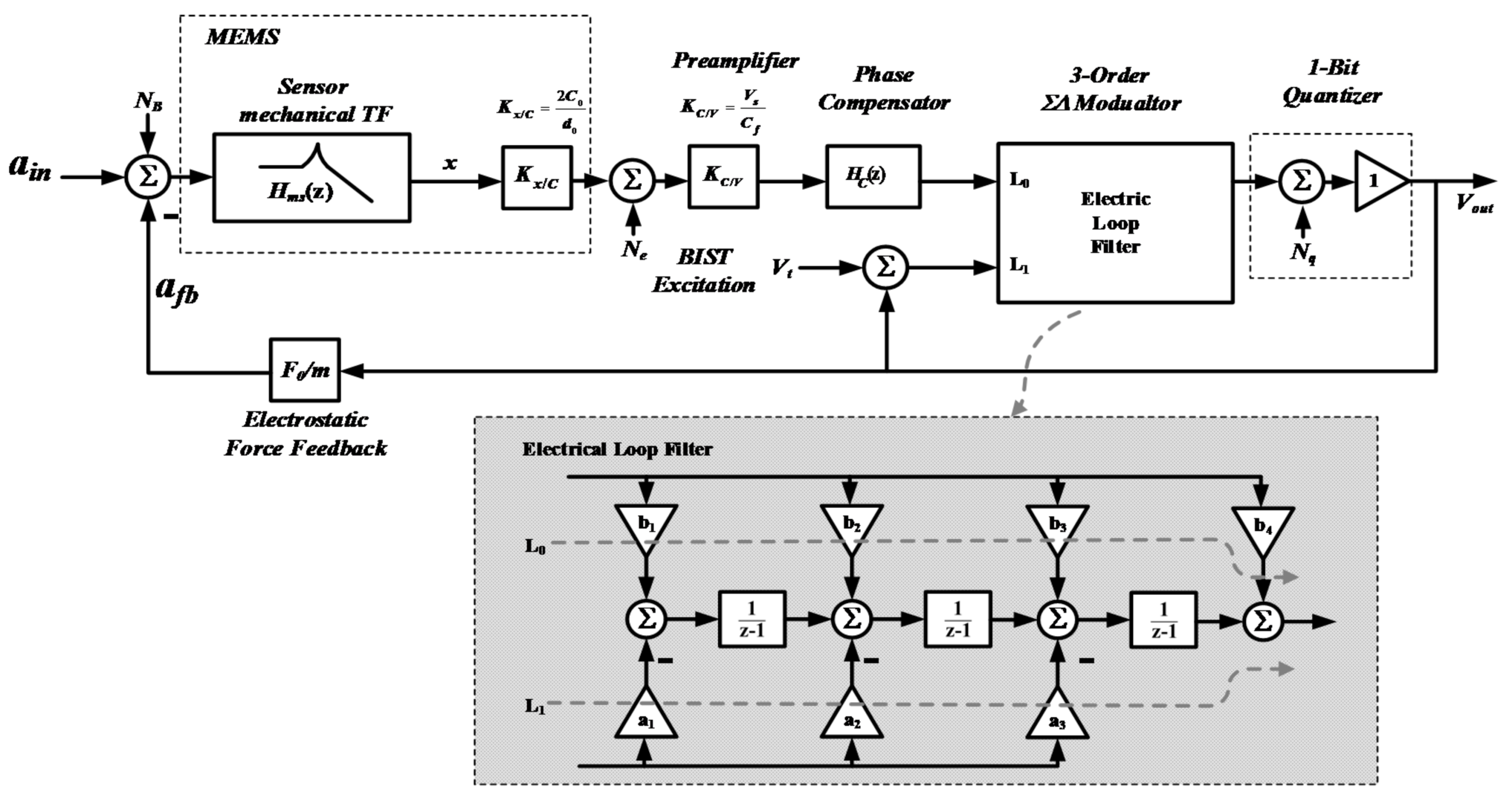

2.3. ΣΔ Closed-Loop Interface

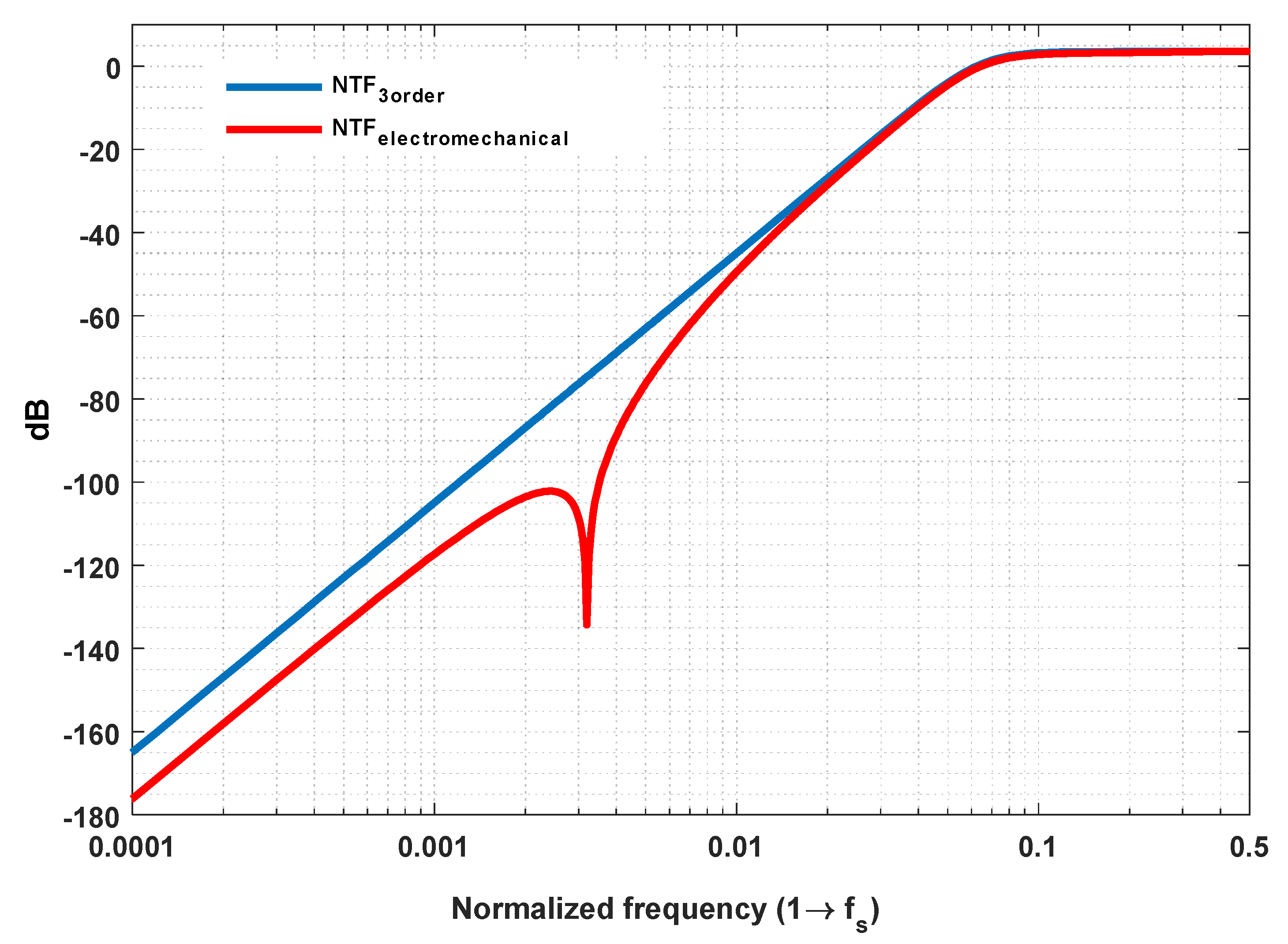

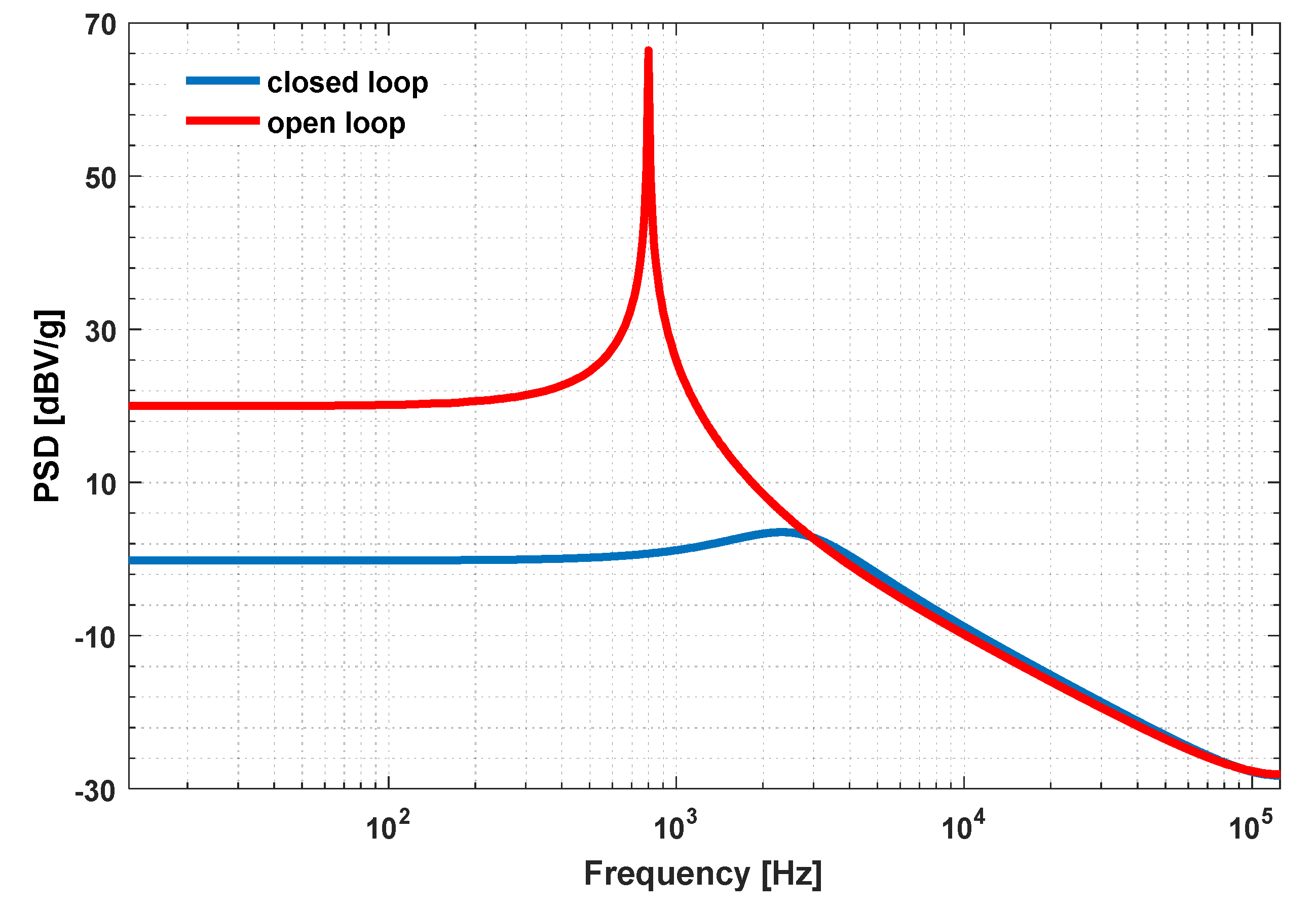

2.3.1. Performance

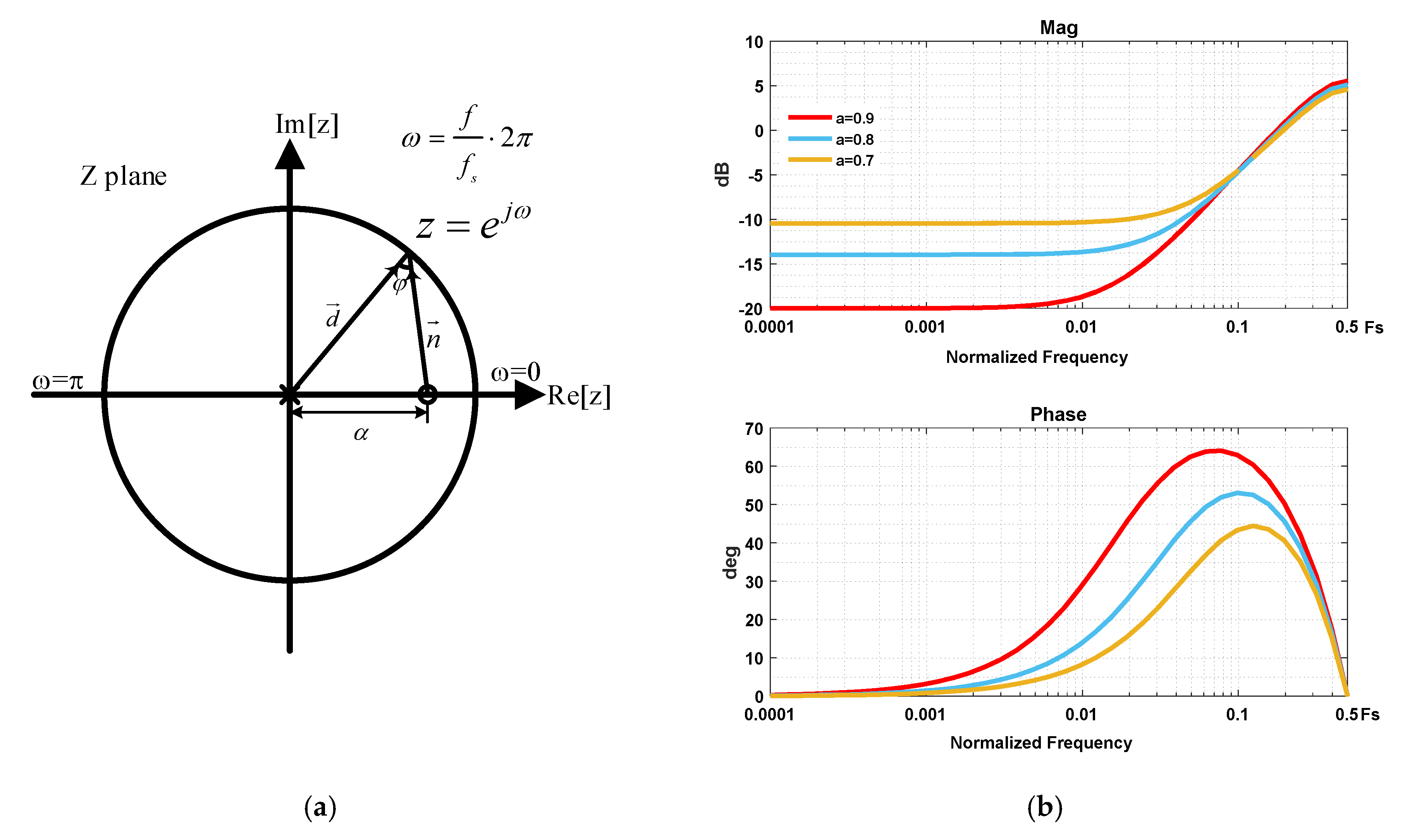

2.3.2. Stability

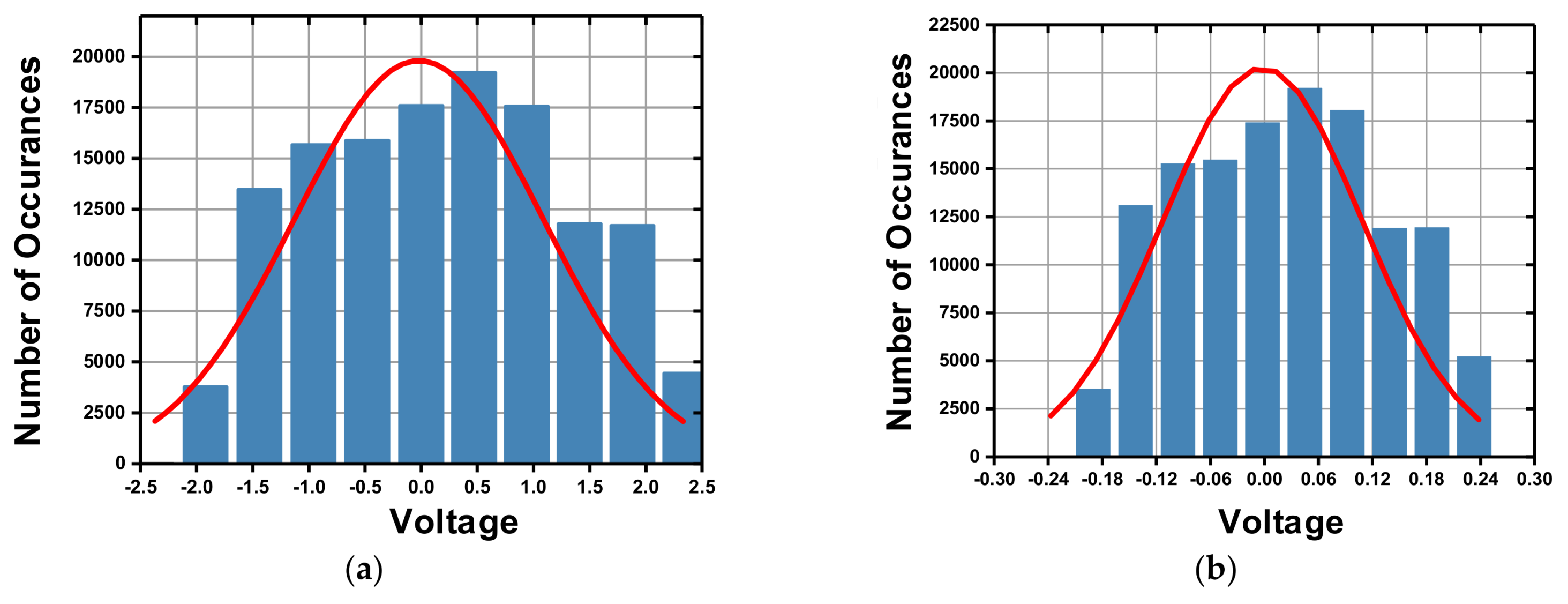

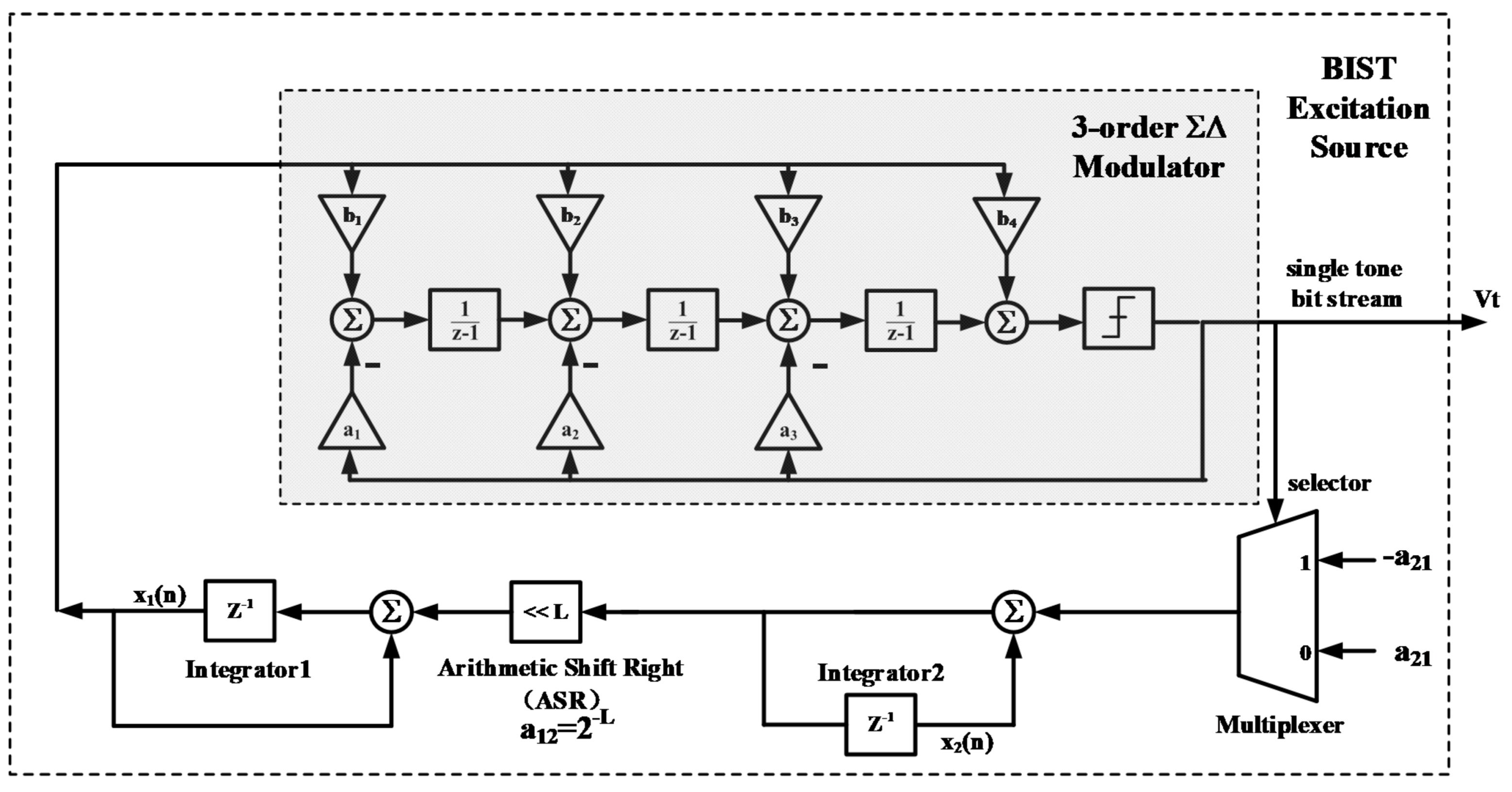

3. BIST Function

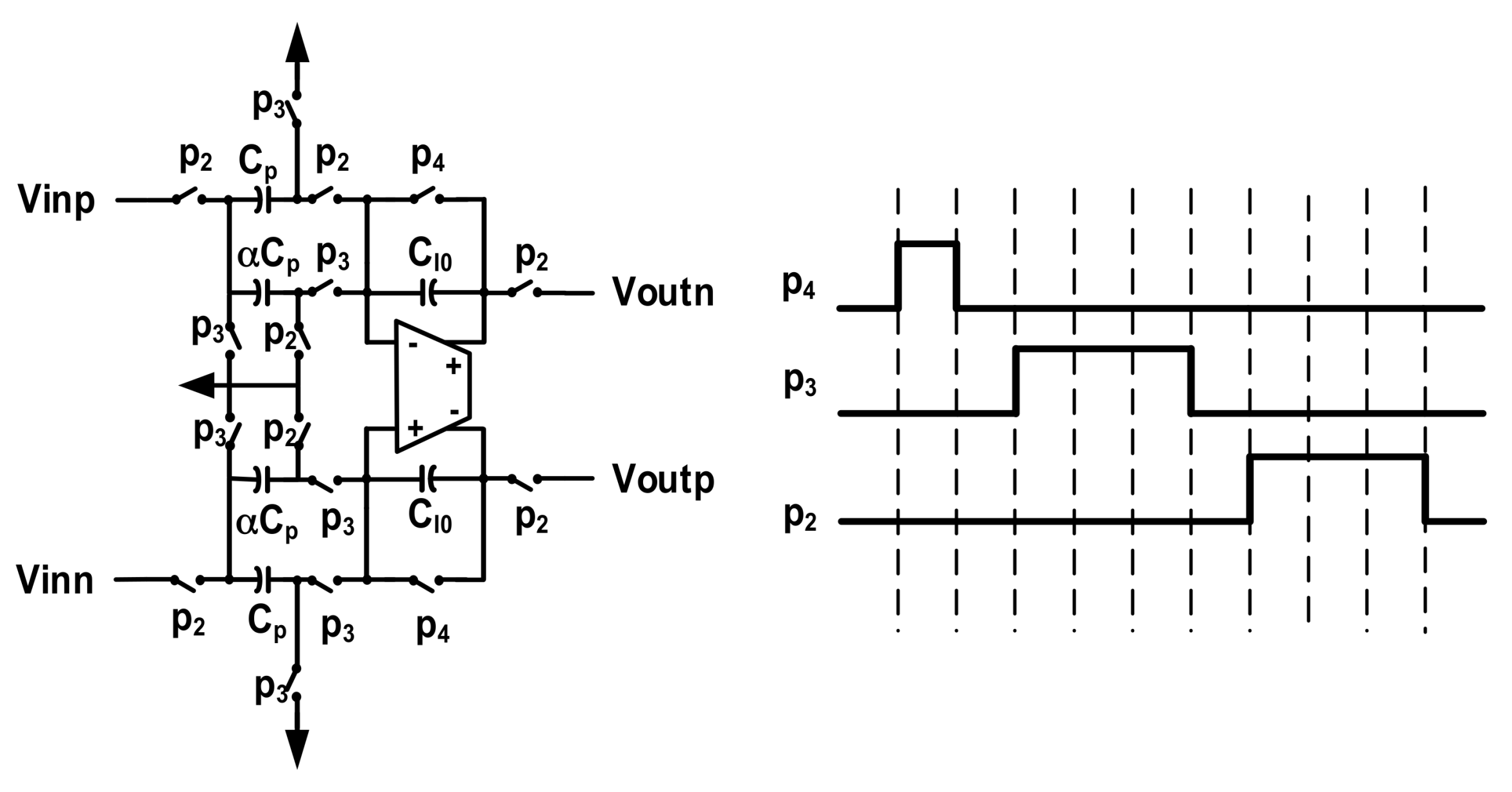

4. Circuit Implementation Details

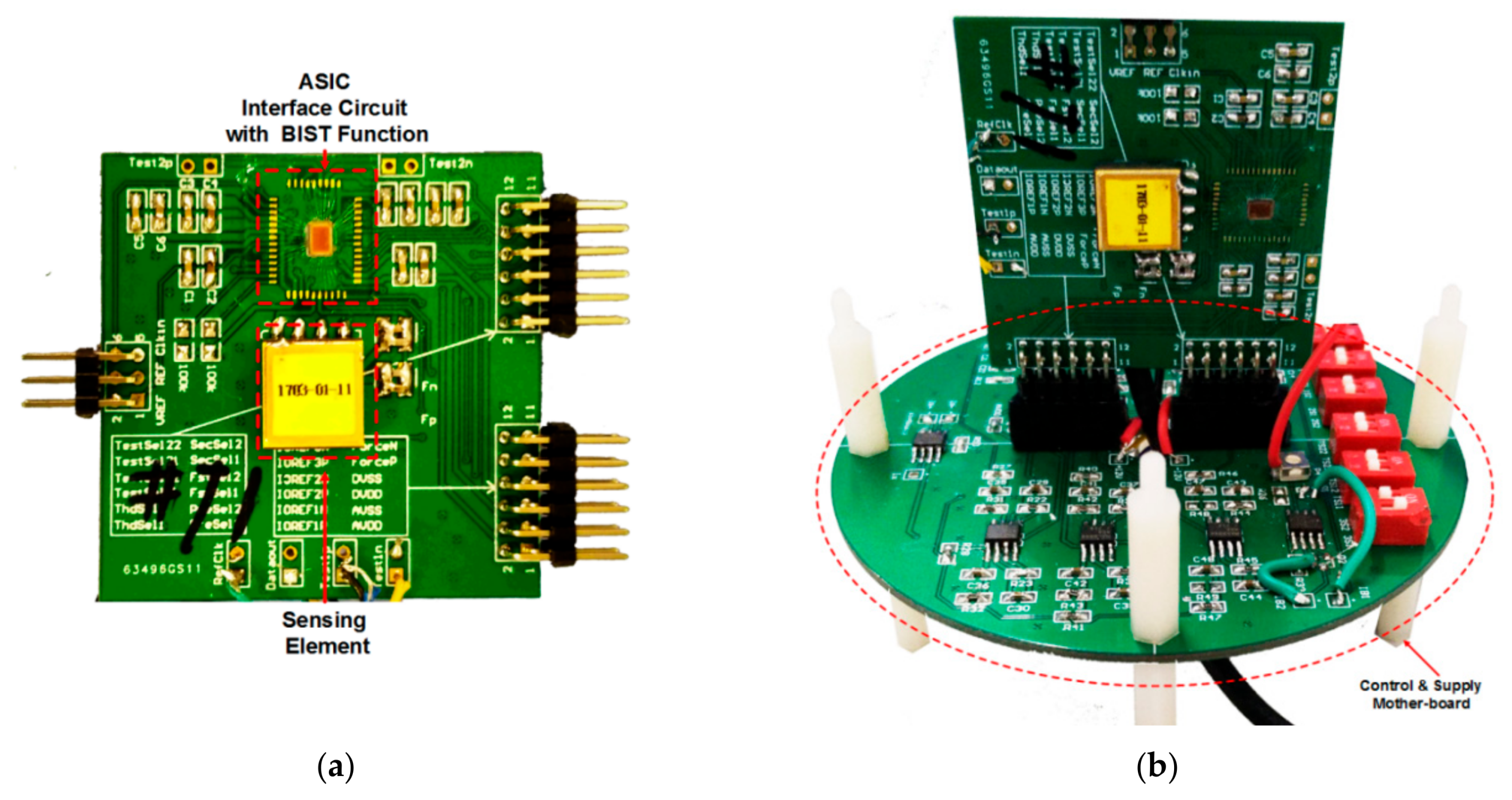

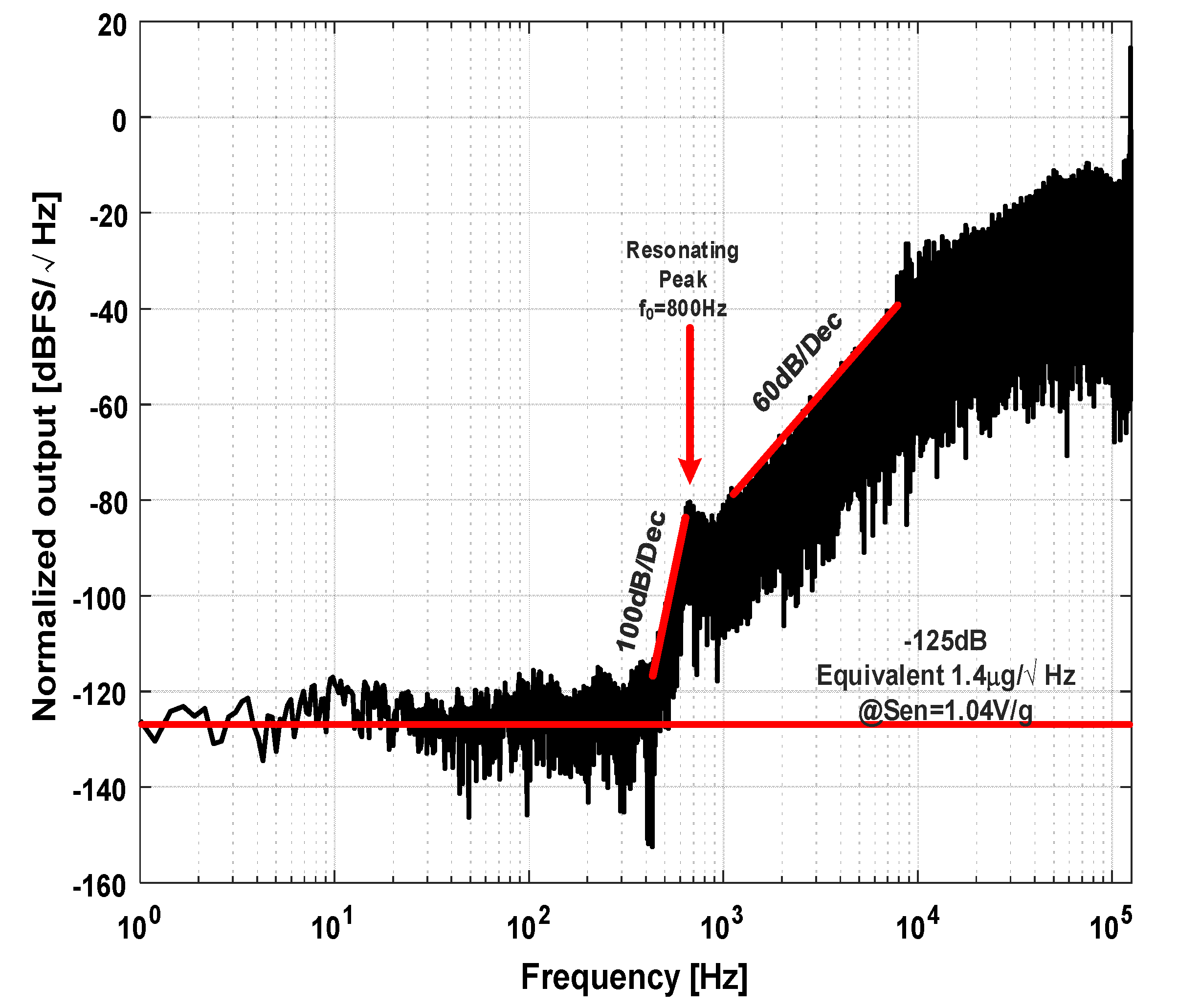

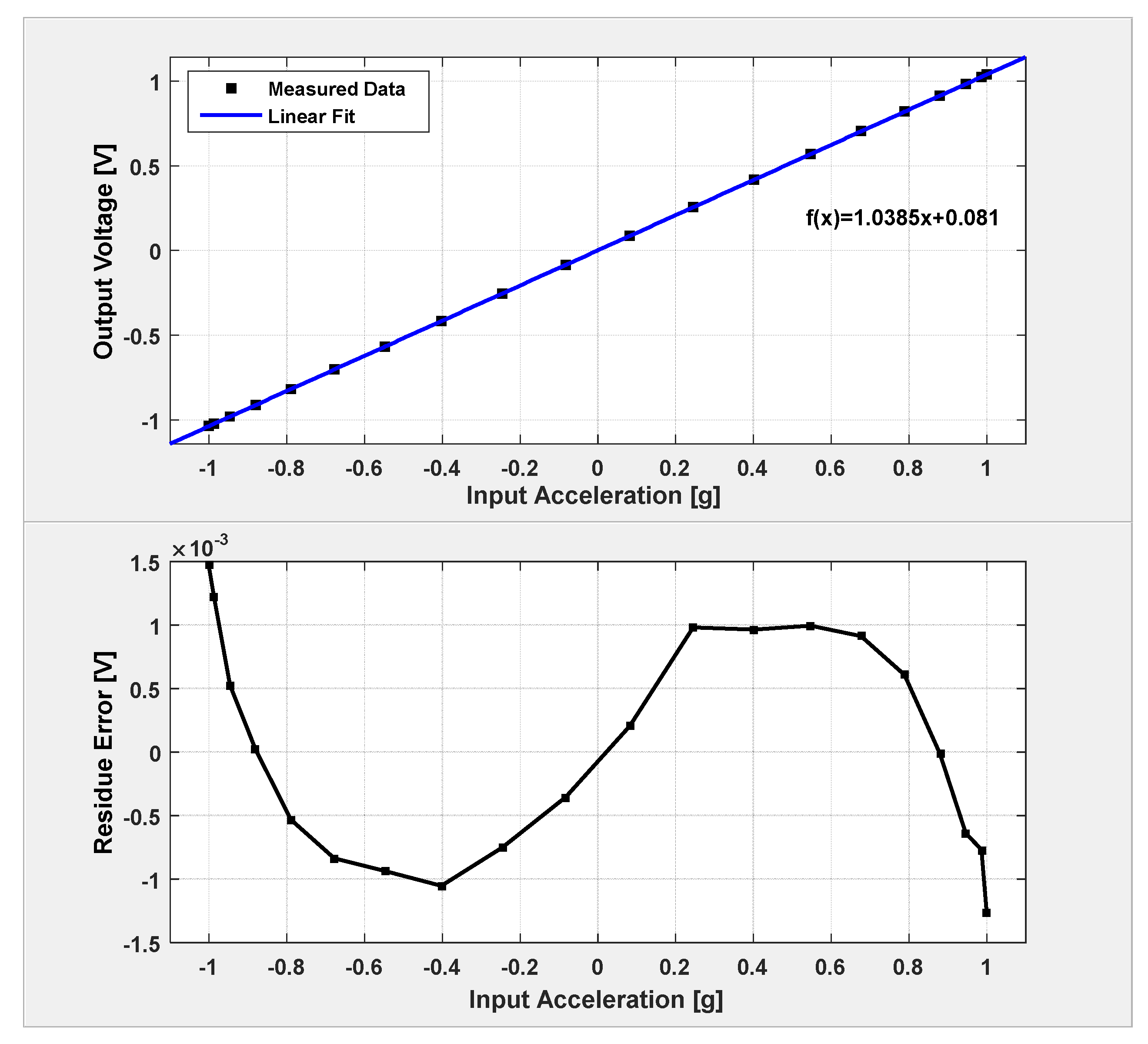

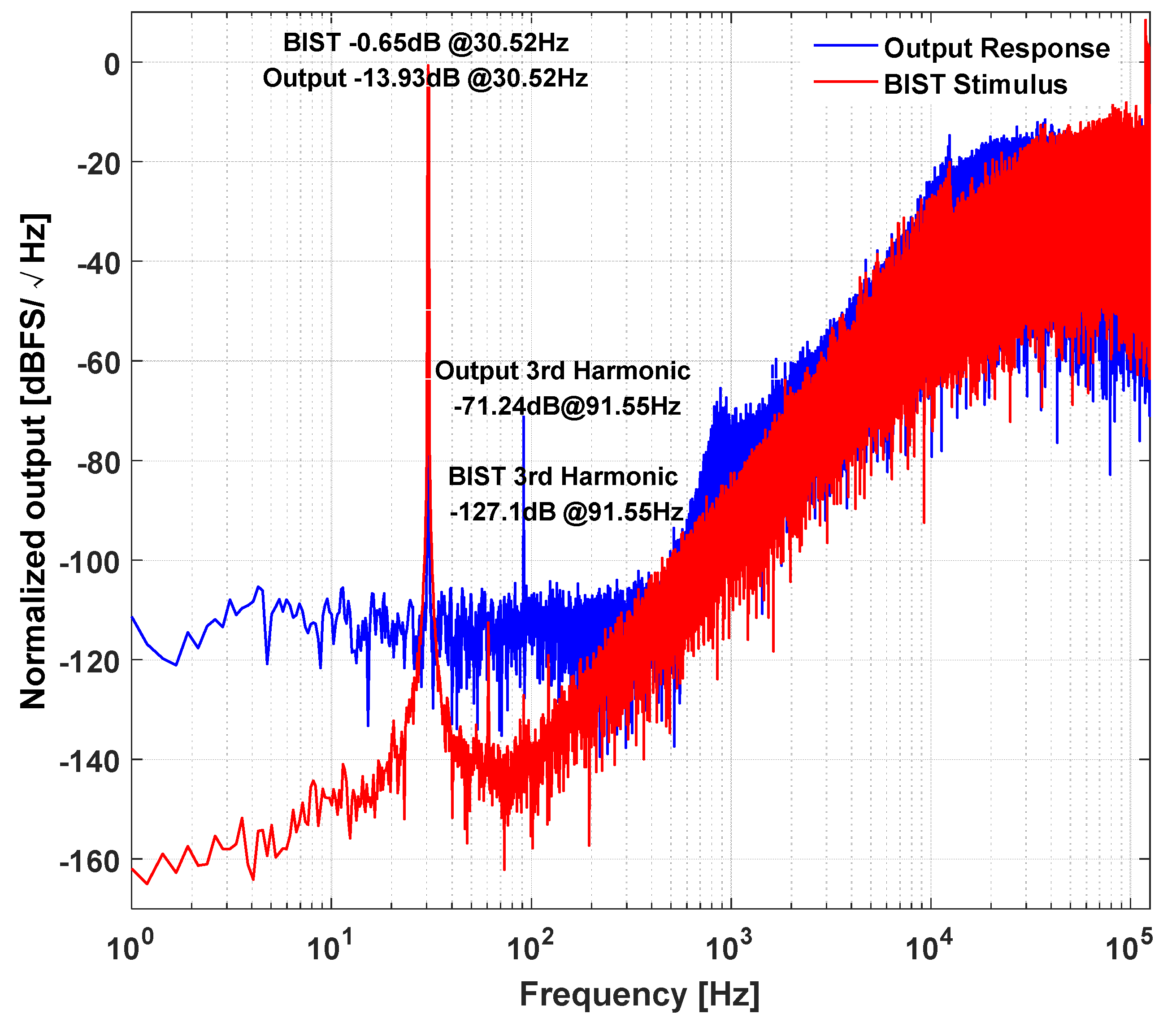

5. Results and Discussion

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Zwahlen, P.; Dong, Y.; Nguyen, A.M.; Rudolf, F.; Stauffer, J.M.; Ullah, P.; Ragot, V. Breakthrough in high performance inertial navigation grade sigma-delta MEMS accelerometer. In Proceedings of the 2012 IEEE/ION Position, Location and Navigation Symposium, Myrtle Beach, SC, USA, 23–26 April 2012; pp. 15–19. [Google Scholar]

- Petkov, V.P.; Boser, B.E. High-order electromechanical ΣΔ modulation in micromachined inertial sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 2006, 53, 1016–1022. [Google Scholar] [CrossRef]

- Jiangfeng, W.; Carley, L.R. Electromechanical ΔΣ modulation with high-Q micromechanical accelerometers and pulse density modulated force feedback. IEEE Trans. Circuits Syst. I Regul. Pap. 2006, 53, 274–287. [Google Scholar] [CrossRef]

- Kulah, H.; Chae, J.; Yazdi, N.; Najafi, K. Noise analysis and characterization of a sigma-delta capacitive microaccelerometer. IEEE J. Solid State Circuits 2006, 41, 352–361. [Google Scholar] [CrossRef]

- Chen, F.; Li, X.; Kraft, M. Electromechanical sigma delta modulators force feedback interfaces for capacitive MEMS inertial sensors: A review. IEEE Sens. J. 2016, 16, 6476–6495. [Google Scholar] [CrossRef]

- Zhao, M.; Chen, Z.; Lu, W.; Zhang, Y.; Niu, Y.; Chen, G. A high-voltage closed-loop SC interface for a ±50 g capacitive micro-accelerometer with 112.4 dB dynamic range. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1328–1341. [Google Scholar]

- Chen, F.; Chang, H.; Yuan, W.; Wilcock, R.; Kraft, M. Parameter optimization for a high-order band-pass continuous-time sigma-delta modulator MEMS gyroscope using a genetic algorithm approach. J. Micromech. Microeng. 2012, 22, 105006. [Google Scholar] [CrossRef]

- Raman, J.; Rombouts, P.; Weyten, L. An unconstrained architecture for systematic design of higher order ΣΔ force-feedback loops. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 1601–1614. [Google Scholar] [CrossRef]

- Xu, H.; Liu, X.; Yin, L. A closed-loop ΣΔ interface for a high-Q micromechanical capacitive accelerometer with 200 Ng/ input noise density. IEEE J. Solid State Circuits 2015, 50, 2101–2112. [Google Scholar] [CrossRef]

- Stauffer, J.M.; Dietrich, O.; Dutoit, B. RS9000, a novel MEMS accelerometer family for mil/aerospace and safety critical applications. In Proceedings of the IEEE/ION Position, Location and Navigation Symposium, Indian Wells, CA, USA, 4–6 May 2010; pp. 1–5. [Google Scholar]

- Shkel, A.M. Precision navigation and timing enabled by microtechnology: Are we there yet? In Proceedings of the 2010 IEEE Sensors, Kona, HI, USA, 1–4 November 2010; pp. 5–9. [Google Scholar]

- Yazdi, N.; Ayazi, F.; Najafi, K. Micromachined inertial sensors. Proc. IEEE 1998, 86, 1640–1659. [Google Scholar] [CrossRef]

- Lutwak, R. Micro-technology for positioning, navigation, and timing towards PNT everywhere and always. In Proceedings of the 2014 International Symposium on Inertial Sensors and Systems (ISISS), Laguna Beach, CA, USA, 25–26 February 2014; pp. 1–4. [Google Scholar]

- Hung, S.F.; Hong, H.C. A fully integrated BIST ΔΣ ADC using the in-phase and quadrature waves fitting procedure. IEEE Trans. Instrum. Meas. 2014, 63, 2750–2760. [Google Scholar] [CrossRef]

- Hong, H.C.; Su, F.Y.; Hung, S.F. A fully integrated built-in self-test Σ-Δ ADC based on the modified controlled sine-wave fitting procedure. IEEE Trans. Instrum. Meas. 2010, 59, 2334–2344. [Google Scholar] [CrossRef]

- Dianat, A.; Attaran, A.; Rashidzadeh, R.; Muscedere, R. Resonant-based test method for MEMS devices. In Proceedings of the 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), Marseille, France, 7–10 December 2014; pp. 423–426. [Google Scholar]

- Dianat, A.; Attaran, A.; Rashidzadeh, R. Test method for capacitive MEMS devices utilizing pierce oscillator. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 633–636. [Google Scholar]

- Basith, I.I.; Kandalaft, N.; Rashidzadeh, R.; Ahmadi, M. Charge-controlled readout and BIST circuit for MEMS sensors. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2013, 32, 433–441. [Google Scholar] [CrossRef]

- Deb, N.; Blanton, R.D. Built-in self-test of MEMS accelerometers. J. Microelectromech. Syst. 2006, 15, 52–68. [Google Scholar] [CrossRef]

- Variyam, P.N.; Cherubal, S.; Chatterjee, A. Prediction of analog performance parameters using fast transient testing. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2002, 21, 349–361. [Google Scholar] [CrossRef] [Green Version]

- Natarajan, V.; Bhattacharya, S.; Chatterjee, A. Alternate Electrical Tests for Extracting Mechanical Parameters of Mems Accelerometer Sensors. In Proceedings of the 24th IEEE VLSI Test Symposium, Berkeley, CA, USA, 30 April–4 May 2006; pp. 6–12. [Google Scholar]

- Dumas, N.; Azais, F.; Mailly, F.; Nouet, P. A method for electrical calibration of MEMS accelerometers through multivariate regression. In Proceedings of the 2009 IEEE 15th International Mixed-Signals, Sensors, and Systems Test Workshop, Scottsdale, AZ, USA, 10–12 June 2009; pp. 1–6. [Google Scholar]

- Ozel, M.K.; Cheperak, M.; Dar, T.; Kiaei, S.; Bakkaloglu, B.; Ozev, S. An electrical-stimulus-only BIST IC for capacitive MEMS accelerometer sensitivity characterization. IEEE Sens. J. 2017, 17, 695–708. [Google Scholar] [CrossRef]

- Glueck, M.; Oshinubi, D.; Schopp, P.; Manoli, Y. Real-time autocalibration of MEMS accelerometers. IEEE Trans. Instrum. Meas. 2014, 63, 96–105. [Google Scholar] [CrossRef]

- Frosio, I.; Pedersini, F.; Borghese, N.A. Autocalibration of triaxial MEMS accelerometers with automatic sensor model selection. IEEE Sens. J. 2012, 12, 2100–2108. [Google Scholar] [CrossRef]

- Glueck, M.; Buhmann, A.; Manoli, Y. Autocalibration of MEMS accelerometers. In Proceedings of the 2012 IEEE International Instrumentation and Measurement Technology Conference Proceedings, Graz, Austria, 13–16 May 2012; pp. 1788–1793. [Google Scholar]

- Rohac, J.; Sipos, M.; Simanek, J. Calibration of low-cost triaxial inertial sensors. IEEE Instrum. Meas. Mag. 2015, 18, 32–38. [Google Scholar] [CrossRef]

- Ye, L.; Guo, Y.; Su, S.W. An efficient autocalibration method for triaxial accelerometer. IEEE Trans. Instrum. Meas. 2017, 66, 2380–2390. [Google Scholar] [CrossRef]

- Zwahlen, P.; Balmain, D.; Habibi, S.; Etter, P.; Rudolf, F.; Brisson, R.; Ullah, P.; Ragot, V. In Open-loop and closed-loop high-end accelerometer platforms for high demanding applications. In Proceedings of the 2016 IEEE/ION Position, Location and Navigation Symposium (PLANS), Savannah, GA, USA, 11–14 April 2016; pp. 932–937. [Google Scholar]

- Institute of Electrical and Electronics Engineers (IEEE). IEEE Recommended Practice for Inertial Sensor Test Equipment, Instrumentation, Data Acquisition, and Analysis; IEEE: Piscataway, NJ, USA, 2013; pp. 1–145. [Google Scholar]

- Nessler, S.; Marx, M.; Manoli, Y. A self-test on wafer level for a MEMS gyroscope readout based on ΔΣ modulation. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 870–880. [Google Scholar] [CrossRef]

- Ezekwe, C.D.; Boser, B.E. Robust compensation of a force-balanced high-Q gyroscope. In Proceedings of the 2008 IEEE Sensors, Lecce, Italy, 26–29 October 2008; pp. 795–798. [Google Scholar]

- Kraft, M.; Lewis, C.; Hesketh, T.; Szymkowiak, S. A novel micromachined accelerometer capacitive interface. Sens. Actuators A Phys. 1998, 68, 466–473. [Google Scholar] [CrossRef] [Green Version]

- Balachandran, G.K.; Petkov, V.P.; Mayer, T.; Balslink, T. A 3-Axis gyroscope for electronic stability control with continuous self-test. IEEE J. Solid State Circuits 2016, 51, 177–186. [Google Scholar]

- Dong, X.; Yang, S.; Zhu, J.; En, Y.; Huang, Q. Method of measuring the mismatch of parasitic capacitance in MEMS accelerometer based on regulating electrostatic stiffness. Micromachines 2018, 9, 128. [Google Scholar] [CrossRef]

- Fan, D.; Liu, Y.; Han, F.; Dong, J. Identification and adjustment of the position and attitude for the electrostatic accelerometer’s proof mass. Sens. Actuators A Phys. 2012, 187, 190–193. [Google Scholar] [CrossRef]

- Zhou, W.; Yu, H.; Zeng, J.; Peng, B.; Zeng, Z.; He, X.; Liu, Y. Improving the dynamic performance of capacitive micro-accelerometer through electrical damping. Microsyst. Technol. 2016, 22, 2961–2969. [Google Scholar] [CrossRef]

- Seeger, J.I.; Crary, S.B. In Stabilization of electrostatically actuated mechanical devices. In Proceedings of the International Solid State Sensors and Actuators Conference (Transducers ‘97), Chicago, IL, USA, 19 June 1997; pp. 1133–1136. [Google Scholar]

- Bechtold, T.; Feng, L.; Schrag, G. System-Level Modeling of MEMS, 1st ed.; John Wiley & Sons: Weinheim, Germany, 2013; pp. 154–165. [Google Scholar]

- Seeger, J.I.; Boser, B.E. Charge control of parallel-plate, electrostatic actuators and the tip-in instability. J. Microelectromech. Syst. 2003, 12, 656–671. [Google Scholar] [CrossRef] [Green Version]

- Fargas-Marques, A.; Casals-Terre, J.; Shkel, A.M. Resonant pull-in condition in parallel-plate electrostatic actuators. J. Microelectromech. Syst. 2007, 16, 1044–1053. [Google Scholar] [CrossRef]

- Rocha, L.A.; Cretu, E.; Wolffenbuttel, R.F. Using dynamic voltage drive in a parallel-plate electrostatic actuator for full-gap travel range and positioning. J. Microelectromech. Syst. 2006, 15, 69–83. [Google Scholar] [CrossRef]

- Nielson, G.N.; Barbastathis, G. Dynamic pull-in of parallel-plate and torsional electrostatic MEMS actuators. J. Microelectromech. Syst. 2006, 15, 811–821. [Google Scholar] [CrossRef]

- Wolfram, H.; Dotzel, W. Stability analysis of a MEMS acceleration sensor. In Proceedings of the 2006 International Conference on Applied Electronics, Pilsen, Czech Republic, 6–7 September 2006. [Google Scholar]

- Veijola, T. Equivalent Circuit Models for Micromechanical Inertial Sensors. Available online: https://pdfs.semanticscholar.org/0cf6/7a4357cd4c1635dbdf6bfc116e936474177f.pdf (accessed on 30 August 2018).

- Xuesong, J. Capacitive Position-Sensing Interface for Micromachined Inertial Sensors. Ph.D. Thesis, University of California, Berkeley, CA, USA, 2003. [Google Scholar]

- Veillette, B.R.; Roberts, G.W. On-chip measurement of the jitter transfer function of charge-pump phase-locked loops. IEEE J. Solid State Circuits 1998, 33, 483–491. [Google Scholar] [CrossRef]

- Lu, A.K.; Roberts, G.W.; Johns, D.A. A high-quality analog oscillator using oversampling D/A conversion techniques. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 1994, 41, 437–444. [Google Scholar] [CrossRef]

- Richard Schreier, G.C.T. Understanding Delta-Sigma Data Converters, 1st ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2005; pp. 115–117. [Google Scholar]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, D.; Liu, X.; Yin, L.; Wang, Y.; Shi, Z.; Zhang, G. A ΣΔ Closed-Loop Interface for a MEMS Accelerometer with Digital Built-In Self-Test Function. Micromachines 2018, 9, 444. https://doi.org/10.3390/mi9090444

Chen D, Liu X, Yin L, Wang Y, Shi Z, Zhang G. A ΣΔ Closed-Loop Interface for a MEMS Accelerometer with Digital Built-In Self-Test Function. Micromachines. 2018; 9(9):444. https://doi.org/10.3390/mi9090444

Chicago/Turabian StyleChen, Dongliang, Xiaowei Liu, Liang Yin, Yinhang Wang, Zhaohe Shi, and Guorui Zhang. 2018. "A ΣΔ Closed-Loop Interface for a MEMS Accelerometer with Digital Built-In Self-Test Function" Micromachines 9, no. 9: 444. https://doi.org/10.3390/mi9090444