A Platform for Mechano(-Electrical) Characterization of Free-Standing Micron-Sized Structures and Interconnects

Abstract

:1. Introduction

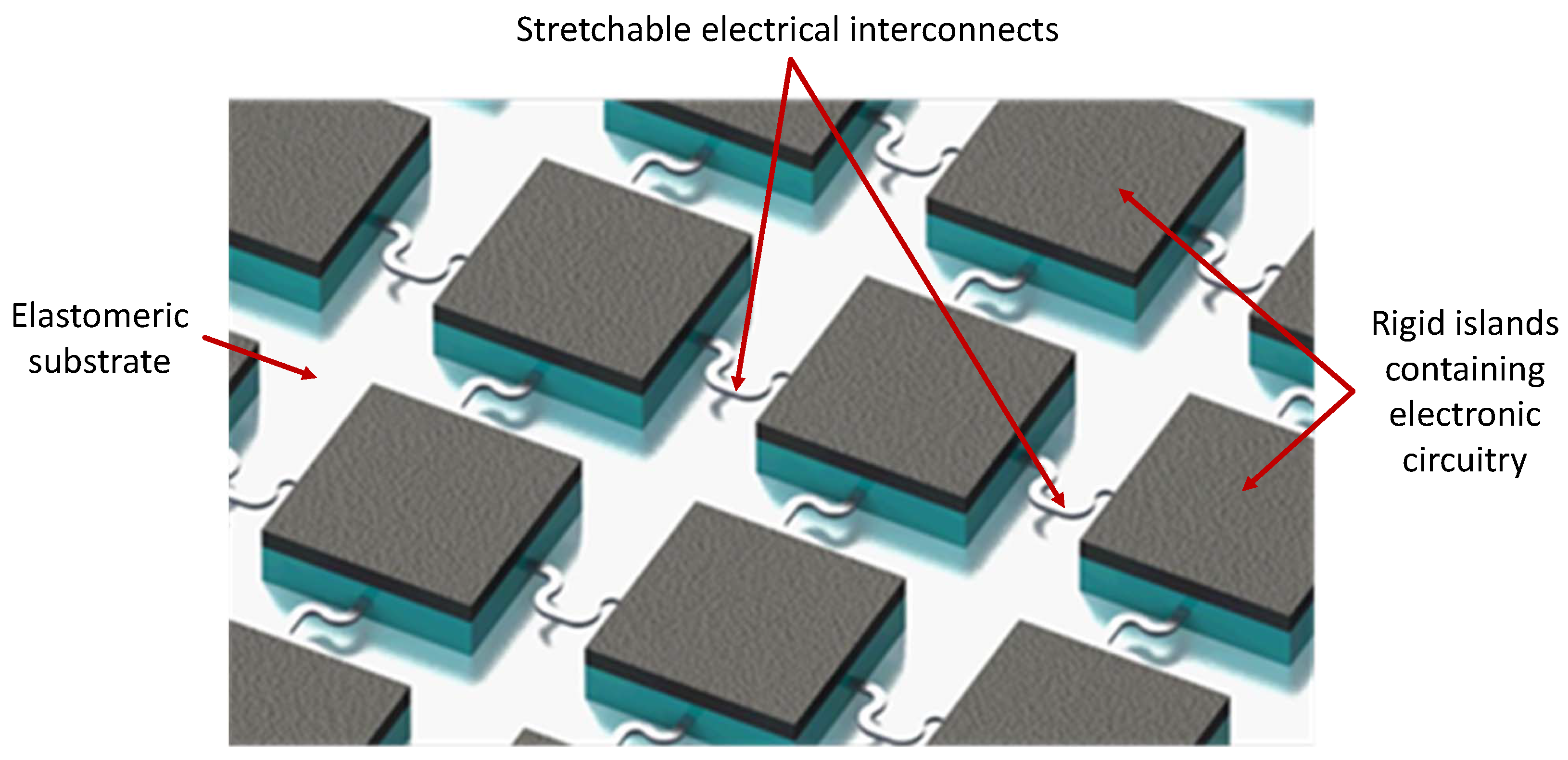

2. Concept Discussion

2.1. Requirements

2.2. Design

3. Experiment

4. Results and Discussions

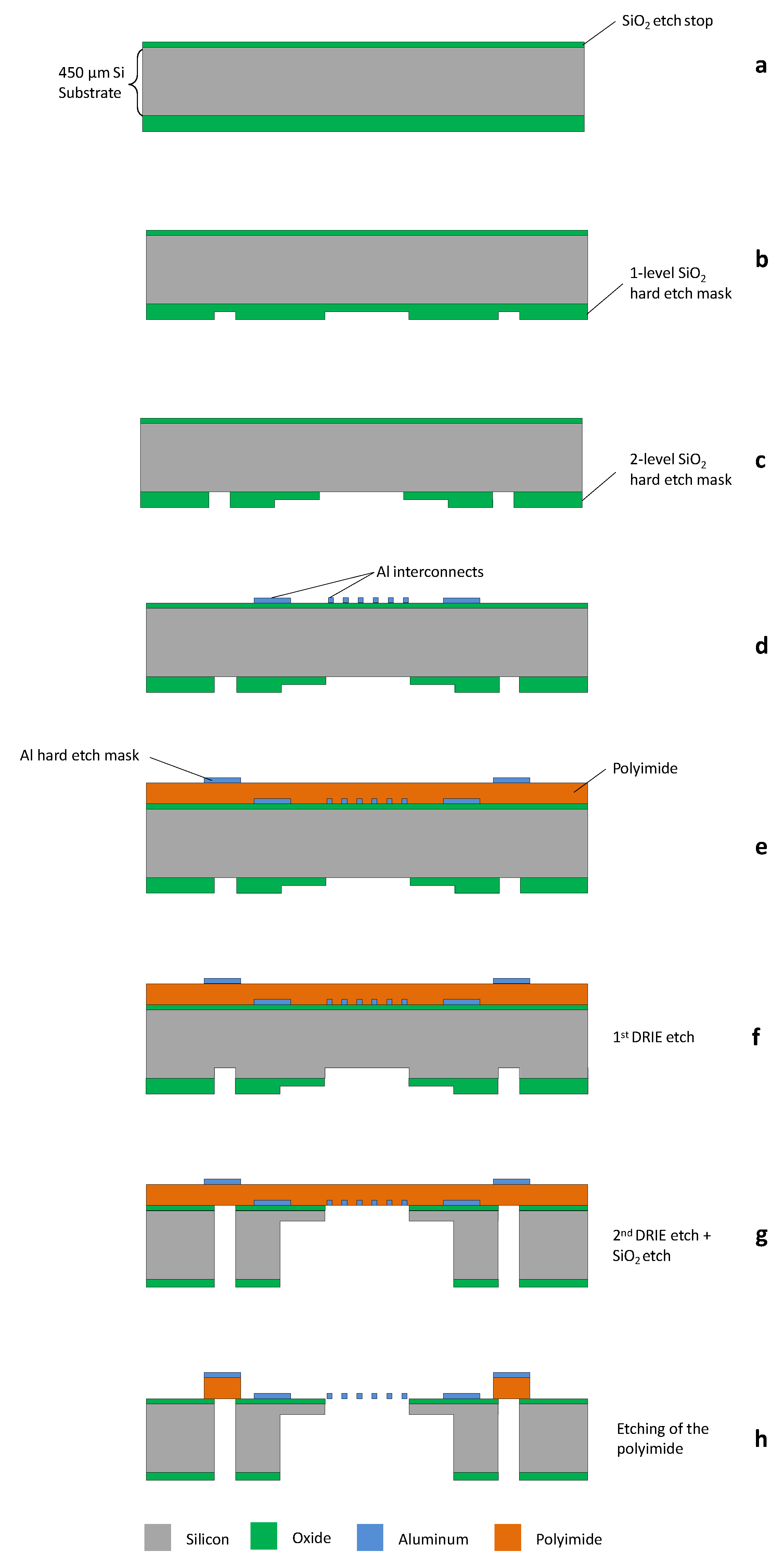

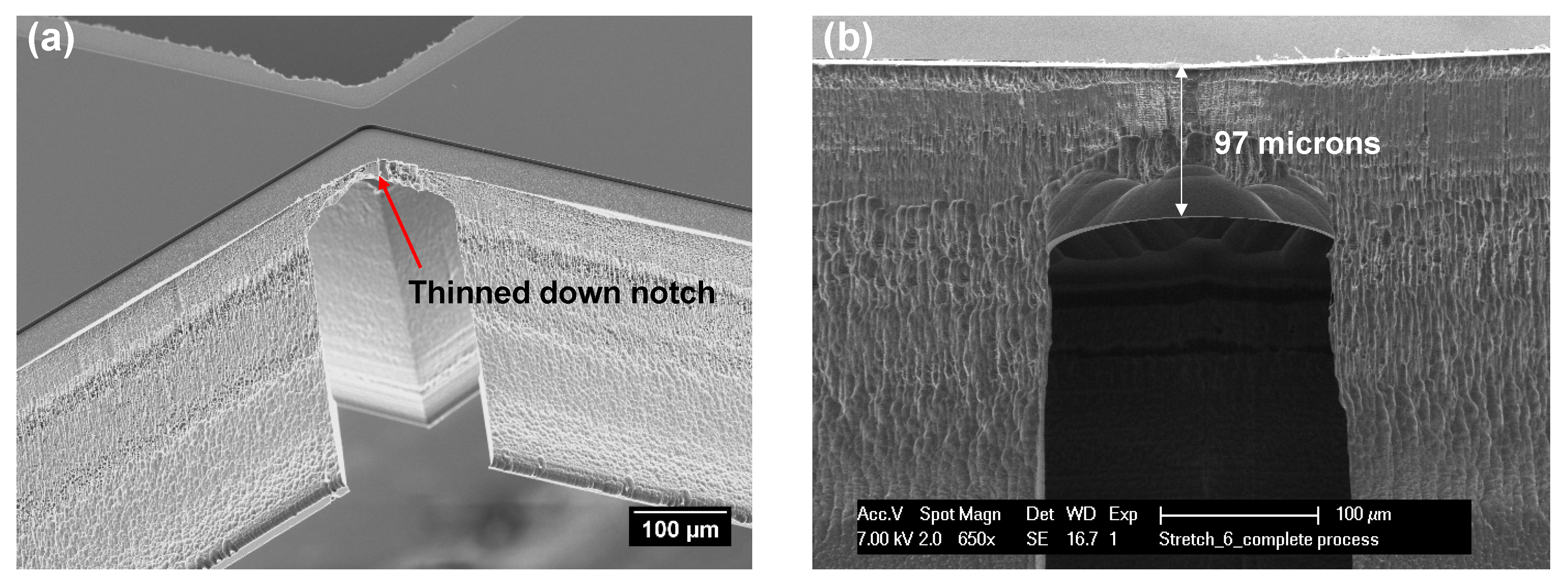

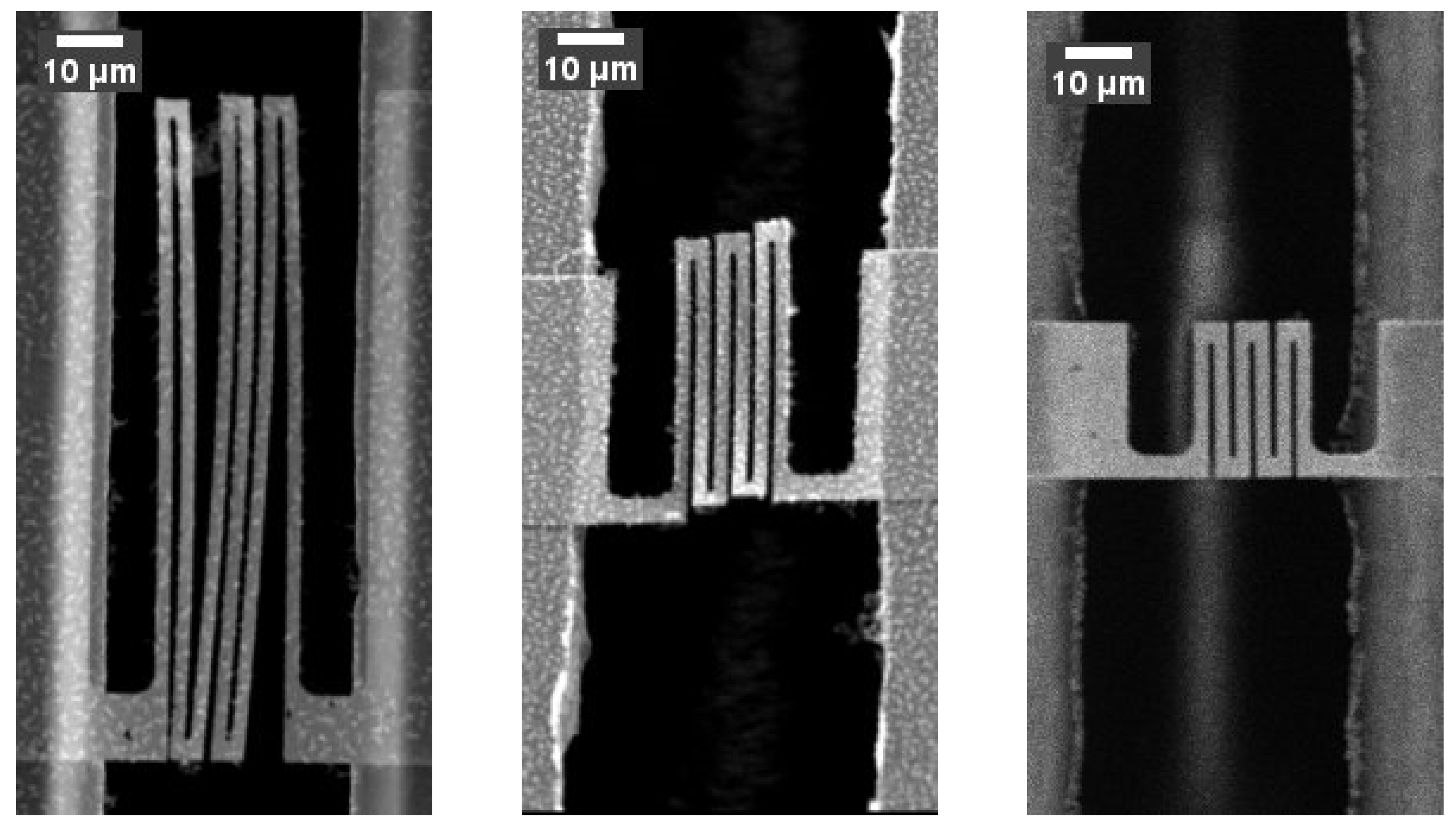

4.1. Fabrication of Test Device

4.2. Fabrication Challenges

4.3. Test Setup and Mounting

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Rogers, J.A.; Someya, T.; Huang, Y. Materials and mechanics for stretchable electronics. Science 2010, 327, 1603–1607. [Google Scholar] [CrossRef] [PubMed]

- Joshi, S.; Savov, A.; Dekker, R. Substrate Transfer Technology for Stretchable Electronics. Procedia Eng. 2016, 168, 1555–1558. [Google Scholar] [CrossRef]

- Kim, D.H.; Lu, N.; Ma, R.; Kim, Y.S.; Kim, R.H.; Wang, S.; Wu, J.; Won, S.M.; Tao, H.; Islam, A.; et al. Epidermal Electronics. Science 2011, 333, 838–843. [Google Scholar] [CrossRef] [PubMed]

- Park, S.I.; Brenner, D.S.; Shin, G.; Morgan, C.D.; Copits, B.A.; Chung, H.U.; Pullen, M.Y.; Noh, K.N.; Davidson, S.; Oh, S.J.; et al. Soft, stretchable, fully implantable miniaturized optoelectronic systems for wireless optogenetics. Nat. Biotechnol. 2015, 33, 1280–1286. [Google Scholar] [CrossRef] [PubMed]

- Maghribi, M.; Hamilton, J.; Polla, D.; Rose, K.; Wilson, T.; Krulevitch, P. Stretchable micro-electrode array [for retinal prosthesis]. In Proceedings of the IEEE Biology 2nd Annual International IEEE-EMB Special Topic Conference on Microtechnologies in Medicine, Madison, WI, USA, 2–4 May 2002; pp. 80–83. [Google Scholar]

- Pakazad, S.K.; Savov, A.; Van De Stolpe, A.; Braam, S.; Van Meer, B.; Dekker, R. A stretchable Micro-Electrode Array for in vitro electrophysiology. In Proceedings of the 2011 IEEE 24th International Conference on Micro Electro Mechanical Systems (MEMS), Cancun, Mexico, 23–27 January 2011; pp. 829–832. [Google Scholar]

- Huh, D.; Leslie, D.C.; Matthews, B.D.; Fraser, J.P.; Jurek, S.; Hamilton, G.A.; Thorneloe, K.S.; McAlexander, M.A.; Ingber, D.E. A human disease model of drug toxicity—Induced pulmonary edema in a lung-on-a-chip microdevice. Sci. Transl. Med. 2012, 4, 159ra147. [Google Scholar] [CrossRef] [PubMed]

- Meacham, K.W.; Giuly, R.J.; Guo, L.; Hochman, S.; DeWeerth, S.P. A lithographically-patterned, elastic multi-electrode array for surface stimulation of the spinal cord. Biomed. Microdevices 2008, 10, 259–269. [Google Scholar] [CrossRef] [PubMed]

- Jung, I.; Xiao, J.; Malyarchuk, V.; Lu, C.; Li, M.; Liu, Z.; Yoon, J.; Huang, Y.; Rogers, J.A. Dynamically tunable hemispherical electronic eye camera system with adjustable zoom capability. Proc. Natl. Acad. Sci. USA 2011, 108, 1788–1793. [Google Scholar] [CrossRef] [PubMed]

- Plovie, B.; Yang, Y.; Guillaume, J.; Dunphy, S.; Dhaenens, K.; Van Put, S.; Vandecasteele, B.; Vervust, T.; Bossuyt, F.; Vanfleteren, J. Arbitrarily Shaped 2.5D Circuits using Stretchable Interconnects Embedded in Thermoplastic Polymers. Adv. Eng. Mater. 2017, 19, 1700032. [Google Scholar] [CrossRef]

- Van Der Sluis, O.; Hsu, Y.Y.; Timmermans, P.; Gonzalez, M.; Hoefnagels, J. Stretching-induced interconnect delamination in stretchable electronic circuits. J. Phys. D Appl. Phys. 2010, 44, 034008. [Google Scholar] [CrossRef]

- Kim, D.H.; Song, J.; Choi, W.M.; Kim, H.S.; Kim, R.H.; Liu, Z.; Huang, Y.Y.; Hwang, K.C.; Zhang, Y.W.; Rogers, J.A. Materials and noncoplanar mesh designs for integrated circuits with linear elastic responses to extreme mechanical deformations. Proc. Natl. Acad. Sci. USA 2008, 105, 18675–18680. [Google Scholar] [CrossRef] [PubMed]

- Kim, D.H.; Lu, N.; Huang, Y.; Rogers, J.A. Materials for stretchable electronics in bioinspired and biointegrated devices. MRS Bull. 2012, 37, 226–235. [Google Scholar] [CrossRef]

- Le Borgne, B.; De Sagazan, O.; Crand, S.; Jacques, E.; Harnois, M. Conformal Electronics Wrapped Around Daily Life Objects Using an Original Method: Water Transfer Printing. ACS Appl. Mater. Interfaces 2017, 9, 29424–29429. [Google Scholar] [CrossRef] [PubMed]

- Shafqat, S.; Hoefnagels, J.P.; Savov, A.; Joshi, S.; Dekker, R.; Geers, M.G. Ultra-stretchable Interconnects for high-density stretchable electronics. Micromachines 2017, 8, 277. [Google Scholar] [CrossRef]

- Feiner, R.; Engel, L.; Fleischer, S.; Malki, M.; Gal, I.; Shapira, A.; Shacham-Diamand, Y.; Dvir, T. Engineered hybrid cardiac patches with multifunctional electronics for online monitoring and regulation of tissue function. Nat. Mater. 2016, 15, 679–685. [Google Scholar] [CrossRef] [PubMed]

- Lee, J.H.; Park, S.; Yang, C.; Choi, H.K.; Cho, M.R.; Cho, S.U.; Park, Y.D. Free-Standing GaMnAs Nanomachined Sheets for van der Pauw Magnetotransport Measurements. Micromachines 2016, 7, 223. [Google Scholar] [CrossRef]

- Kang, W.; Rajagopalan, J.; Saif, A.; Taher, M. In situ uniaxial mechanical testing of small scale materials—A review. Nanosci. Nanotechnol. Lett. 2010, 2, 282–287. [Google Scholar] [CrossRef]

- Han, J.H.; Rajagopalan, J.; Saif, M.T.A. MEMS-based testing stage to study electrical and mechanical properties of nanocrystalline metal films. In Proceedings of the SPIE—The International Society for Optical Engineering, San Jose, CA, USA, 22–23 January 2007; Volume 6464, p. 64640C-1. [Google Scholar]

- Pantano, M.F.; Espinosa, H.D.; Pagnotta, L. Mechanical characterization of materials at small length scales. J. Mech. Sci. Technol. 2012, 26, 545–561. [Google Scholar] [CrossRef]

- Zhu, Y.; Chang, T.H. A review of microelectromechanical systems for nanoscale mechanical characterization. J. Micromech. Microeng. 2015, 25, 093001. [Google Scholar] [CrossRef]

- Bell, D.J.; Lu, T.; Fleck, N.A.; Spearing, S.M. MEMS actuators and sensors: observations on their performance and selection for purpose. J. Micromech. Microeng. 2005, 15, S153. [Google Scholar] [CrossRef]

- Jeong, S.H.; Hagman, A.; Hjort, K.; Jobs, M.; Sundqvist, J.; Wu, Z. Liquid alloy printing of microfluidic stretchable electronics. Lab Chip 2012, 12, 4657–4664. [Google Scholar] [CrossRef] [PubMed]

- Jeerapan, I.; Sempionatto, J.R.; Pavinatto, A.; You, J.M.; Wang, J. Stretchable biofuel cells as wearable textile-based self-powered sensors. J. Mater. Chem. A 2016, 4, 18342–18353. [Google Scholar] [CrossRef] [PubMed]

- Mimoun, B.; Henneken, V.; Dekker, R. Flex-to-Rigid (F2R): A novel ultra-flexible technology for smart invasive medical instruments. In Proceedings of the MRS Symposium on Stretchable Electronics and Conformal Biointerfaces, San Francisco, CA, USA, 5–9 April 2010; Volume 89. [Google Scholar]

- Mimoun, B.; Henneken, V.; van der Horst, A.; Dekker, R. Flex-to-rigid (F2R): A generic platform for the fabrication and assembly of flexible sensors for minimally invasive instruments. IEEE Sens. J. 2013, 13, 3873–3882. [Google Scholar] [CrossRef]

- Tsang, Y.L.; Miller, C.; Lii, T. Investigation of polyimide residue due to reactive ion etching in O2. J. Electrochem. Soc. 1996, 143, 1464–1469. [Google Scholar] [CrossRef]

- Mimoun, B.; Pham, H.T.; Henneken, V.; Dekker, R. Residue-free plasma etching of polyimide coatings for small pitch vias with improved step coverage. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2013, 31, 021201. [Google Scholar] [CrossRef]

- Joshi, S.; Savov, A.; Shafqat, S.; Dekker, R. Investigation of “fur-like” residues post dry etching of polyimide using aluminum hard etch mask. Mater. Sci. Semicond. Process. 2018, 75, 130–135. [Google Scholar] [CrossRef]

- Lanzara, G.; Salowitz, N.; Guo, Z.; Chang, F.K. A Spider-Web-Like Highly Expandable Sensor Network for Multifunctional Materials. Adv. Mater. 2010, 22, 4643–4648. [Google Scholar] [CrossRef] [PubMed]

- Li, T.; Zhang, Z.; Michaux, B. Competing failure mechanisms of thin metal films on polymer substrates under tension. Theor. Appl. Mech. Lett. 2011, 1, 041002. [Google Scholar] [CrossRef]

- Yang, S.; Ng, E.; Lu, N. Indium Tin Oxide (ITO) serpentine ribbons on soft substrates stretched beyond 100%. Extreme Mech. Lett. 2015, 2, 37–45. [Google Scholar] [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Savov, A.; Joshi, S.; Shafqat, S.; Hoefnagels, J.; Louwerse, M.; Stoute, R.; Dekker, R. A Platform for Mechano(-Electrical) Characterization of Free-Standing Micron-Sized Structures and Interconnects. Micromachines 2018, 9, 39. https://doi.org/10.3390/mi9010039

Savov A, Joshi S, Shafqat S, Hoefnagels J, Louwerse M, Stoute R, Dekker R. A Platform for Mechano(-Electrical) Characterization of Free-Standing Micron-Sized Structures and Interconnects. Micromachines. 2018; 9(1):39. https://doi.org/10.3390/mi9010039

Chicago/Turabian StyleSavov, Angel, Shivani Joshi, Salman Shafqat, Johan Hoefnagels, Marcus Louwerse, Ronald Stoute, and Ronald Dekker. 2018. "A Platform for Mechano(-Electrical) Characterization of Free-Standing Micron-Sized Structures and Interconnects" Micromachines 9, no. 1: 39. https://doi.org/10.3390/mi9010039