An Investigation of the Effect of the Work-Function Variation of a Monolithic 3D Inverter Stacked with MOSFETs

Abstract

:1. Introduction

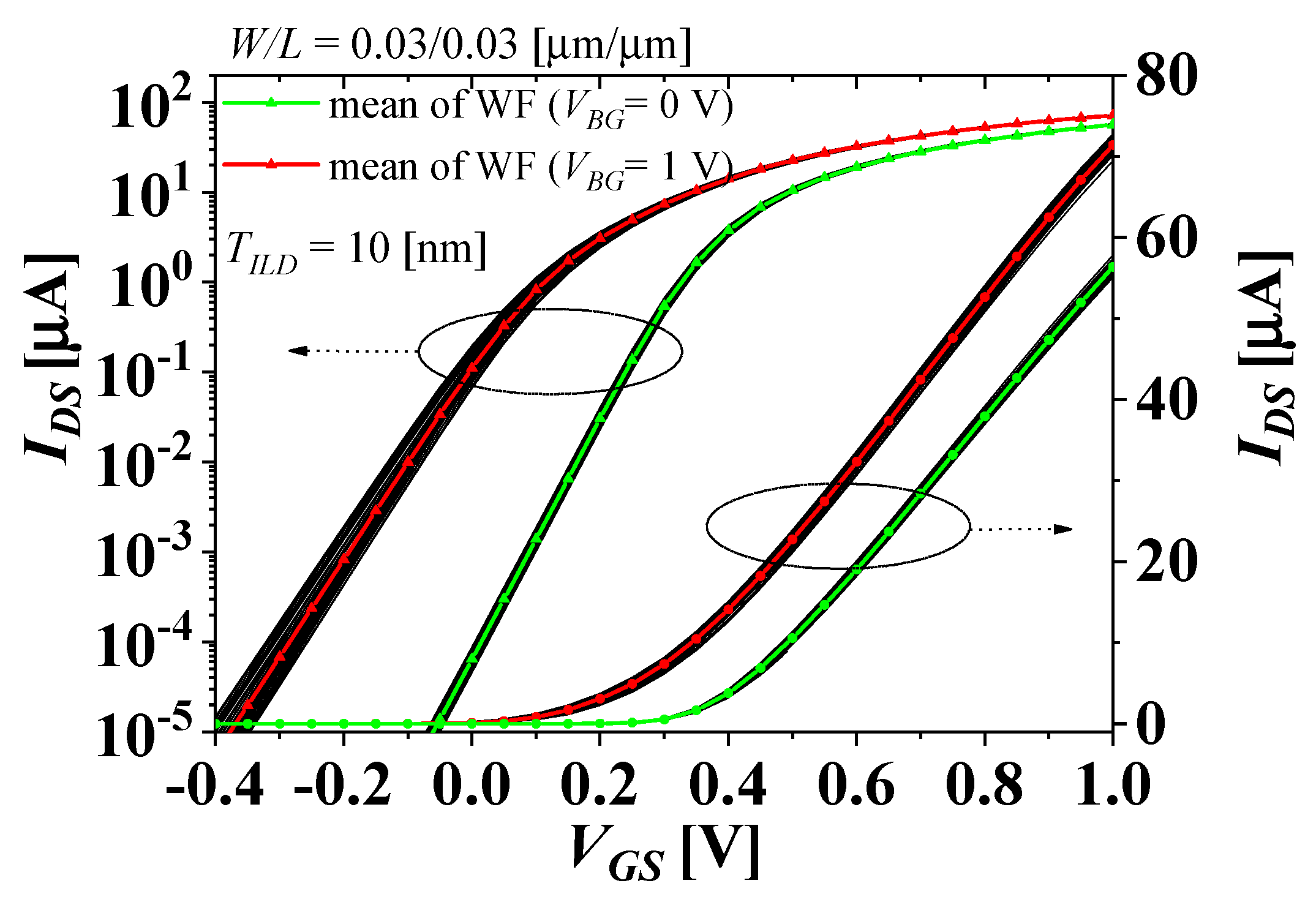

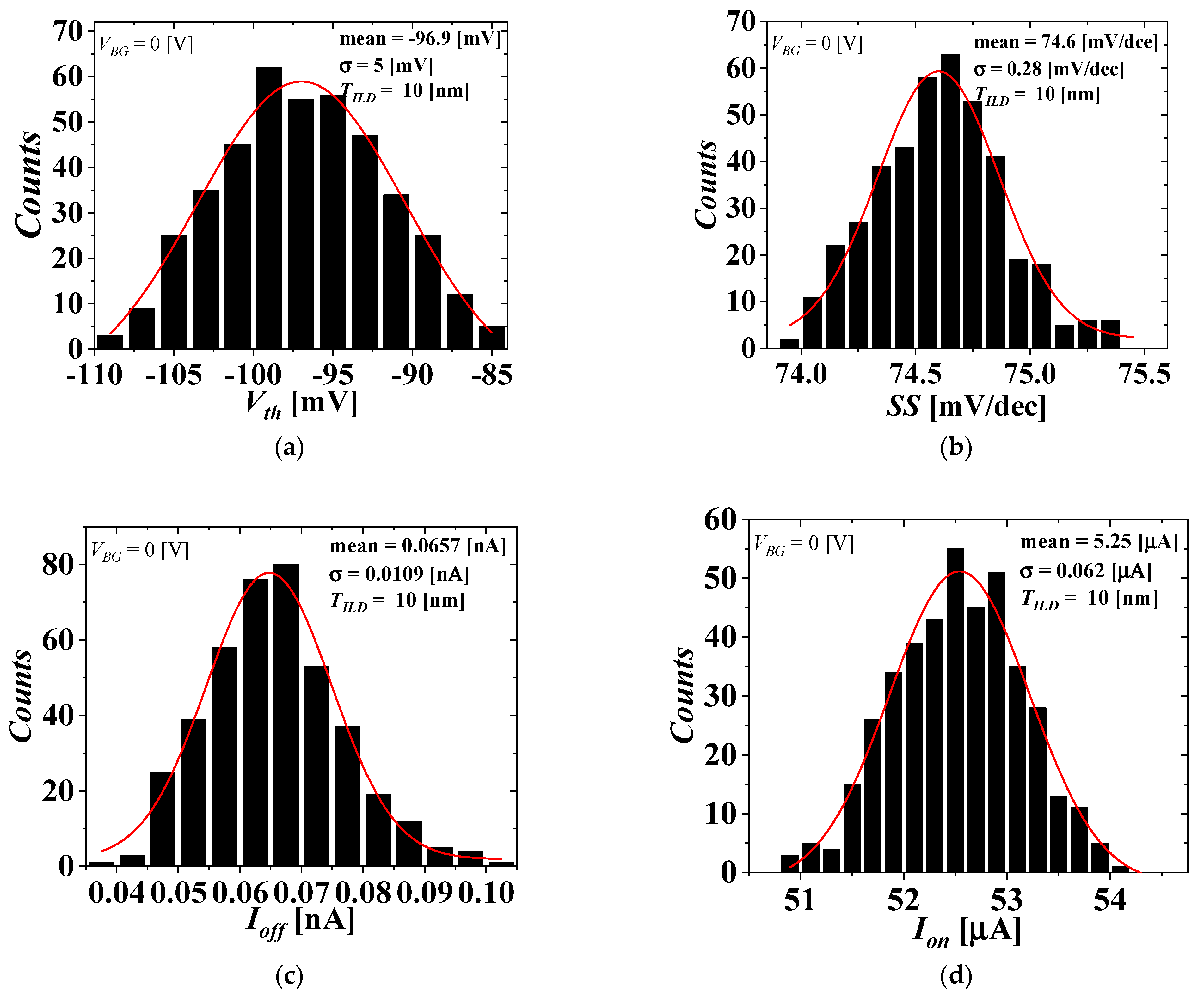

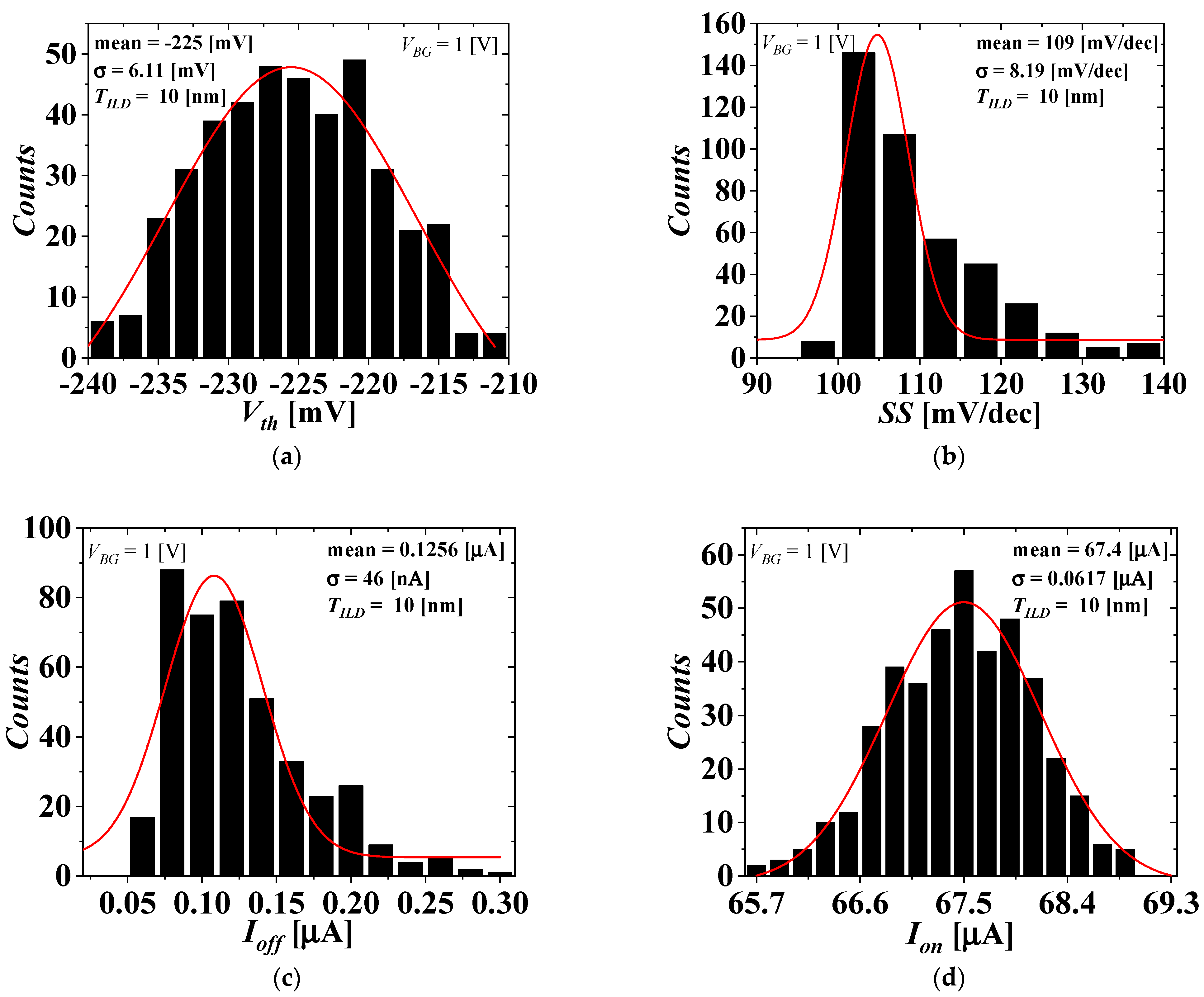

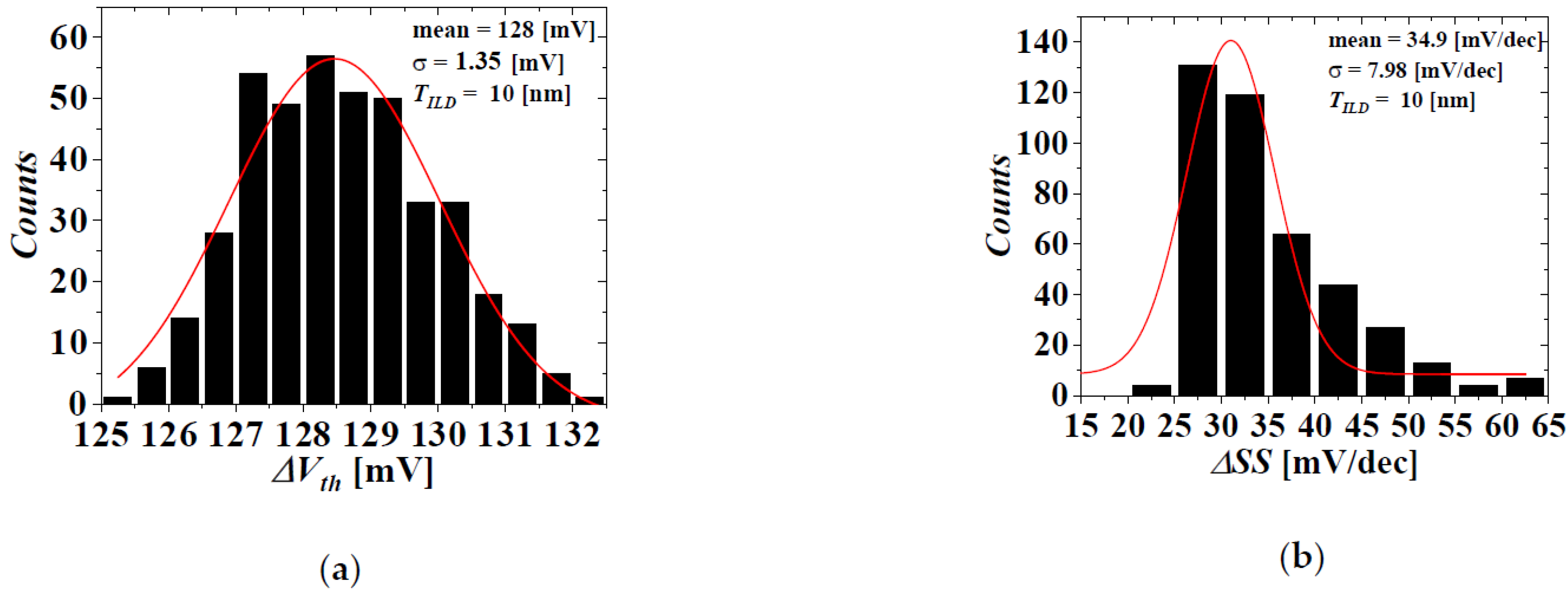

2. Structure and Method for Work-Function Variation (WFV) Simulation

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- International Roadmap for Devices and Systems (IRDS) Report. 2022. Available online: https://irds.ieee.org (accessed on 22 August 2022).

- Batude, P.; Vinet, M.; Pouydebasque, A.; Le Royer, C.; Previtali, B.; Tabone, C.; Hartmann, J.-M.; Sanchez, L.; Baud, L.; Carron, V.; et al. 3D Monolithic Integration. In Proceedings of the 2011 IEEE International Symposium of Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 2233–2236. [Google Scholar] [CrossRef]

- Tarakji, A.H.; Chaudhary, N. Potential of a Novel Double-Sided Fully-Depleted Silicon-on-Insulator CMOS Architecture for the next-Generation Monolithic 3D CPUs and SOCs. In Proceedings of the 2019 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), San Jose, CA, USA, 14–17 October 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Or-Bach, Z. Practical Process Flows for Monolithic 3D. In Proceedings of the 2013 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monterey, CA, USA, 7–10 October 2013; pp. 1–2. [Google Scholar] [CrossRef]

- Radu, I.; Nguyen, B.-Y.; Gaudin, G.; Mazure, C. 3D Monolithic Integration: Stacking Technology and Applications. In Proceedings of the 2015 International Conference on IC Design & Technology (ICICDT), Leuven, Belgium, 1–3 June 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Panth, S.; Samal, S.; Yu, Y.S.; Lim, S.K. Design Challenges and Solutions for Ultra-High-Density Monolithic 3D ICs. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–2. [Google Scholar] [CrossRef]

- Fitzgerald, E.A.; Yoon, S.F.; Tan, C.S.; Palacios, T.; Zhou, X.; Peh, L.S.; Boon, C.C.; Kohen, D.A.; Lee, K.H.; Liu, Z.H.; et al. Monolithic 3D Integration in a CMOS Process Flow. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–3. [Google Scholar] [CrossRef]

- Santos, C.; Vivet, P.; Thuries, S.; Billoint, O.; Colonna, J.-P.; Coudrain, P.; Wang, L. Thermal Performance of CoolCubeTM Monolithic and TSV-Based 3D Integration Processes. In Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC), Millbrae, CA, USA, 6–9 October 2014; pp. 1–3. [Google Scholar] [CrossRef]

- Miketic, I.; Salman, E. Power and Data Integrity in Monolithic 3D Integrated SIMON Core. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Nayak, D.K.; Banna, S.; Samal, S.K.; Lim, S.K. Power, Performance, and Cost Comparisons of Monolithic 3D ICs and TSV-Based 3D ICs. In Proceedings of the 2015 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–2. [Google Scholar] [CrossRef]

- Zhao, F.; Zhang, L.; Wang, Q.; Jiang, Z. Impact of Line Edge Roughness and Linewidth Roughness on Critical Dimension Variation. In Proceedings of the 2012 IEEE International Conference on Computer Science and Automation Engineering (CSAE), Zhangjiajie, China, 25–27 May 2012; pp. 475–479. [Google Scholar] [CrossRef]

- Lee, G.J.; Ahn, T.J.; Lim, S.K.; Yu, Y.S. Investigation into electrical characteristics of logic circuit consisting of modularized monolithic 3D inverter unit cell. J. Inf. Commun. Converg. Eng. 2022, 20, 137–142. [Google Scholar] [CrossRef]

- Ohtou, T.; Sugii, N.; Hiramoto, T. Impact of Parameter Variations and Random Dopant Fluctuations on Short-Channel Fully Depleted SOI MOSFETs With Extremely Thin BOX. IEEE Electron. Device Lett. 2007, 28, 740–742. [Google Scholar] [CrossRef]

- Dubey, A.K.; Pal, P.K.; Varshney, V.; Kumar, A.; Nagaria, R.K. Impact of Channel Doping Fluctuation and Metal Gate Work Function Variation in FD-SOI MOSFET for 5nm BOX Thickness. In Proceedings of the 2019 IEEE Conference on Information and Communication Technology, Allahabad, India, 6–8 December 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Dhiman, G.; Pourush, R. Analysis on Variations of Metal Gate Work Function on Junctionless Double Gate MOSFET with High-k Spacers. In Proceedings of the 2020 International Conference on Emerging Trends in Communication, Control and Computing (ICONC3), Lakshmangarh, India, 21–22 February 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Kannaujiya, A.; Kannaujiya, S.; Chauhan, R.K. Effect of Gate Metal Work Function on Leakage Current in Single Pocket FDSOI 28 nm Transistor. In Proceedings of the 2021 10th IEEE International Conference on Communication Systems and Network Technologies (CSNT), Bhopal, India, 18–19 June 2021; pp. 241–246. [Google Scholar] [CrossRef]

- Hu, V.P.-H.; Chiu, P.-C.; Lu, Y.-C. Impact of Work Function Variation, Line-Edge Roughness, and Ferroelectric Properties Variation on Negative Capacitance FETs. IEEE J. Electron. Devices Soc. 2019, 7, 295–302. [Google Scholar] [CrossRef]

- Ghosh, S.; Rajan, L. Simulation Based Investigation of Sensing Current with Channel Length and Work Function Variation to Realize Hydrogen Detection. In Proceedings of the 2020 International Conference on Innovative Trends in Information Technology (ICITIIT), Kottayam, India, 13–14 February 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Dadgour, H.F.; Endo, K.; De, V.K.; Banerjee, K. Grain-Orientation Induced Work Function Variation in Nanoscale Metal-Gate Transistors—Part II: Implications for Process, Device, and Circuit Design. IEEE Trans. Electron. Devices 2010, 57, 2515–2525. [Google Scholar] [CrossRef]

- Nam, H.; Shin, C. Impact of Current Flow Shape in Tapered (Versus Rectangular) FinFET on Threshold Voltage Variation Induced by Work-Function Variation. IEEE Trans. Electron. Devices 2014, 61, 2007–2011. [Google Scholar] [CrossRef]

- Nam, H.; Lee, Y.; Park, J.-D.; Shin, C. Study of Work-Function Variation in High-κ /Metal-Gate Gate-All-Around Nanowire MOSFET. IEEE Trans. Electron. Devices 2016, 63, 3338–3341. [Google Scholar] [CrossRef]

- Lee, Y.; Shin, C. Impact of Equivalent Oxide Thickness on Threshold Voltage Variation Induced by Work-Function Variation in Multigate Devices. IEEE Trans. Electron. Devices 2017, 64, 2452–2456. [Google Scholar] [CrossRef]

- Yu, Y.S.; Panth, S.; Lim, S.K. Electrical Coupling of Monolithic 3-D Inverters. IEEE Trans. Electron. Devices 2016, 63, 3346–3349. [Google Scholar] [CrossRef]

- Silvaco Int. ATLAS Ver. 5.32.1. R Manual; Silvaco Int.: Santa Clara, CA, USA, 2021. [Google Scholar]

- Silvaco Int. DeckBuild Ver. 5.2.14.R Manual; Silvaco Int.: Santa Clara, CA, USA, 2021. [Google Scholar]

- Ahn, T.J.; Perumal, R.; Lim, S.K.; Yu, Y.S. Parameter Extraction and Power/Performance Analysis of Monolithic 3-D Inverter (M3INV). IEEE Trans. Electron. Devices 2019, 66, 1006–1011. [Google Scholar] [CrossRef]

- Rasouli, S.H.; Endo, K.; Banerjee, K. Work-Function Variation Induced Fluctuation in Bias-Temperature-Instability Characteristics of Emerging Metal-Gate Devices and Implications for Digital Design. In Proceedings of the 2010 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 7–11 November 2010; pp. 714–720. [Google Scholar] [CrossRef]

- Shin, C. Introduction: Barriers Preventing CMOS Device Technology from Moving Forward. In Variation-Aware Advanced CMOS Devices and SRAM; Springer: Dordrecht, The Netherlands, 2016; pp. 1–16. [Google Scholar]

- Ohmori, K.; Matsuki, T.; Ishikawa, D.; Morooka, T.; Aminaka, T.; Sugita, Y.; Chikyow, T.; Shiraishi, K.; Nara, Y.; Yamada, K. Impact of Additional Factors in Threshold Voltage Variability of Metal/High-k Gate Stacks and Its Reduction by Controlling Crystalline Structure and Grain Size in the Metal Gates. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Ahn, T.J.; Yu, Y.S. Electrical Coupling of Monolithic 3D Inverters (M3INVs): MOSFET and Junctionless FET. Appl. Sci. 2021, 11, 277. [Google Scholar] [CrossRef]

- Li, X.; Yang, X.; Zhang, Z.; Wang, T.; Sun, Y.; Liu, Z.; Li, X.; Shi, Y.; Xu, J. Impact of Process Fluctuations on Reconfigurable Silicon Nanowire Transistor. IEEE Trans. Electron. Devices 2021, 68, 885–891. [Google Scholar] [CrossRef]

| Device Type | Material | Orientation | Probability [%] | WF [eV] | Average Grain Size [nm] |

|---|---|---|---|---|---|

| N-type | TiN | <100> | 60 | 4.6 | 4.3 [27,29] |

| <111> | 40 | 4.4 | |||

| P-type | MoN | <110> | 60 | 5.0 | 17 [27] |

| <112> | 40 | 4.4 |

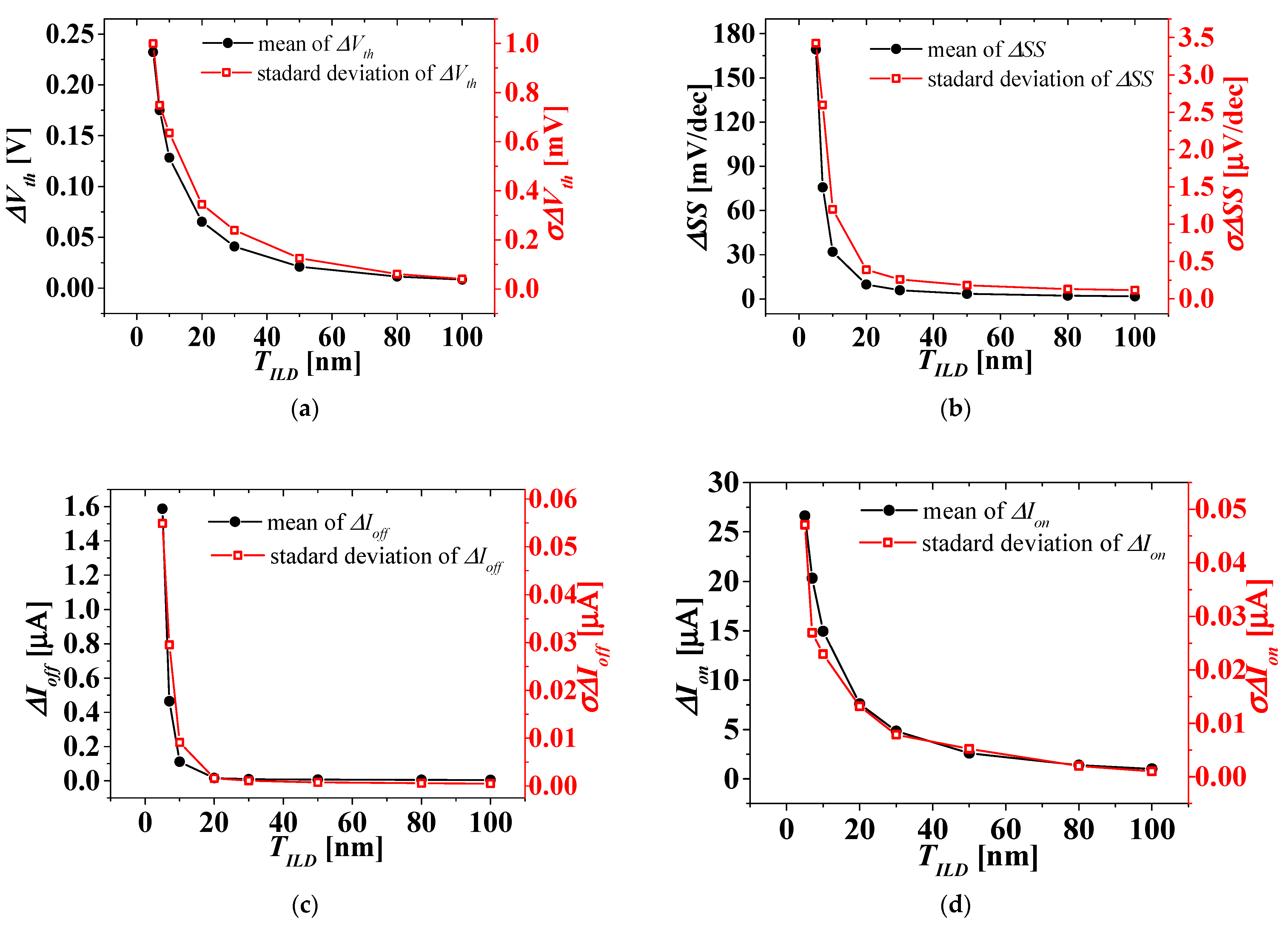

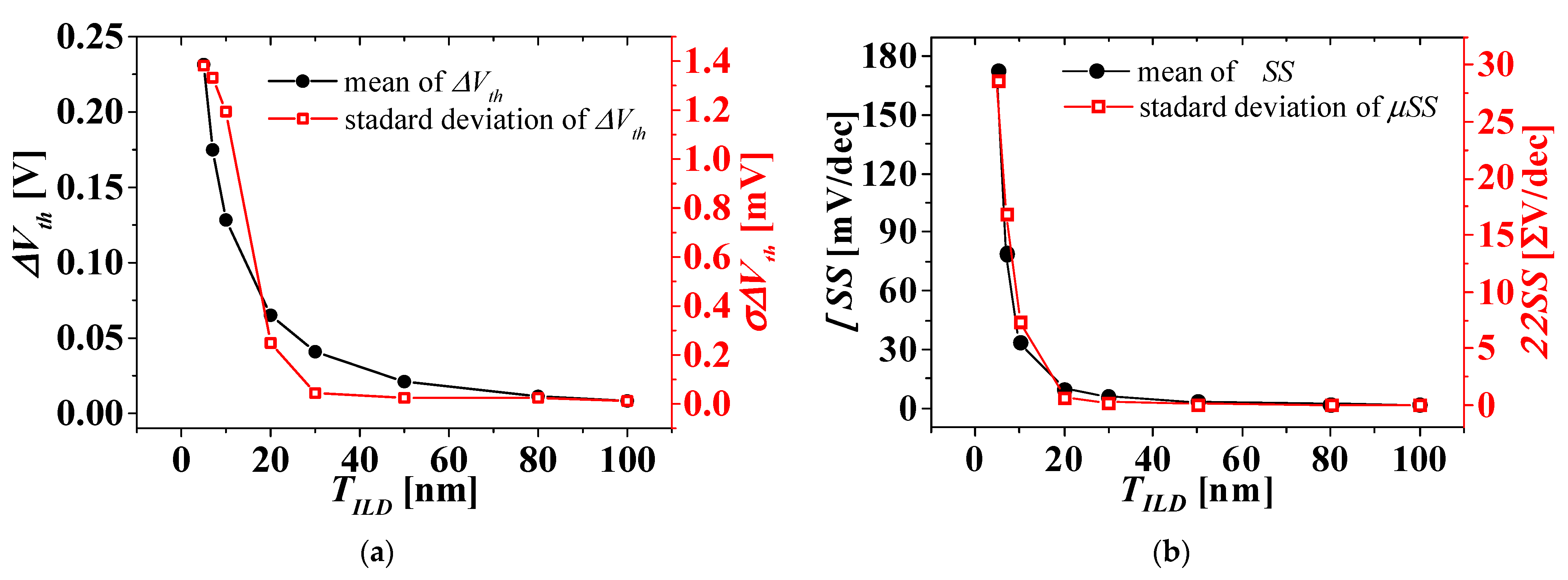

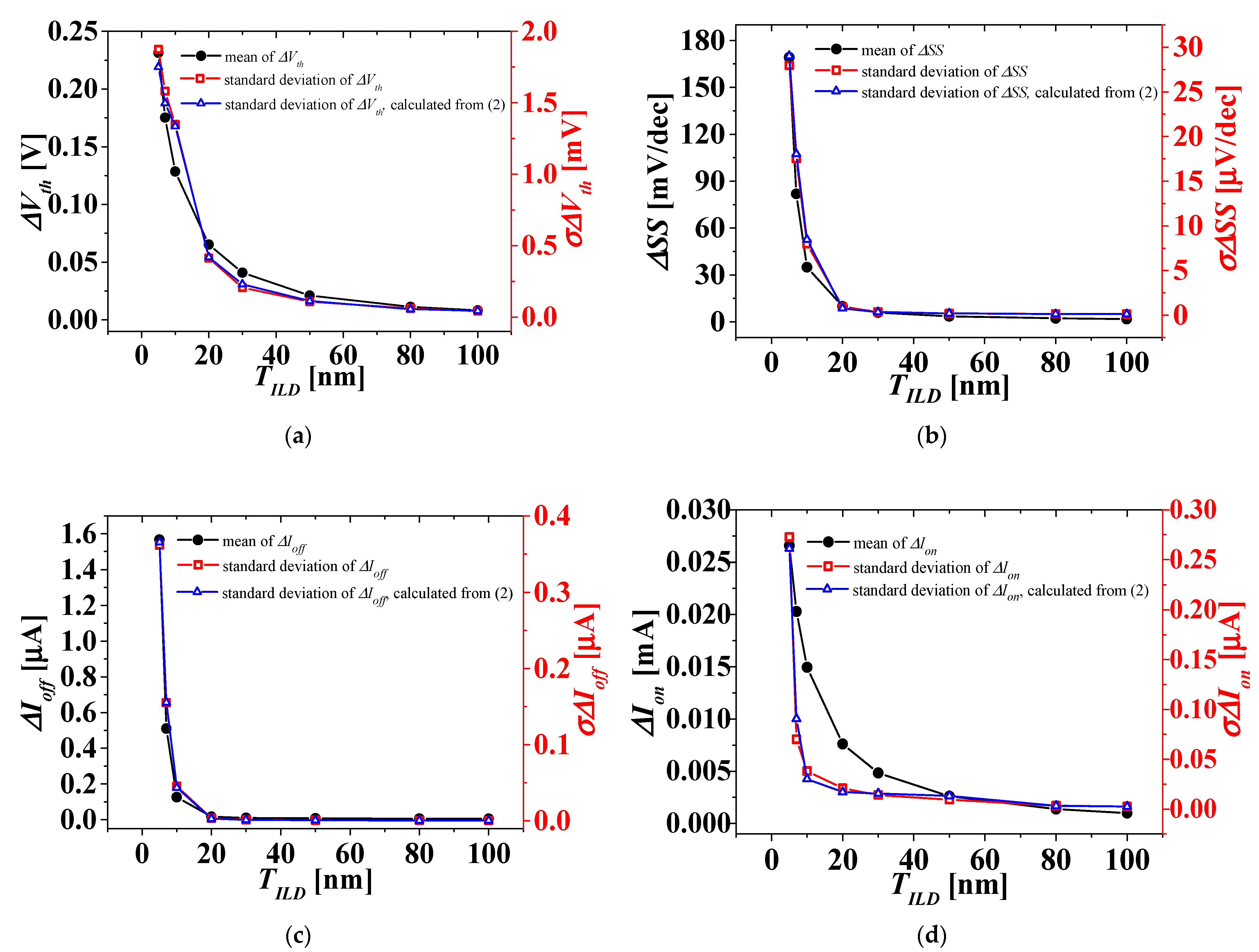

| TILD [nm] | ΔVth [V] | ΔSS [mV/dec] | ΔIoff [A] | ΔIon [A] | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Mean | σ* | σ** | Mean | σ* | σ** | Mean | σ* | σ** | Mean | σ* | σ** | |

| 5 | 0.23144 | 0.00187 | 0.00175 | 169.17 | 0.02796 | 0.02902 | 1.56 × 10−6 | 3.61 × 10−7 | 3.65 × 10−7 | 2.65 × 10−5 | 2.73 × 10−7 | 2.61 × 10−7 |

| 7 | 0.17523 | 0.00158 | 0.0015 | 81.84 | 0.01751 | 0.01804 | 5.10 × 10−7 | 1.55 × 10−7 | 1.55 × 10−7 | 2.03 × 10−5 | 6.99 × 10−8 | 9.05 × 10−8 |

| 10 | 0.12856 | 0.00135 | 0.00134 | 34.92 | 0.00798 | 0.00845 | 1.25 × 10−7 | 4.54 × 10−8 | 4.37 × 10−8 | 1.49 × 10−5 | 3.81 × 10−8 | 3.01 × 10−8 |

| 20 | 0.06525 | 4.13 × 10−4 | 4.19 × 10−4 | 9.97 | 9.22 × 10−4 | 7.62 × 10−4 | 1.64 × 10−8 | 3.43 × 10−9 | 2.91 × 10−9 | 7.61 × 10−6 | 2.08 × 10−8 | 1.69 × 10−8 |

| 30 | 0.04091 | 2.06 × 10−4 | 2.30 × 10−4 | 5.91 | 3.71 × 10−4 | 3.42 × 10−4 | 9.73 × 10−9 | 1.47 × 10−9 | 1.34 × 10−9 | 4.84 × 10−6 | 1.41 × 10−8 | 1.56 × 10−8 |

| 50 | 0.02105 | 1.07 × 10−4 | 1.12 × 10−4 | 3.49 | 1.87 × 10−4 | 2.01 × 10−4 | 7.01 × 10−9 | 8.39 × 10−10 | 8.33 × 10−10 | 2.60 × 10−6 | 9.42 × 10−9 | 1.31 × 10−8 |

| 80 | 0.01129 | 6.08 × 10−5 | 5.53 x10−5 | 2.23 | 1.43 × 10−4 | 1.21 × 10−4 | 5.46 × 10−9 | 6.49 × 10−10 | 5.43 × 10−10 | 1.38 × 10−6 | 3.43 × 10−9 | 3.30 × 10−9 |

| 100 | 0.00828 | 4.24 × 10−5 | 4.43 × 10−5 | 1.77 | 1.17 × 10−4 | 1.17 × 10−4 | 4.71 × 10−9 | 5.37 × 10−10 | 5.27 × 10−10 | 1.01 × 10−6 | 2.47 × 10−9 | 2.53 × 10−9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, G.J.; Yu, Y.S. An Investigation of the Effect of the Work-Function Variation of a Monolithic 3D Inverter Stacked with MOSFETs. Micromachines 2022, 13, 1524. https://doi.org/10.3390/mi13091524

Lee GJ, Yu YS. An Investigation of the Effect of the Work-Function Variation of a Monolithic 3D Inverter Stacked with MOSFETs. Micromachines. 2022; 13(9):1524. https://doi.org/10.3390/mi13091524

Chicago/Turabian StyleLee, Geun Jae, and Yun Seop Yu. 2022. "An Investigation of the Effect of the Work-Function Variation of a Monolithic 3D Inverter Stacked with MOSFETs" Micromachines 13, no. 9: 1524. https://doi.org/10.3390/mi13091524