A Monolithic 3-Dimensional Static Random Access Memory Containing a Feedback Field Effect Transistor

Abstract

:1. Introduction

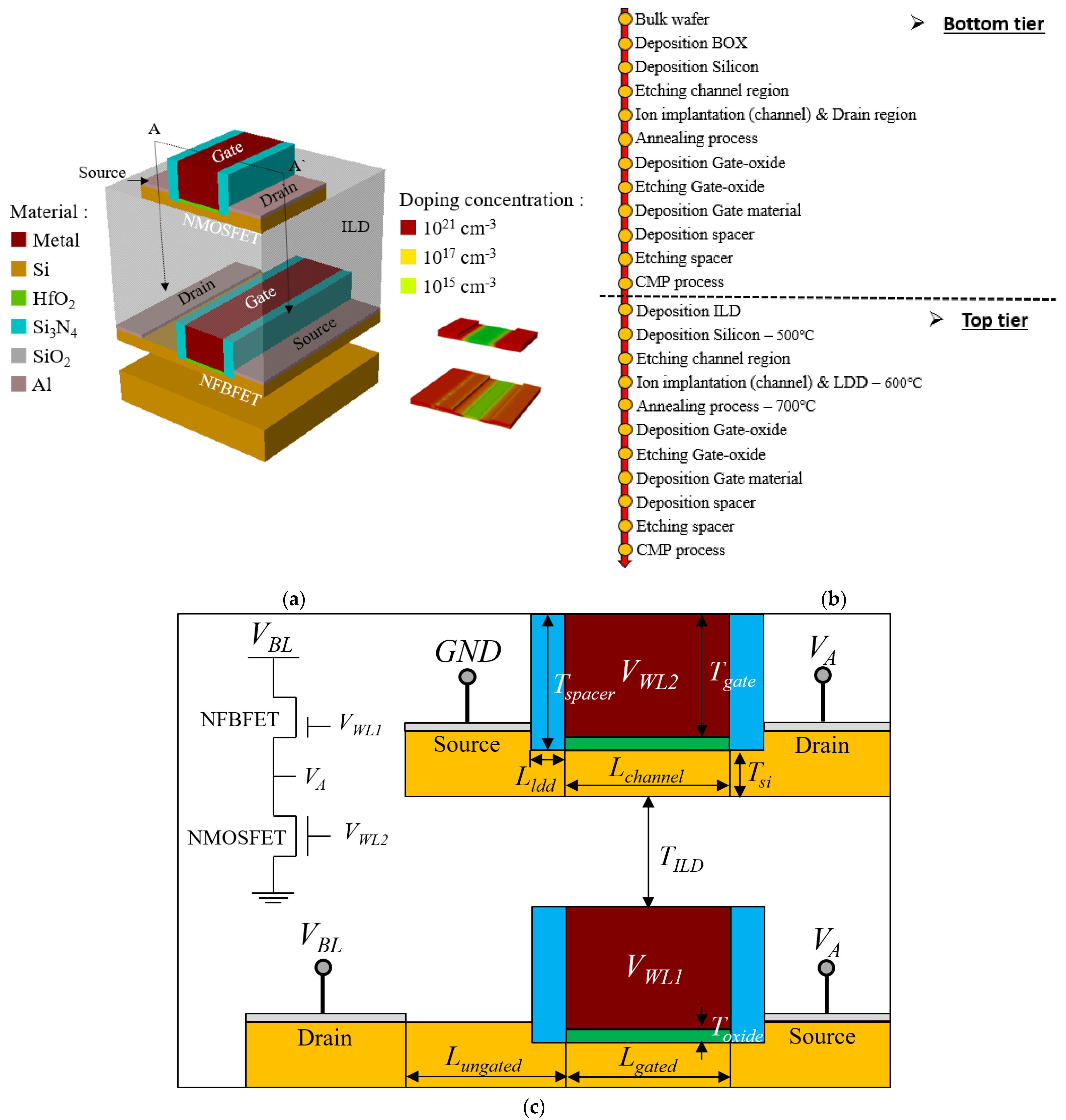

2. Simulation Structure

3. Simulation Results

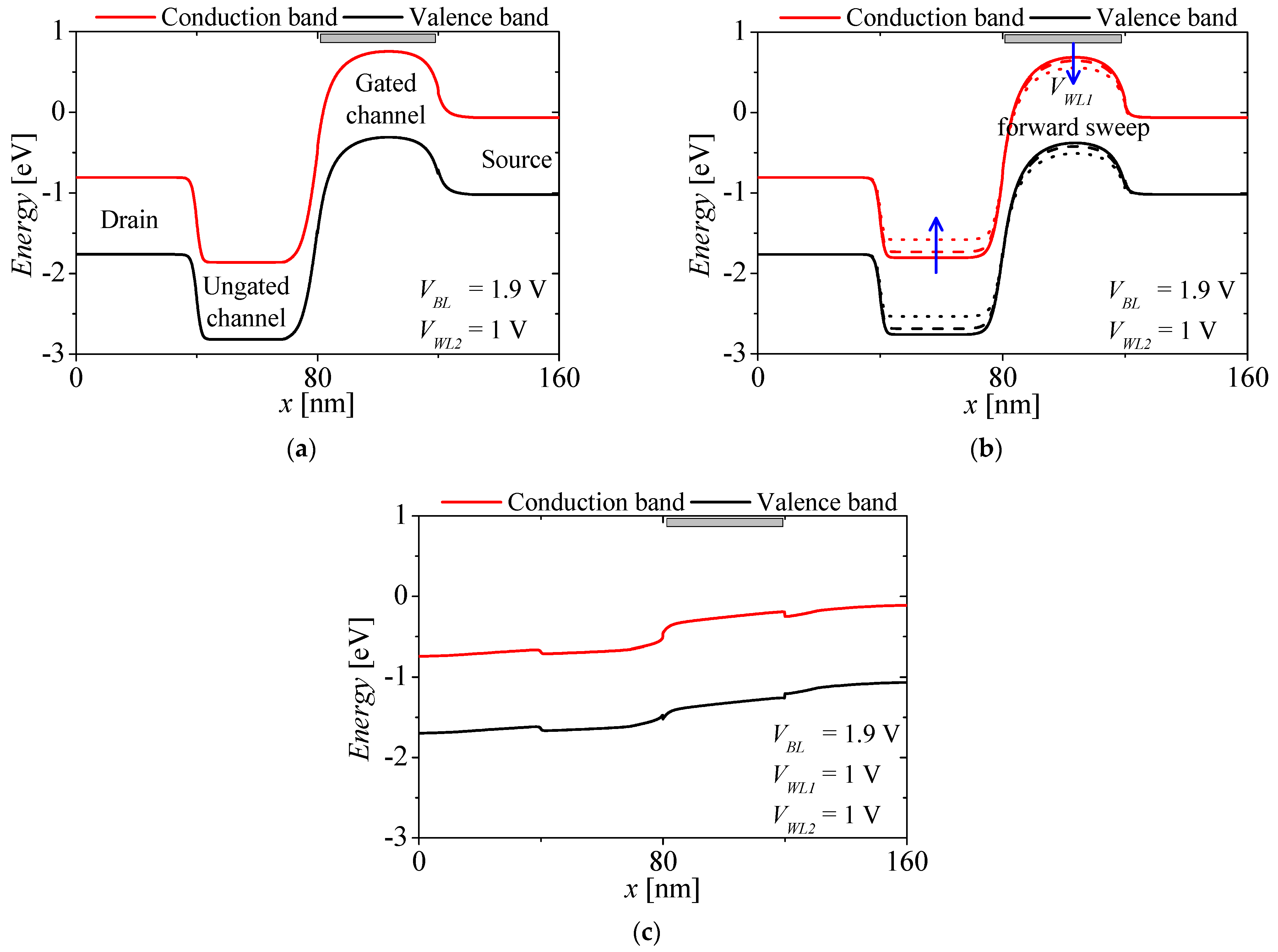

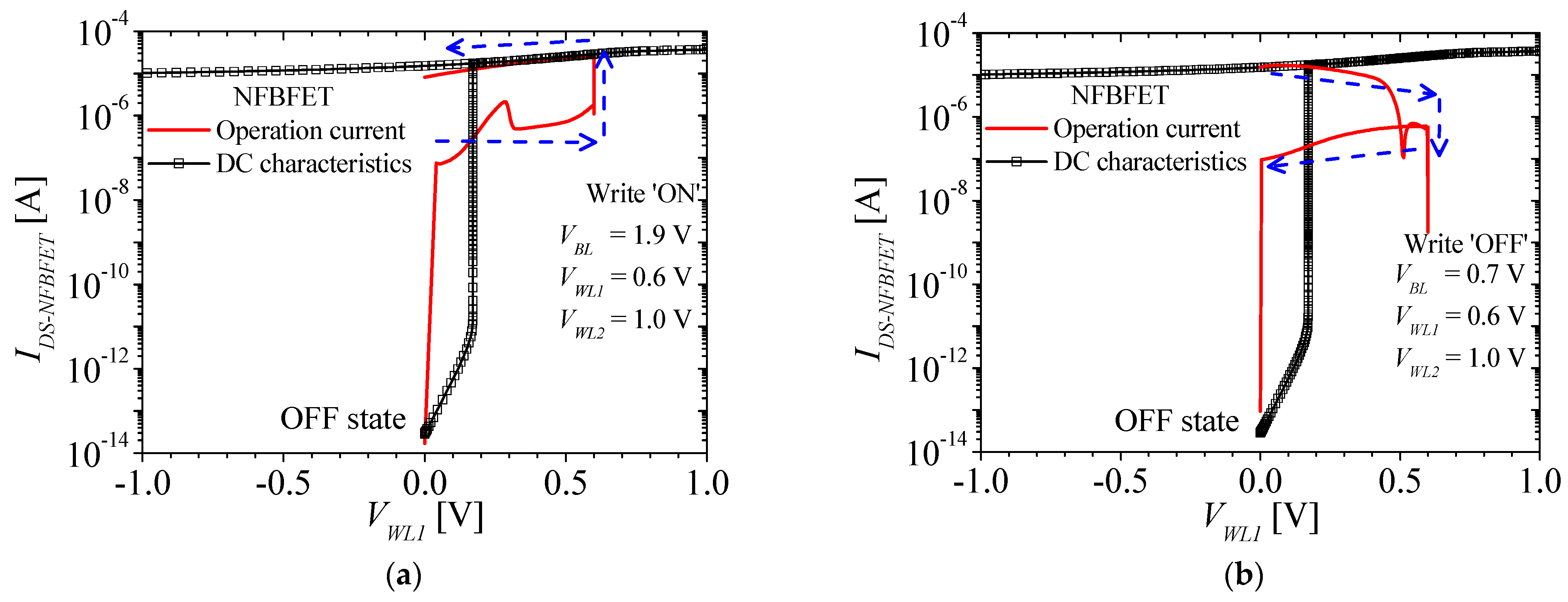

3.1. Electrical Characteristics of the NFBFET in the M3D-FBFET-SRAM Cell

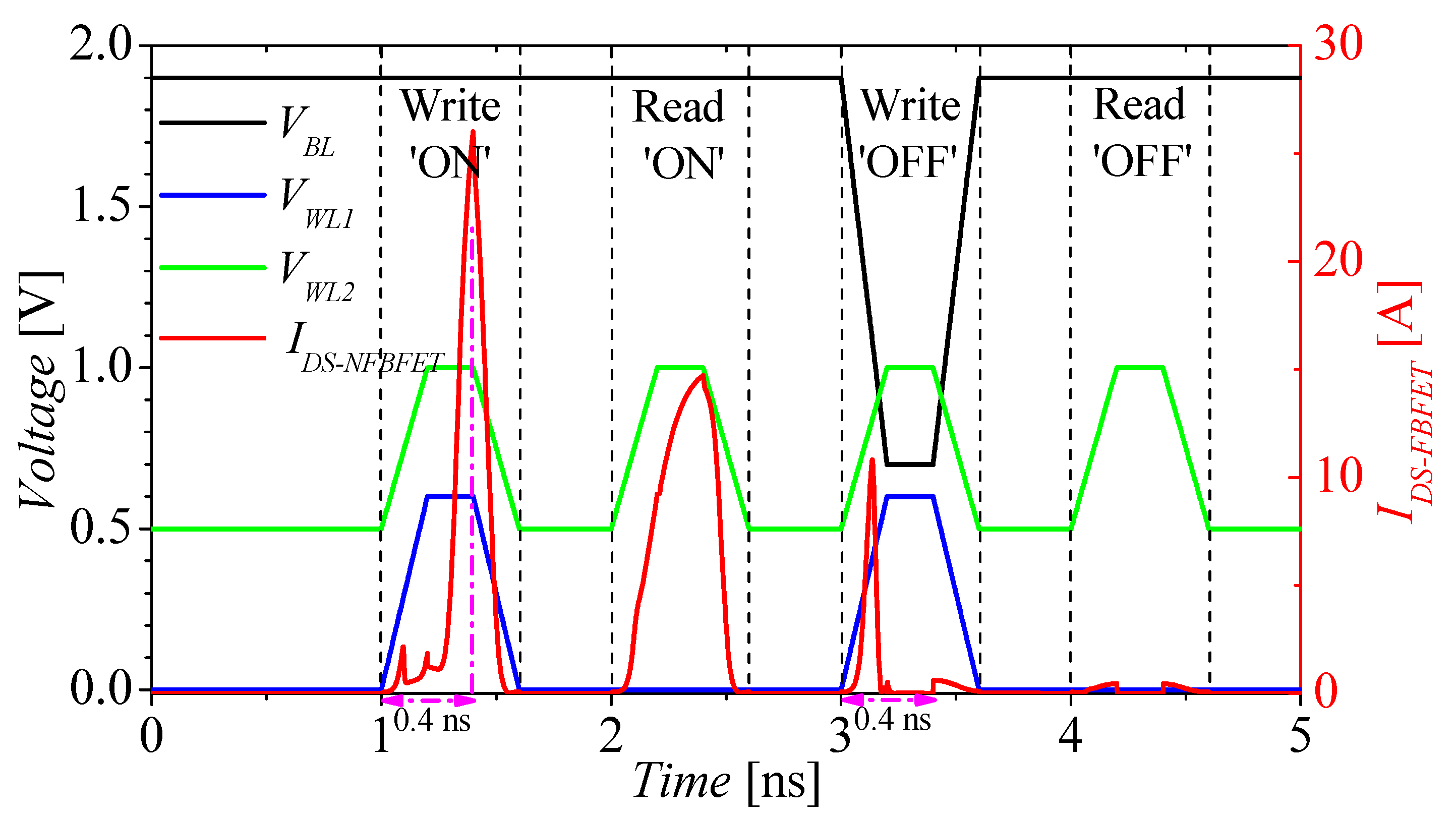

3.2. M3D-FBFET-SRAM Cell Operation

3.3. Electrical Coupling

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Jaiswal, A.; Chakraborty, I.; Agrawal, A.; Roy, K. 8T SRAM Cell as a Multibit Dot-Product Engine for Beyond Von Neumann Computing. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 2556–2567. [Google Scholar] [CrossRef]

- Lee, C.-F.; Lu, C.-H.; Lee, C.-E.; Mori, H.; Fujiwara, H.; Shih, Y.-C.; Chou, T.-L.; Chih, Y.-D.; Chang, T.-Y.J. A 12 nm 121-TOPS/W 41.6-TOPS/mm2 all digital full precision SRAM-based compute-in-memory with configurable bit-width for AI edge applications. In Proceedings of the 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 12–17 June 2022; pp. 24–25. [Google Scholar]

- Wong, S.; El-Gamal, A.; Griffin, P.; Nishi, Y.; Pease, F.; Plummer, J. Monolithic 3D integrated circuits. In Proceedings of the 2007 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), Hsinchu, Taiwan, 23–25 April 2007; pp. 1–4. [Google Scholar]

- Liu, C.; Lim, S.K. A design tradeoff study with monolithic 3D integration. In Proceedings of the Thirteenth International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 19–21 March 2012; pp. 529–536. [Google Scholar]

- Panth, S.; Samal, S.; Yu, Y.S.; Lim, S.K. Design challenges and solutions for ultra-high-density monolithic 3D ICs. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–2. [Google Scholar]

- Park, J.-H.; Tada, M.; Kuzum, D.; Kapur, P.; Yu, H.-Y.; Philip Wong, H.-S.; Saraswat, K.C. Low temperature (≤380 °C) and high performance Ge CMOS technology with novel source/drain by metal-induced dopants activation and high-k/metal gate stack for monolithic 3D integration. In Proceedings of the 2008 IEEE International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Vinet, M.; Batude, P.; Fenouillet-Beranger, C.; Clermidy, F.; Brunet, L.; Rozeau, O.; Hartmannn, J.M.; Billoint, O.; Cibrario, G.; Previtali, B.; et al. Monolithic 3D integration: A powerful alternative to classical 2D scaling. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–3. [Google Scholar]

- Nayak, D.K.; Banna, S.; Samal, S.K.; Lim, S.K. Power, performance, and cost comparisons of monolithic 3D ICs and TSV-based 3D ICs. In Proceedings of the 2015 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–2. [Google Scholar]

- Panth, S.; Samadi, K.; Du, Y.; Lim, S.K. High-density integration of functional modules using monolithic 3D-IC technology. In Proceedings of the 2013 18th Asia and South Pacific Design Automation Conference (ASP-DAC), Yokohama, Japan, 22–25 January 2013; pp. 681–686. [Google Scholar]

- Lee, Y.-J.; Lim, S.K. Ultrahigh density logic designs using monolithic 3-D integration. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2013, 32, 1892–1905. [Google Scholar] [CrossRef]

- Shulaker, M.M.; Wu, T.F.; Pal, A.; Zhao, L.; Nishi, Y.; Saraswat, K.; Philip Wong, H.-S.; Mitra, S. Monolithic 3D integration of logic and memory: Carbon nanotube FETs, resistive RAM, and silicon FETs. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014. [Google Scholar]

- Lee, G.J.; Ahn, T.J.; Lim, S.K.; Yu, Y.S. Investigation into electrical characteristics of logic circuit consisting of modularized monolithic 3D inverter unit cell. J. Inf. Commun. Converg. Eng. 2022, 20, 137–142. [Google Scholar] [CrossRef]

- Yu, M.-J.; Lin, R.-P.; Chang, Y.-H.; Hou, T.-H. High-voltage amorphous InGaZnO TFT with Al2O3 high-k dielectric for low-temperature monolithic 3-D integration. IEEE Trans. Electron Devices 2016, 63, 3944–3949. [Google Scholar] [CrossRef]

- Jiang, J.; Parto, K.; Cao, W.; Banerjee, K. Ultimate monolithic-3D integration with 2D materials: Rationale, prospects, and challenges. IEEE J. Electron Devices Soc. 2019, 7, 878–887. [Google Scholar] [CrossRef]

- Ahn, T.-J.; Yu, Y.S.; Kim, N.H. Comparison of two-types of monolithic 3D inverter consisting of MOSFETs and junctionless FETs. In Proceedings of the 2020 International Conference on Electronics, Information, and Communication (ICEIC), Barcelona, Spain, 19–22 January 2020; pp. 1–3. [Google Scholar]

- Shulaker, M.M.; Saraswat, K.; Philip Wong, H.-S.; Mitra, S. Monolithic three-dimensional integration of carbon nanotube FETs with silicon CMOS. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Paper, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Ahn, T.J.; Choi, B.H.; Lim, S.K.; Yu, Y.S. Electrical Coupling and Simulation of Monolithic 3D Logic Circuits and Static Random Access Memory. Micromachines 2019, 10, 637. [Google Scholar] [CrossRef] [PubMed]

- Boumchedda, R.; Noel, J.-P.; Giraud, B.; Akyel, K.C.; Brocard, M.; Turgis, D.; Beigne, E. High-Density 4T SRAM Bitcell in 14-Nm 3-D CoolCube Technology Exploiting Assist Techniques. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 2296–2306. [Google Scholar] [CrossRef]

- Batude, P.; Jaud, M.-A.; Thomas, O.; Clavelier, L.; Pouydebasque, A.; Vinet, M.; Deleonibus, S.; Amara, A. 3D CMOS Integration: Introduction of Dynamic Coupling and Application to Compact and Robust 4T SRAM. In Proceedings of the 2008 IEEE International Conference on Integrated Circuit Design and Technology and Tutorial, Grenoble, France, 2–4 June 2008; pp. 281–284. [Google Scholar]

- Srinivasa, S.; Li, X.; Chang, M.-F.; Sampson, J.; Gupta, S.K.; Narayanan, V. Compact 3-D-SRAM memory with concurrent row and column data access capability using sequential monolithic 3-D integration. IEEE Trans. Very Large Scale Integr. Syst. 2018, 26, 671–683. [Google Scholar] [CrossRef]

- Naito, T.; Ishida, T.; Onoduka, T.; Nishigoori, M.; Nakayama, T.; Ueno, Y.; Ishimoto, Y.; Suzuki, A.; Chung, W.; Madurawe, R.; et al. World’s first monolithic 3D-FPGA with TFT SRAM over 90 nm 9 layer Cu CMOS. In Proceedings of the 2010 Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 219–220. [Google Scholar]

- Yu, C.-H.; Su, P.; Chuang, C.-T. Performance and stability benchmarking of monolithic 3-D logic circuits and SRAM cells with monolayer and few-layer transition metal dichalcogenide MOSFETs. IEEE Trans. Electron Devices 2017, 64, 2445–2451. [Google Scholar] [CrossRef]

- Tripathi, S.; Choudhary, S.; Misra, P.K. A novel STT-SOT MTJ-based nonvolatile SRAM for power gating application. IEEE Trans. Electron Devices 2022, 69, 1058–1064. [Google Scholar] [CrossRef]

- Garg, N.; Pratap, Y.; Kabra, S. Stability and reliability performance of double gate junctionless transistor (DG-JLT) 6T SRAM. In Proceedings of the 2021 International Conference on Industrial Electronics Research and Applications (ICIERA), New Delhi, India, 22–24 December 2021; pp. 1–5. [Google Scholar]

- Woo, S.; Cho, J.; Lim, D.; Cho, K.; Kim, S. Transposable 3T-SRAM Synaptic Array Using Independent Double-Gate Feedback Field-Effect Transistors. IEEE Trans. Electron Devices 2019, 66, 4753–4758. [Google Scholar] [CrossRef]

- Padilla, A.; Yeung, C.W.; Shin, C.; Hu, C.; Liu, T.-J.K. Feedback FET: A Novel Transistor Exhibiting Steep Switching Behavior at Low Bias Voltages. In Proceedings of the 2008 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Cho, J.; Lim, D.; Woo, S.; Cho, K.; Kim, S. Static Random Access Memory Characteristics of Single-Gated Feedback Field-Effect Transistors. IEEE Trans. Electron Devices 2019, 66, 413–419. [Google Scholar] [CrossRef]

- Silvaco Int. Victory Process, version 7.58.3. R Manual; Silvaco Int.: Santa Clara, CA, USA, 2021.

- Silvaco Int. ATLAS, version 5.32.1. R Manual; Silvaco Int.: Santa Clara, CA, USA, 2022.

- Lee, K.H.; El-Dirani, H.; Fonteneau, P.; Bawedin, M.; Cristoloveanu, S. Sharp Logic Switch Based on Band Modulation. IEEE Electron Device Lett. 2019, 40, 1852–1855. [Google Scholar] [CrossRef]

- Santos, C.; Vivet, P.; Thuries, S.; Billoint, O.; Colonna, J.-P.; Coudrain, P.; Wang, L. Thermal Performance of CoolCubeTM Monolithic and TSV-Based 3D Integration Processes. In Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 8–11 November 2016; pp. 1–5. [Google Scholar]

- Yu, Y.S.; Panth, S.; Lim, S.K. Electrical Coupling of Monolithic 3-D Inverters. IEEE Trans. Electron Devices 2016, 63, 1–4. [Google Scholar] [CrossRef]

- Oh, J.H.; Yu, Y.S. Investigation of monolithic 3D integrated circuit inverter with feedback field effect transistors using TCAD simulation. Micromachines 2020, 11, 852. [Google Scholar] [CrossRef] [PubMed]

| Parameters | Description | Value/Unit |

|---|---|---|

| Lungated | Length of the ungated channel region for the NFBFET | 40 nm |

| Lgated, Lchannel | Length of the gated channel region for the NFBFET and NMOSFET | 40 nm |

| LLDD | Length of the lightly doped drain (LDD) region | 10 nm |

| Tgate | Thickness of the gate | 30 nm |

| Tspacer | Thickness of the spacer | 33 nm |

| Toxide | Thickness of the gate oxide | 3 nm |

| Tsi | Thickness of the silicon body | 6 nm |

| TILD | Thickness of the interlayer dielectric (ILD) | Var. |

| Nsource, Ndrain | Doping concentration of the source and drain regions | 1 × 1020 cm−3 |

| Ngated | Doping concentration of the gated channel region for NFBFET | 2 × 1017 cm−3 |

| Nungated | Doping concentration of the ungated channel region for NFBFET | 1 × 1020 cm−3 |

| Nch | Doping concentration of the channel region for NMOSFET | 1 × 1015 cm−3 |

| NLDD | Doping concentration of the LDD region for NMOSFET | 1 × 1018 cm−3 |

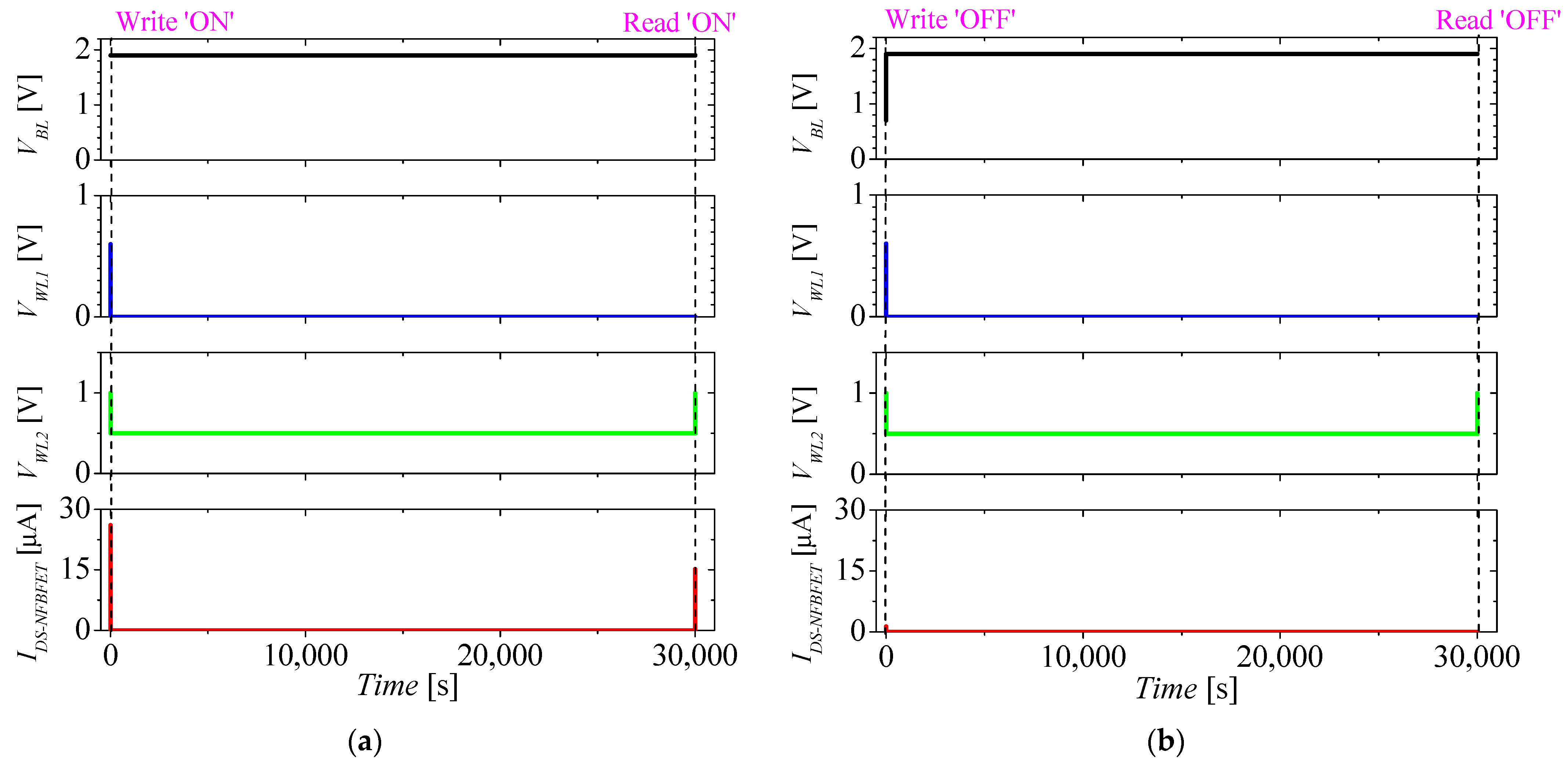

| Voltages | Write ‘ON’ | Write ‘OFF’ | Hold | Read |

|---|---|---|---|---|

| VBL | 1.9 V | 0.7 V | 1.9 V | 1.9 V |

| VWL1 | 0.6 V | 0.6 V | 0.0 V | 0.0 V |

| VWL2 | 1.0 V | 1.0 V | 0.5 V | 1.0 V |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oh, J.H.; Yu, Y.S. A Monolithic 3-Dimensional Static Random Access Memory Containing a Feedback Field Effect Transistor. Micromachines 2022, 13, 1625. https://doi.org/10.3390/mi13101625

Oh JH, Yu YS. A Monolithic 3-Dimensional Static Random Access Memory Containing a Feedback Field Effect Transistor. Micromachines. 2022; 13(10):1625. https://doi.org/10.3390/mi13101625

Chicago/Turabian StyleOh, Jong Hyeok, and Yun Seop Yu. 2022. "A Monolithic 3-Dimensional Static Random Access Memory Containing a Feedback Field Effect Transistor" Micromachines 13, no. 10: 1625. https://doi.org/10.3390/mi13101625