Schottky Barrier Height Tuning via the Dopant Segregation Technique through Low-Temperature Microwave Annealing

Abstract

:1. Introduction

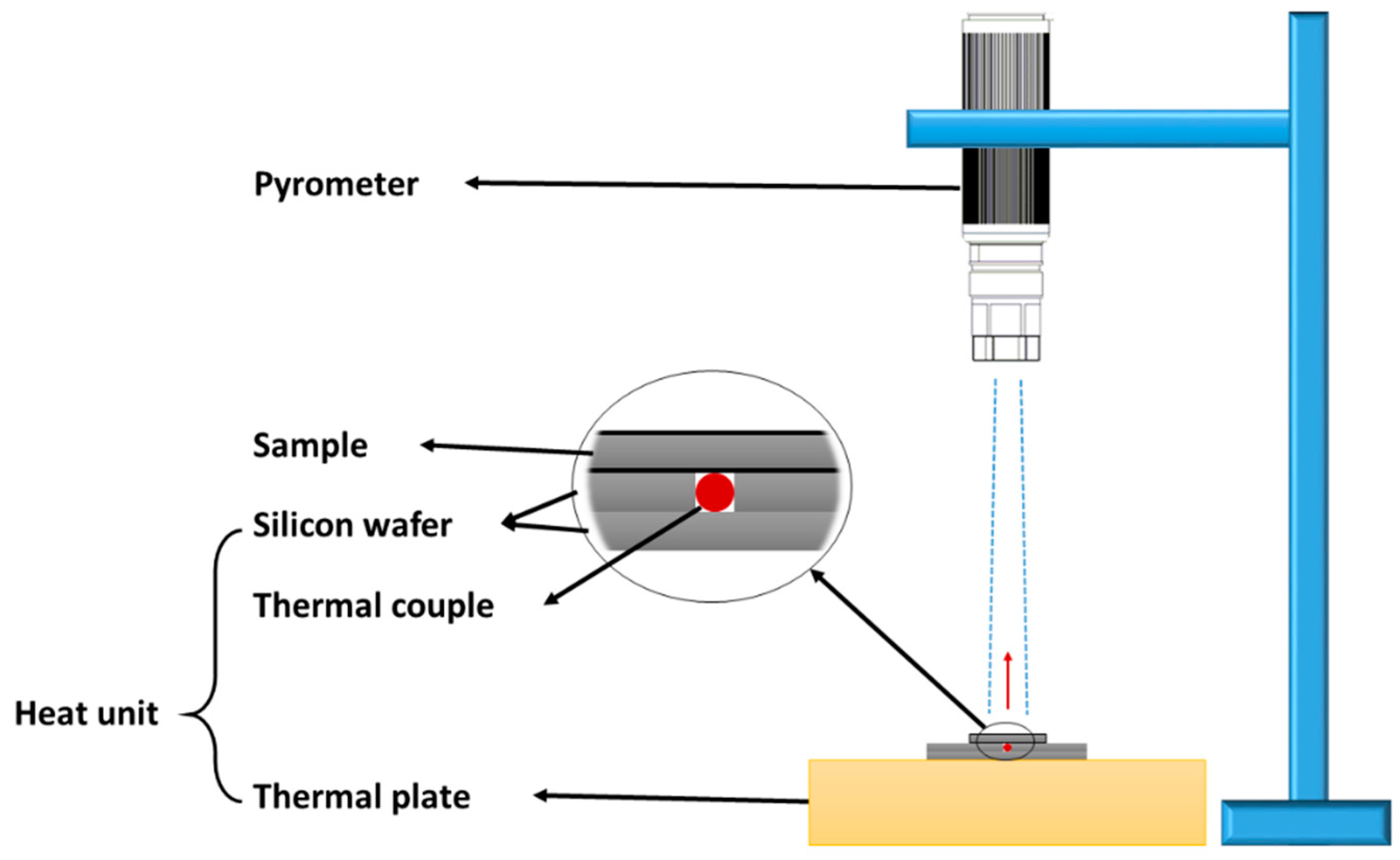

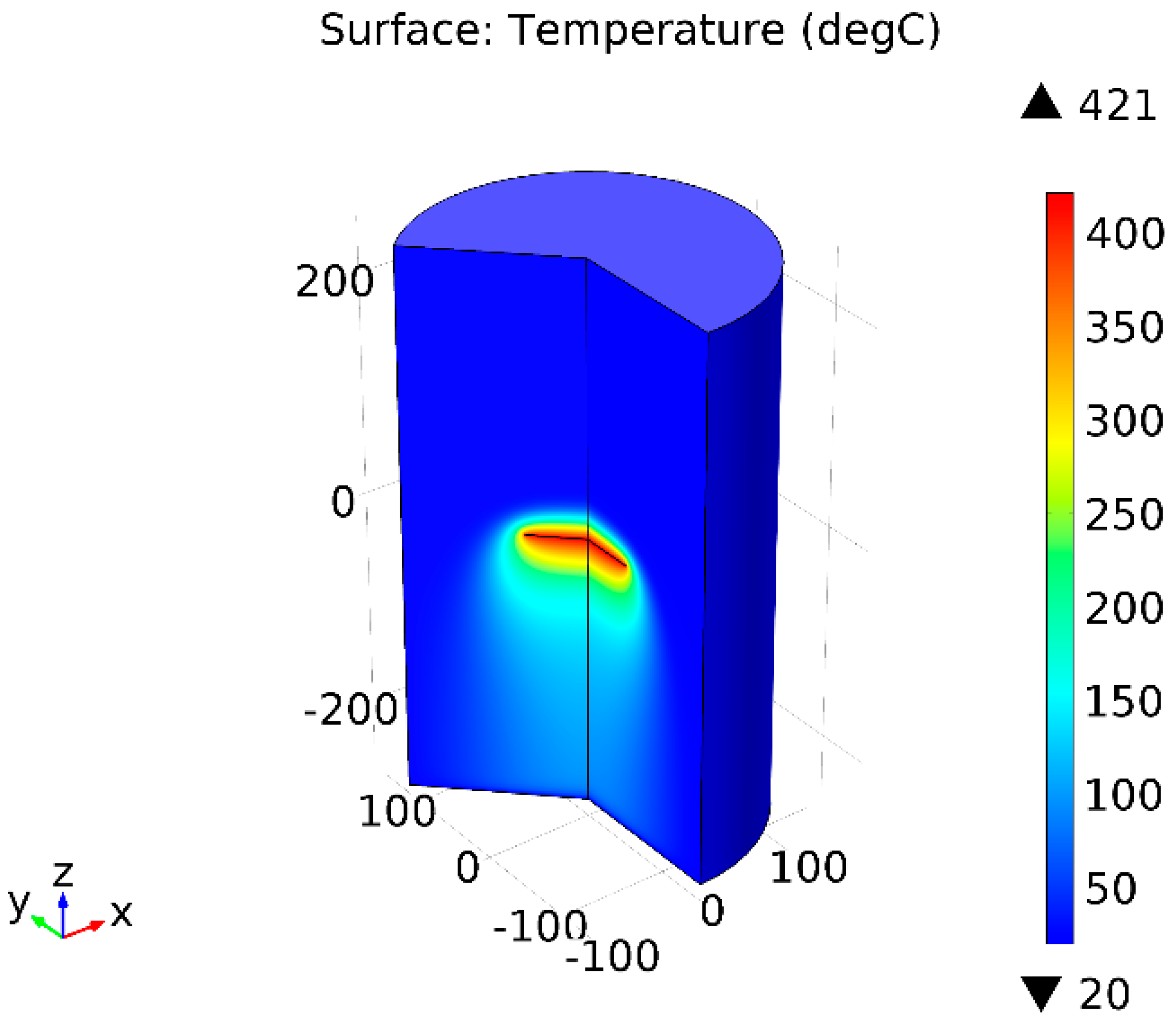

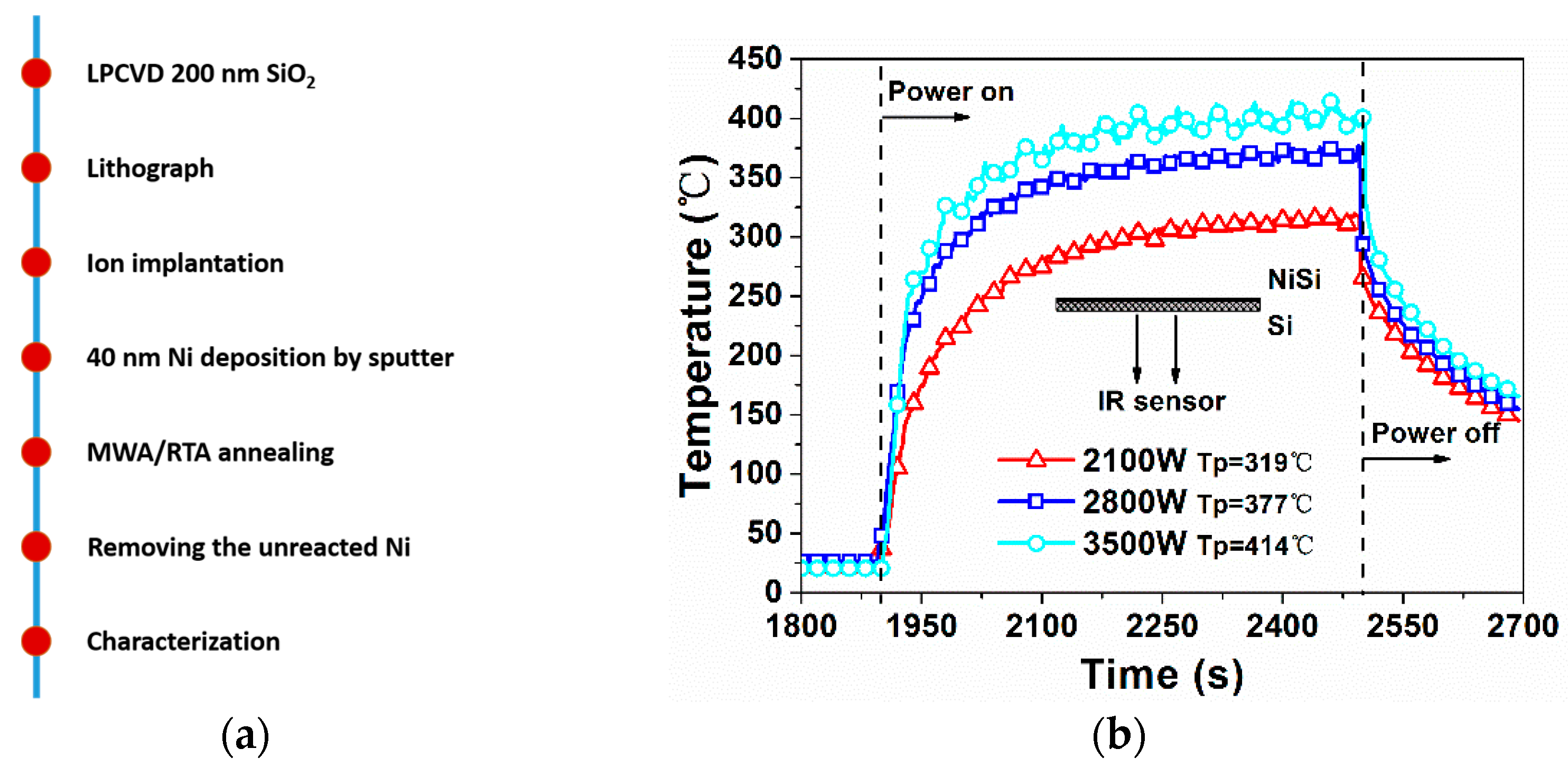

2. Experimental Section

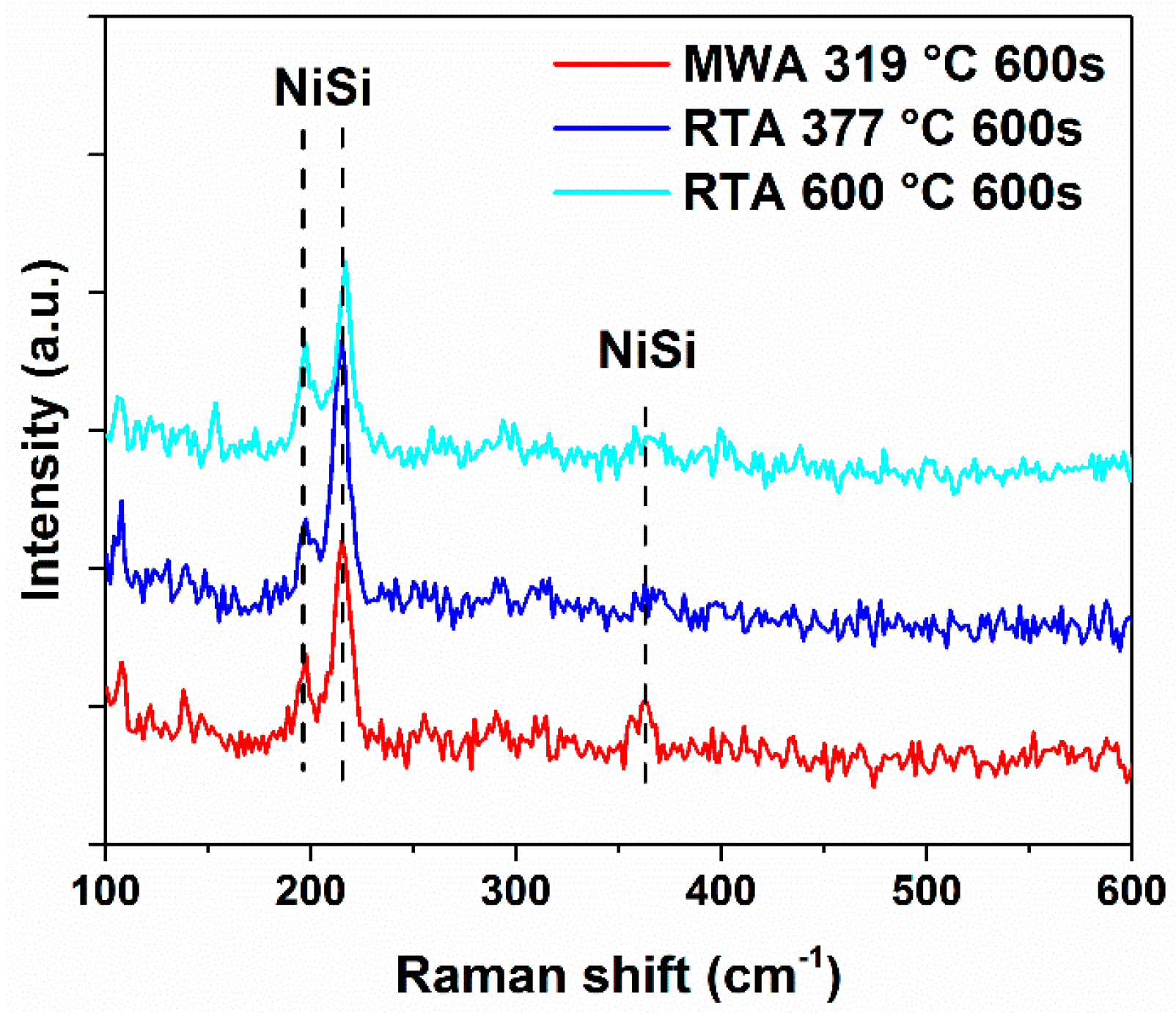

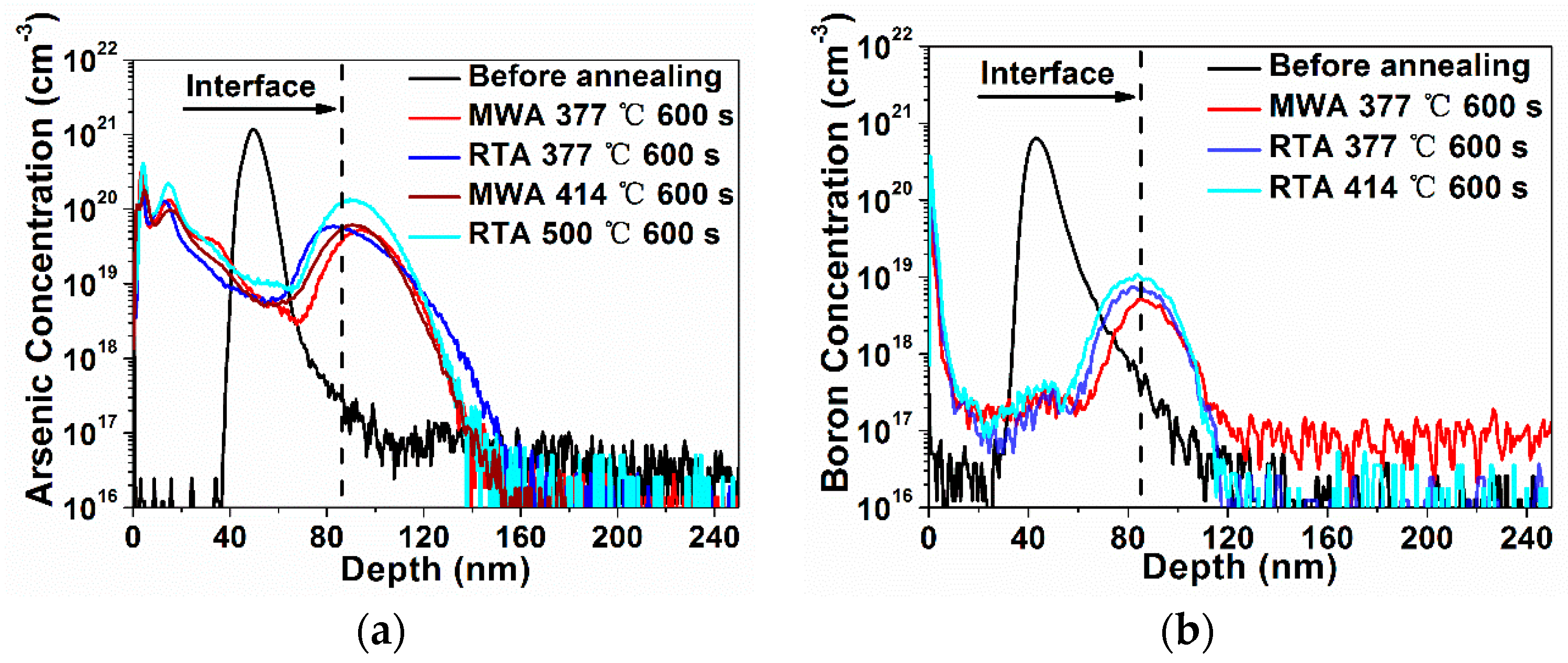

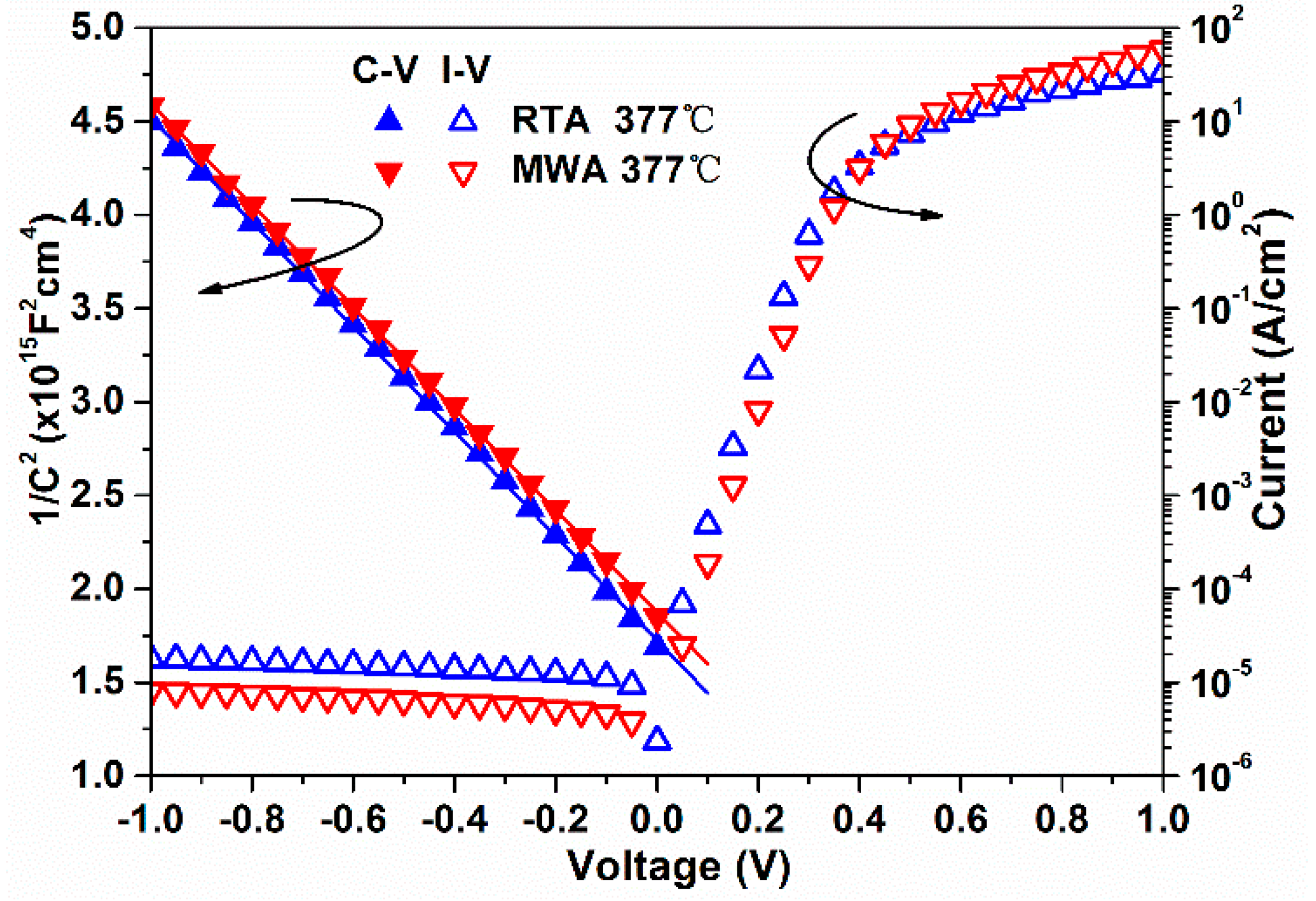

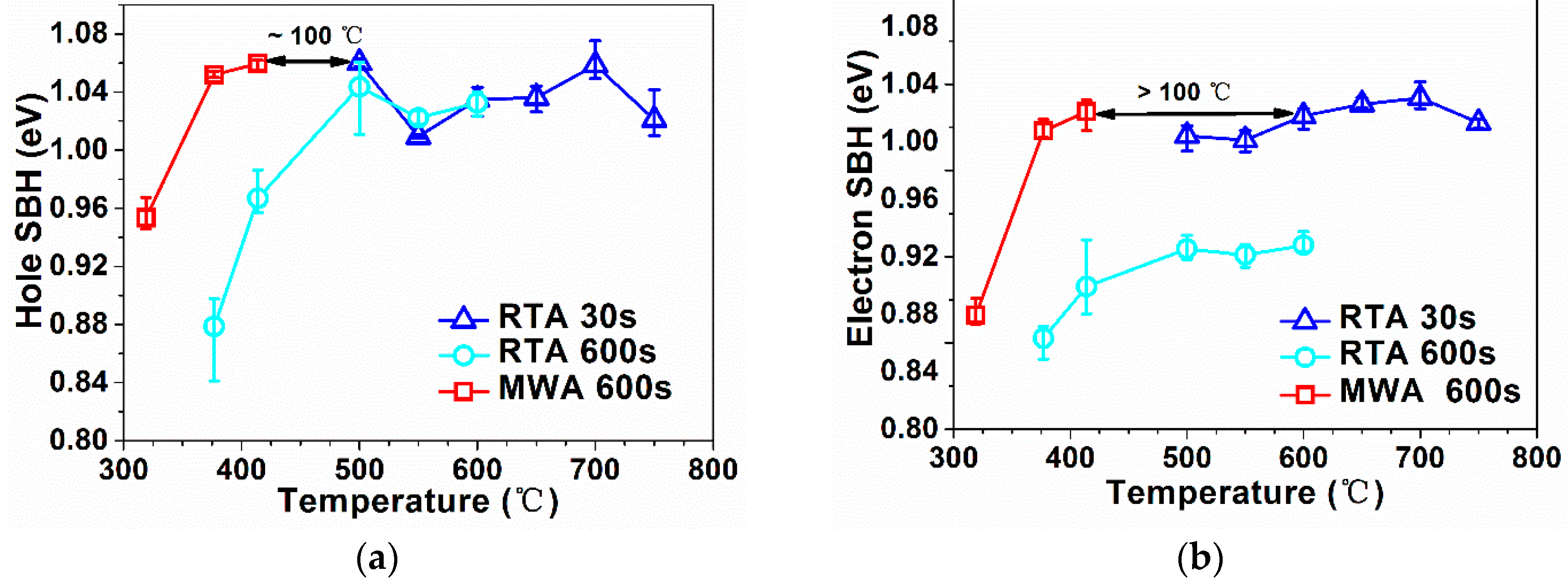

3. Results and Discussion

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Appendix A

References

- Shannon, J.M. Reducing the effective height of a Schottky barrier using low-energy ion implantation. Appl. Phys. Lett. 1974, 24. [Google Scholar] [CrossRef]

- Zhang, Z.; Pagette, F.; D’Emic, C.; Yang, B.; Lavoie, C.; Zhu, Y.; Hopstaken, M.; Maurer, S.; Murray, C.; Guillorn, M.; et al. Sharp Reduction of Contact Resistivities by Effective Schottky Barrier Lowering with Silicides as Diffusion Sources. IEEE Electron Device Lett. 2010, 31, 731–733. [Google Scholar] [CrossRef]

- Luo, J.; Wu, D.P.; Qiu, Z.J.; Lu, J.; Hultman, L.; Ostling, M.; Zhang, S.L. On Different Process Schemes for MOSFETs with a Controllable NiSi-Based Metallic Source/Drain. IEEE Trans. Electron Dev. 2011, 58, 1898–1906. [Google Scholar] [CrossRef]

- Larrieu, G.; Dubois, E.; Valentin, R.; Breil, N.; Danneville, F.; Dambrine, G.; Raskin, J.P.; Pesant, J.C. Low temperature implementation of dopant-segregated band-edge metallic S/D junctions in thin-body SOI p-MOSFETs. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; Volumes 1 and 2, pp. 147–150.

- Connelly, D.; Faulkner, C.; Grupp, D.E. Performance advantage of Schottky source/drain in ultrathin-body silicon-on-insulator and dual-gate CMOS. IEEE Trans. Electron Dev. 2003, 50, 1340–1345. [Google Scholar] [CrossRef]

- Qiu, Z.J.; Zhang, Z.; Ostling, M.; Zhang, S.L. A comparative study of two different schemes to dopant segregation at NiSi/Si and PtSi/Si interfaces for Schottky barrier height lowering. IEEE Trans. Electron Dev. 2008, 55, 396–403. [Google Scholar] [CrossRef]

- Yamauchi, T.; Nishi, Y.; Tsuchiya, Y.; Kinoshita, A.; Koga, J.; Kato, K. Novel doping technology for a 1 nm NiSi/Si junction with dipoles comforting Schottky (DCS) barrier. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; Volumes 1 and 2, pp. 963–966.

- Zhang, Z.; Qiu, Z.J.; Liu, R.; Ostling, M.; Zhang, S.L. Schottky-barrier height tuning by means of ion implantation into preformed silicide films followed by drive-in anneal. IEEE Electron Device Lett. 2007, 28, 565–568. [Google Scholar] [CrossRef]

- Yamaguchi, T.; Kawasaki, Y.; Yamashita, T.; Yamamoto, Y.; Goto, Y.; Tsuchimoto, J.; Kudo, S.; Maekawa, K.; Fujisawa, M.; Asai, K. Low-Resistive and Homogenous NiPt-Silicide Formation using Ultra-Low Temperature Annealing with Microwave System for 22 nm-node CMOS and beyond. In Proceedings of the 2010 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 26–26.

- Hu, C.; Xu, P.; Fu, C.C.; Zhu, Z.W.; Gao, X.D.; Jamshidi, A.; Noroozi, M.; Radamson, H.; Wu, D.P.; Zhang, S.L. Characterization of Ni(Si,Ge) films on epitaxial SiGe(100) formed by microwave annealing. Appl. Phys. Lett. 2012, 101. [Google Scholar] [CrossRef]

- Lee, Y.J.; Cho, T.C.; Chuang, S.S.; Hsueh, F.K.; Lu, Y.L.; Sung, P.J.; Chen, H.C.; Current, M.I.; Tseng, T.Y.; Chao, T.S.; et al. Low-Temperature Microwave Annealing Processes for Future IC Fabrication—A Review. IEEE Trans. Electron Dev. 2014, 61, 651–665. [Google Scholar] [CrossRef]

- Lin, Y.H.; Tsai, Y.H.; Hsu, C.C.; Luo, G.L.; Lee, Y.J.; Chien, C.H. Microwave Annealing for NiSiGe Schottky Junction on SiGe P-Channel. Materials 2015, 8, 7519–7523. [Google Scholar] [CrossRef]

- Xu, P.; Fu, C.C.; Hu, C.; Zhang, D.W.; Wu, D.P.; Luo, J.; Zhao, C.; Zhang, Z.B.; Zhang, S.L. Ultra-shallow junctions formed using microwave annealing. Appl. Phys. Lett. 2013, 102. [Google Scholar] [CrossRef]

- Luo, J.; Qiu, Z.J.; Zha, C.L.; Zhang, Z.; Wu, D.P.; Lu, J.; Akerman, J.; Ostling, M.; Hultman, L.; Zhang, S.L. Surface-energy triggered phase formation and epitaxy in nanometer-thick Ni1−xPtx silicide films. Appl. Phys. Lett. 2010, 96. [Google Scholar] [CrossRef]

- Cichon, S.; Machac, P.; Barda, B.; Machovic, V.; Slepicka, P. Raman study of Ni and Ni silicide contacts on 4H- and 6H-SiC. Thin Solid Films 2012, 520, 4378–4388. [Google Scholar] [CrossRef]

- Li, F.; Lustig, N.; Klosowski, P.; Lannin, J.S. Disorder-Induced Raman-Scattering in NiSi2. Phys. Rev. B 1990, 41, 10210–10213. [Google Scholar] [CrossRef]

- Iwai, H.; Ohguro, T.; Ohmi, S. NiSi salicide technology for scaled CMOS. Microelectron. Eng. 2002, 60, 157–169. [Google Scholar] [CrossRef]

- Sze, S.M. VLSI Technology, 2nd ed.; McGraw-Hill: New York, NY, USA, 1988; pp. 286–288. [Google Scholar]

- Jiang, Y.L.; Agarwal, A.; Ru, G.P.; Qu, X.P.; Poate, J.; Li, B.Z.; Holland, W. Nickel silicidation on n and p-type junctions at 300 degrees C. Appl. Phys. Lett. 2004, 85, 410–412. [Google Scholar] [CrossRef]

- Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; Wiley-IEEE Press: Hoboken, NJ, 2006; pp. 161–162. [Google Scholar]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Wiley-Interscience: Hoboken, NJ, USA, 2007; pp. 154–157. [Google Scholar]

- Firrincieli, A.; Martens, K.; Rooyackers, R.; Vincent, B.; Rosseel, E.; Simoen, E.; Geypen, J.; Bender, H.; Claeys, C.; Kittl, J.A. Study of ohmic contacts to n-type Ge: Snowplow and laser activation. Appl. Phys. Lett. 2011, 99. [Google Scholar] [CrossRef]

| Implanted Ions/Substrate | Arsenic/p-Type | Boron/n-Type | ||||

|---|---|---|---|---|---|---|

| Annealing technique | MWA | RTA | RTA | MWA | RTA | RTA |

| Time (s) | 600 | 600 | 30 | 600 | 600 | 30 |

| Temperature (°C) | 319 | 377 | 500 | 319 | 377 | 500 |

| 377 | 414 | 550 | 377 | 414 | 550 | |

| 414 | 500 | 600 | 414 | 500 | 600 | |

| - | 550 | 650 | - | 550 | 650 | |

| - | 600 | 700 | - | 600 | 700 | |

| - | - | 750 | - | - | 750 | |

| Annealing Technique | Time (s) | Temperature (°C) | Implanted Ions/Substrate | |||

|---|---|---|---|---|---|---|

| Arsenic/p-Type | Boron/n-Type | |||||

| ϕbp (eV) | Ideality Factor (@ −0.15 V) | ϕbn (eV) | Ideality Factor (@ 0.15 V) | |||

| MWA | 600 | 319 | 0.96 | 1.077 | 0.85 | 1.021 |

| 377 | 1.05 | 1.125 | 0.94 | 1.027 | ||

| 414 | 1.06 | 1.074 | 0.95 | 1.025 | ||

| RTA | 600 | 377 | 0.88 | 1.024 | 0.86 | 1.049 |

| 414 | 0.97 | 1.092 | 0.90 | 1.050 | ||

| 500 | 1.04 | 1.063 | 0.93 | 1.056 | ||

| 550 | 1.02 | 1.118 | 0.92 | 1.034 | ||

| 600 | 1.03 | 1.065 | 0.93 | 1.037 | ||

| 30 | 500 | 1.06 | 1.012 | 0.94 | 1.025 | |

| 550 | 1.01 | 1.029 | 0.93 | 1.018 | ||

| 600 | 1.03 | 1.059 | 0.95 | 1.025 | ||

| 650 | 1.04 | 1.043 | 0.95 | 1.043 | ||

| 700 | 1.06 | 1.093 | 0.95 | 1.060 | ||

| 750 | 1.02 | 1.121 | 0.94 | 1.005 | ||

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fu, C.; Zhou, X.; Wang, Y.; Xu, P.; Xu, M.; Wu, D.; Luo, J.; Zhao, C.; Zhang, S.-L. Schottky Barrier Height Tuning via the Dopant Segregation Technique through Low-Temperature Microwave Annealing. Materials 2016, 9, 315. https://doi.org/10.3390/ma9050315

Fu C, Zhou X, Wang Y, Xu P, Xu M, Wu D, Luo J, Zhao C, Zhang S-L. Schottky Barrier Height Tuning via the Dopant Segregation Technique through Low-Temperature Microwave Annealing. Materials. 2016; 9(5):315. https://doi.org/10.3390/ma9050315

Chicago/Turabian StyleFu, Chaochao, Xiangbiao Zhou, Yan Wang, Peng Xu, Ming Xu, Dongping Wu, Jun Luo, Chao Zhao, and Shi-Li Zhang. 2016. "Schottky Barrier Height Tuning via the Dopant Segregation Technique through Low-Temperature Microwave Annealing" Materials 9, no. 5: 315. https://doi.org/10.3390/ma9050315