Hybrid Integrated Platforms for Silicon Photonics

Abstract

:1. Introduction

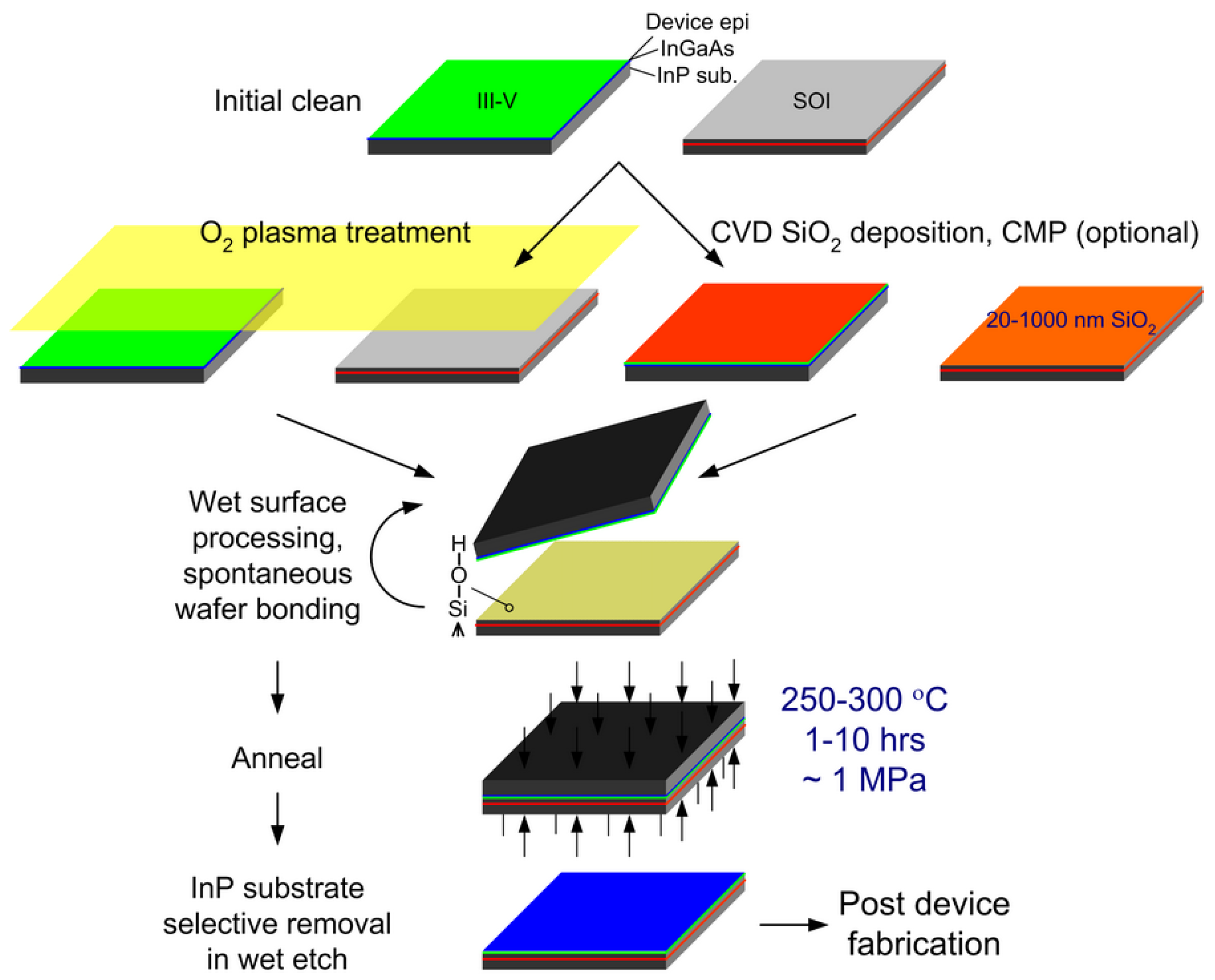

2. O2 Plasma-Assisted/SiO2 Covalent Direct Bonding

2.1. Bonding process flow and mechanism

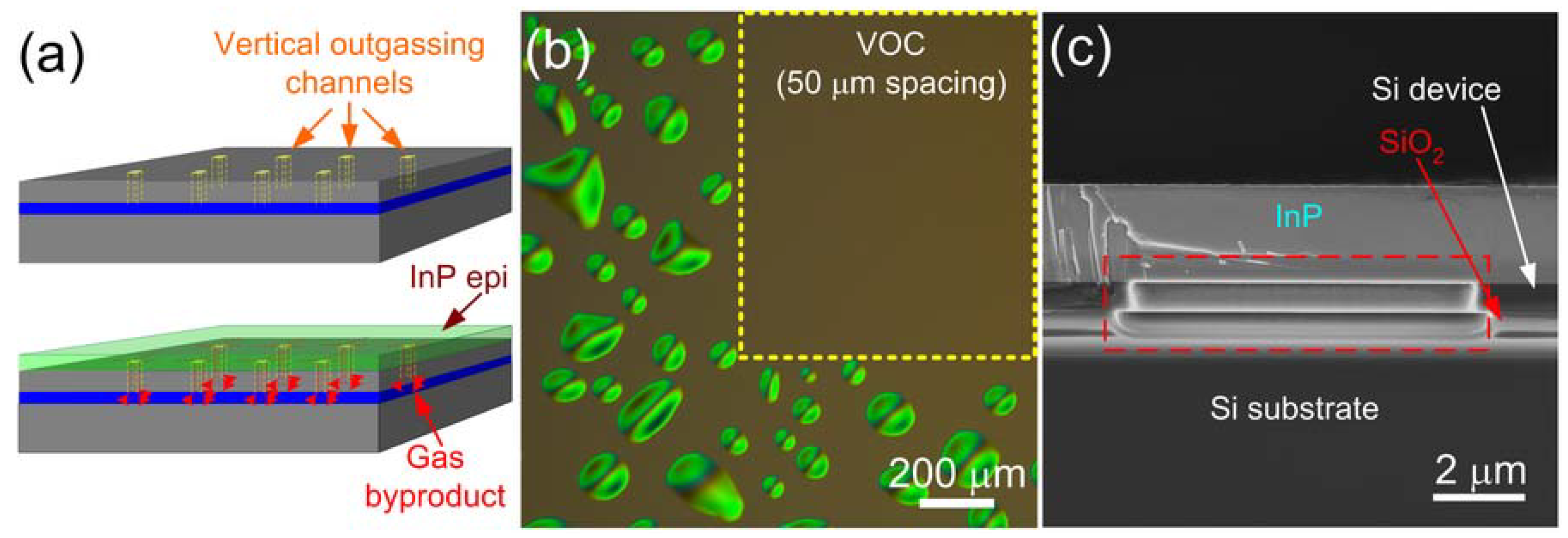

2.2. Solutions to outgassing in hydrophilic bonding

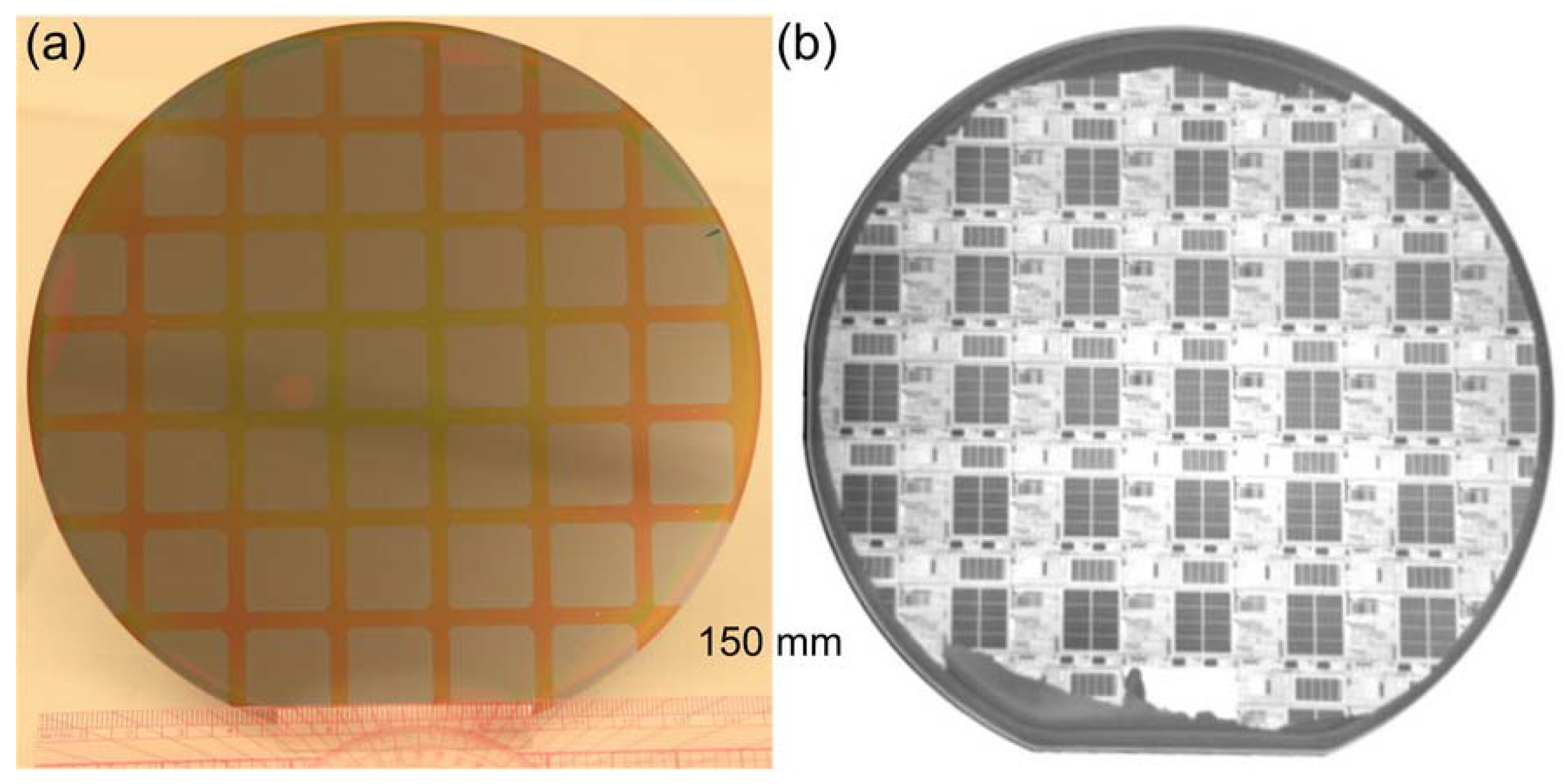

2.3. Wafer-scale integration

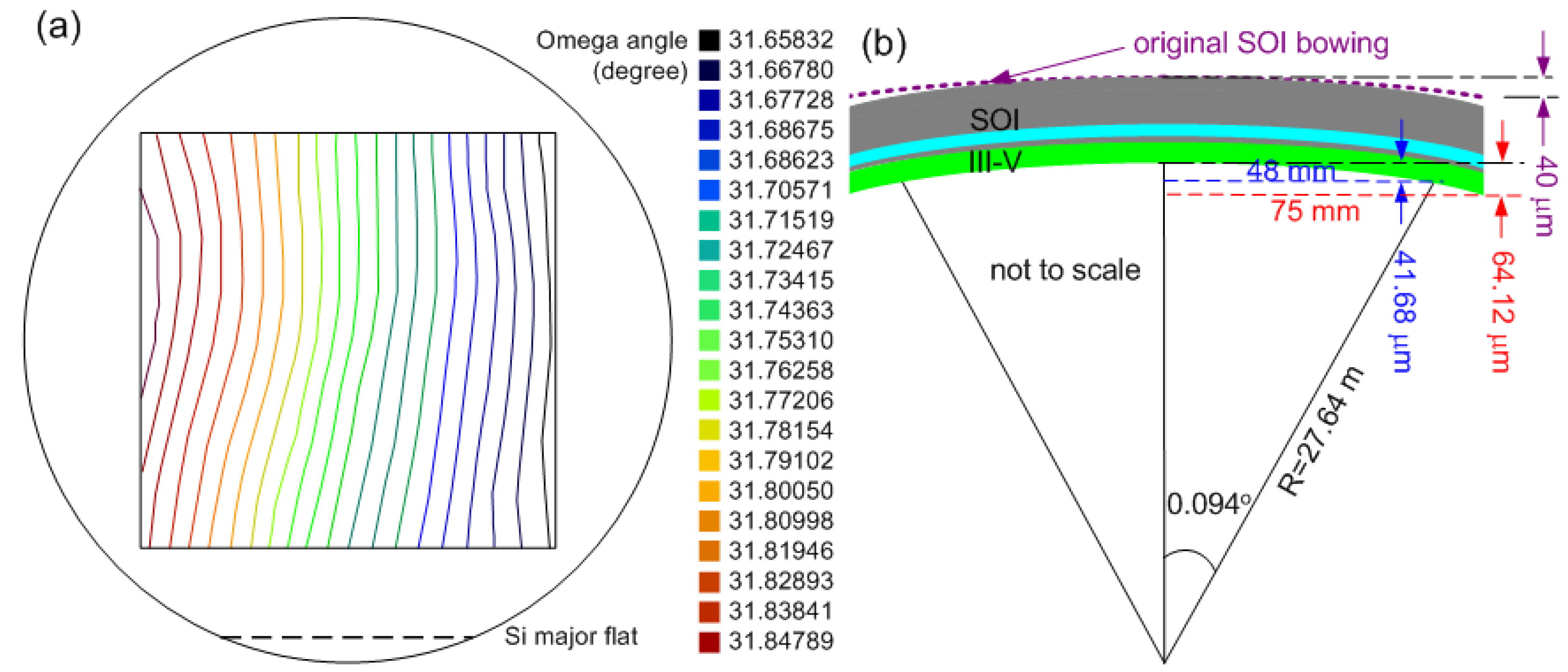

2.4. Epitaxial transfer quality characterization in wafer-scale integration

3. Adhesive Wafer Bonding Technology

| Electrical properties | |

| Dielectric constant | 2.5 at 10 GHz |

| Dissipation factor | 0.002 at 10 GHz |

| Breakdown voltage | 5.3 MV/cm |

| Optical properties | |

| Refractive index | 1.543 at 1.55 µm |

| Optical loss | <0.1 dB at 1.55 µm |

| Mechanical properties | |

| Tensile modulus | 2.9 GPa |

| Intrinsic stress | 28 MPa |

| Tensile strength | 89 MPa |

| Poisson ratio | 0.34 |

| Shrinkage upon cure | 0.05 |

| Thermal properties | |

| Glass transition temperature | >350 °C |

| Thermal conductivity | 0.29 W/mK |

| Thermal expansion coefficient | 42 ppm/K |

| Other properties | |

| Planarization | Very good |

| Moisture uptake | Very low |

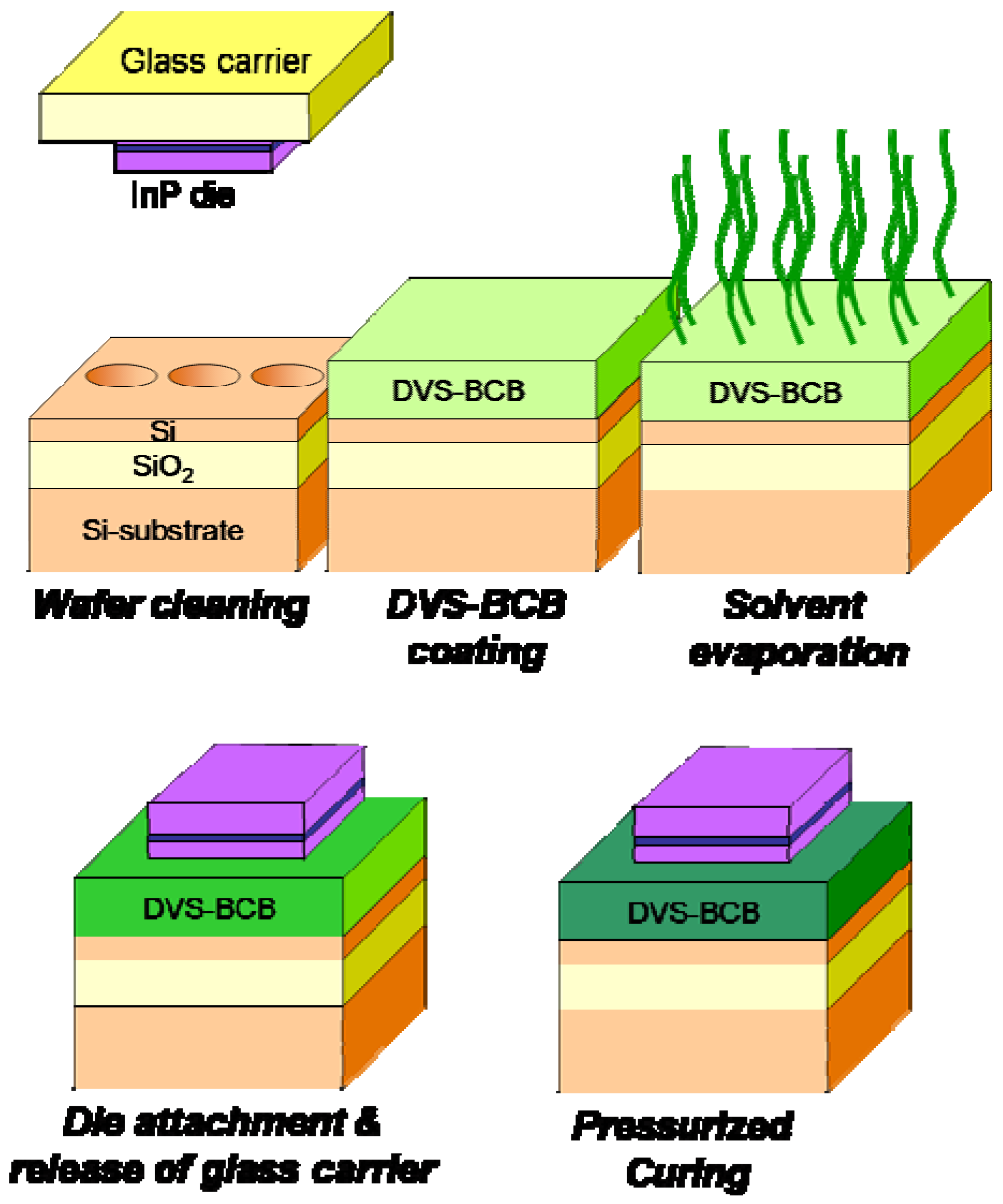

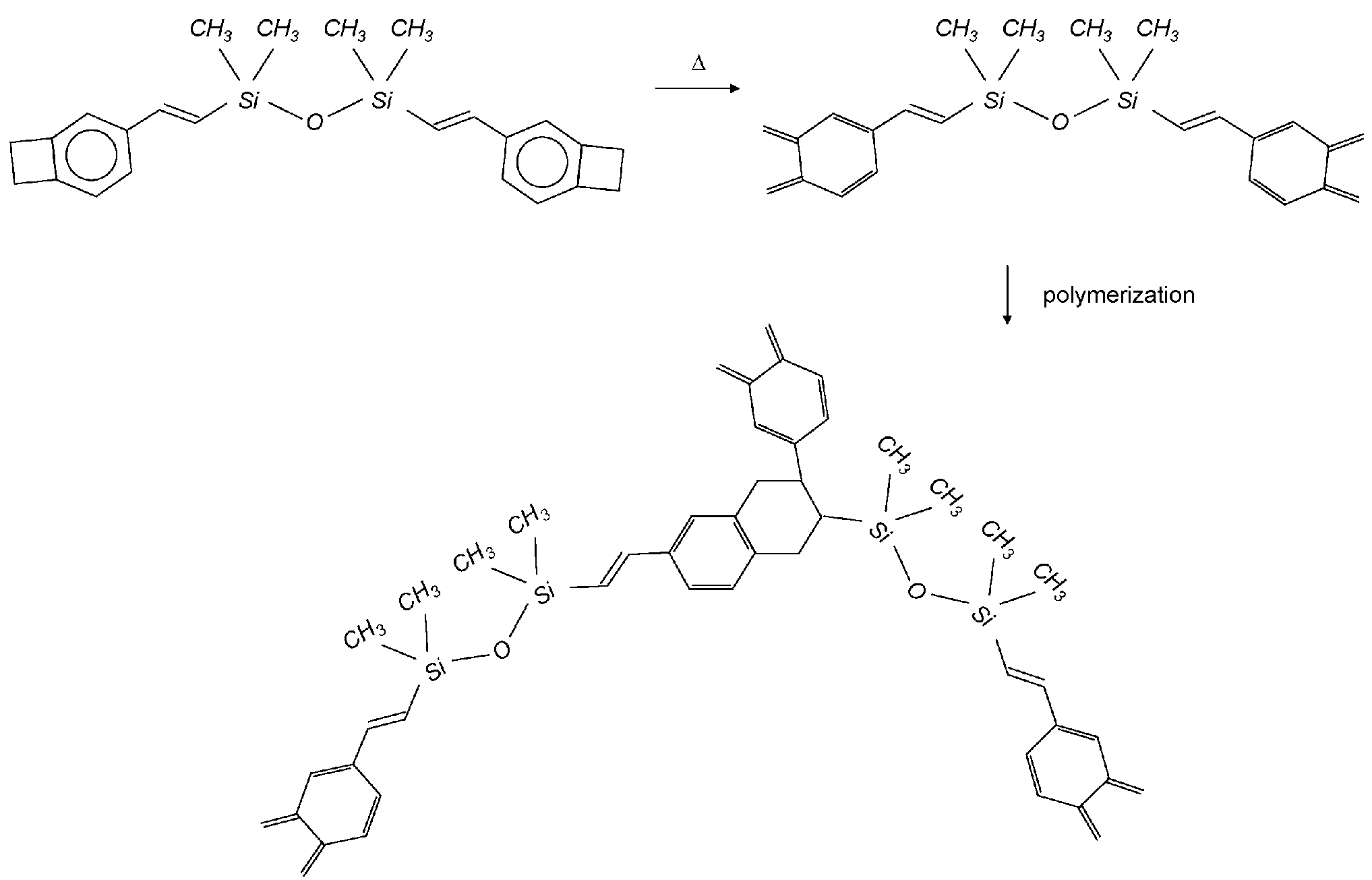

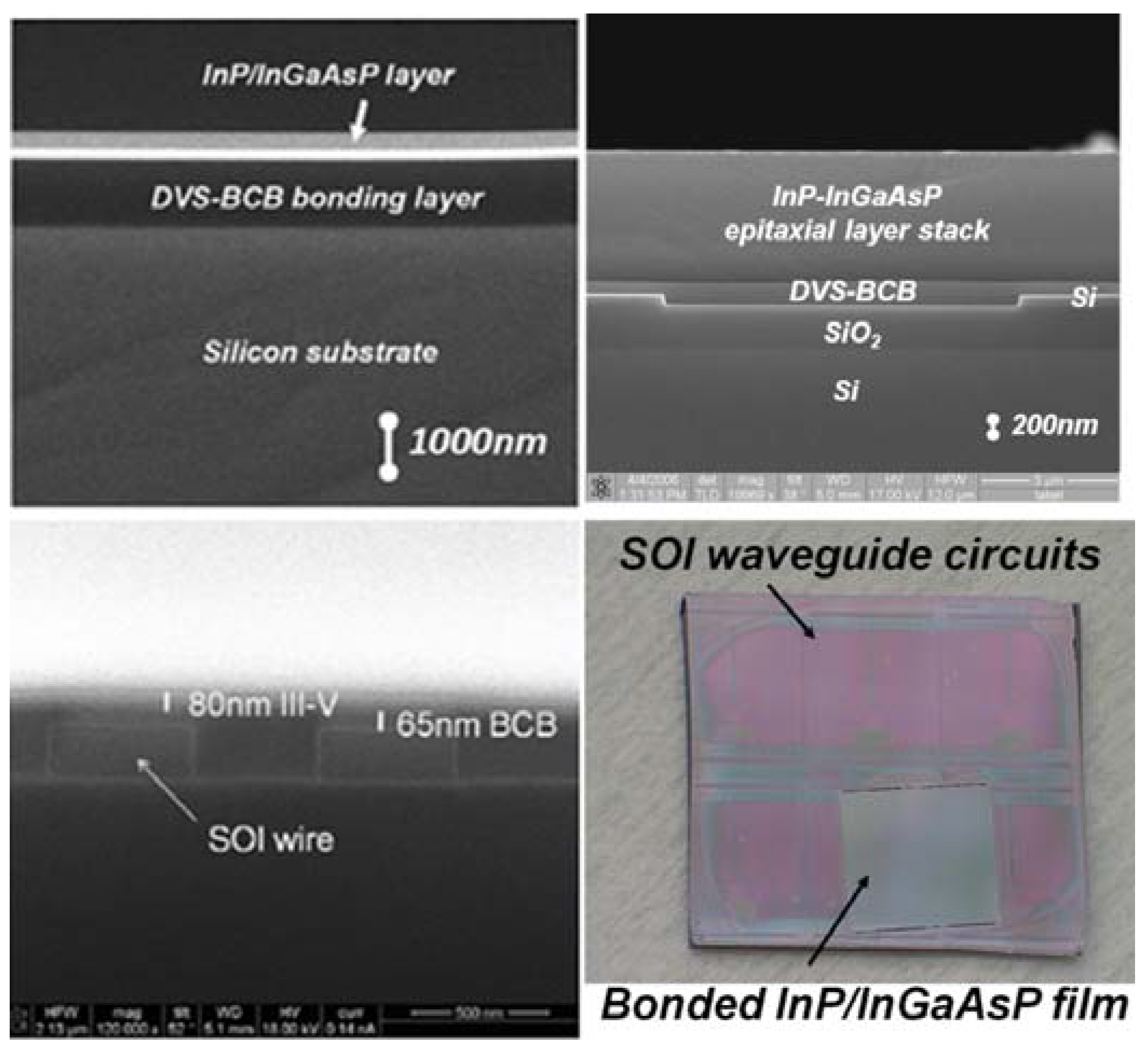

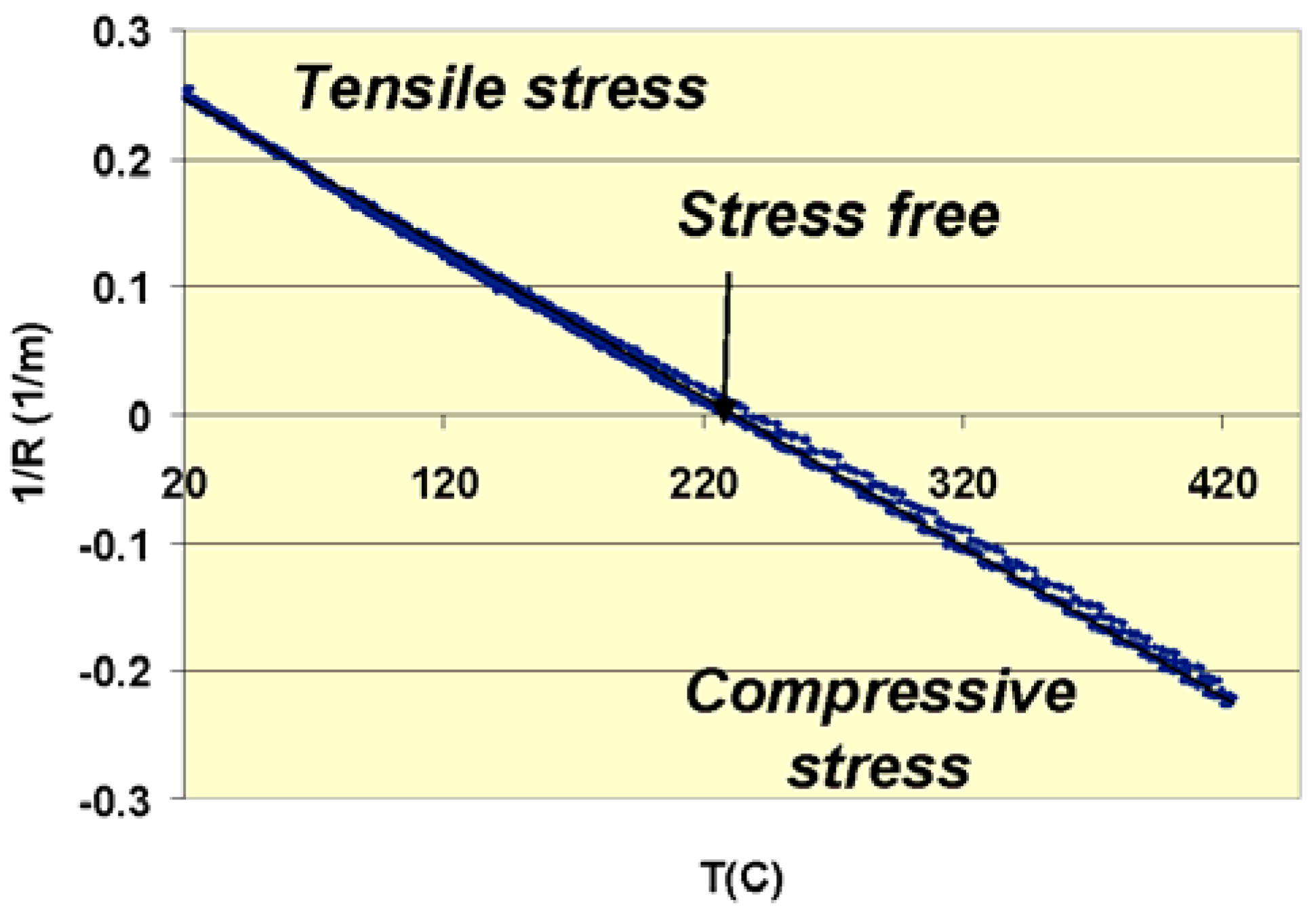

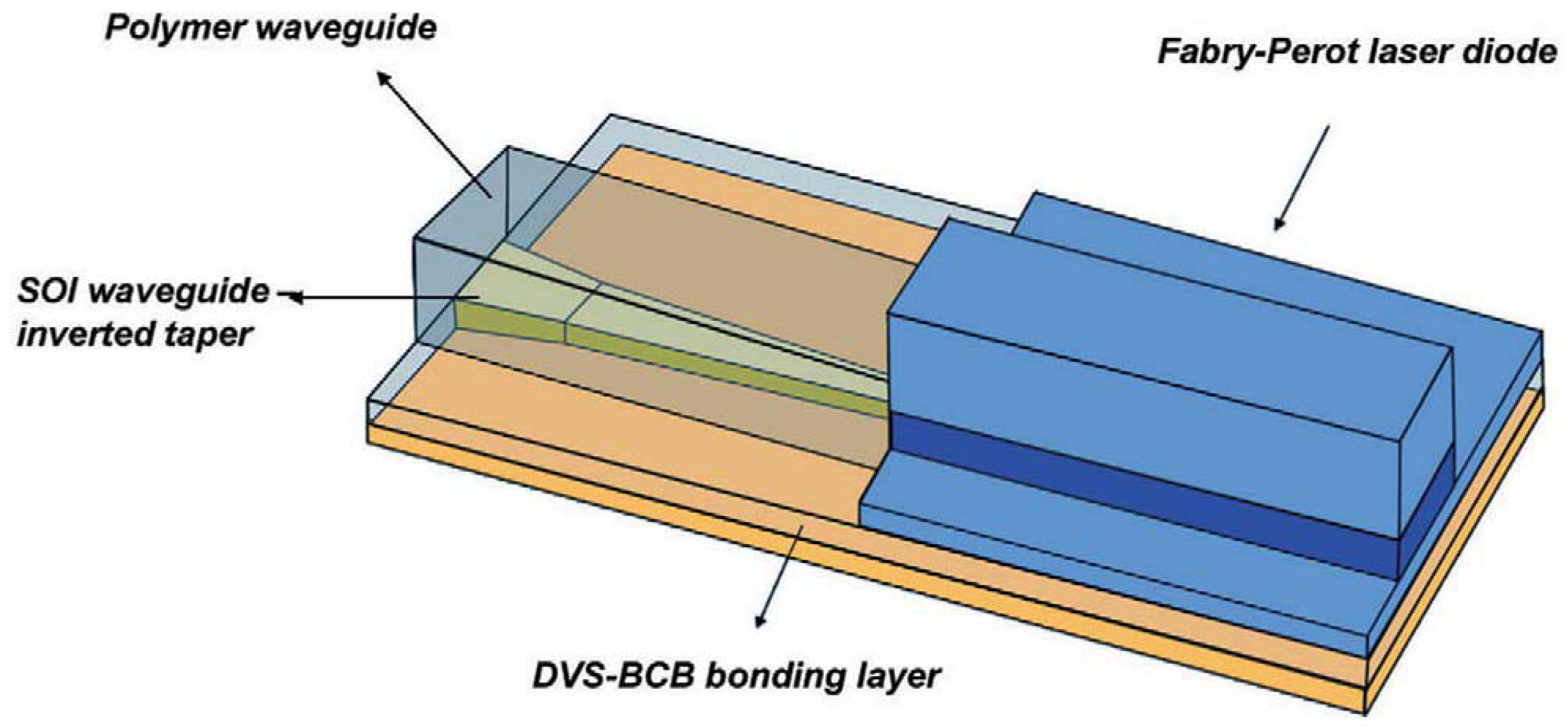

3.1. DVS-BCB adhesive die-to-wafer bonding

4. III-V-on-Si Photonic Device Platforms

4.1. Hybrid silicon platform

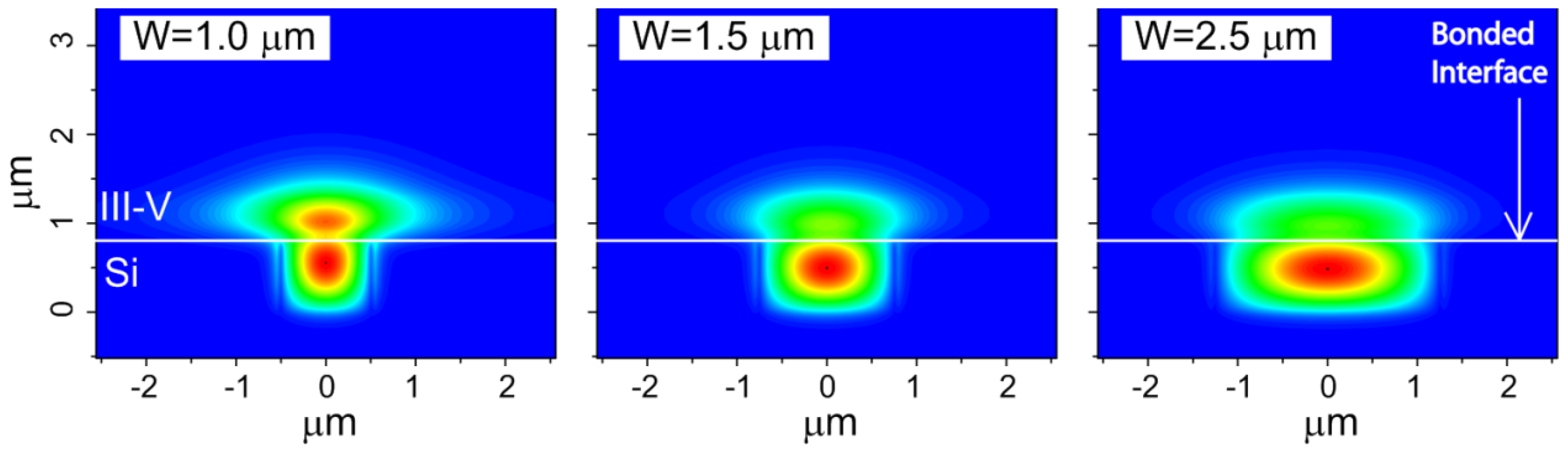

4.2. Heterogeneous III-V/SOI platform

4. Conclusions

| Bonding characteristic | Molecule bonding | Adhesive bonding |

|---|---|---|

| Bonding strength (<400 °C) | High | High |

| Process complexity | Medium | Low |

| Tolerance to surface defects, roughness and contamination | Low | High−medium |

| Bonding-induced strain | Low | Low |

| Integration proximity | High | High–medium |

| Intrinsic outgassing problem | High | Low |

| Uniformity | High | High–medium |

| Stability | High | High |

| Scalability | High | High |

Acknowledgements

References and Notes

- Gosele, U.; Tong, Q.Y. Semiconductor Wafer Bonding. Annu. Rev. Mater. Sci. 1998, 28, 215–241. [Google Scholar] [CrossRef]

- Miller, D.A.B.; Özaktas, H.M. Limit to the Bit-Rate Capacity of Electrical Interconnects from the Aspect Ratio of the System Architecture. J. Parallel Distrib. Comput. 1997, 41, 4252–4272. [Google Scholar]

- Miller, D.A.B. Device Requirements for Optical Interconnects to Silicon Chips. Proc. IEEE 2009, 97, 1166–1185. [Google Scholar] [CrossRef]

- Black, A.; Hawkins, A.R.; Margalit, N.M.; Babic, D.I.; Holmes, A.L., Jr.; Chang, Y.-L.; Abraham, P.; Bowers, J.E.; Hu, E.L. Wafer Fusion: Materials Issues and Device Results. IEEE J. Select. Top. Quantum Electron. 1997, 3, 943–951. [Google Scholar] [CrossRef]

- Fang, A.W.; Park, H.; Kuo, Y.-H.; Jones, R.; Cohen, O.; Liang, D.; Raday, O.; Sysak, M.N.; Paniccia, M.J.; Bowers, J.E. Hybrid Silicon Evanescent Devices. Mater. Today 2007, 10, 28–35. [Google Scholar] [CrossRef]

- Roelkens, G.; van Campenhout, J.; Brouckaert, J.; van Thourhout, D.; Baets, R.; Romeo, P.R.; Regreny, P.; Kazmierczak, A.; Seassal, C.; Letartre, X.; Hollinger, G.; Fedeli, J.M.; Di Cioccio, L.; Lagahe-Blanchard, C. III-V/Si Photonics by Die-to-Wafer Bonding. Mater. Today 2007, 10, 36–43. [Google Scholar] [CrossRef]

- Pasquariello, D.; Hedlund, C.; Hjort, K. Oxidation and Induced Damages in Oxygen Plasma in situ Wafer Bonding. J. Electrochem. Soc. 2000, 147, 2699–2702. [Google Scholar] [CrossRef]

- Pasquariello, D.; Lindeberg, M.; Hedlund, C.; Hjort, K. Surface Energy as A Function of Self-bias Voltage in Oxygen Plasma Wafer Bonding. Sens. Actuator. A 2000, 82, 239–244. [Google Scholar] [CrossRef]

- Soitec Home Page. http://www.soitec.com/ (accessed 12 January 2010).

- Singh, R.; Radu, I.; Scholz, R.; Himcinschi, C.; Gosele, U.; Christiansen, S.H. Low Temperature InP Layer Transfer onto Si by Helium Implantation and Direct Wafer Bonding. Semicond. Sci. Technol. 2006, 21, 1311–1314. [Google Scholar] [CrossRef]

- Tan, C.S.; Fan, A.; Chen, K.N.; Reif, R. Low-temperature Thermal Oxide to Plasma-enhanced Chemical Vapor Deposition Oxide Wafer Bonding for Thin-film Transfer Application. Appl. Phys. Lett. 2003, 82, 2649–2651. [Google Scholar] [CrossRef]

- Tong, Q.Y.; Gan, Q.; Fountain, G.; Hudson, G.; Enquist, P. Low-temperature Bonding of Silicon-Oxide-Covered Wafers Using Diluted HF Etching. Appl. Phys. Lett. 2004, 85, 2762–2764. [Google Scholar] [CrossRef]

- Tong, Q.Y.; Gan, Q.; Hudson, G.; Fountain, G.; Enquist, P. Low Temperature InP/Si Wafer Bonding. Appl. Phys. Lett. 2004, 84, 732–734. [Google Scholar] [CrossRef]

- Liang, D.; Chapman, D.; Li, Y.; Oakley, D.; Napoleone, T.; Juodawlkis, P.; Brubaker, C.; Mann, C.; Bar, H.; Raday, O.; Bowers, J.E. Uniformity Study of Wafer-scale InP-to-Silicon Hybrid Integration. J. Electrochem. Soc. 2010. submitted. [Google Scholar]

- Liang, D.; Bowers, J.E.; Oakley, D.C.; Napoleone, T.; Chapman, D.C.; Chen, C.-L.; Juodawlkis, P. W.; Raday, O. High-Quality 150 mm InP-to-Silicon Epitaxial Transfer for Silicon Photonic Integrated Circuits. Electrochem. Solid State Lett. 2009, 12, H101–H104. [Google Scholar] [CrossRef]

- Pasquariello, D.; Hjort, K. Plasma-assisted InP-to-Si Low Temperature Wafer Bonding. IEEE J. Select. Top. Quantum Electron. 2002, 8, 118–131. [Google Scholar] [CrossRef]

- Warner, K.; Oakley, D.; Donnelly, J.; Keast, C.; Shaver, D. Layer Transfer of FDSOI CMOS to 150 mm InP Substrate for Mixed-material Integration. In IEEE Conference on Indium Phosphide and Related Materials (IPRM), Princeton, NJ, USA, May 2006; pp. 226–228.

- Liang, D.; Fang, A.W.; Park, H.; Reynolds, T.E.; Warner, K.; Oakley, D.C.; Bowers, J.E. Low-temperature, Strong SiO2-SiO2 Covalent Wafer Bonding for III-V Compound Semiconductors-to-Silicon Photonic Integrated Circuits. J. Electron. Mater. 2008, 37, 1552–1559. [Google Scholar] [CrossRef]

- Tong, Q.Y.; Gösele, U. Semiconductor Wafer Bonding: Science and Technology; John Wiley & Sons: New York, NY, USA, 1998. [Google Scholar]

- Weldon, M.K.; Chabal, Y.J.; Hamann, D.R.; Christman, S.B.; Chaban, E.E.; Feldman, L.C. Physics and Chemistry of Silicon Wafer Bonding Investigated by Infrared Absorption Spectroscopy. J. Vac. Sci. Technol. B 1996, 14, 3095–3106. [Google Scholar] [CrossRef]

- Mack, S.; Baumann, H.; Gosele, U. Gas Development at The Interface of Directly Bonded Silicon Wafers: Investigation on Silicon-based Pressure Sensors. Sens. Actuator. A 1996, 56, 273–277. [Google Scholar] [CrossRef]

- Mack, S.; Baumann, H.; Gosele, U.; Werner, H.; Schlogl, R. Analysis of Bonding-Related Gas Enclosure in Micromachined Cavities Sealed by Silicon Wafer Bonding. J. Electrochem. Soc. 1997, 144, 1106–1111. [Google Scholar] [CrossRef]

- Irene, E.A.; Tierney, E.; Angilello, J. A Viscous Flow Model to Explain the Appearance of High Density Thermal SiO2 at Low Oxidation Temperatures. J. Electrochem. Soc. 1982, 129, 2594–2597. [Google Scholar] [CrossRef]

- Zhang, X.; Raskin, J.P. Low-temperature Wafer Bonding: A Study of Void Formation and Influence on Bonding Strength. IEEE J. Microelectromechanic. Syst. 2005, 14, 368–382. [Google Scholar] [CrossRef]

- Itsumi, M. SiO2 in Si Microdevices; Springer: Berlin, Germany, 2002. [Google Scholar]

- Liang, D.; Bowers, J.E. Highly Efficient Vertical Outgassing Channels for Low-Temperature InP-to-Silicon Direct Wafer Bonding on the Silicon-on-insulator (SOI) Substrate. J. Vac. Sci. Technol. B 2008, 26, 1560–1568. [Google Scholar] [CrossRef]

- Maszara, W.P.; Goetz, G.; Caviglia, A.; McKitterick, J.B. Bonding of Silicon Wafers for Silicon-on-insulator. J. Appl. Phys. 1988, 64, 4943–4950. [Google Scholar] [CrossRef]

- Maszara, W.P. Silicon-on-insulator by Wafer Bonding: A Review. J. Electrochem. Soc. 1991, 138, 341–347. [Google Scholar] [CrossRef]

- Niklaus, F.; Stemme, G.; Lu, J.Q.; Gutmann, R.J. Adhesive Wafer Bonding. J. Appl. Phys. 2006, 99, 031101. [Google Scholar] [CrossRef]

- Niklaus, F.; Andersson, H.; Enoksson, P.; Stemme, G. Low Temperature Full Wafer Adhesive Bonding of Structured Wafers. Sens. Actuator. A 2001, 92, 235–241. [Google Scholar] [CrossRef]

- Rooman, C.; Kuijk, M.; De Jonge, S.; Heremans, P. High Efficiency AlGaInP Thin-film LEDs Using Surface-texturing and Wafer Bonding with Conductive Epoxy. IEEE Photon. Technol. Lett. 2005, 17, 2649–2651. [Google Scholar] [CrossRef]

- Lin, H.; Chang, K.; Pickrell, G.; Hsieh, K.; Cheng, K. Low Temperature Wafer Bonding by Spin-on-glass. J. Vac. Sci. Technol. B 2002, 20, 752–754. [Google Scholar] [CrossRef]

- Dragoi, V.; Glinsner, T.; Mittendorfer, G.; Wieder, B.; Lindner, P. Adhesive Wafer Bonding for MEMS Applications. In Proceedings of the SPIE International Symposium: Microtechnologies for the New Millennium, Maspalomas, Gran Canarias, Spain, May 2003; pp. 160–167.

- Blanco, F.; Agirregabiria, M.; Garcia, J.; Berganzo, J.; Tijero, M.; Arroyo, M.T.; Ruano, J.M.; Aramburu, I.; Mayora, K. Novel Three-dimensional Embedded SU-8 Microchannels Fabricated Using A Low Temperature Full Wafer Adhesive Bonding. J. Micromech. Microeng. 2004, 14, 1047–1056. [Google Scholar] [CrossRef]

- Garrou, P.; Heistand, R.; Dibbs, M.; Mainal, T.; Mohler, C.; Stokich, T.; Townsend, P.; Adema, G.; Berry, M.; Turlik, I. Rapid Thermal Curing of BCB Dielectric. IEEE Trans. Compon. Hybr. Manuf. Technol. 1993, 16, 46–52. [Google Scholar] [CrossRef]

- Kwon, Y.; Seok, J.; Lu, J.Q.; Cale, T.S.; Gutmann, R.J. Thermal Cycling Effects on Critical Adhesion Energy And Residual Stress in Benzocyclobutene Bonded Wafers. J. Electrochem. Soc. 2005, 152, G286–G294. [Google Scholar] [CrossRef]

- Kwon, Y.; Seok, J.; Lu, J.Q.; Cale, T.S.; Gutmann, R.J. Critical Adhesion Energy of Benzocyclobutene-bonded Wafers. J. Electrochem. Soc. 2006, 153, G347–G352. [Google Scholar] [CrossRef]

- Niklaus, F.; Kumar, R.; McMahon, J.J.; Yu, J.; Lu, J.Q.; Cale, T.S.; Gutmann, R.J. Adhesive Wafer Bonding Using Partially Cured Benzocyclobutene for Three-dimensional Integration. J. Electrochem. Soc. 2006, 153, G291–G295. [Google Scholar] [CrossRef]

- Fang, A.W.; Park, H.; Cohen, O.; Jones, R.; Paniccia, M.J.; Bowers, J.E. Electrically Pumped Hybrid AlGaInAs-silicon Evanescent Laser. Opt. Expr. 2006, 14, 9203–9210. [Google Scholar] [CrossRef]

- Black, K.A.; Abraham, P.; Karim, A.; Bowers, J.E.; Hu, E.L. Improved Luminescence From InGaAsP/InP MQW Active Regions Using A Wafer Fused Superlattice Barrier. In Indium Phosphide and Related Materials (IPRM), Davos, Switzerland, May 1999; pp. 357–360.

- Fang, A.W.; Jones, R.; Park, H.; Cohen, O.; Raday, O.; Paniccia, M.J.; Bowers, J.E. Integrated AlGaInAs-silicon Evanescent Race Track Laser and Photodetector. Opt. Expr. 2007, 15, 2315–2322. [Google Scholar] [CrossRef]

- Park, H.; Fang, A.W.; Liang, D.; Kuo, Y.-H.; Chang, H.-H.; Koch, B.R.; Chen, H.-W.; Sysak, M.N.; Jones, R.; Bowers, J.E. Photonic Integration on The Hybrid Silicon Evanescent Device Platform. Adv. Opt. Technol. 2008, 682978. [Google Scholar]

- Roelkens, G.; Brouckaert, J.; van Thourhout, D.; Baets, R.; Notzel, R.; Smit, M. Adhesive Bonding of InP/InGaAsP Dies to Processed Silicon-On-Insulator Wafers Using DVS-bis-Benzocyclobutene. J. Electrochem. Soc. 2006, 153, G1015–G1019. [Google Scholar] [CrossRef]

- Roelkens, G.; van Thourhout, D.; Baets, R.; Notzel, R.; Smit, M. Laser Emission and Photodetection in An InP/InGaAsP Layer Integrated on and Coupled to a Silicon-on-Insulator Waveguide Circuit. Opt. Expr. 2006, 14, 8154–8159. [Google Scholar] [CrossRef]

- Koch, B.R.; Fang, A.W.; Cohen, O.; Bowers, J.E. Mode-locked Silicon Evanescent Lasers. Opt. Expr. 2007, 15, 11225–11233. [Google Scholar] [CrossRef]

- van Campenhout, J.; Rojo Romeo, P.; Regreny, P.; Seassal, C.; van Thourhout, D.; Verstuyft, S.; Di Cioccio, L.; Fedeli, J.M.; Lagahe, C.; Baets, R. Electrically Pumped InP-based Microdisk Lasers Integrated with A Nanophotonic Silicon-on-insulator Waveguide Circuit. Opt. Expr. 2007, 15, 6744–6749. [Google Scholar] [CrossRef]

- Fang, A.W.; Lively, E.; Kuo, Y.-H.; Liang, D.; Bowers, J.E. A Distributed Feedback Silicon Evanescent Laser. Opt. Expr. 2008, 16, 4413–4419. [Google Scholar] [CrossRef]

- Fang, A.W.; Koch, B.R.; Jones, R.; Lively, E.; Liang, D.; Kuo, Y.-H; Bowers, J.E. A Distributed Bragg Reflector Silicon Evanescent Laser. IEEE Photon. Tech. Lett. 2008, 20, 1667–1669. [Google Scholar] [CrossRef]

- Liang, D.; Fiorentino, M.; Okumura, T.; Chang, H.-H.; Spencer, D.T.; Kuo, Y.-H.; Fang, A.W.; Dai, D.; Beausoleil, R.G.; Bowers, J.E. Electrically-pumped Compact Hybrid Silicon Microring Lasers for Optical Interconnects. Opt. Expr. 2009, 17, 20355–20364. [Google Scholar] [CrossRef]

- Park, H.; Fang, A.W.; Cohen, O.; Jones, R.; Paniccia, M.J.; Bowers, J.E. A Hybrid AlGaInAs-Silicon Evanescent Amplifier. IEEE Photon. Tech. Lett. 2007, 19, 230–232. [Google Scholar] [CrossRef]

- Park, H.; Fang, A.W.; Jones, R.; Cohen, O.; Raday, O.; Sysak, M.N.; Paniccia, M.J.; Bowers, J.E. A Hybrid AlGaInAs-silicon Evanescent Waveguide Photodetector. Opt. Expr. 2007, 15, 6044–6052. [Google Scholar] [CrossRef]

- Brouckaert, J.; Roelkens, G.; Selvaraja, S.K.; Bogaerts, W.; Dumon, P.; Verstuyft, S.; van Thourhout, D.; Baets, R. Silicon-on-insulator CWDM Power Monitor/Receiver with Integrated Thin-Film InGaAs Photodetectors. IEEE Photon. Tech. Lett. 2009, 21, 1423–1425. [Google Scholar] [CrossRef]

- Kuo, Y.-H.; Chen, H.-W.; Bowers, J.E. High Speed Hybrid Silicon Evanescent Electroabsorption Modulator. Opt. Expr. 2008, 16, 9936–9941. [Google Scholar] [CrossRef]

- Chen, H.-W.; Kuo, Y.-H.; Bowers, J.E. A Hybrid Silicon AlGaInAs Phase Modulator. IEEE Photon. Tech. Lett. 2008, 20, 1920–1922. [Google Scholar] [CrossRef]

- Liu, L.; van Campenhout, J.; Roelkens, G.; Soref, R.A.; van Thourhout, D.; Rojo-Romeo, P.; Regreny, P.; Seassal, C.; Fedeli, J.-M.; Baets, R. Carrier-injection-based Electro-optic Modulator on Silicon-on-insulator with A Heterogeneously Integrated III-V Microdisk Cavity. Opt. Lett. 2008, 33, 2518–2520. [Google Scholar] [CrossRef] [PubMed]

- Chen, H.-W.; Kuo, Y.-H.; Bowers, J.E. High Speed Hybrid Silicon Evanescent Mach-Zehnder Modulator and Switch. Opt. Expr. 2008, 16, 20571–20576. [Google Scholar] [CrossRef]

- Sysak, M.N.; Anthes, J.O.; Bowers, J.E.; Raday, O.; Jones, R. Integration of Hybrid Silicon Lasers and Electroabsorption Modulators. Opt. Expr. 2008, 16, 12478–12486. [Google Scholar] [CrossRef]

- Maruyama, T.; Okumura, T.; Sakamoto, S.; Miura, K.; Nishimoto, Y.; Arai, S. GaInAsP/InP Membrane BH-DFB Lasers Directly Bonded on SOI substrate. Opt. Expr. 2006, 14, 8184–8188. [Google Scholar] [CrossRef]

- Yariv, A.; Sun, X. Supermode Si/III-V Hybrid Lasers, Optical Amplifiers and Modulators: A Proposal and Analysis. Opt. Expr. 2007, 15, 9147–9151. [Google Scholar] [CrossRef]

- Yuya, S.; Tetsuya, M.; Hideki, Y.; Hsieh, I.W.; Osgood, R.M., Jr. Magneto-optical Isolator with Silicon Waveguides Fabricated by Direct Bonding. Appl. Phys. Lett. 2008, 92, 071117. [Google Scholar] [CrossRef]

- Chen, L.; Dong, P.; Lipson, M. High Performance Germanium Photodetectors Integrated on Submicron Silicon Waveguides by Low Temperature Wafer Bonding. Opt. Expr. 2008, 16, 11513–11518. [Google Scholar] [CrossRef]

© 2010 by the authors; licensee Molecular Diversity Preservation International, Basel, Switzerland. This article is an open-access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Liang, D.; Roelkens, G.; Baets, R.; Bowers, J.E. Hybrid Integrated Platforms for Silicon Photonics. Materials 2010, 3, 1782-1802. https://doi.org/10.3390/ma3031782

Liang D, Roelkens G, Baets R, Bowers JE. Hybrid Integrated Platforms for Silicon Photonics. Materials. 2010; 3(3):1782-1802. https://doi.org/10.3390/ma3031782

Chicago/Turabian StyleLiang, Di, Gunther Roelkens, Roel Baets, and John E. Bowers. 2010. "Hybrid Integrated Platforms for Silicon Photonics" Materials 3, no. 3: 1782-1802. https://doi.org/10.3390/ma3031782