The Design of a Single-Bit CMOS Image Sensor for Iris Recognition Applications

Abstract

:1. Introduction

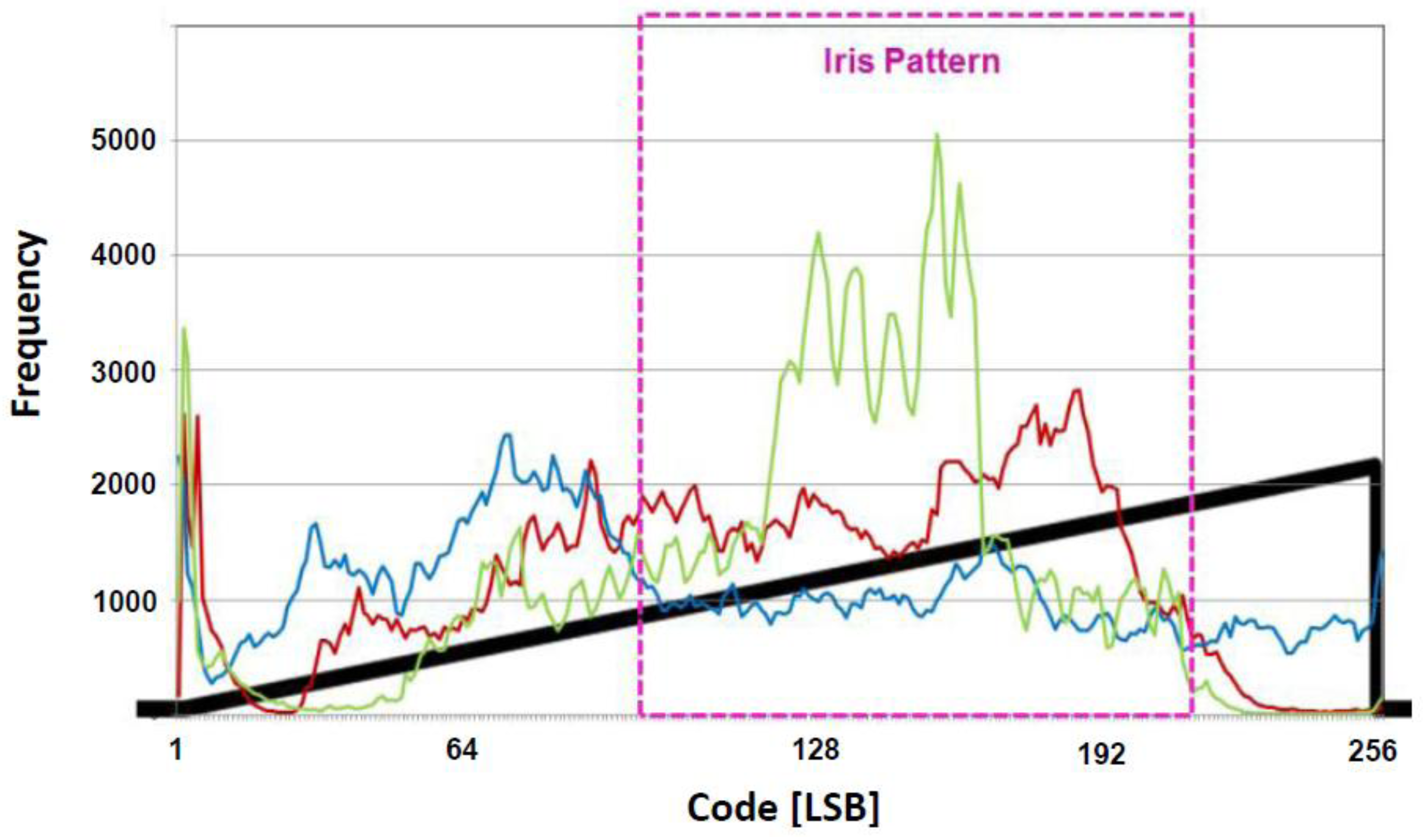

2. Design of the Proposed CIS for Iris Segmentation Using Edge Detection Block

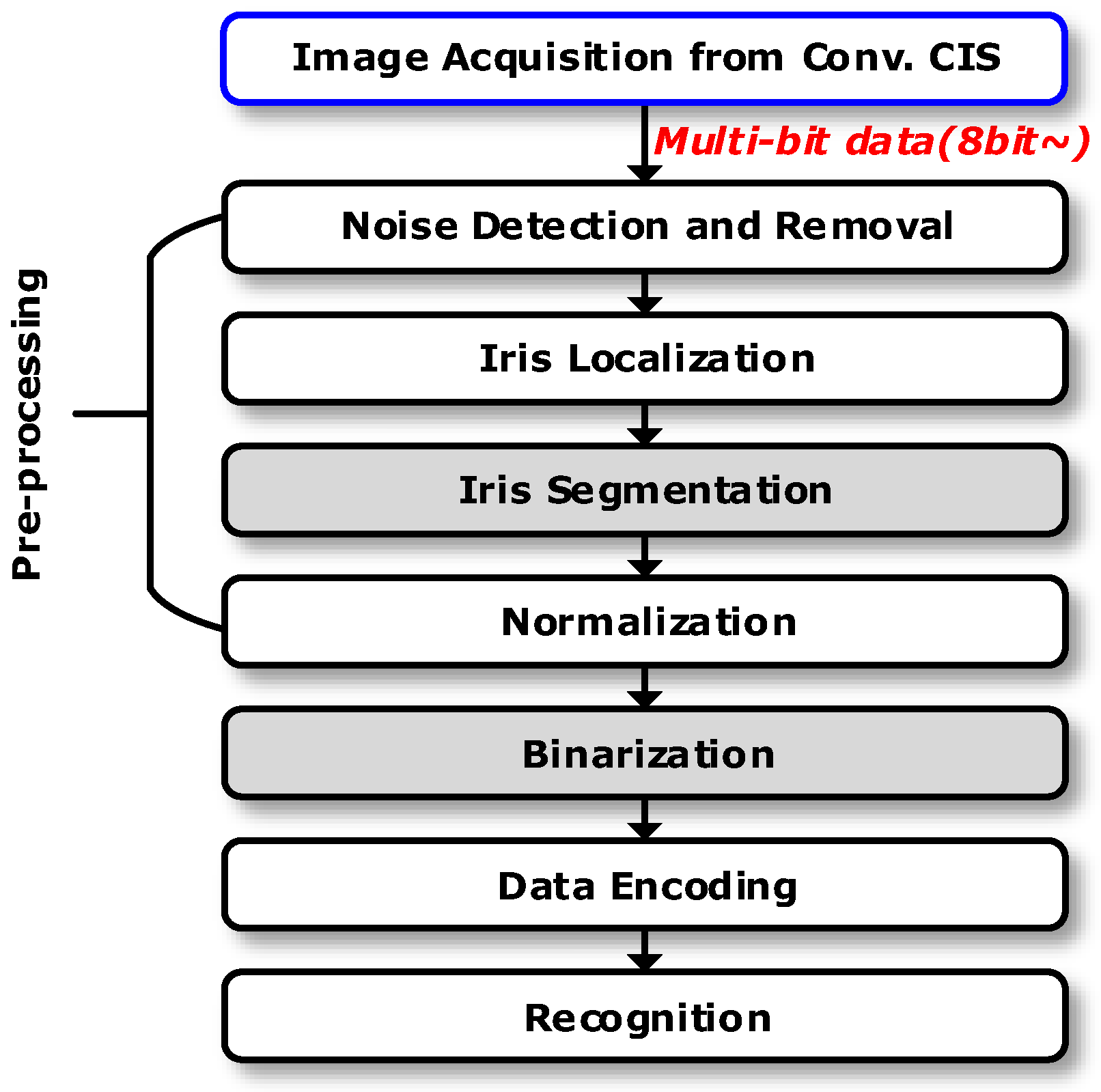

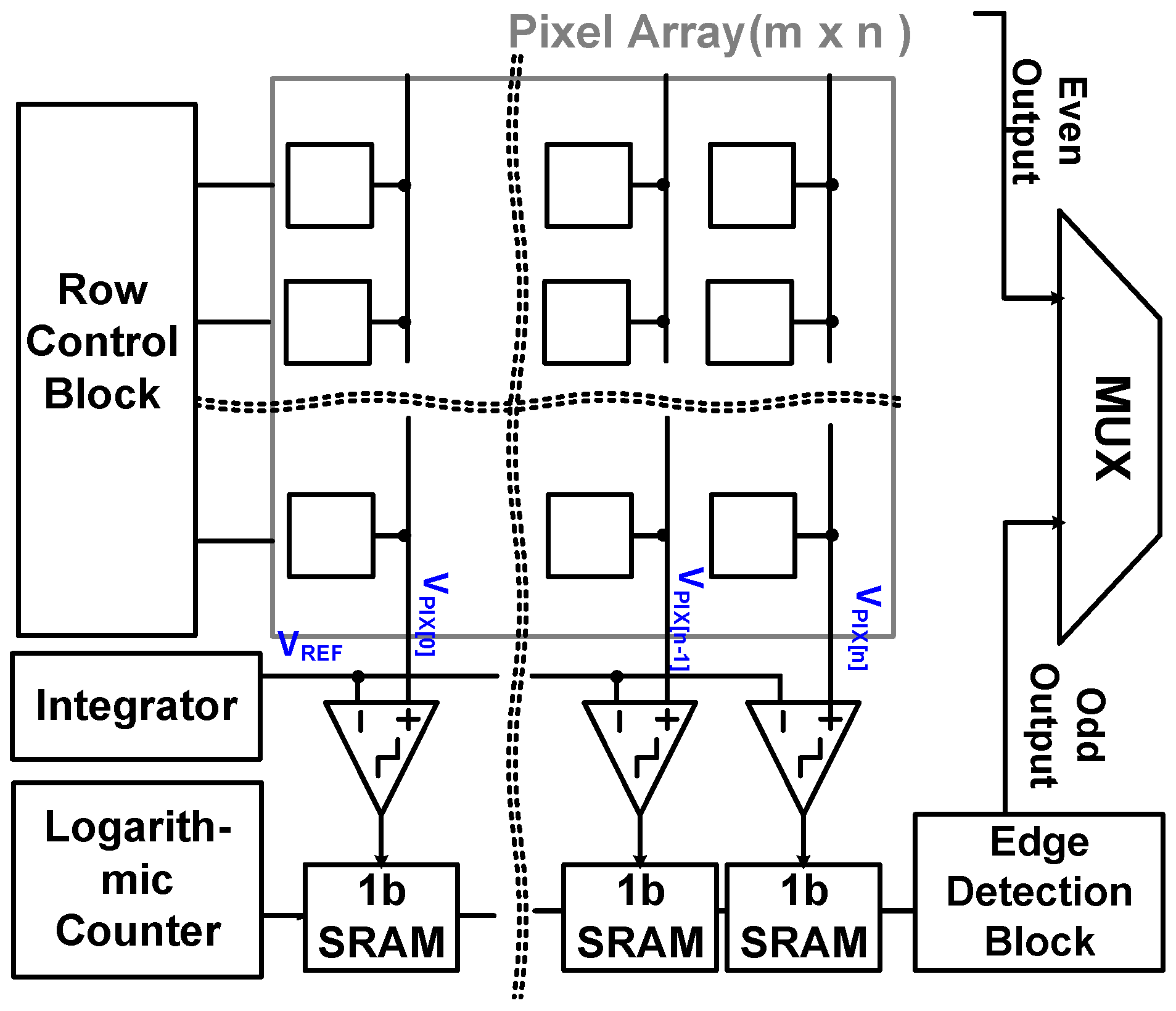

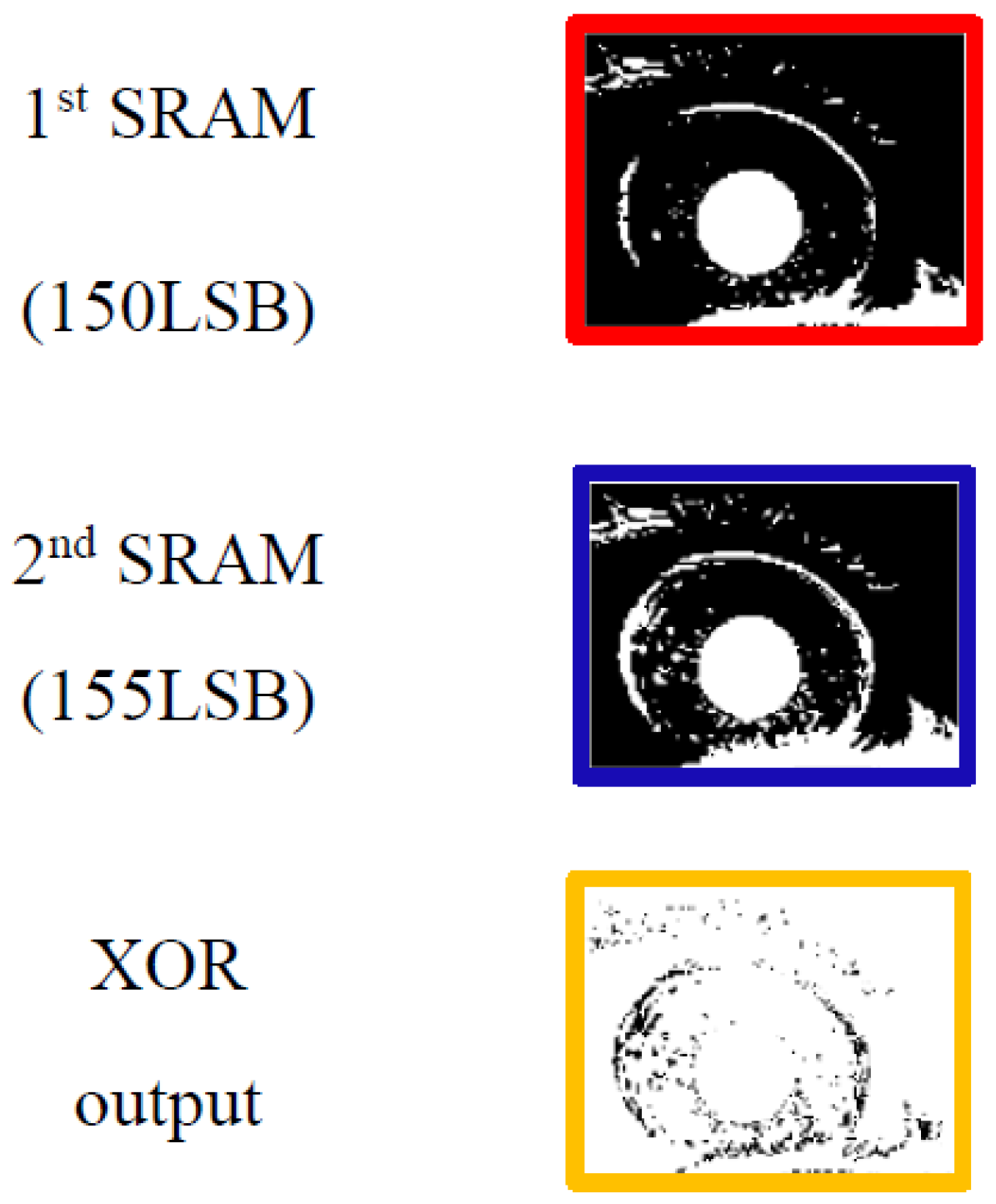

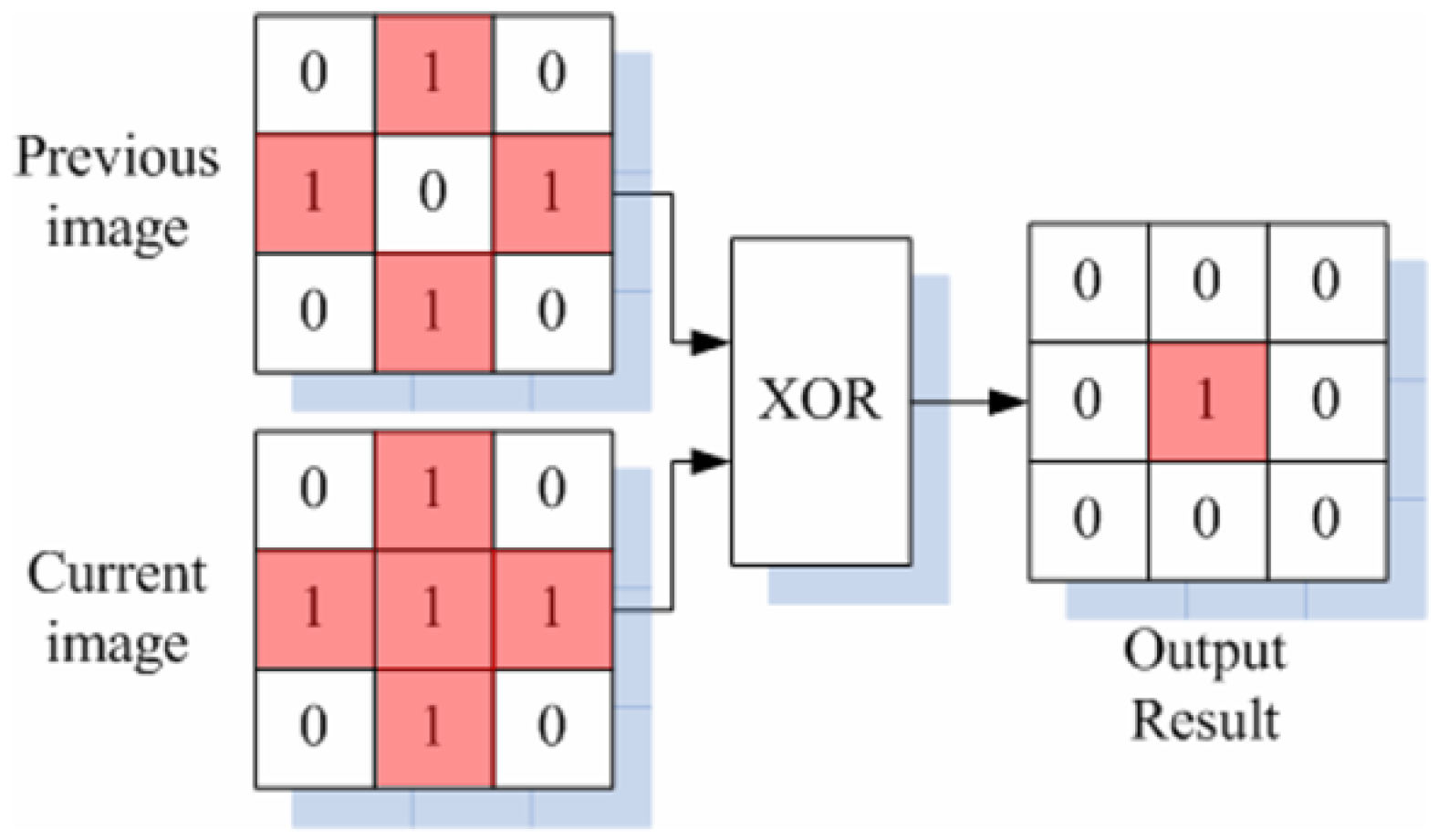

2.1. The Proposed Single-Bit CIS with Iris Recognition Algorithm

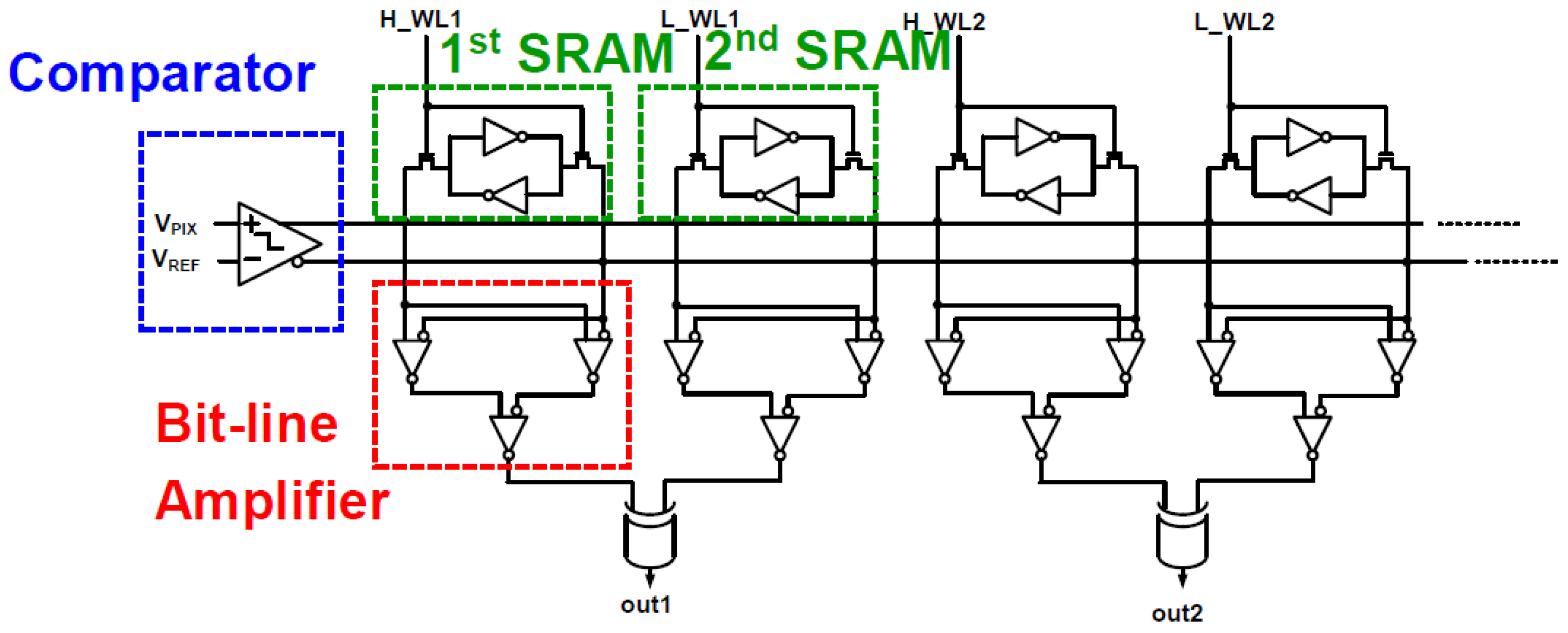

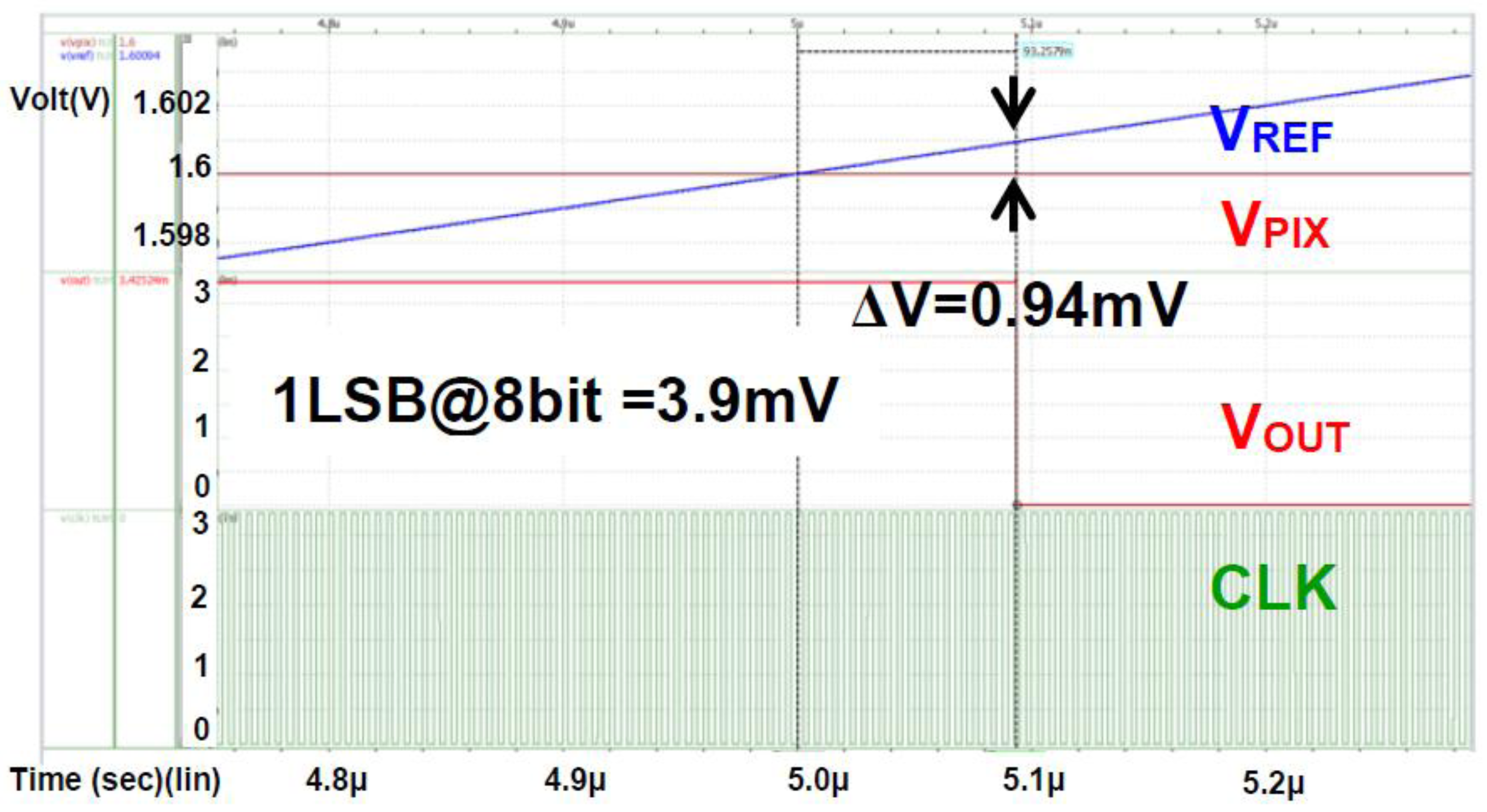

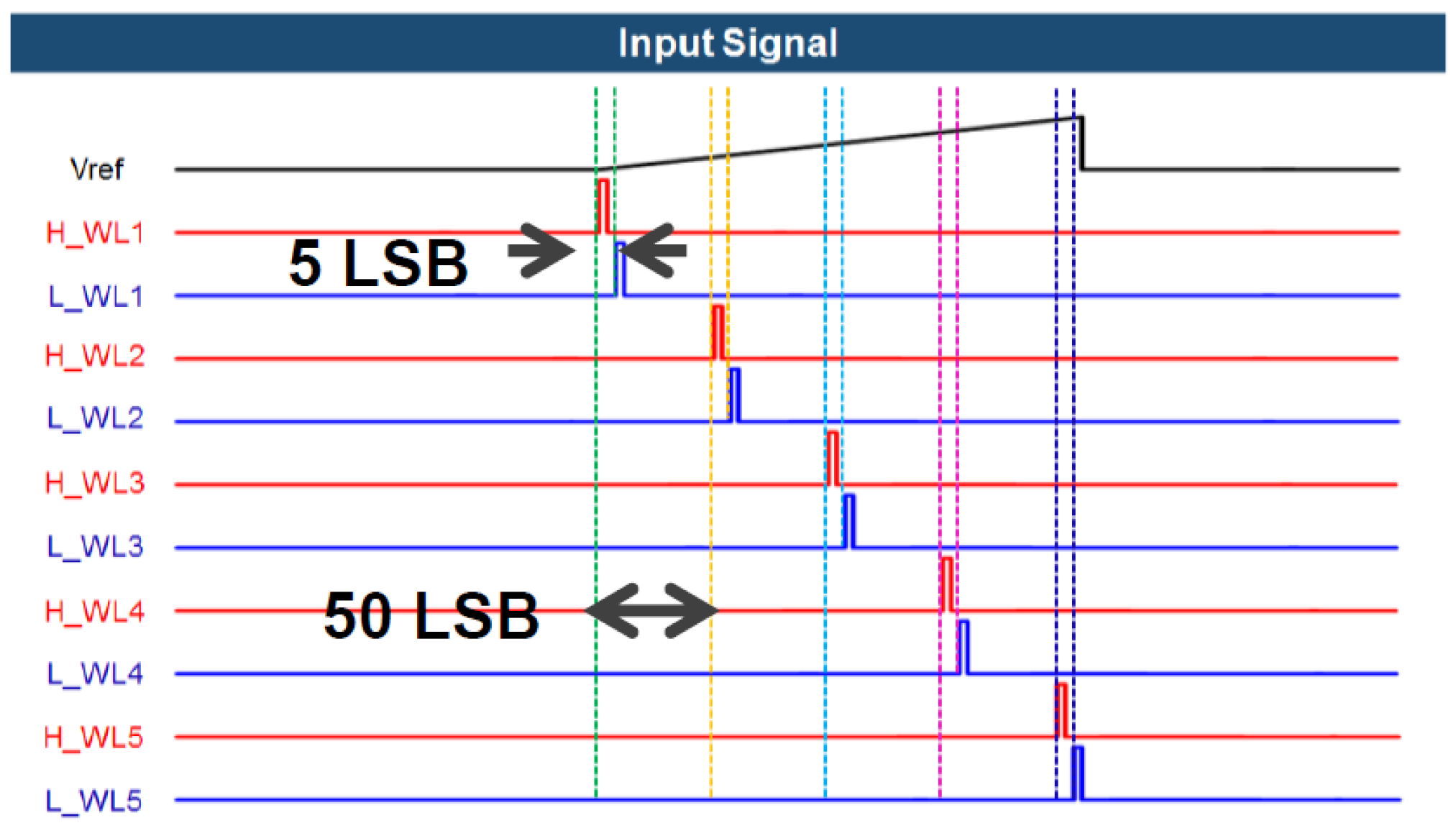

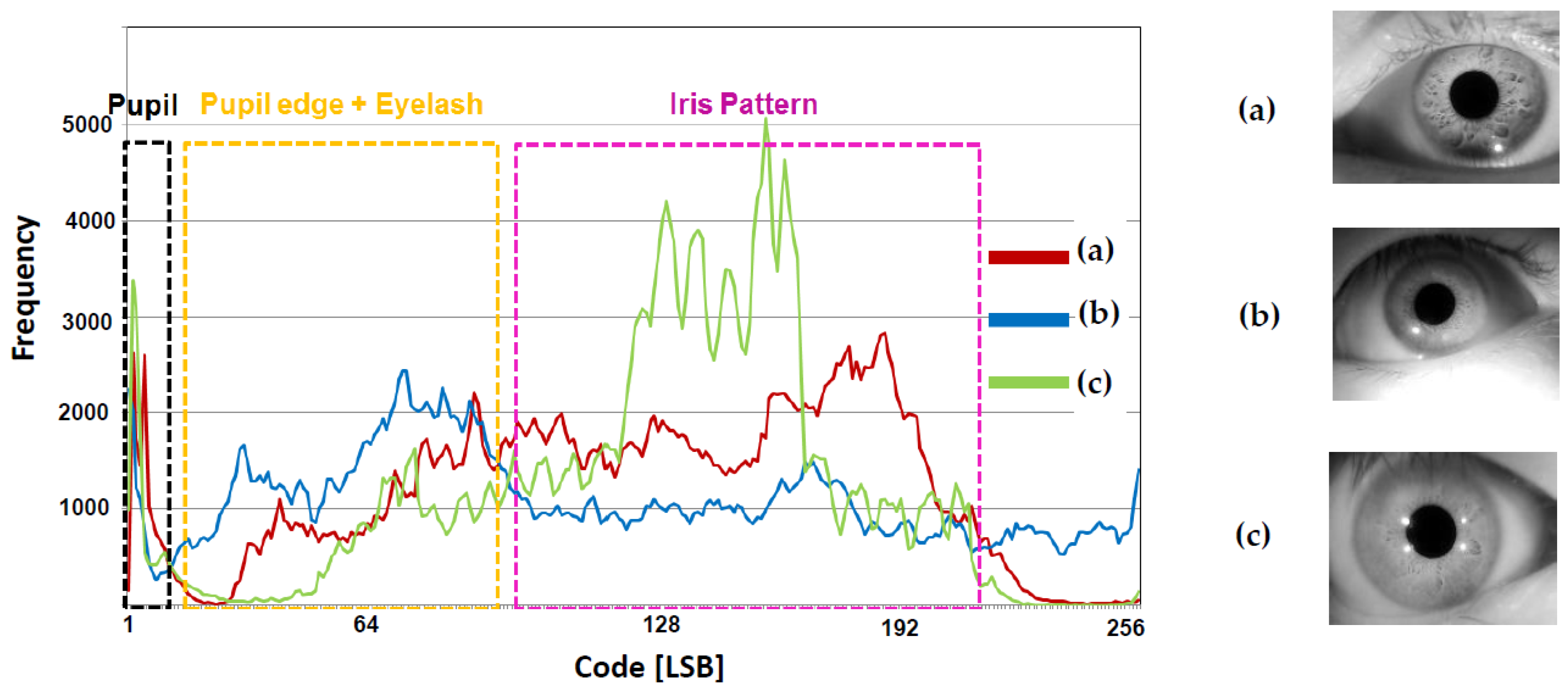

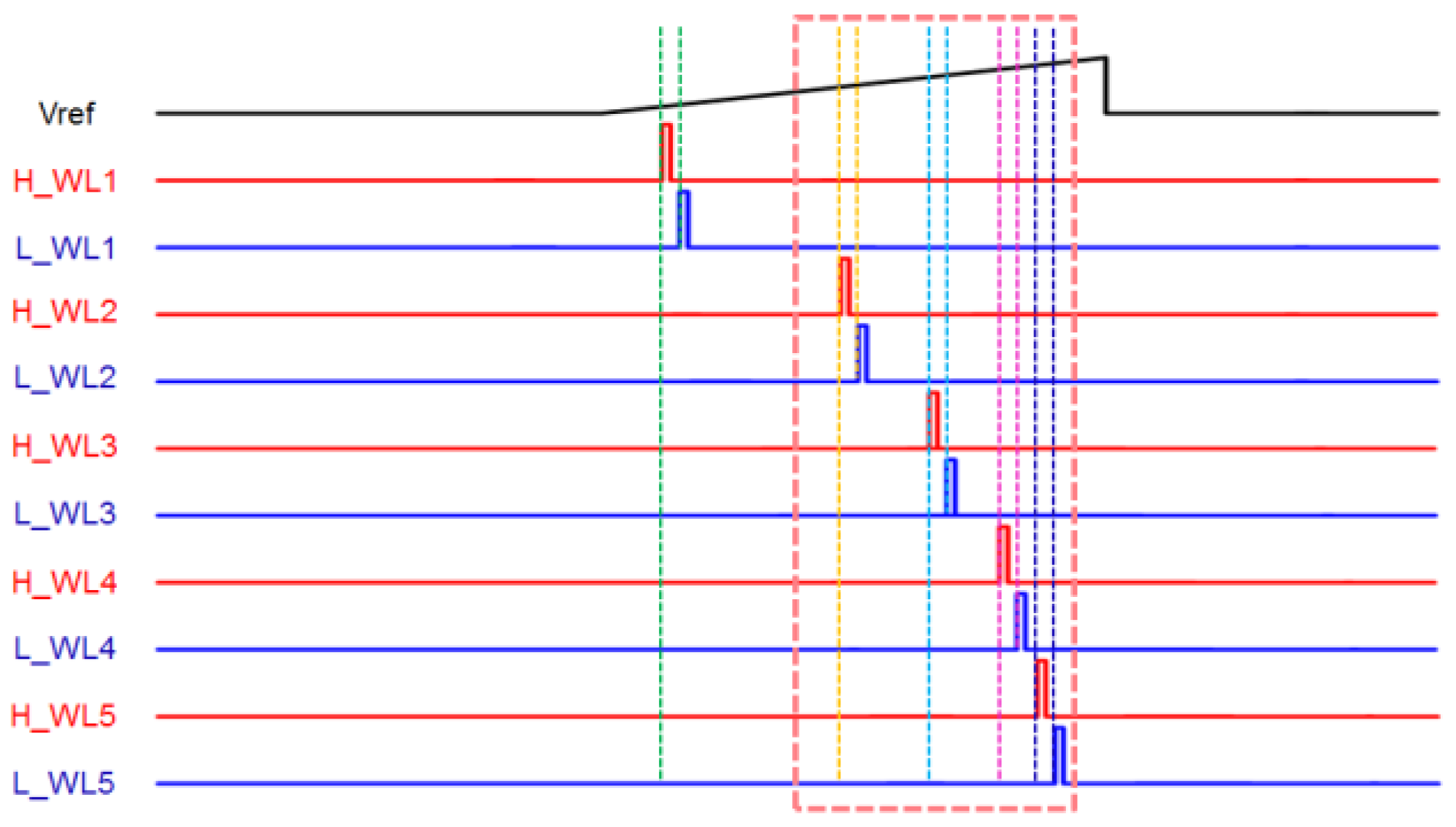

2.2. The Operation of the Proposed CIS

2.3. The Proposed Logarithmic Counter for Word Line Signals

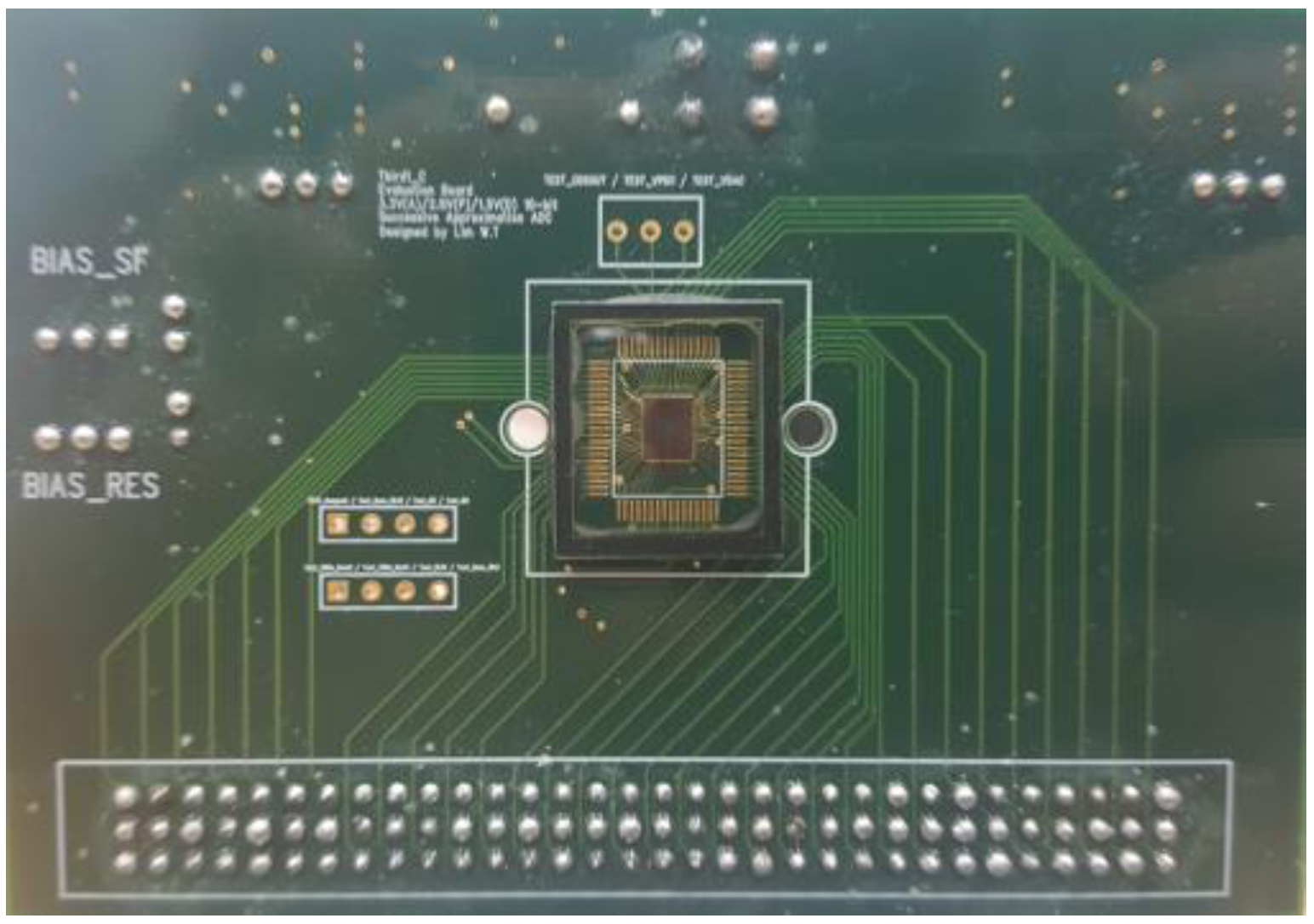

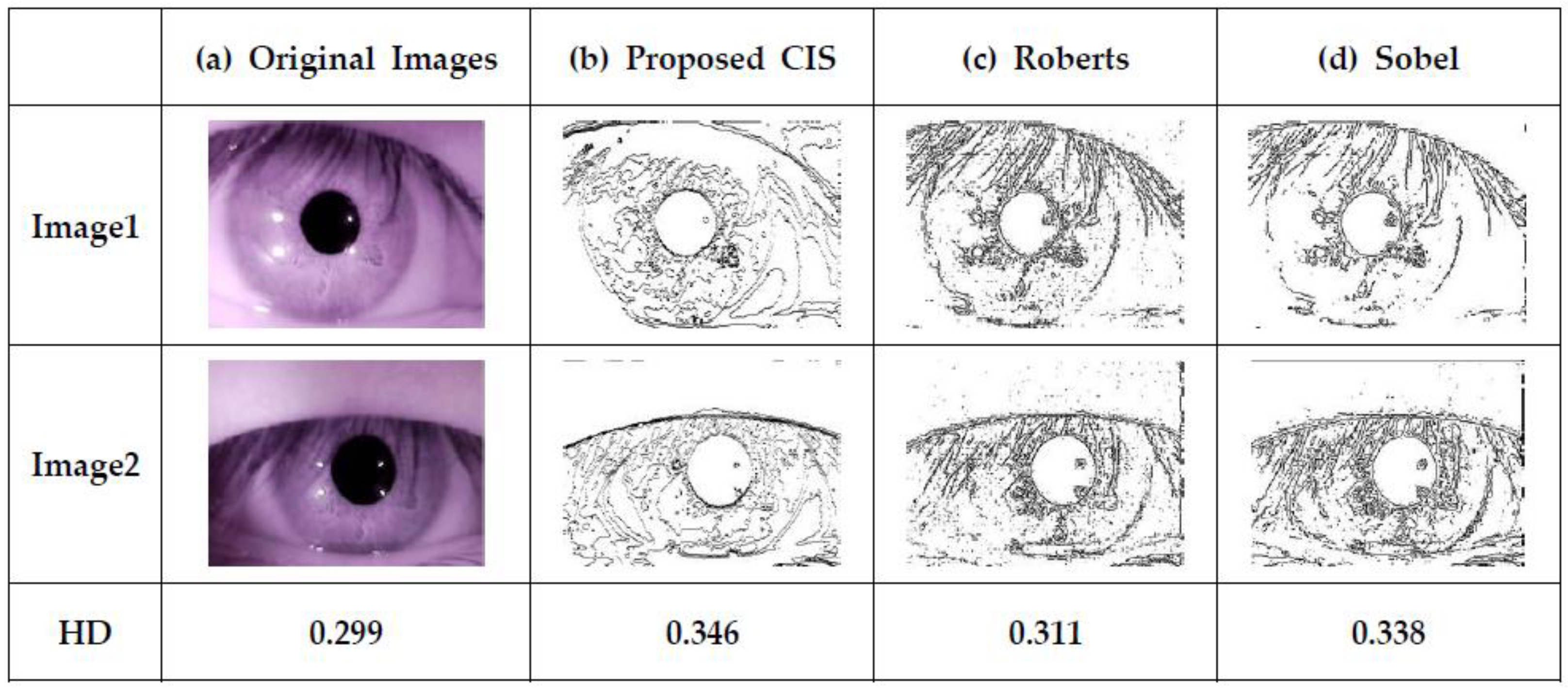

3. Experimental Results

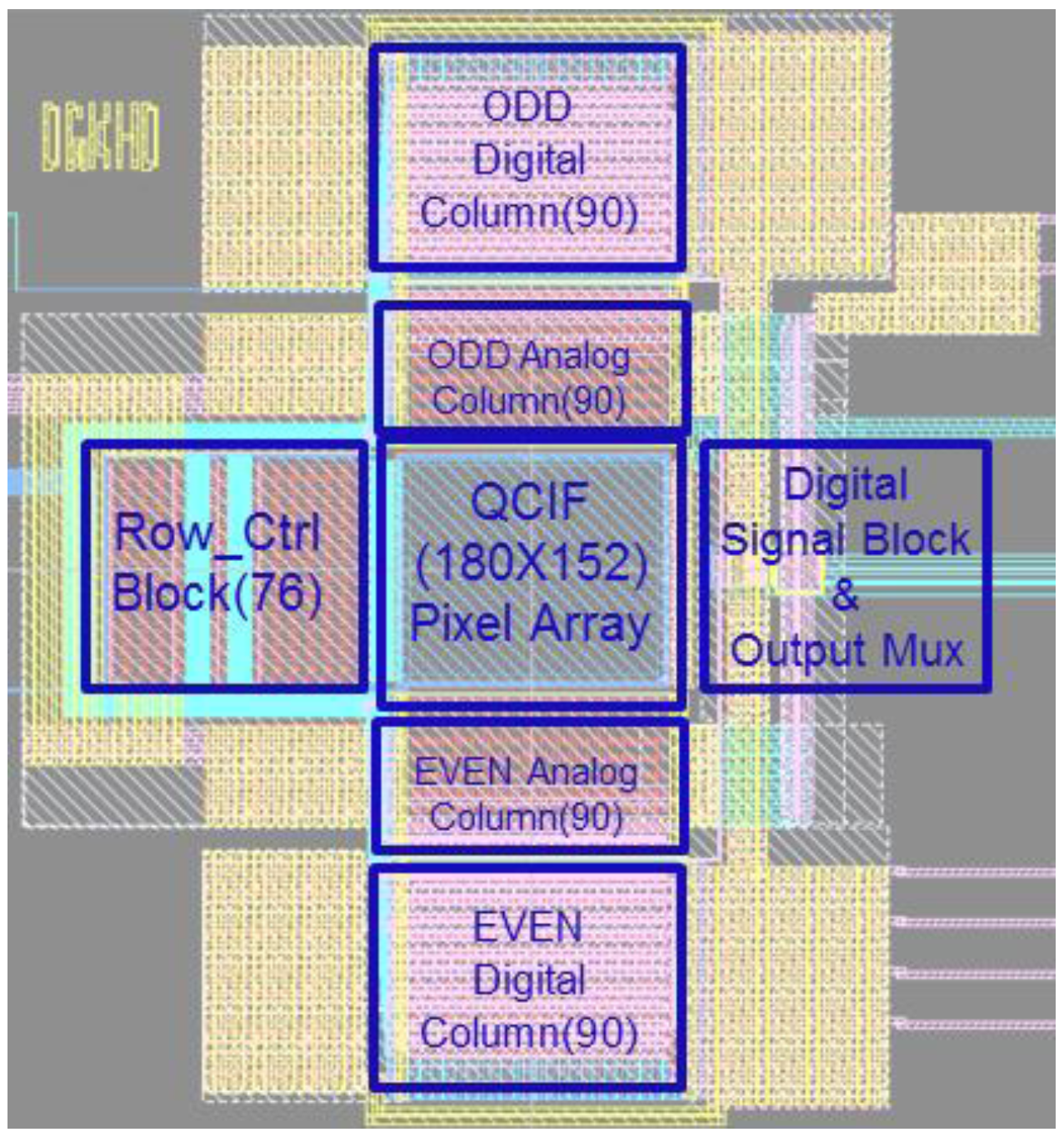

3.1. Layout of the Proposed CIS

3.2. Measurement Results

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Argles, D.; Pease, A.; Walters, R. An Improved Approach to Secure Authentication and Signing. In Proceedings of the Advanced Information Networking and Applications Workshops, Niagara Falls, ON, Canada, 21–23 May 2007; pp. 1–4. [Google Scholar]

- De Marsico, M.; Petrosino, A.; Ricciardi, S. Iris recognition through machine learning techniques: A survey. Pattern Recognit. Lett. 2016, 82, 106–115. [Google Scholar] [CrossRef]

- De Marsico, M.; Nappi, M.; Narducci, F.; Proença, H. Insights into the results of MICHE I-Mobile Iris CHallenge Evaluation. Pattern Recognit. 2018, 74, 286–304. [Google Scholar] [CrossRef]

- Hajari, K.; Bhoyar, K. A review of issues and challenges in designing Iris Recognition Systems for noisy imaging environment. In Proceedings of the 2015 International Conference on Pervasive Computing (ICPC), Pune, India, 8–10 January 2015; pp. 1–6. [Google Scholar]

- Miyazawa, K.; Ito, K.; Aoki, T.; Kobayashi, K.; Nakajima, H. An efficient iris recognition algorithm using phase-based image matching. In Proceedings of the IEEE International Conference on Image Processing, Geneva, Italy, 14 September 2005; pp. 49–52. [Google Scholar]

- Bin, L.; Fuxing, Y.; Lei, Y. Key technologies and research development of CMOS image sensors. In Proceedings of the 2010 Second IITA International Conference on Geoscience and Remote Sensing (IITA-GRS), Qingdao, China, 28–31 August 2010; pp. 322–325. [Google Scholar]

- Komuro, T.; Watanabe, Y.; Ishikawa, M.; Narabu, T. High-S/N imaging of a moving object using a high-frame-rate camera. In Proceedings of the 15th IEEE International Conference on Image Processing, San Diego, CA, USA, 12–15 October 2008; pp. 517–520. [Google Scholar]

- Liu, H.; Huang, Y.; Li, M.; Weixiong, L. A Simple and Impactful Approach to Detect the Edge of Space Images. In Proceedings of the International Conference on Information Engineering and Computer Science, Wuhan, China, 19–20 December 2009; pp. 1–4. [Google Scholar]

- Daugman, J. How Iris Recognition Works. IEEE Trans. Circuits Syst. Video Technol. 2004, 14, 21–30. [Google Scholar] [CrossRef]

- Son, S.; Jeon, J.; Namgung, S.; Yoo, Y.; Song, M. A one-shot digital correlated double sampling with a differential difference amplifier for a high-speed CMOS image sensor. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 1054–1057. [Google Scholar]

- Zhong, S.; Yao, L.; Zhang, J. A small-area low-power ADC array for image sensor applications. In Proceedings of the 2013 IEEE 10th International Conference on ASIC (ASICON), Shenzhen, China, 28–31 October 2013; pp. 1–4. [Google Scholar]

- Sony IMX332 Sensor Datasheet. Available online: https://www.sony-semicon.co.jp/products_en/IS/sensor1/products/imx332.html (accessed on 23 February 2018).

- SuperPix SP9260 Datasheet. Available online: http://www.superpix.com.cn/en/xiazai/SP9260.pdf (accessed on 23 February 2018).

- Zuo, J.; Schmid, N. An Automatic Algorithm for Evaluating the Precision of Iris Segmentation. In Proceedings of the 2008 IEEE 2nd International Conference on Biometrics: Theory, Applications and Systems, Arlington, TX, USA, 29 September–1 October 2008. [Google Scholar]

- GIRIST Tutorial. Available online: http://www.grusoft.com/girist/GIRIST_tutorial.pdf (accessed on 23 February 2018).

- Maini, R.; Aggarwal, H. Aggarwal Study and comparison of various image edge detection techniques. Int. J. Image Process. 2009, 3, 1–12. [Google Scholar]

| Process | Open Loop Gain [dB] | Unity Gain Frequency [MHz] | ||||||

|---|---|---|---|---|---|---|---|---|

| Max. | Min. | Mean | STD. | Max. | Min. | Mean | STD. | |

| ff | 34.82 | 25.4 | 29.74 | 1.38 | 32.3 | 28.12 | 30.36 | 0.81 |

| nn | 34.02 | 25.1 | 29.61 | 1.34 | 23.91 | 22.07 | 23.08 | 0.35 |

| ss | 32.79 | 24.9 | 29.55 | 1.30 | 19.27 | 17.7 | 18.60 | 0.38 |

| Process | 0.18 μm 1P4M CMOS process |

| Chip size | 2.35 mm × 2.35 mm(5.53 mm2) |

| Core size | 1.72 mm × 1.65 mm(2.84 mm2) |

| Resolution | QCIF (174 × 144) |

| Pixel type | 4-shared 4T-APS |

| Supply voltages | 3.3 V(Analog)/1.8 (Digital) |

| ADC resolution | 1 bit (8-bit ADC-comparable accuracy) |

| Power consumption | 2.80 mW @ 60 fps 12.36 mW @ 520 fps |

| Maximum frame rate | 520 fps |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, K.; Song, M.; Kim, S.Y. The Design of a Single-Bit CMOS Image Sensor for Iris Recognition Applications. Sensors 2018, 18, 669. https://doi.org/10.3390/s18020669

Park K, Song M, Kim SY. The Design of a Single-Bit CMOS Image Sensor for Iris Recognition Applications. Sensors. 2018; 18(2):669. https://doi.org/10.3390/s18020669

Chicago/Turabian StylePark, Keunyeol, Minkyu Song, and Soo Youn Kim. 2018. "The Design of a Single-Bit CMOS Image Sensor for Iris Recognition Applications" Sensors 18, no. 2: 669. https://doi.org/10.3390/s18020669