Noise Reduction Effect of Multiple-Sampling-Based Signal-Readout Circuits for Ultra-Low Noise CMOS Image Sensors

Abstract

:1. Introduction

2. Signal Readout Architecture for Ultra-Low-Noise CISs

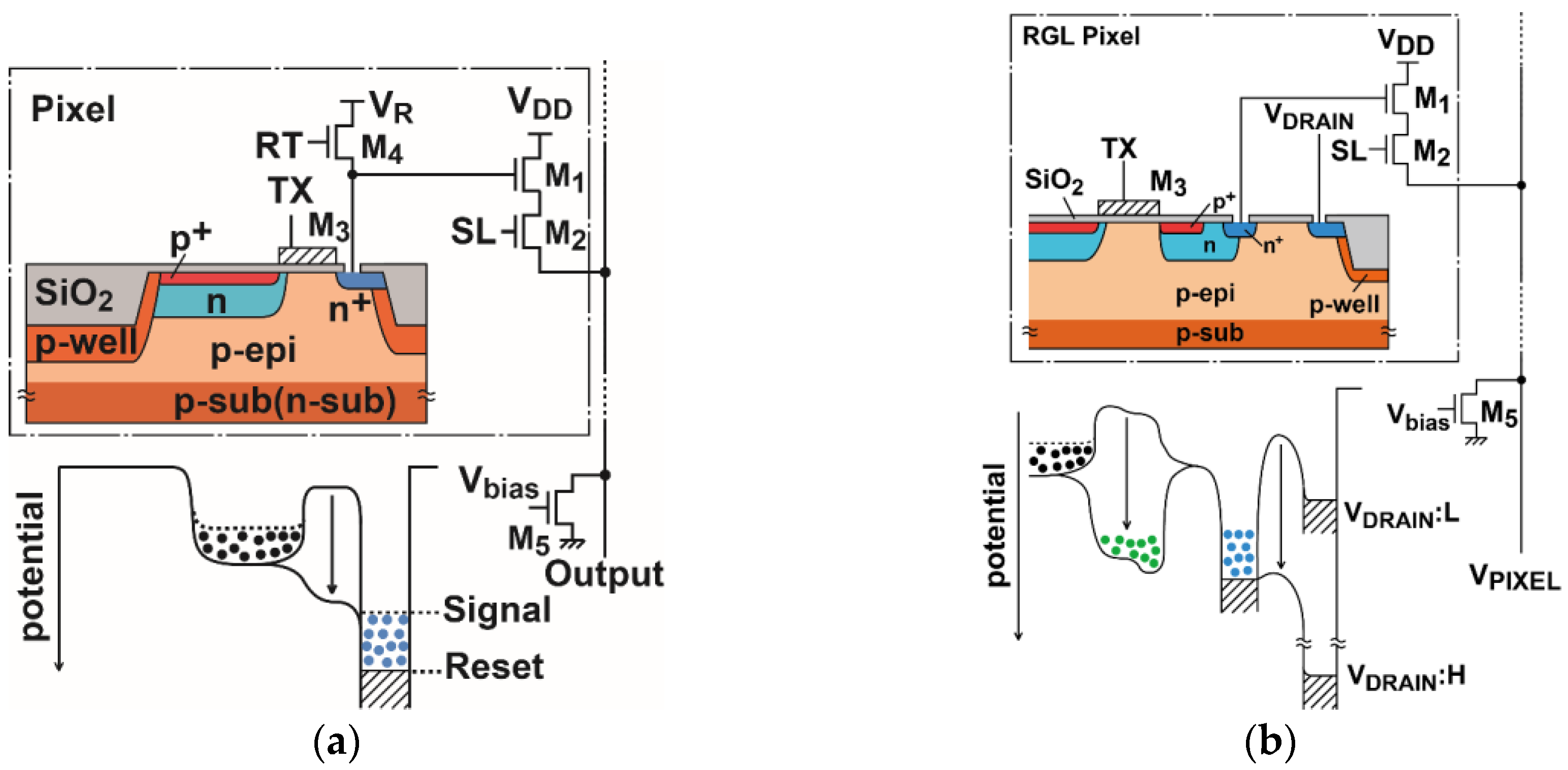

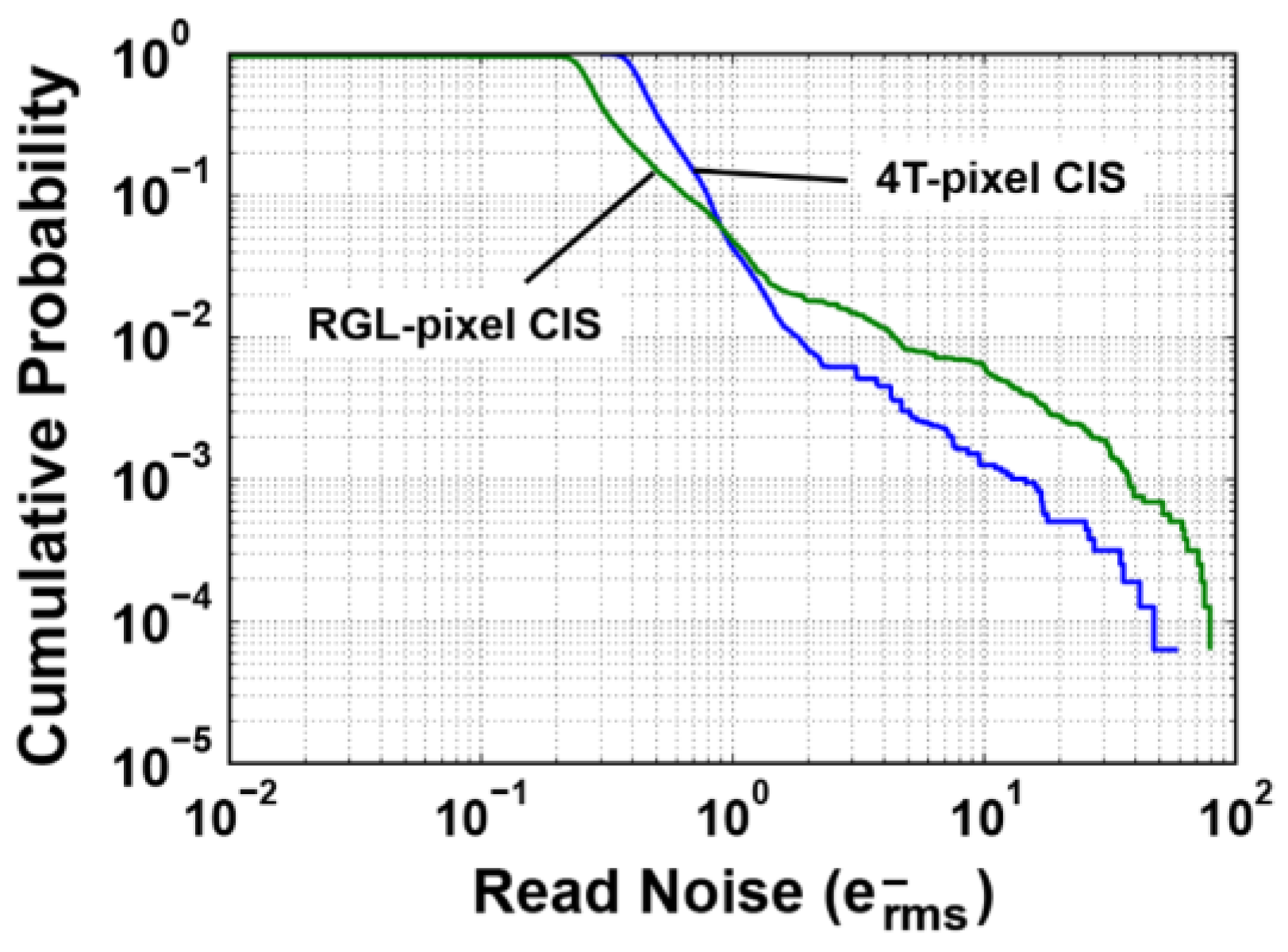

2.1. Active Pixel Sensors for High-Conversion Gain

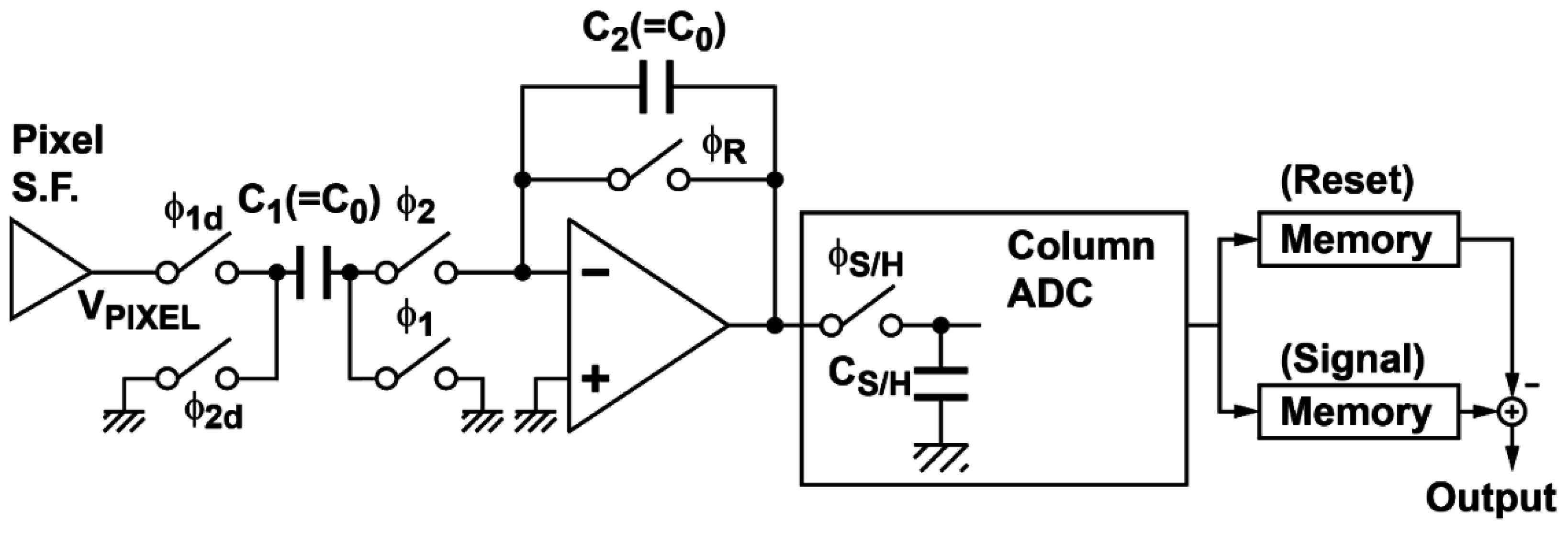

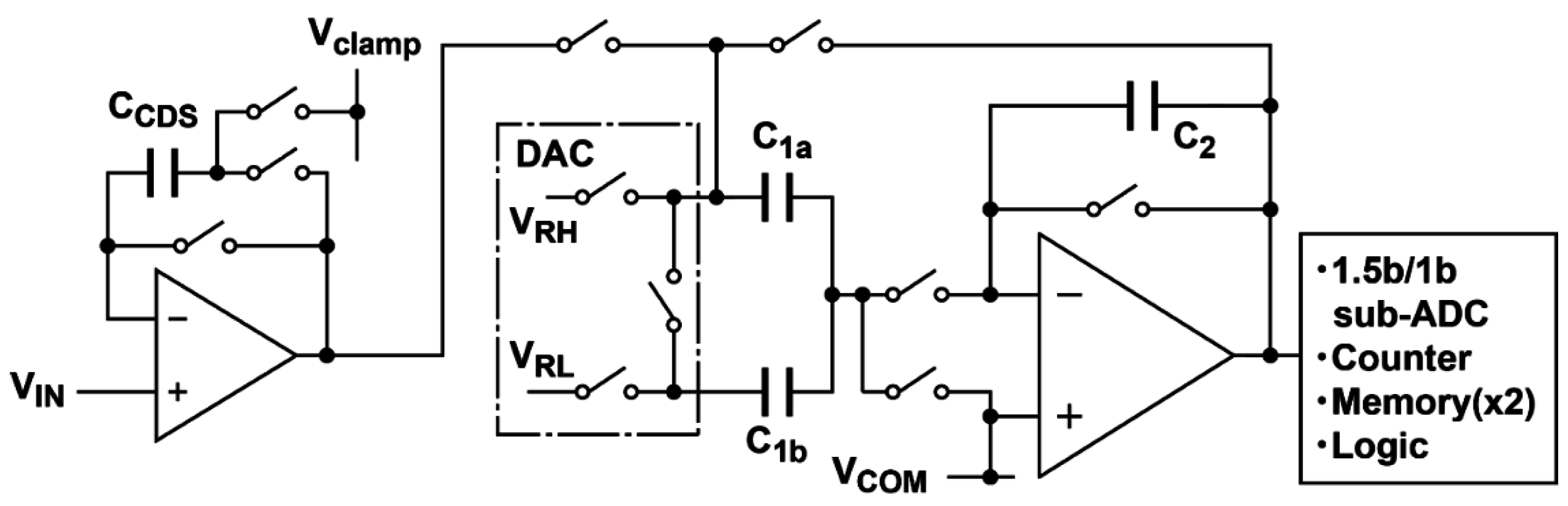

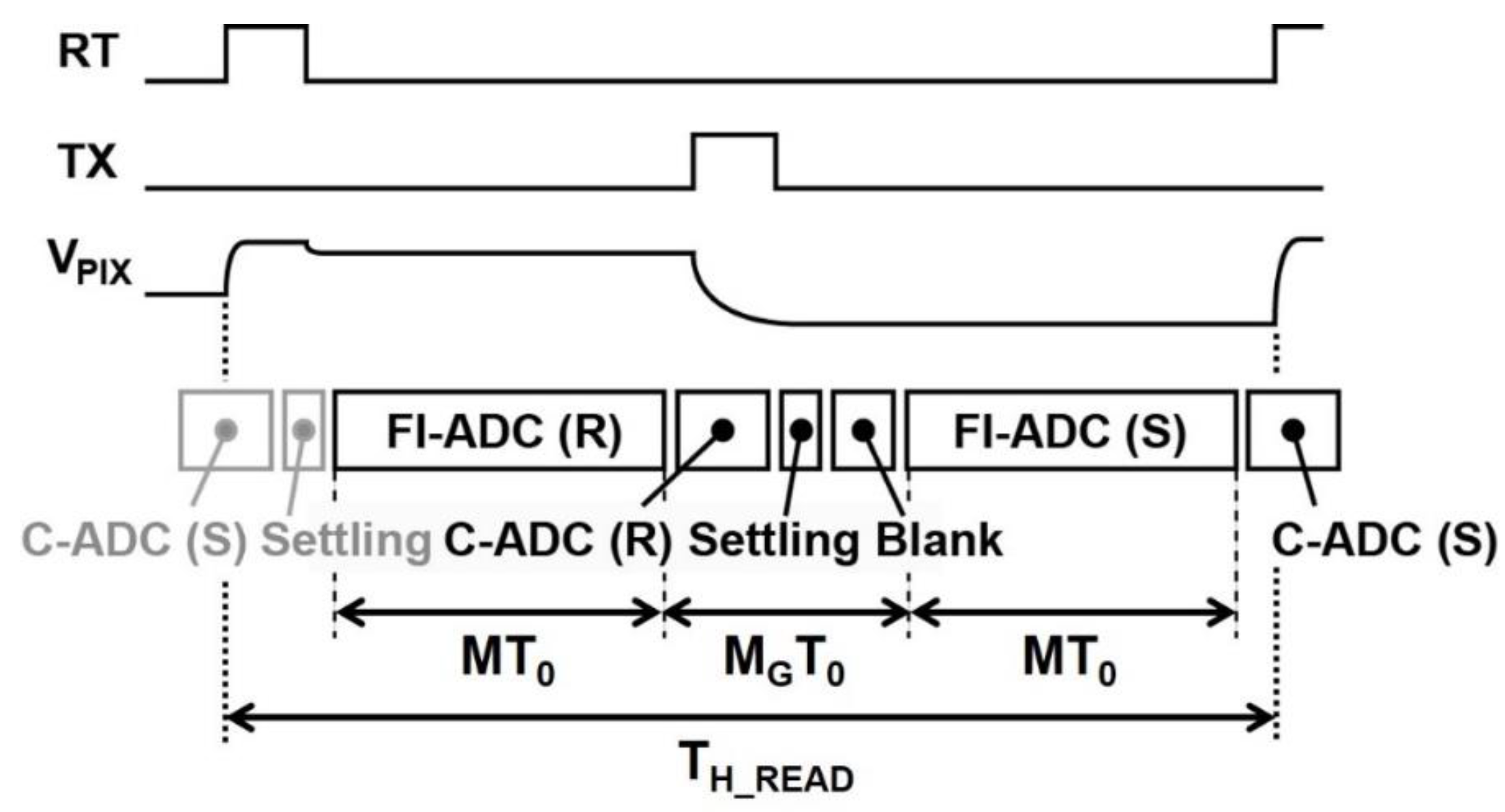

2.2. Column Readout and ADC Circuits Using Multiple Sampling

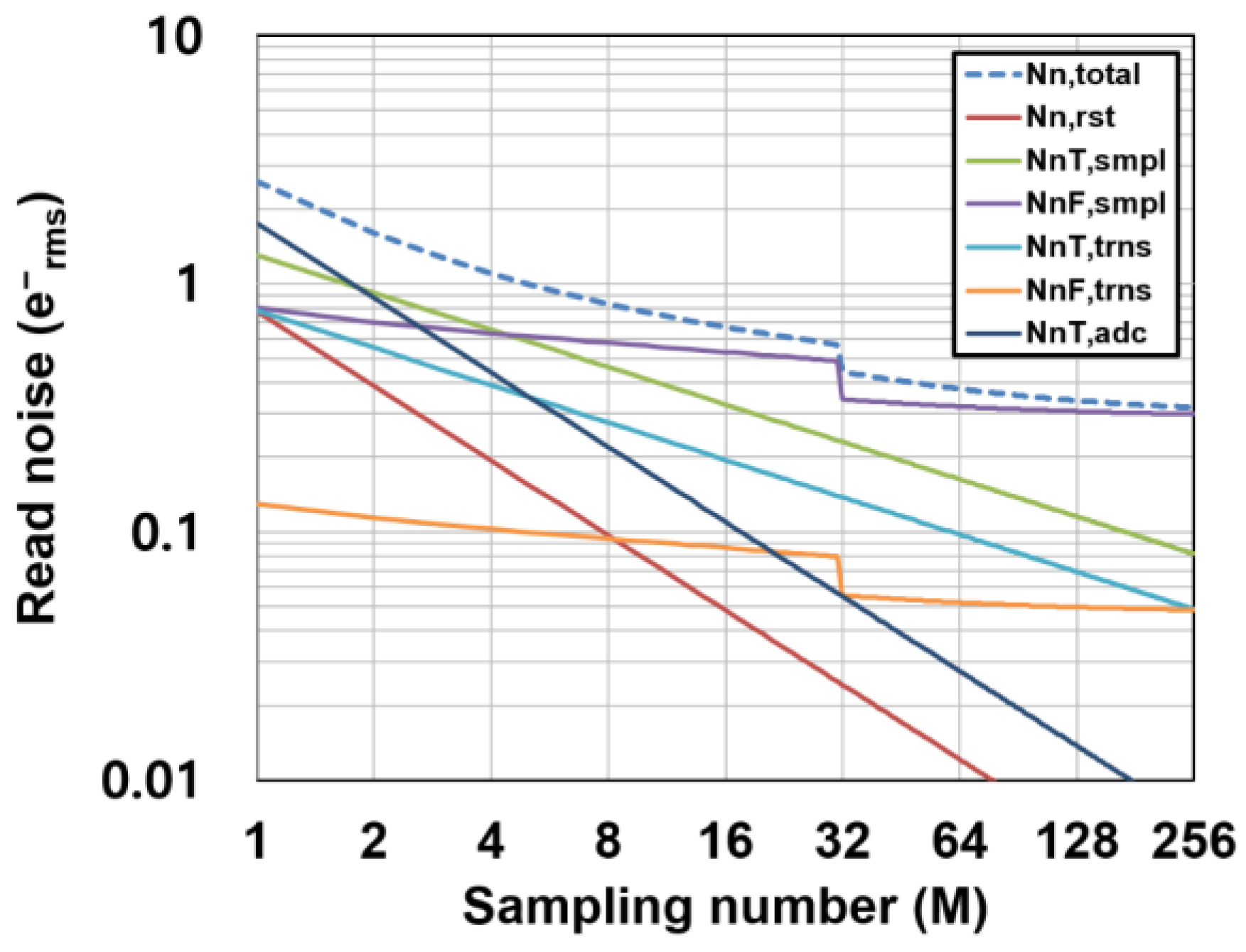

3. Noise Analysis of Readout Circuits with Multiple Sampling

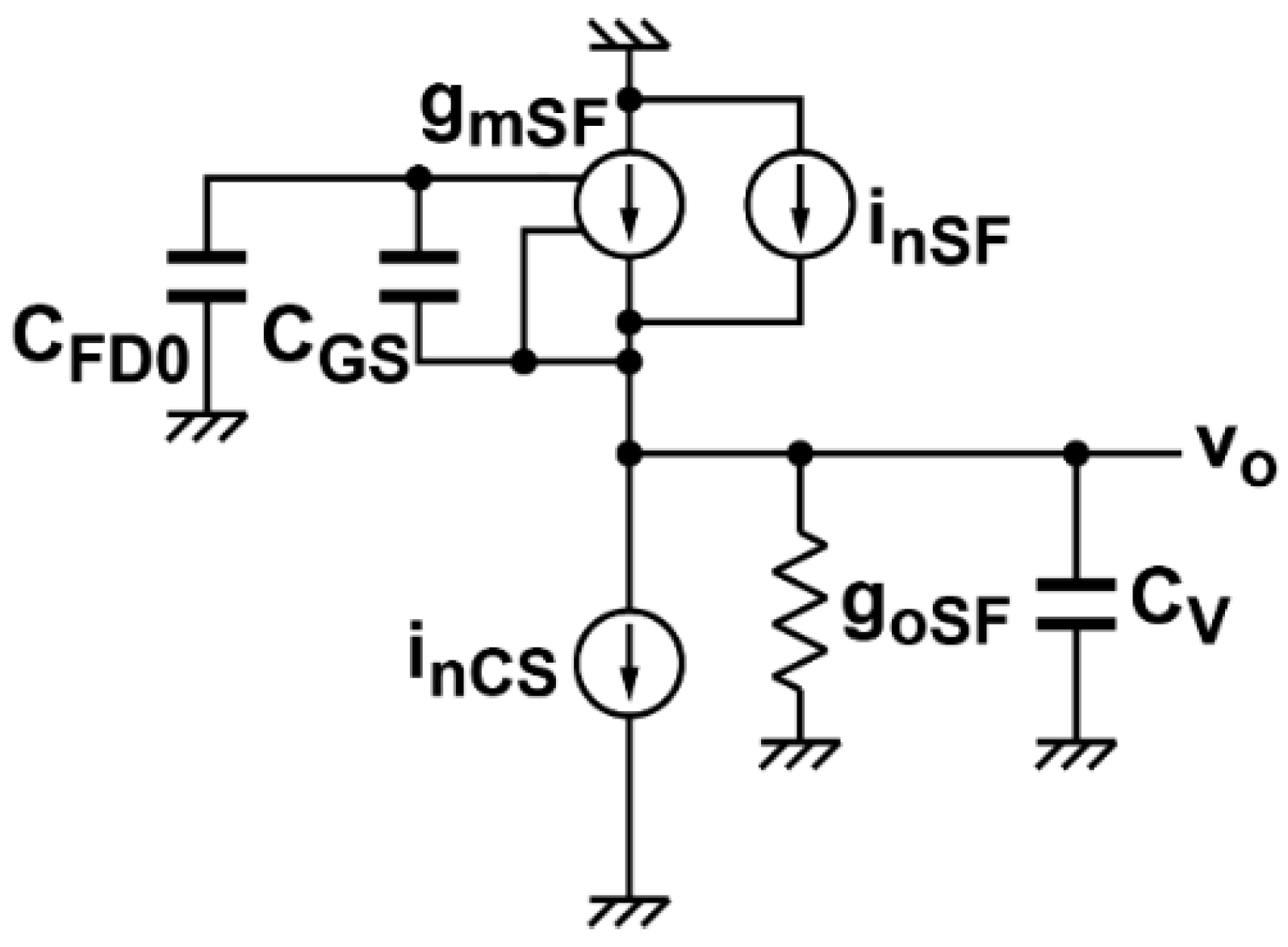

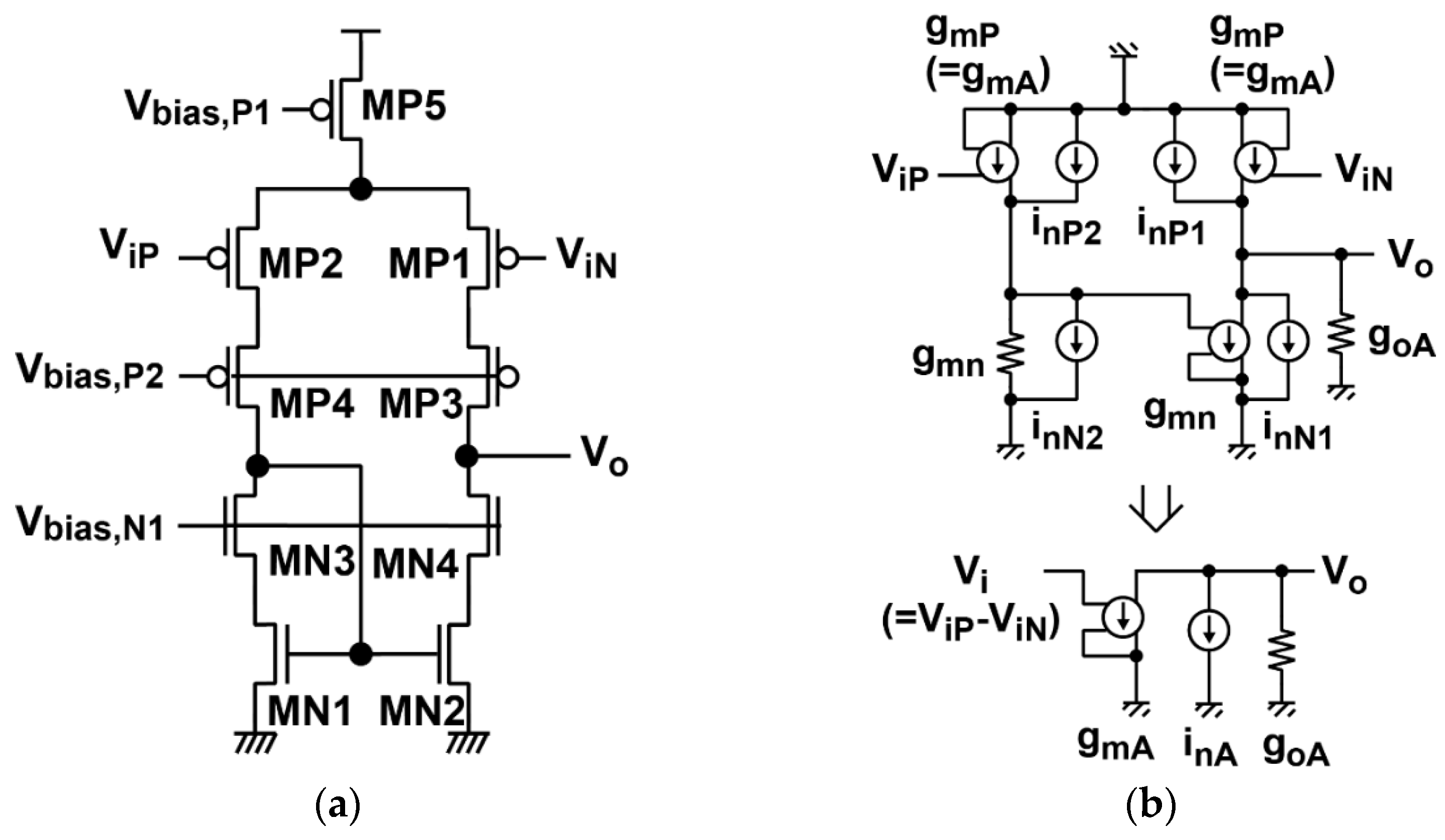

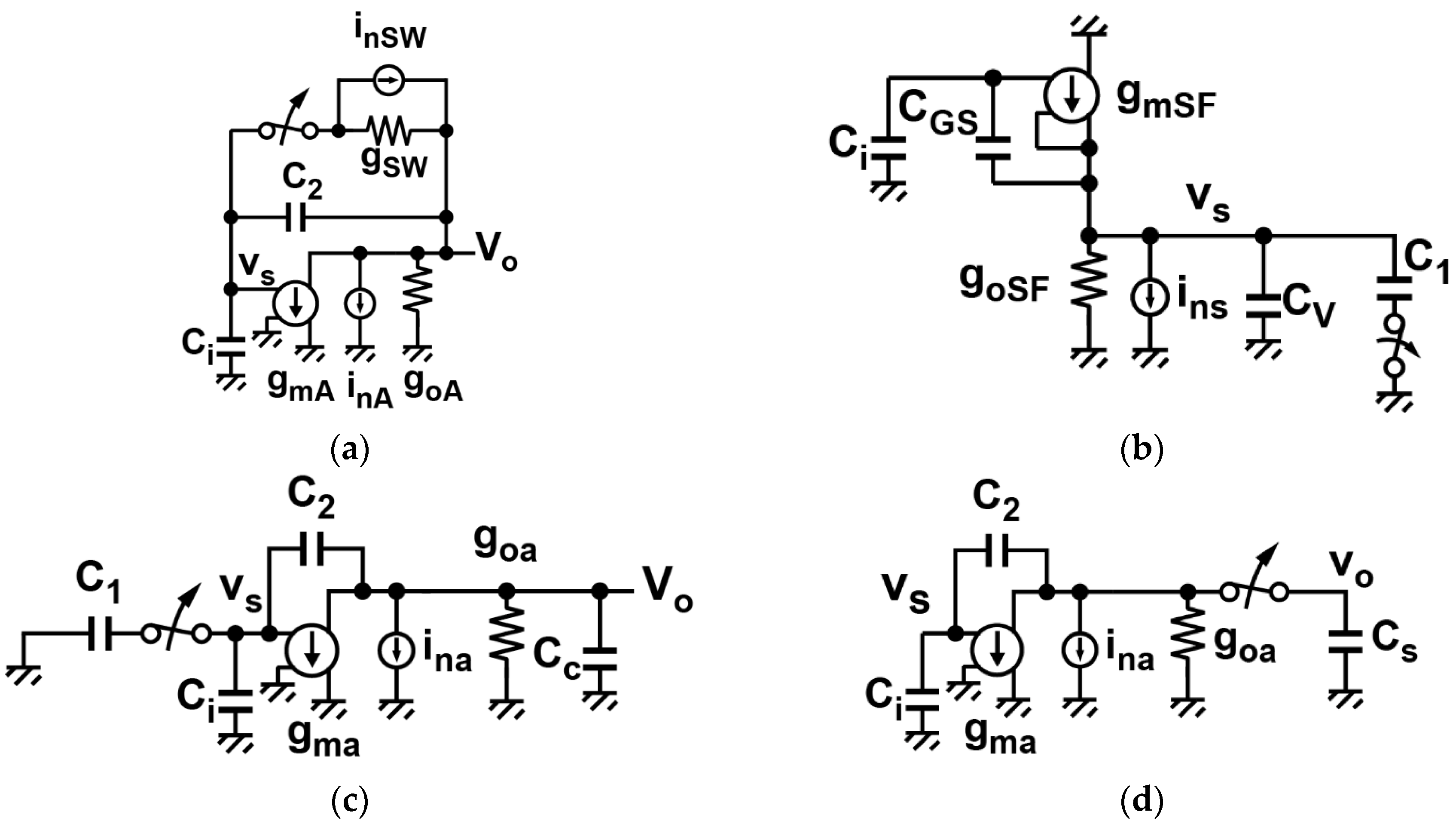

3.1. Modeling of Noise Sources: Pixel Source Follower and Column Amplifier

3.2. Analysis of Noise Components of Readout Circuits

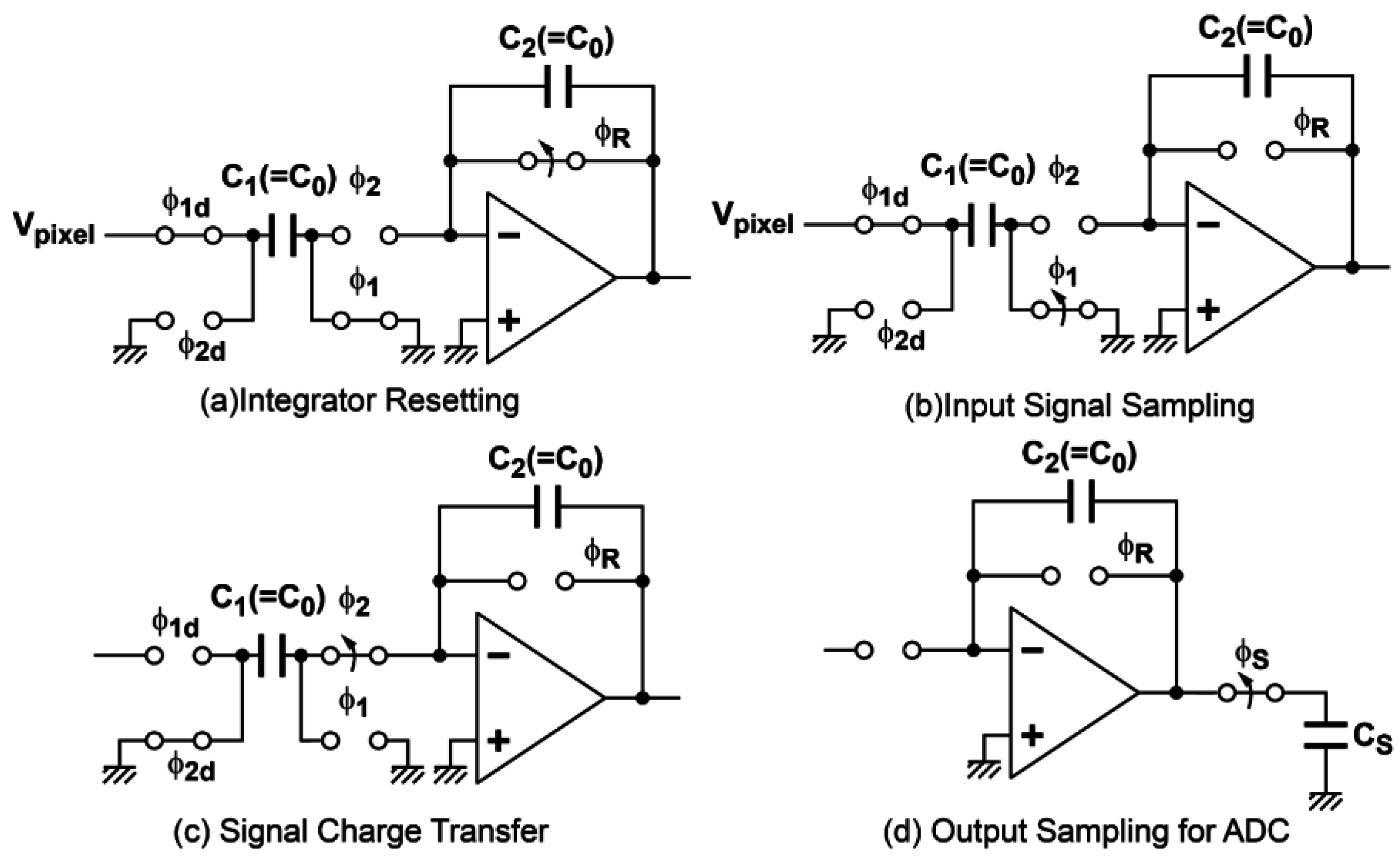

3.2.1. Reset Noise of the Integrator

3.2.2. Thermal and 1/f Noise in the Input Signal Sampling Phase

3.2.3. Thermal and 1/f Noise in the Signal Charge Transfer Phase

3.2.4. Sampled Noise of the Integrator Output for A/D Conversion

3.2.5. Total Noise

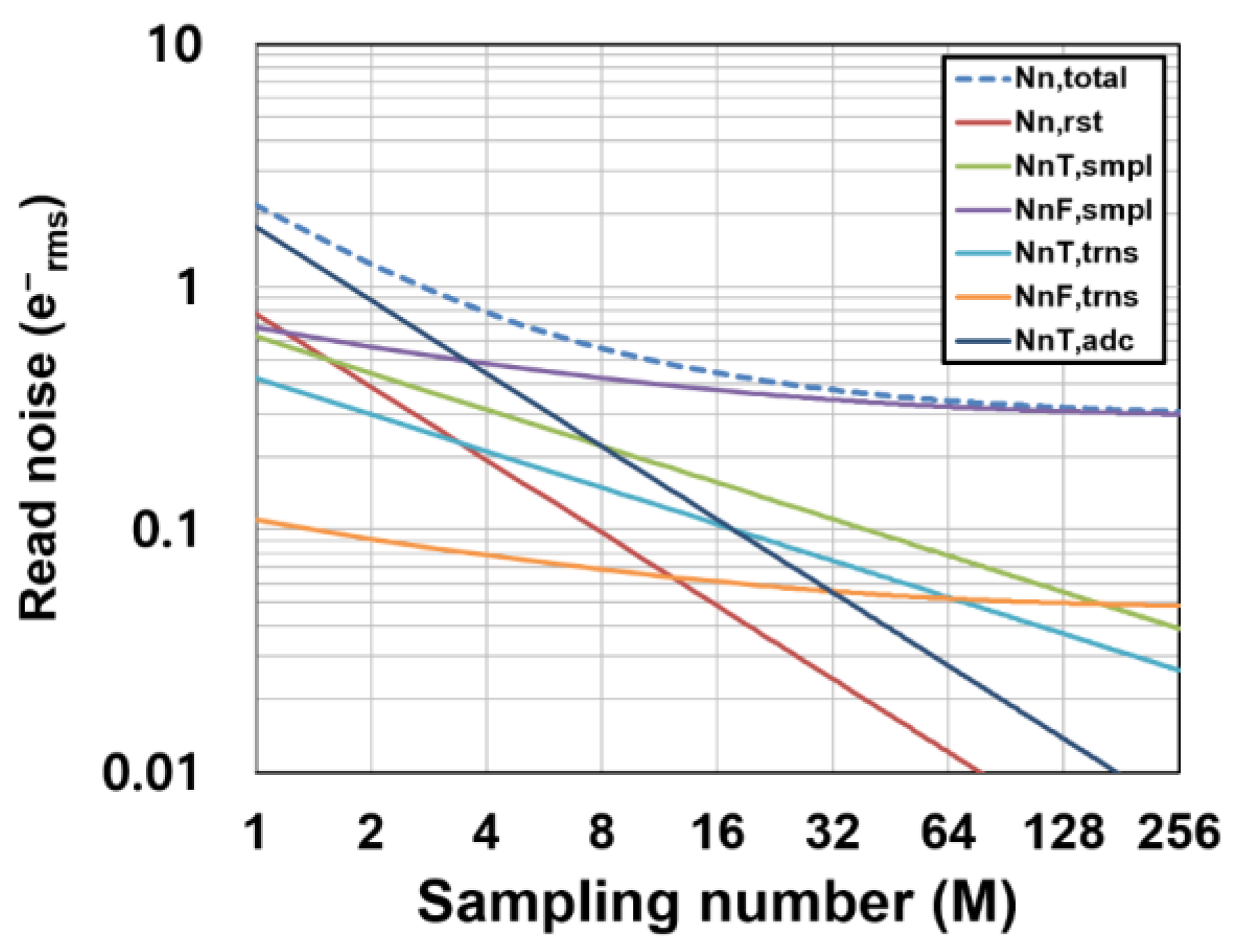

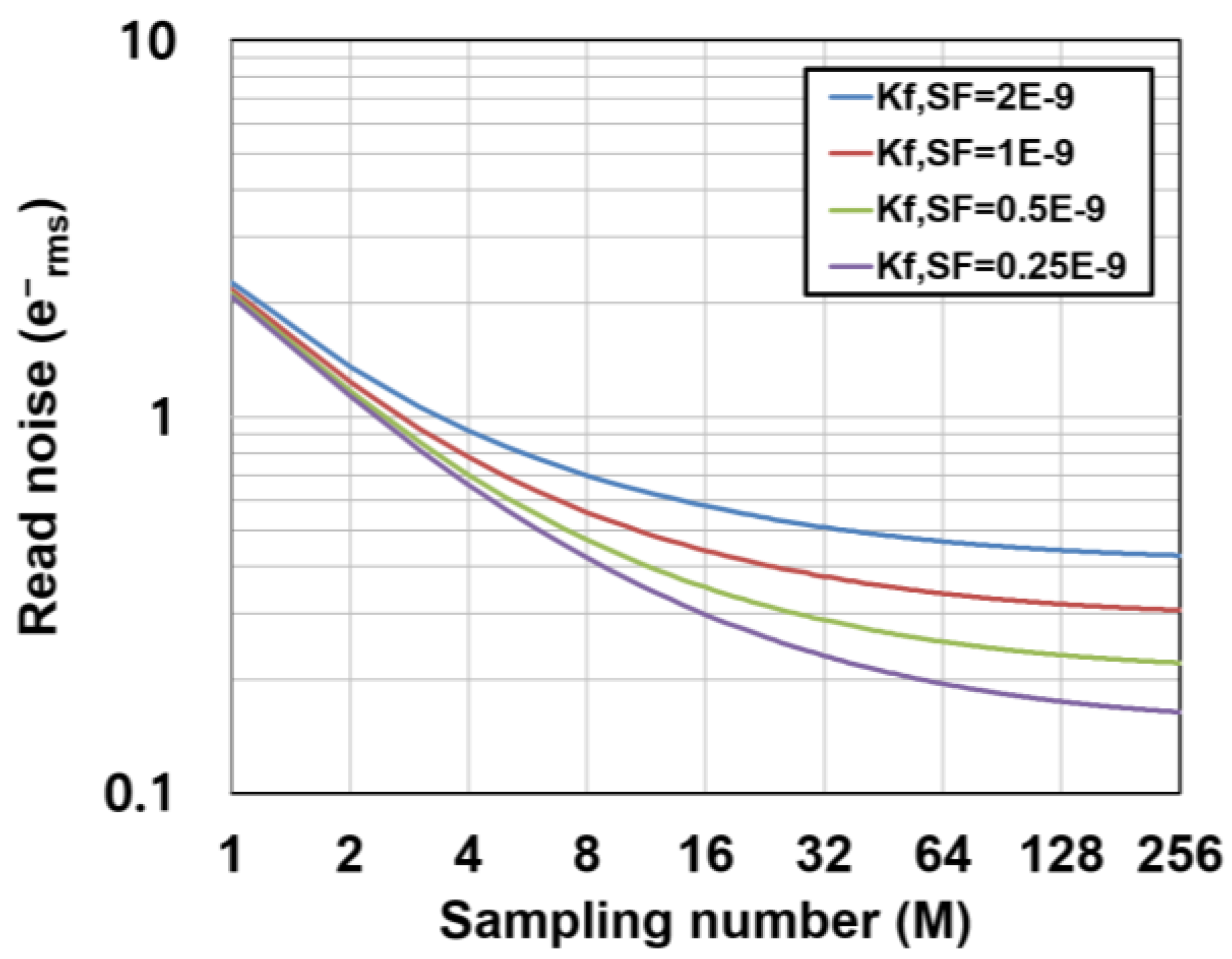

3.3. Noise Calculation for the Designed Ultra-Low-Noise CIS

4. Implementation and Results

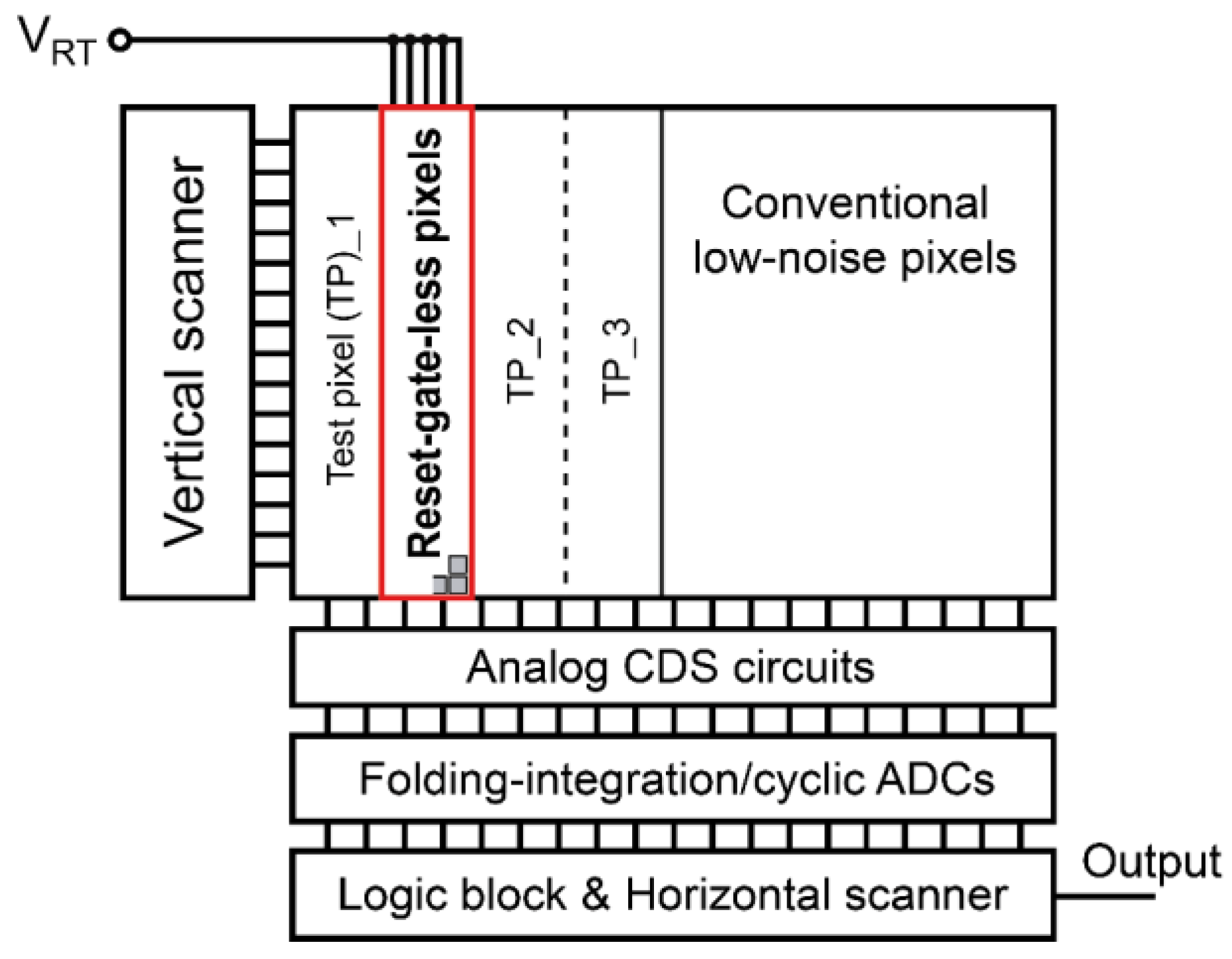

4.1. Implementation

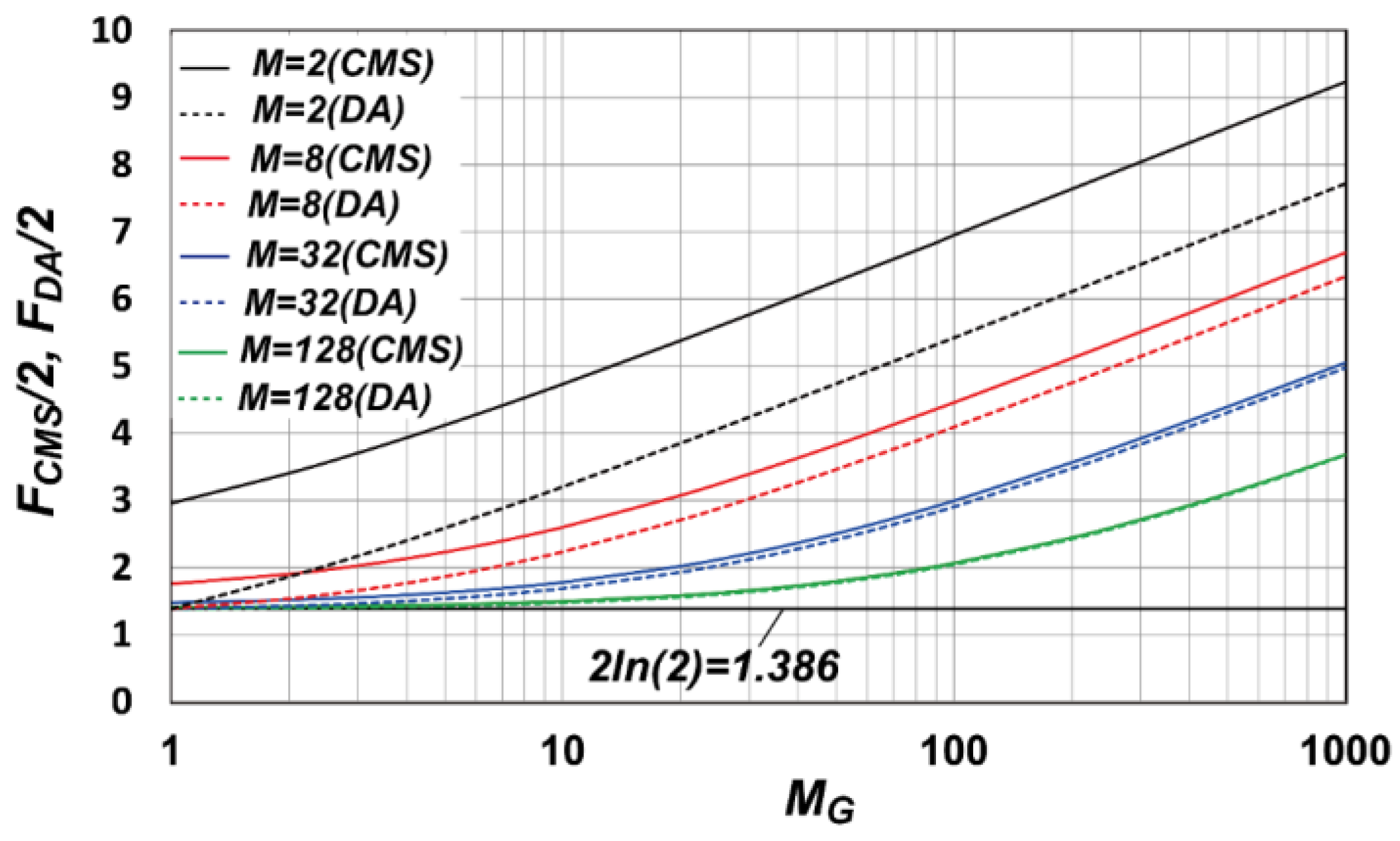

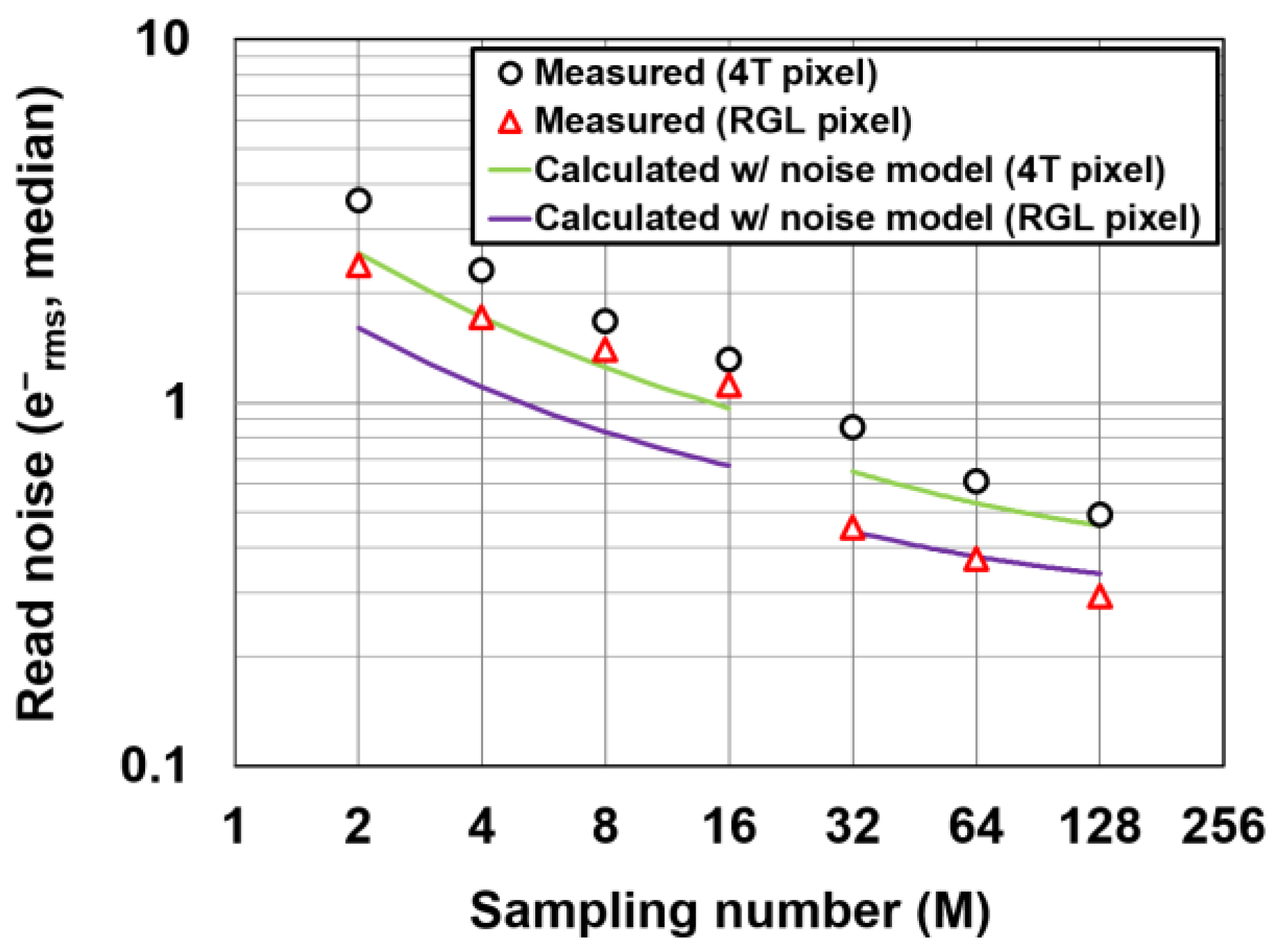

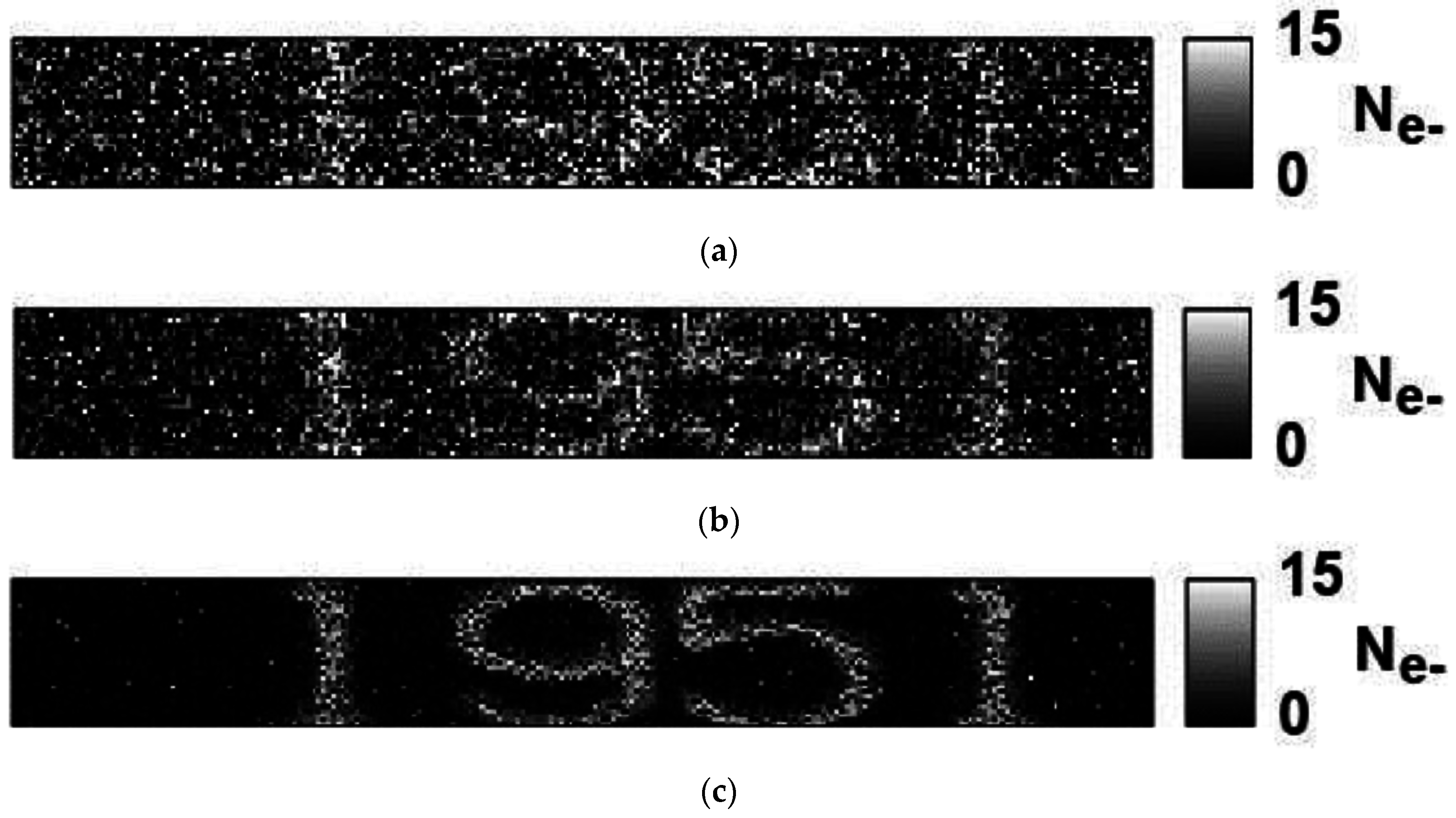

4.2. Noise Reduction Effect of the CMS

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations

| CIS | CMOS image sensor |

| CDS | correlated double sampling |

| CMS | correlated double sampling, |

| ADC | analog to digital converter |

| MCDS | multiple correlated double sampling |

References

- Fossum, E.R. Active pixel sensors: Are CCDs dinosaurs? Proc. IEEE 1993, 1900, 2–14. [Google Scholar]

- Mendis, S.; Kemeny, S.E.; Fossum, E.R. CMOS active pixel image sensor. IEEE Trans. Electron Devices 1994, 41, 452–453. [Google Scholar] [CrossRef]

- Lee, P.R.K.; Gee, R.C.; Guidash, R.M.; Lee, T.-H.; Fossum, E.R. An active pixel sensor fabricated using CMOS/CCD process technology. In Proceedings of the IEEE Workshop CCD and Advanced Image Sensors, Dana Point, CA, USA, 20–22 April 1995; pp. 115–119.

- Teranishi, N.; Kohno, A.; Ishihara, Y.; Oda, E.; Arai, K. No image lag photodiode structure in the interline CCD image sensor. In Proceedings of the IEDM ’98 Technical Digest International Electron Devices Meeting, San Francisco, CA, USA, 6–9 December 1998; pp. 324–327.

- Fossum, E.R.; Hondongwa, D.B. A review of the pinned photodiode for CCD and CMOS image sensors. IEEE J. Electron Devices Soc. 2014, 2, 33–43. [Google Scholar] [CrossRef]

- Inoue, S.; Sakurai, K.; Ueno, I.; Koizumi, T.; Hiyama, H.; Asaba, T.; Sugawa, S.; Maeda, A.; Higashitani, K.; Kato, H.; et al. A 3.25-Mpixel APS-C size CMOS image sensor. In Proceedings of the IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors, Lake Tahoe, NV, USA, 7–9 June 2001.

- Fowler, B.; Liu, C.; Mims, S.; Balicki, J.; Li, W.; Do, H.; Vu, P. Wide dynamic range low-light-level CMOS image sensor. In Proceedings of the 2009 International Image Sensor Workshop, Bergen, Norway, 26–28 June 2009; pp. 340–343.

- Lotto, C.; Seitz, P.; Baechler, T. A sub-electron readout noise CMOS image sensor with pixel-level open-loop voltage amplification. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 402–403.

- Chen, Y.; Xu, Y.; Mierop, A.; Wang, X.; Theuwissen, A. A 0.7 e− temporal readout noise CMOS image sensor for low-light-level imaging. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 384–385.

- Boukhayma, A.; Peizeat, A.; Enz, C. A 0.4 e−rms temporal readout noise 7.5 µm pitch and a 66% fill factor pixel for low light CMOS image sensors. In Proceedings of the 2015 International Image Sensor Workshop, Vaals, the Netherlands, 8–11 June 2015; pp. 365–368.

- Yao, Q.; Dierickx, B.; Dupont, B.; Rutterns, G. CMOS image sensor reaching 0.34 e−rms read noise by inversion-accumulation cycling. In Proceedings of the 2015 International Image Sensor Workshop, Vaals, The Netherlands, 8–11 June 2015; pp. 369–372.

- Wakabayashi, S.; Kusuhara, F.; Kuroda, R.; Sugawa, S. A linear response single exposure CMOS image sensor with 0.5 e− readout noise and 76 ke− full well capacity. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. 88–89.

- Ma, J.; Fossum, E. Quanta image sensor jot with sub 0.3 e−rms read noise and photon counting capability. IEEE Electron Device Lett. 2015, 36, 926–928. [Google Scholar] [CrossRef]

- Ma, J.; Starkey, D.; Rao, A.; Odame, K.; Fossum, E.R. Characterization of quanta image sensor pump-gate jots with deep sub-electron read noise. J. Electron Devices Soc. 2015, 3, 472–480. [Google Scholar] [CrossRef]

- Seo, M.W.; Kawahito, S.; Kagawa, K.; Yasutomi, K. A 0.27 e−rms read noise 220 µV/e− conversion gain reset-gate-less CMOS image sensor with 0.11 µm CIS process. IEEE Electron Device Lett. 2015, 36, 1344–1347. [Google Scholar]

- Wolfel, S.; Herrmann, S.; Lechner, P.; Lutz, G.; Porro, M.; Richter, R.H.; Struder, L.; Treis, J. A novel way of single optical photon detection: Beating 1/f noise limit with ultra-high resolution DEPFET-RNDR devices. IEEE Trans. Nucl. Sci. 2007, 54, 1311–1318. [Google Scholar] [CrossRef]

- Lutz, G.; Porro, M.; Aschauer, S.; Wolfel, S.; Struder, L. The DEPFET sensor-amplifier structure: A method to beat 1/f noise and reach sub-electron noise in pixel detectors. Sensors 2016, 16, 608. [Google Scholar] [CrossRef]

- Krymski, A.; Khaliullin, N.; Rhodes, H. A 2 e− noise 1.3-megapixel CMOS sensor. In Proceedings of the IEEE Workshop on CCD and Advanced Image Sensors, Elmau, Germany, 15–17 May 2003; pp. 1–6.

- Kawahito, S.; Sakakibara, M.; Handoko, D.; Nakmura, N.; Satoh, H.; Higashi, M.; Mabuchi, K.; Sumi, H. A column-based pixel-gain-adaptive CMOS image sensor for low-light-level imaging. In Proceedings of the 2003 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003; pp. 224–225.

- Sakakibara, M.; Kawahito, S.; Handoko, D.; Nakmura, N.; Satoh, H.; Higashi, M.; Mabuchi, K.; Sumi, H. A high-sensitivity CMOS image sensor with gain-adaptive column amplifiers. IEEE J. Solid State Circuits 2005, 40, 1147–1156. [Google Scholar] [CrossRef]

- Fowler, A.M.; Gatley, I. Noise reduction strategy for hybrid IR focal plane arrays. Proc. SPIE 1991, 1541, 127–133. [Google Scholar]

- Porro, M.; Fiorini, C.; Studer, L. Theoretical comparison between two different filtering techniques suitable for VLSI spectroscopic amplifier ROTOR. Nucl. Instrum. Methods Phys. Res. A 2003, 512, 179–190. [Google Scholar] [CrossRef]

- Kawahito, S.; Kawai, N. Column parallel signal processing techniques for reducing thermal and RTS noises in CMOS image sensors. In Proceedings of the IEEE International Image Sensor Workshop, Ogunquit, ME, USA, 7–10 June 2007; pp. 226–229.

- Seo, M.W.; Suh, S.H.; Iida, T.; Takasawa, T.; Isobe, K.; Watanabe, T.; Itoh, S.; Yasutomi, K.; Kawahito, S. A low-noise high intrascene dynamic range CMOS image sensor with a 13 to 19b variable-resolution column-parallel folding-integration/cyclic ADC. IEEE J. Solid State Circuits 2012, 47, 272–283. [Google Scholar] [CrossRef]

- Seo, M.-W.; Sawamoto, T.; Akahori, T.; Iida, T.; Takasawa, T.; Yasutomi, K.; Kawahito, S. A low noise wide dynamic range CMOS image sensor with low-noise transistors and 17b column-parallel ADCs. IEEE Sens. J. 2013, 13, 2922–2929. [Google Scholar] [CrossRef]

- Guidash, M. Active Pixel Sensor with Punch-through Reset and Cross-Talk Suppression. U.S. Patent 5,872,371, 16 February 1999. [Google Scholar]

- Seitz, P.; Theuwissen, A.J.P. Single-Photon Imaging; Springer: Berlin, Germany, 2011; pp. 197–217. [Google Scholar]

- Yadid-Pecht, O.; Fossum, E.R.; Pain, B. Optimization of noise and responsivity in CMOS active pixel sensors for detection of ultra low-light level. Proc. SPIE 1997, 3019, 123–136. [Google Scholar]

- Suh, S.G.; Itoh, S.; Aoyama, S.; Kawahito, S. Column parallel correlated multiple sampling circuits for CMOS image sensors and their noise reduction effect. Sensors 2010, 10, 9139–9154. [Google Scholar] [CrossRef]

- Kawai, N.; Kawahito, S. Effectiveness of a correlated multiple sampling differential averager for 1/f noise. IEICE Express Lett. 2005, 2, 379–383. [Google Scholar] [CrossRef]

- Hopkinson, G.R.; Lumb, D.H. Noise reduction techniques for CCD image sensors. J. Phys. E Sci. Instrum. 1982, 15, 1214–1222. [Google Scholar] [CrossRef]

- Goo, J.-S.; Choi, C.-H.; Abramo, A.; Ahn, J.-G.; Yu, Z.; Lee, T.-H.; Dutton, R.W. Physical origin of the excess thermal noise in short channel MOSFETs. IEEE Electron Device Lett. 2001, 22, 101–103. [Google Scholar]

- Kawai, N.; Kawahito, S. Noise analysis of high-gain low-noise column readout circuits for CMOS image sensors. IEEE Trans. Electron Devices 2004, 51, 185–194. [Google Scholar] [CrossRef]

- Findlater, K.M.; Vaillant, J.M.; Baxter, D.J.; Augier, C.; Herault, D.; Henderson, R.K.; Hurwitz, J.E.D.; Grant, L.A.; Volle, J.M. Source follower noise limitations in CMOS active pixel sensors. Proc. SPIE 2004, 5251, 187–195. [Google Scholar]

| Parameters | Values (Conventional 4T) | Values (RGL pixel) |

|---|---|---|

| Temperature (K) | 263 | 263 |

| GcSF (μV/e−) | 135 | 220 |

| GnSF | 2.22 | 1.21 |

| GI | 0.5 | 0.5 |

| C1 (F) | 0.5 × 10−12 | 0.5 × 10−12 |

| C2 (F) | 1.0 × 10−12 | 1.0 × 10−12 |

| CV (F) | 0.84 × 10−12 | 0.84 × 10−12 |

| Ci (F) | 0.15 × 10−12 | 0.15 × 10−12 |

| CS (F) | 0.5 × 10−12 | 0.5 × 10−12 |

| CC (F) | 0.5 × 10−12 | 0.5 × 10−12 |

| KfSF (V2) | 1.8 × 10−10 | 1.0 × 10−9 |

| KfA (V2) | 0.98 × 10−11 | 0.98 × 10−11 |

| ξSF | 2.15 | 2.87 |

| ξA | 2.25 | 2.25 |

| ζSF | 1.01 | 1.01 |

| ζA | 3.94 | 3.94 |

| M | MG | VH_READ (μs) |

|---|---|---|

| 2 | 268 | 172 |

| 4 | 264 | 172 |

| 8 | 256 | 172 |

| 16 | 240 | 172 |

| 32 | 16 | 57.6 |

| 64 | 16 | 96 |

| 128 | 16 | 172 |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kawahito, S.; Seo, M.-W. Noise Reduction Effect of Multiple-Sampling-Based Signal-Readout Circuits for Ultra-Low Noise CMOS Image Sensors. Sensors 2016, 16, 1867. https://doi.org/10.3390/s16111867

Kawahito S, Seo M-W. Noise Reduction Effect of Multiple-Sampling-Based Signal-Readout Circuits for Ultra-Low Noise CMOS Image Sensors. Sensors. 2016; 16(11):1867. https://doi.org/10.3390/s16111867

Chicago/Turabian StyleKawahito, Shoji, and Min-Woong Seo. 2016. "Noise Reduction Effect of Multiple-Sampling-Based Signal-Readout Circuits for Ultra-Low Noise CMOS Image Sensors" Sensors 16, no. 11: 1867. https://doi.org/10.3390/s16111867