Fully Integrated Low-Noise Readout Circuit with Automatic Offset Cancellation Loop for Capacitive Microsensors

Abstract

:1. Introduction

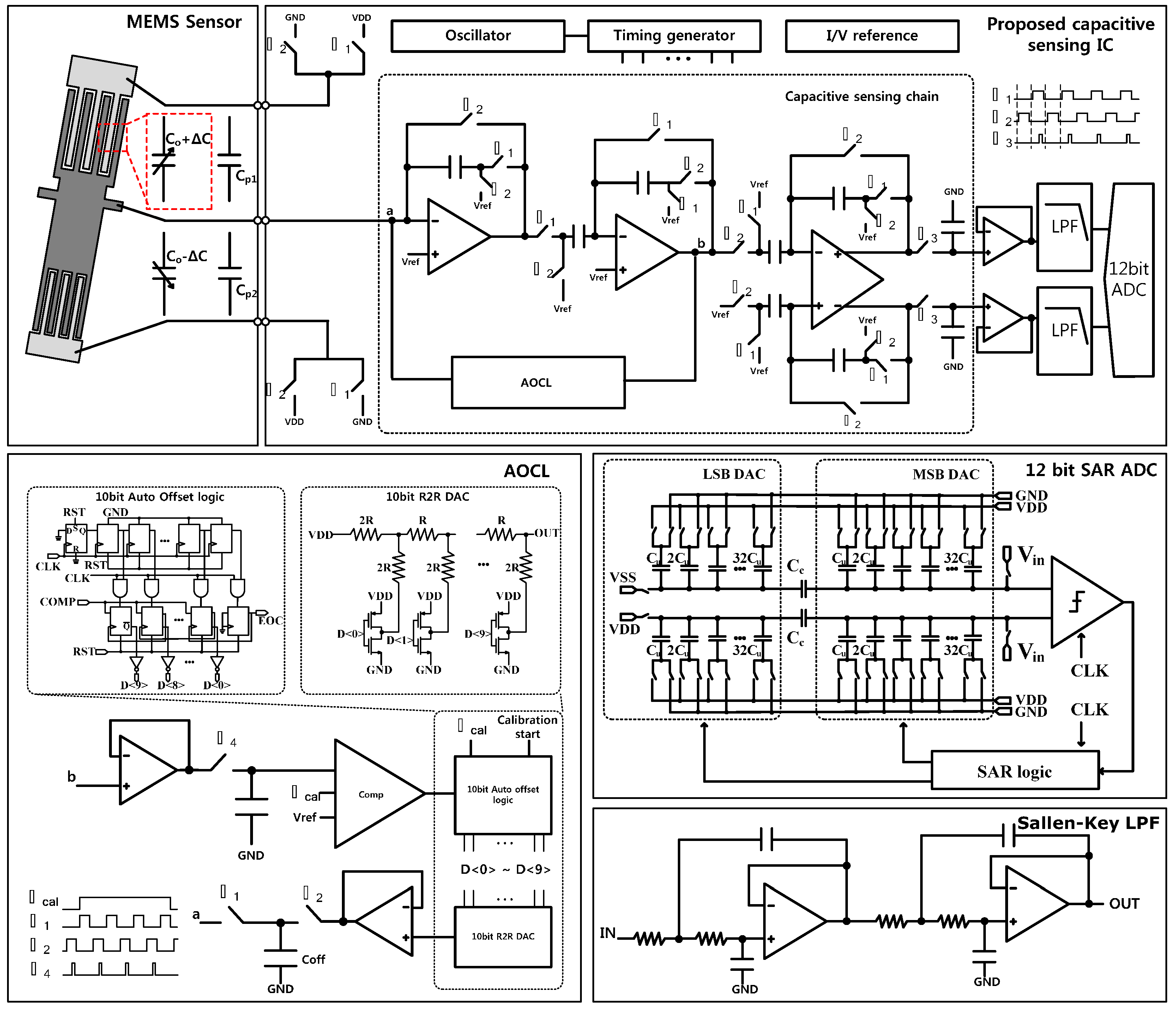

2. Circuit Description

2.1. Top Level Architecture

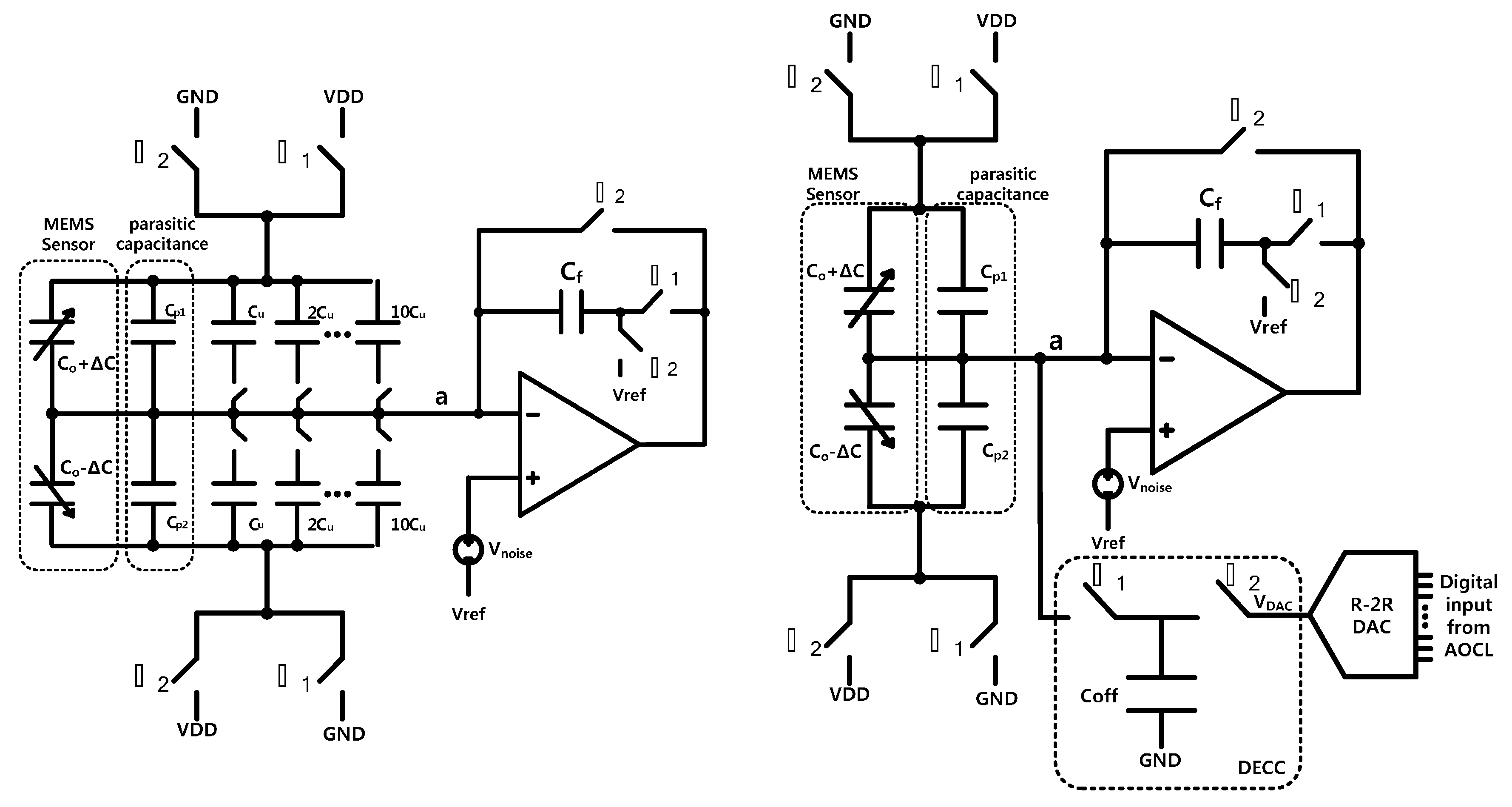

2.2. Capacitive Sensing Amplifier (CSA)

| Capacitor Implementation | Capacitor Arrays Calibration | Charge-Domain Calibration |

|---|---|---|

| Physical Capacitor (MIM or PIP) | Electrically Equivalent Capacitor | |

| Minimum capacitor | Limited by physical design rules (in this design, 16 fF = 4 μm × 4 μm × 1 fF/μm2) | LSB voltage × Coff/VDD (in this design, 0.488 fF = 1/1024 × 3.3/3.3 × 500 fF) |

| Size | Large (binary-weighted capacitor array) | Small (R-2R DAC, switches, and a charge-storing capacitor) |

| DC current | 0 | DC current consumption in R-2R DAC (1.2 μA in this design) |

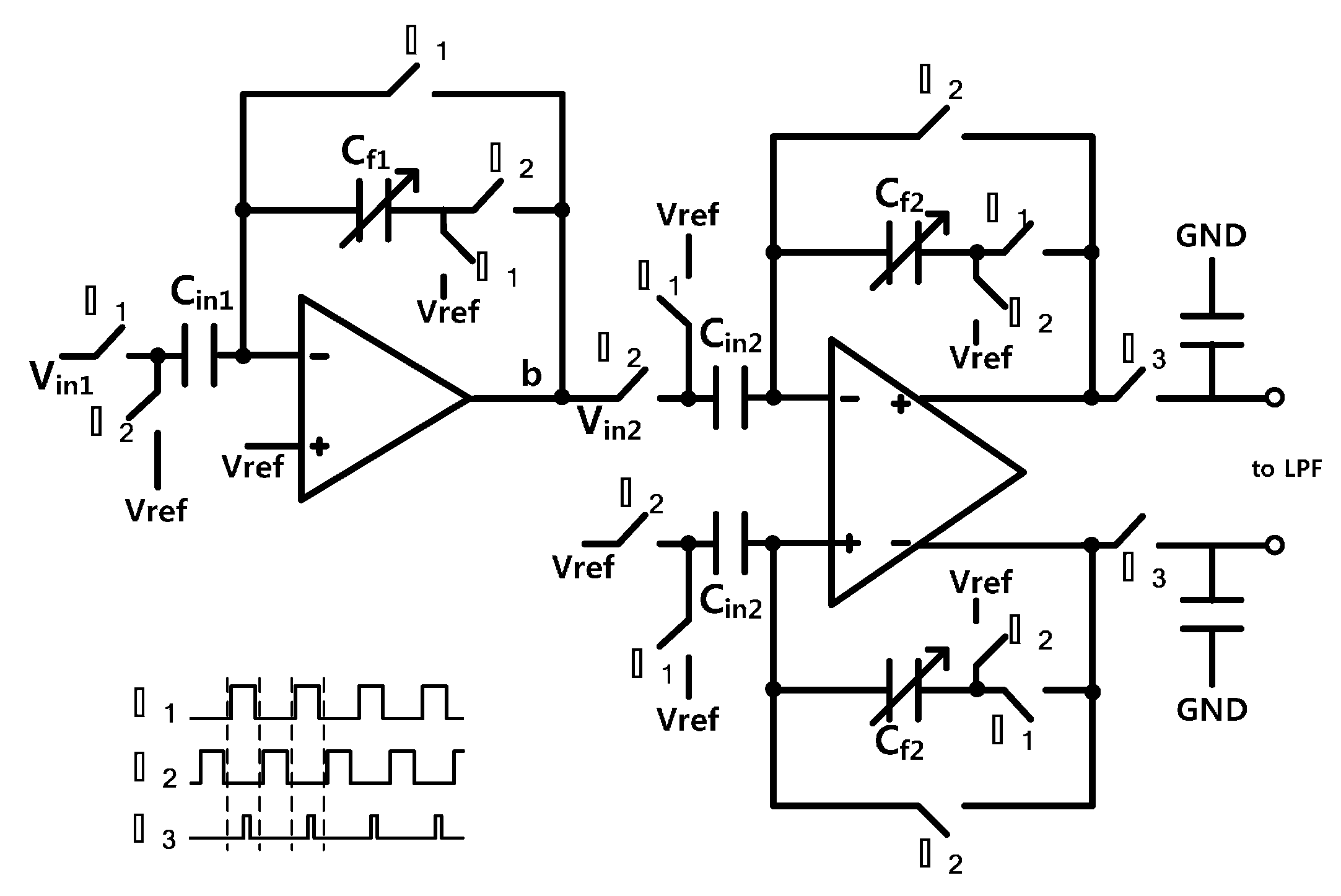

2.3. Programmable Gain Amplifier (PGA) and Single-to-Differential Amplifier (SDA)

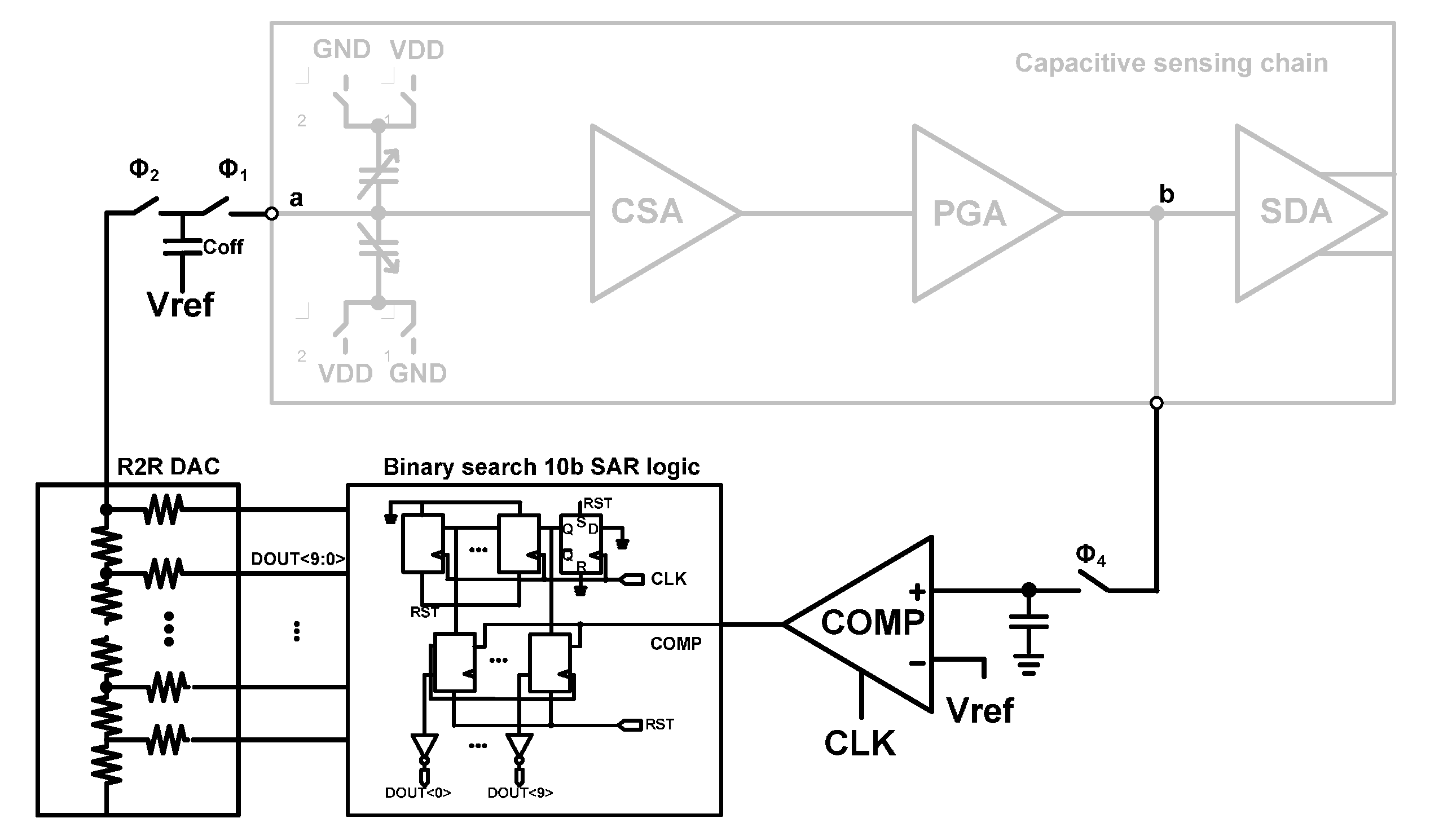

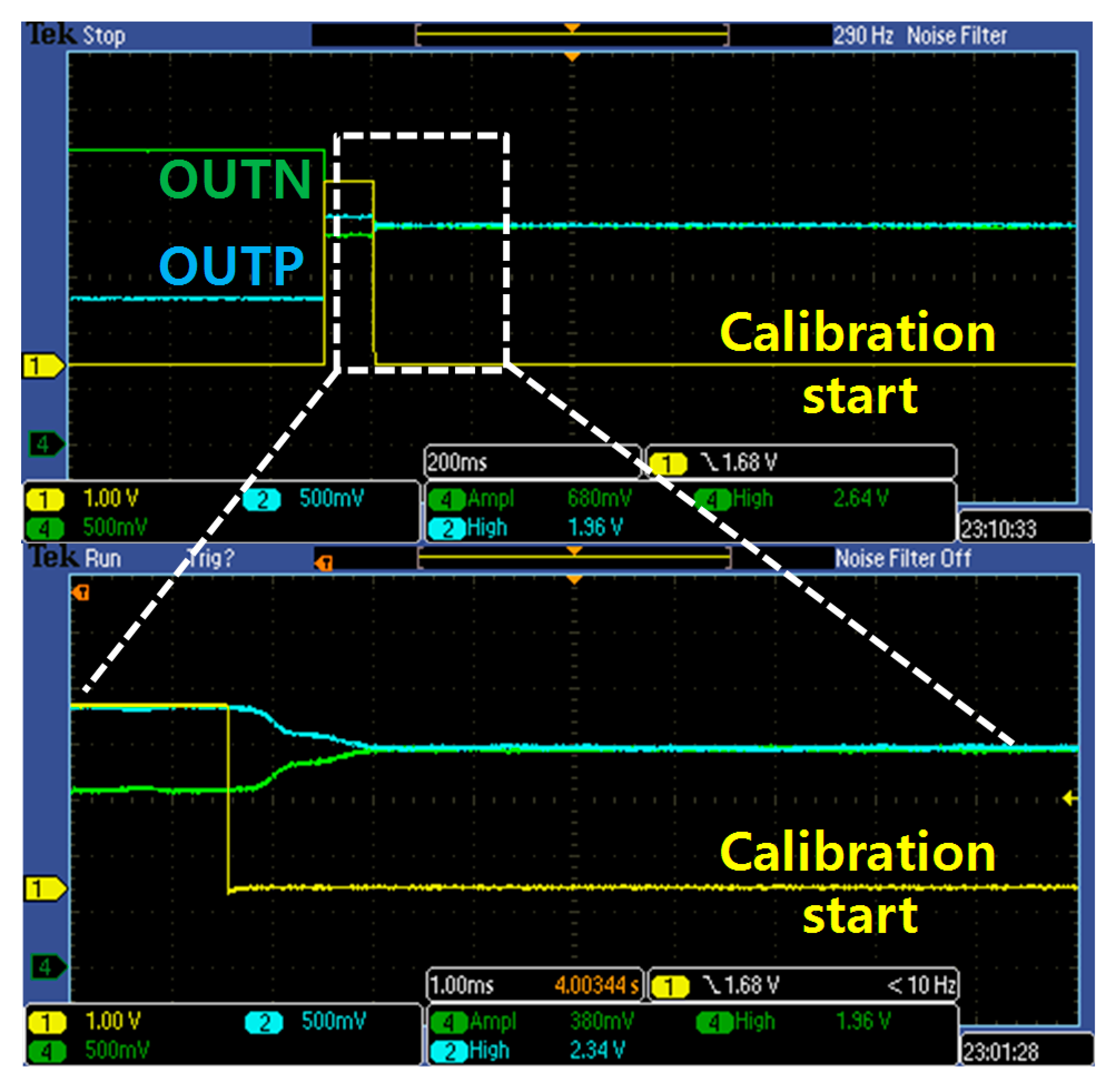

2.4. Automatic Offset Cancellation Loop (AOCL)

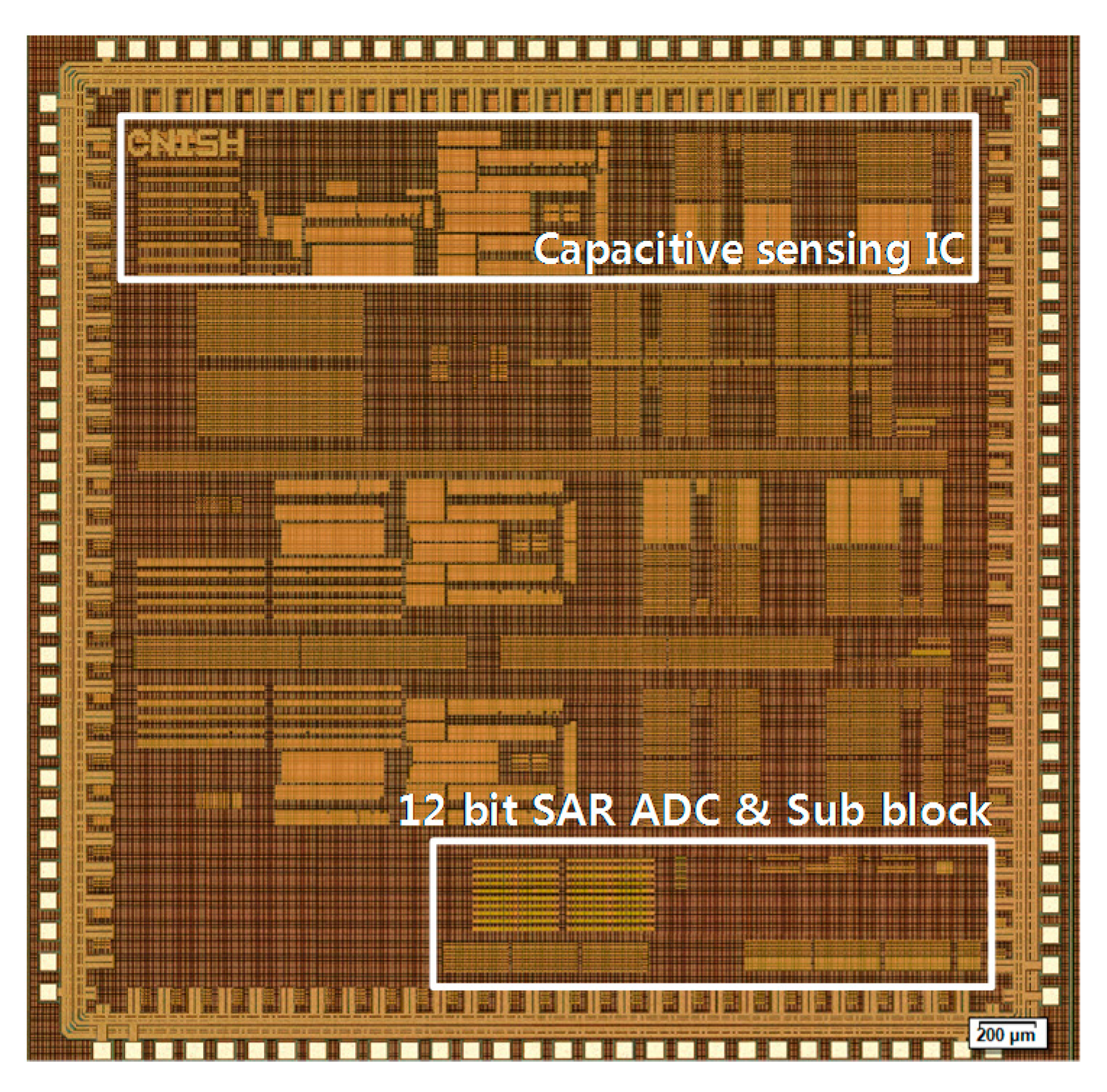

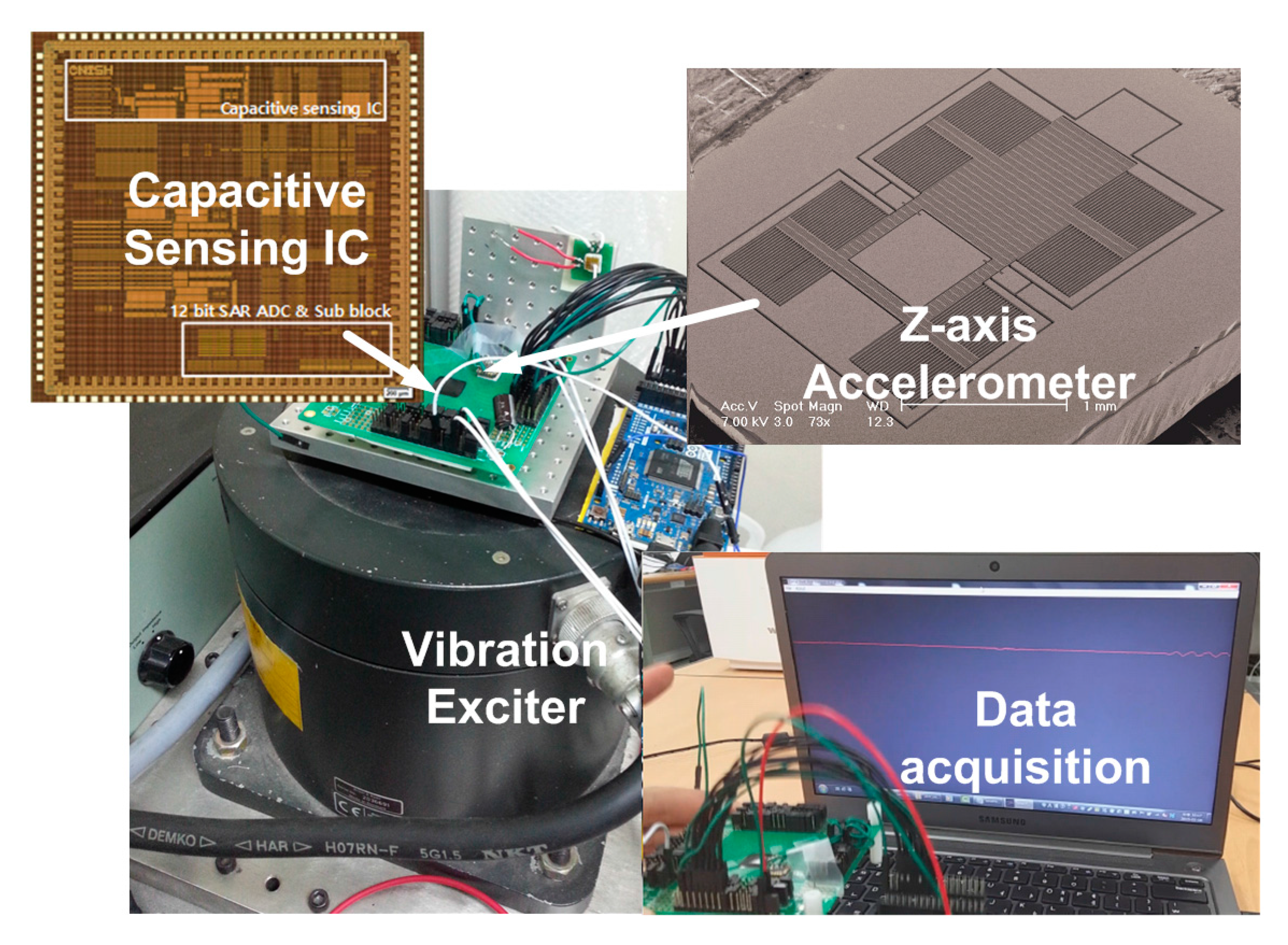

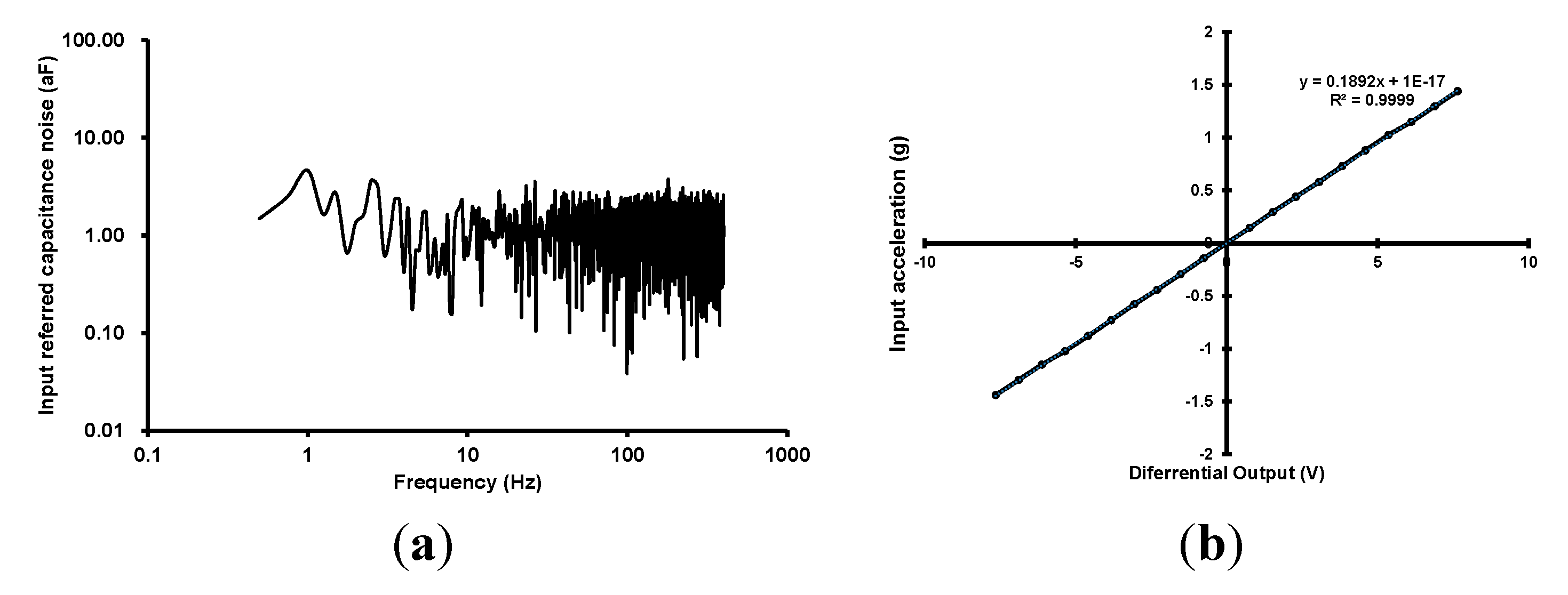

3. Measurement Results

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Sun, H.; Fang, D.; Jia, K.; Maarouf, F.; Qu, H.; Xie, H. A low-power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. IEEE Sens. J. 2011, 11, 925–633. [Google Scholar] [CrossRef]

- Tez, S.; Akin, T. Fabrication of a Sandwich Type Three Axis Capacitive MEMS Accelerometer. In Proceedings of the IEEE Sensors, Baltimore, MD, USA, 3–6 November 2013; pp. 1–4.

- Yu, H.Y.; Qin, M.; Huang, J.Q.; Huang, Q.A. A MEMS Capacitive Pressure Sensor Compatible with CMOS Process. In Proceedings of the IEEE Sensors, Taipei, Taiwan, 28–31 October 2012; pp. 1–4.

- Tan, Z.; Shalmany, S.H.; Meijer, G.; Pertijs, M.A. An energy-efficient 15-bit capacitive-sensor interface based on period modulation. IEEE J. Solid-State Circ. 2012, 47, 1703–1711. [Google Scholar] [CrossRef]

- Dobrzynska, J.A.; Gijs, M.A.M. Polymer-based flexible capacitive sensor for three-axial force measurements. J. Micromech. Microeng. 2013, 23, 1–11. [Google Scholar]

- Yole Developpement & System Plus Consulting, Inertial MEMS Manufacturing Trends 2014. Available online: http:// www.systemplus.fr/reverse-costing-reports/inertial-mems-inertial-mems-manufacturing-trends-2014-volumes-1-2 (accessed on 10 October 2015).

- Shin, D.; Lee, H.; Kim, S. Delta–sigma interface circuit for capacitive sensors with an automatically calibrated zero point. IEEE Trans. Circuits Syst. II Exp. Briefs. 2011, 58, 90–94. [Google Scholar] [CrossRef]

- Kim, G.; Seok, C.; Kim, T.; Park, J.H.; Kim, H.; Ko, H. The Micro Pirani Gauge with Low Noise CDS-CTIA for In-Situ Vacuum Monitoring. J. Semicond. Tech. Sci. 2014, 14, 733–740. [Google Scholar] [CrossRef]

- Ha, H.; Suh, Y.; Lee, S.; Park, H.; Sim, J. A 0.5-V, 11.3-μW, 1-kS/s Resistive Sensor Interface Circuit with Correlated Double Sampling. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 9–12 September 2012; pp. 1–4.

- Perenzoni, M.; Massari, N.; Stoppa, D.; Pancheri, L.; Malfatti, M.; Gonzo, L. A 160 by 120-pixels range camera with in-pixel correlated double sampling and fixed-pattern noise correction. IEEE J. Solid-State Circ. 2011, 46, 1672–1681. [Google Scholar] [CrossRef]

- Wong, S.; Chio, U.; Zhu, Y.; Sin, S.; Seng-Pan, U.; Martins, R. A 2.3 mW 10-bit 170 MS/s two-step binary-search assisted time-interleaved SAR ADC. IEEE J. Solid-State Circ. 2013, 48, 1783–1794. [Google Scholar] [CrossRef]

- Zhand, D.; Bhide, A.; Alvandpour, A. A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-m CMOS for medical implant devices. IEEE J. Solid-State Circ. 2012, 47, 1585–1593. [Google Scholar]

- Ouh, H.K.; Choi, J.; Lee, J.; Han, S.; Kim, S.; Seo, J.; Ko, H. Capacitive Readout Circuit for Tri-axes Microaccelerometer with Sub-fF Offset Calibration. J. Semicond. Tech. Sci. 2014, 14, 83–91. [Google Scholar] [CrossRef]

- Lee, S.; Ko, H.; Choi, B.; Cho, D. Optimal and robust design method for two-chip out-of-plane microaccelerometers. Sensors 2010, 10, 10524–10544. [Google Scholar] [CrossRef] [PubMed]

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Song, H.; Park, Y.; Kim, H.; Cho, D.-i.D.; Ko, H. Fully Integrated Low-Noise Readout Circuit with Automatic Offset Cancellation Loop for Capacitive Microsensors. Sensors 2015, 15, 26009-26017. https://doi.org/10.3390/s151026009

Song H, Park Y, Kim H, Cho D-iD, Ko H. Fully Integrated Low-Noise Readout Circuit with Automatic Offset Cancellation Loop for Capacitive Microsensors. Sensors. 2015; 15(10):26009-26017. https://doi.org/10.3390/s151026009

Chicago/Turabian StyleSong, Haryong, Yunjong Park, Hyungseup Kim, Dong-il Dan Cho, and Hyoungho Ko. 2015. "Fully Integrated Low-Noise Readout Circuit with Automatic Offset Cancellation Loop for Capacitive Microsensors" Sensors 15, no. 10: 26009-26017. https://doi.org/10.3390/s151026009

APA StyleSong, H., Park, Y., Kim, H., Cho, D.-i. D., & Ko, H. (2015). Fully Integrated Low-Noise Readout Circuit with Automatic Offset Cancellation Loop for Capacitive Microsensors. Sensors, 15(10), 26009-26017. https://doi.org/10.3390/s151026009