CRM PFC Converter with New Valley Detection Method for Improving Power System Quality

Abstract

:1. Introduction

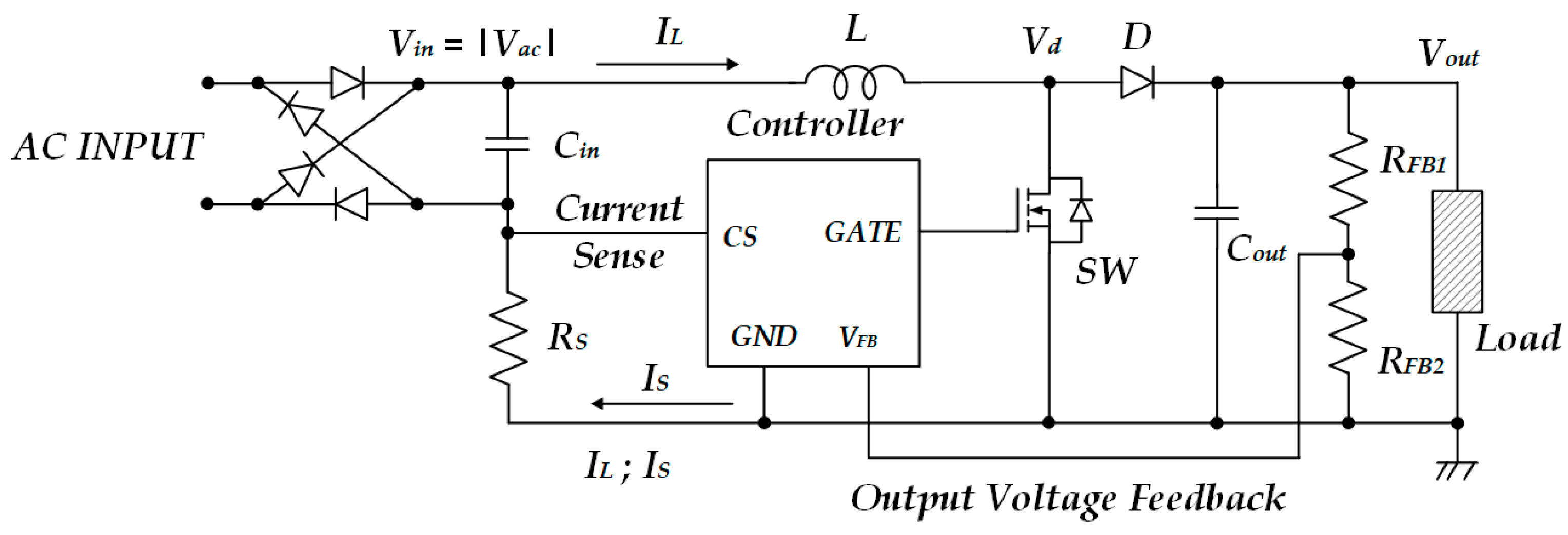

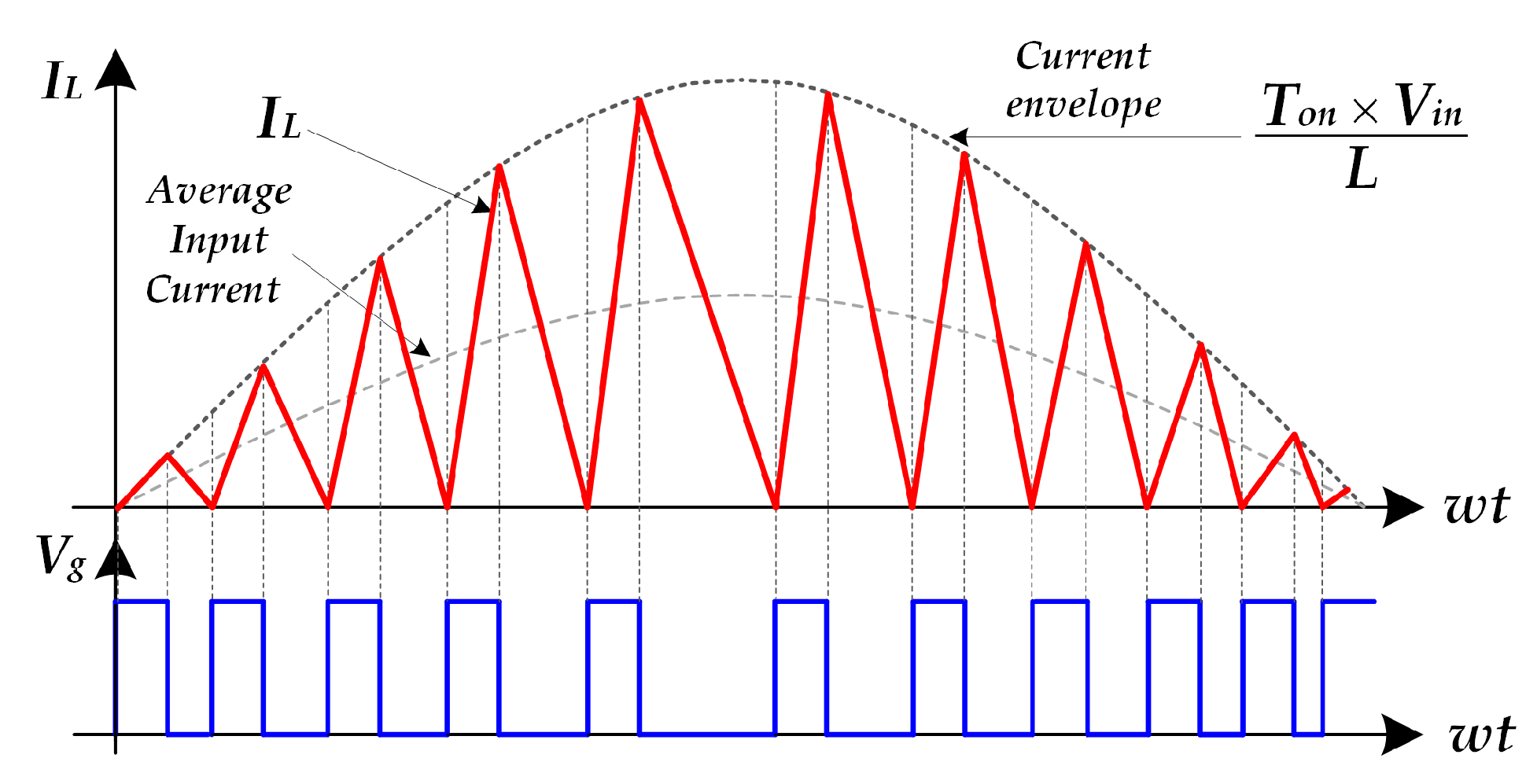

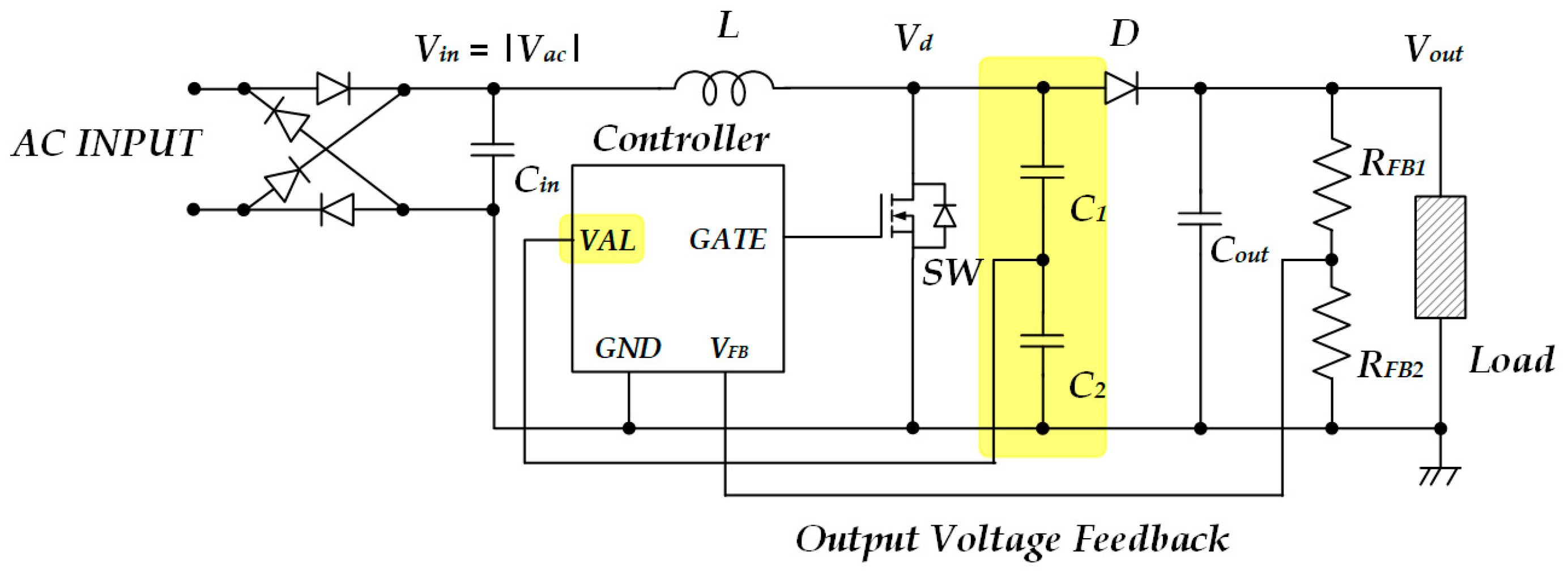

2. Description for Conventional CRM boost PFC

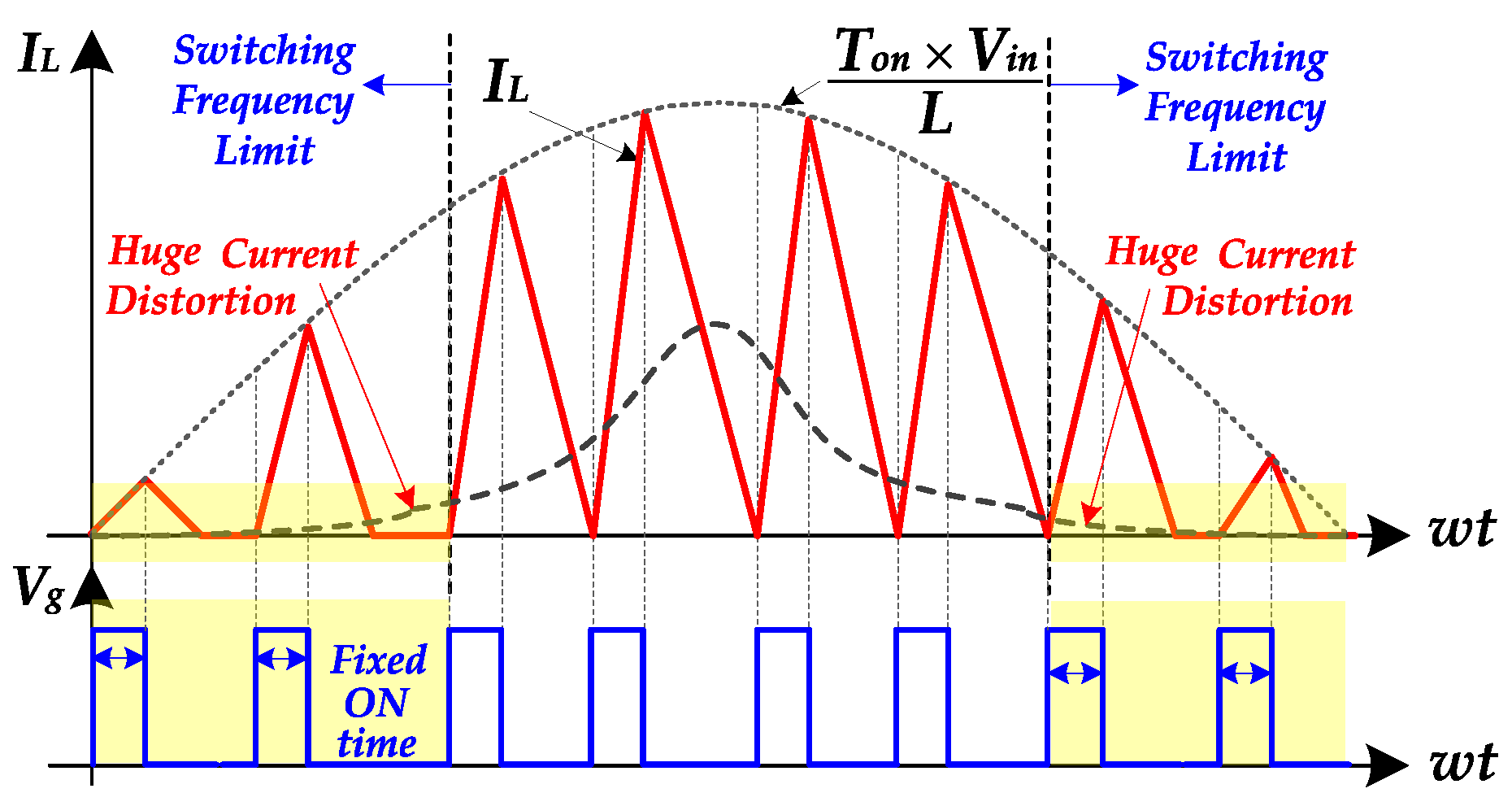

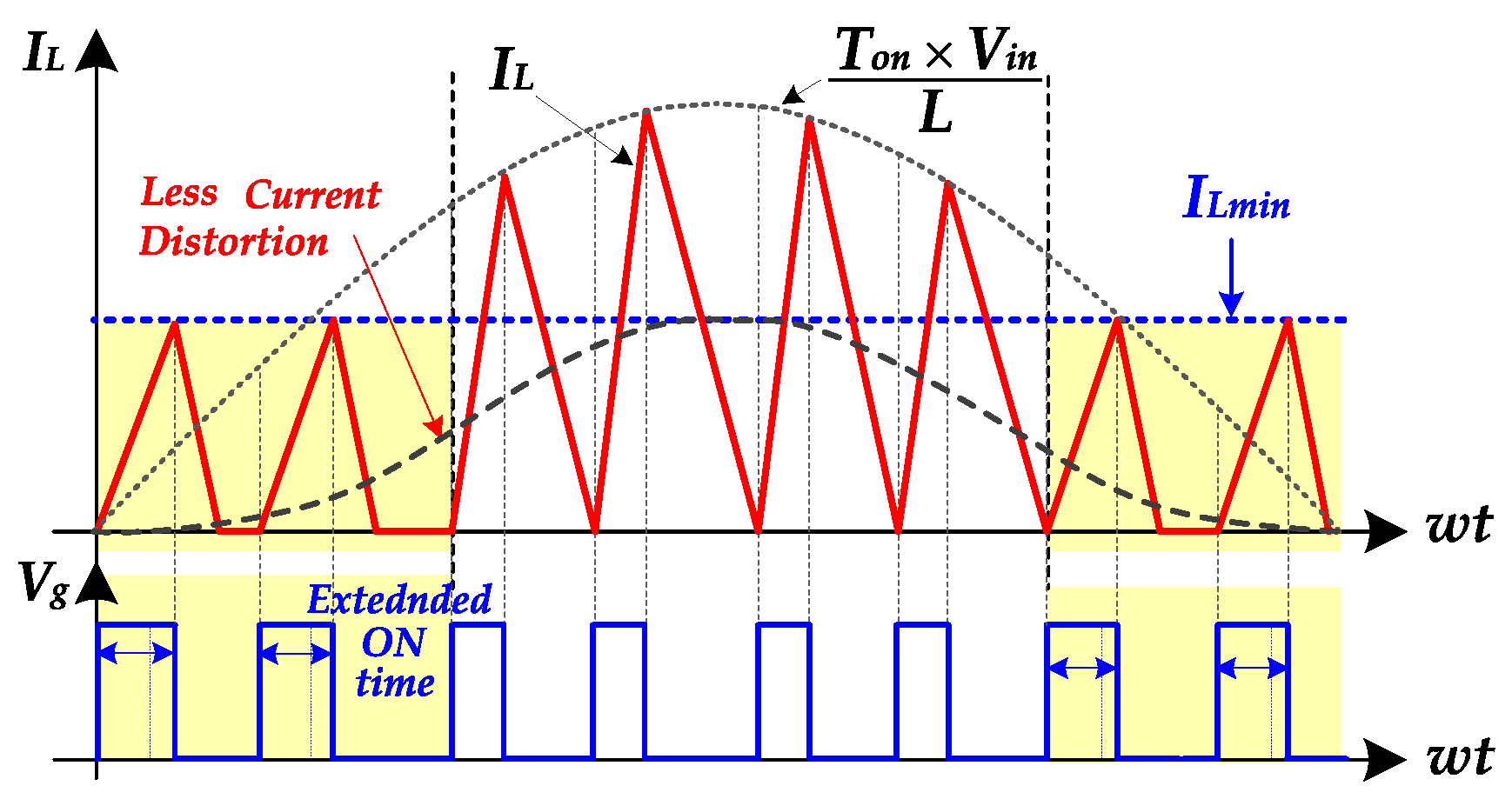

2.1. Switching Frequency Limit Method

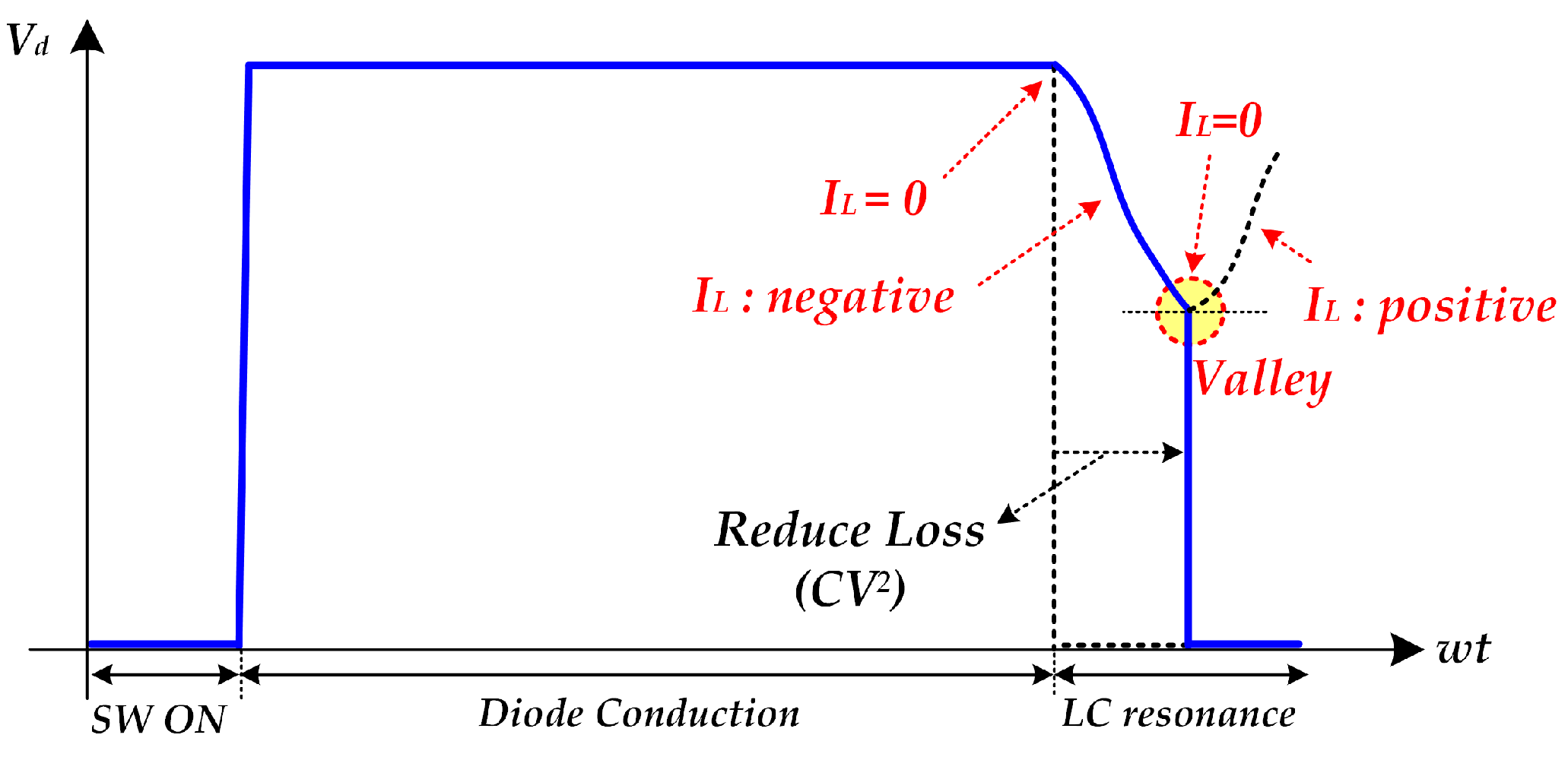

2.2. Existing Valley Switching Method

3. Proposed Valley Detection Strategies with ON-Time Extension

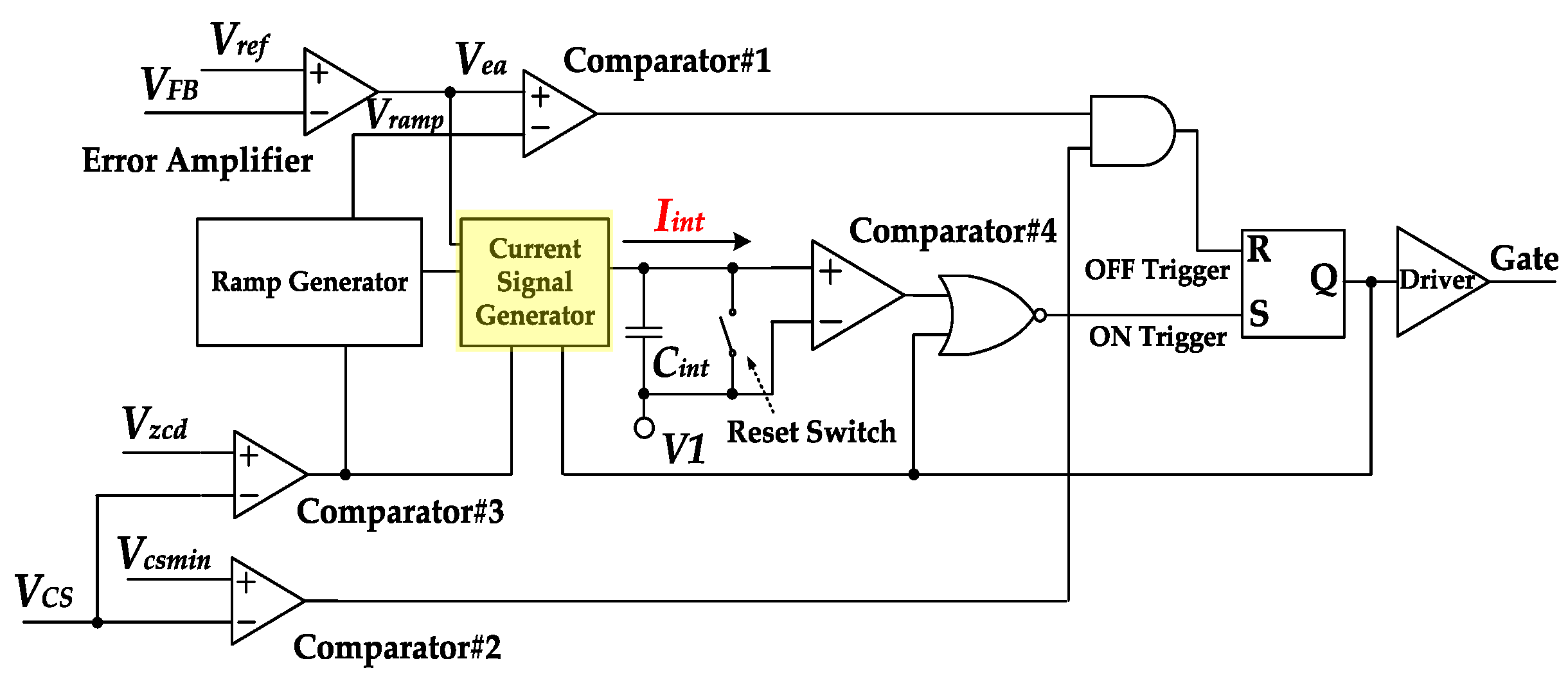

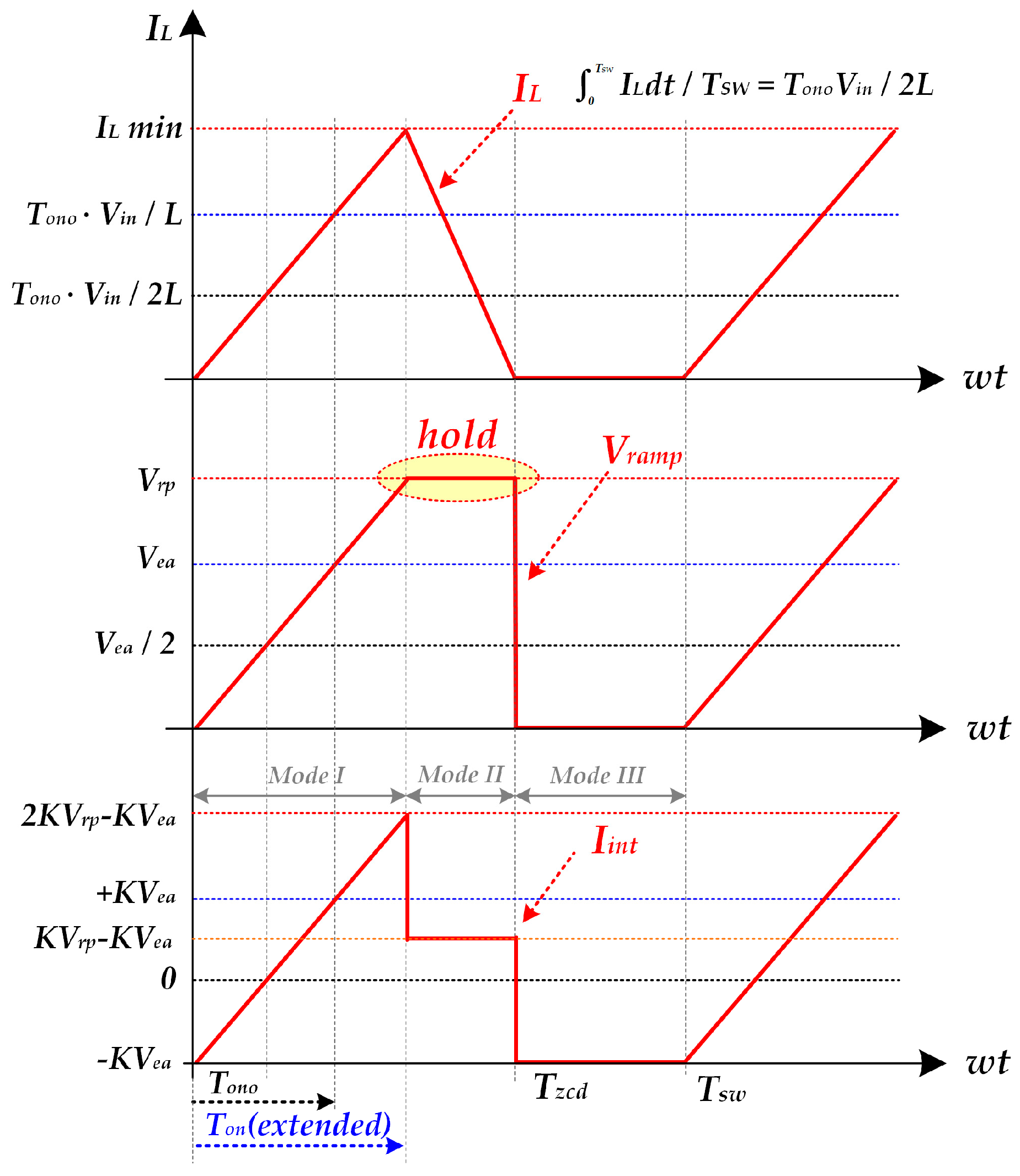

3.1. Realization of Proposed Method

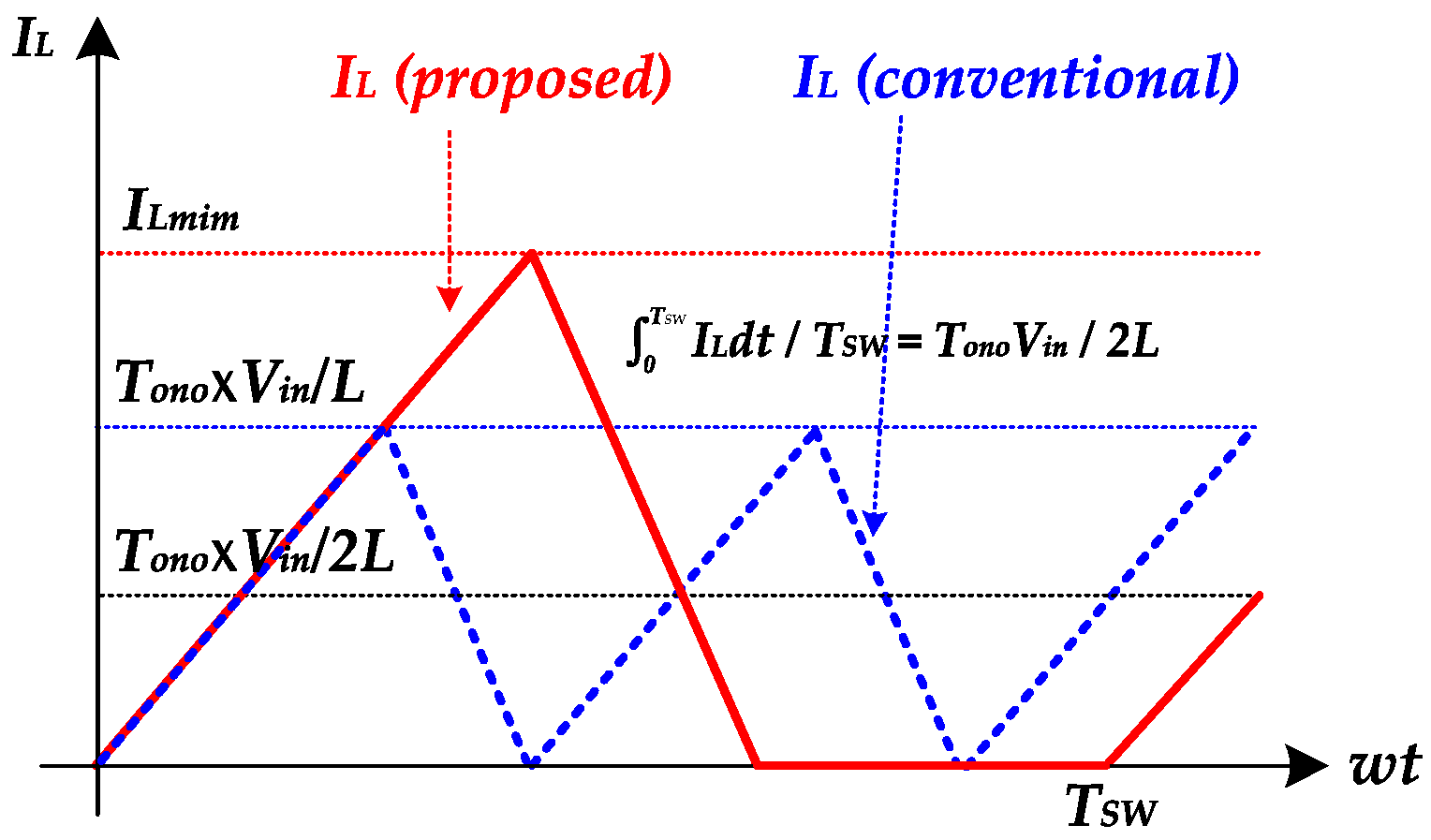

3.2. Description of ON-Time Extension

4. Circuit Implementations and Design Considerations

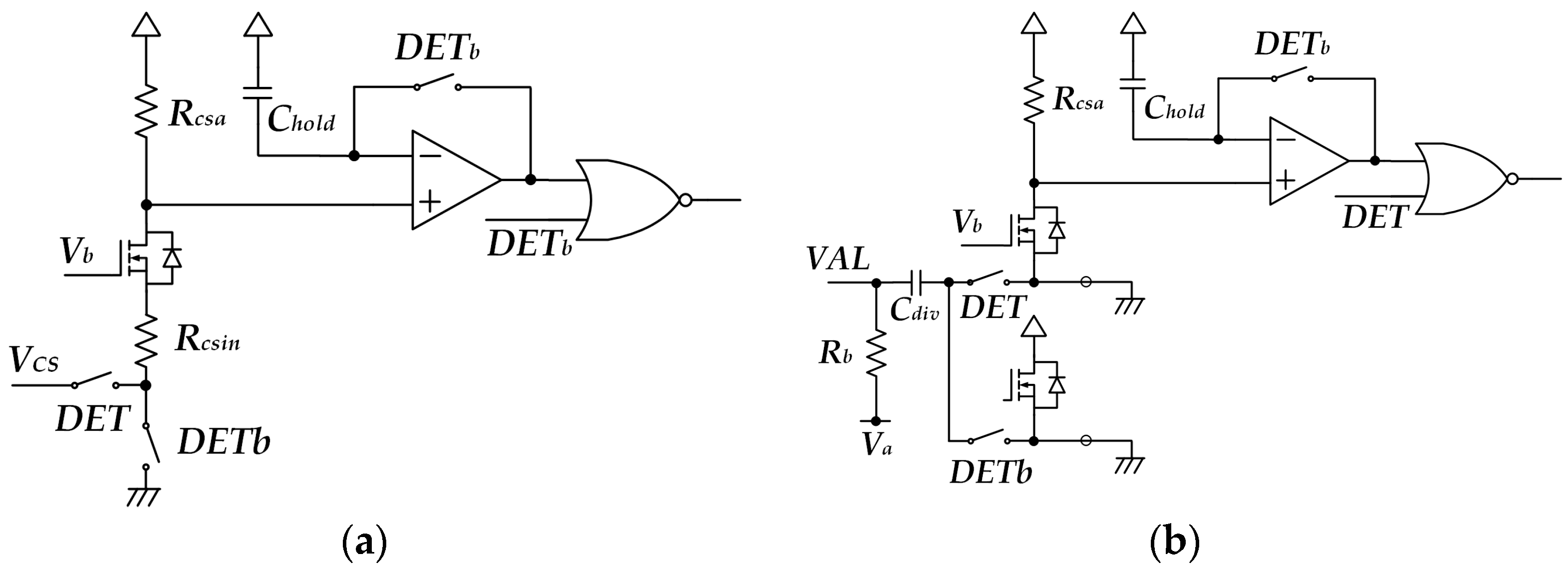

4.1. Proposed Valley Detect Method with Current Sense Voltage

4.2. Proposed Valley Detect Method with Divided Drain Voltage

5. Simulation and Experimental Results

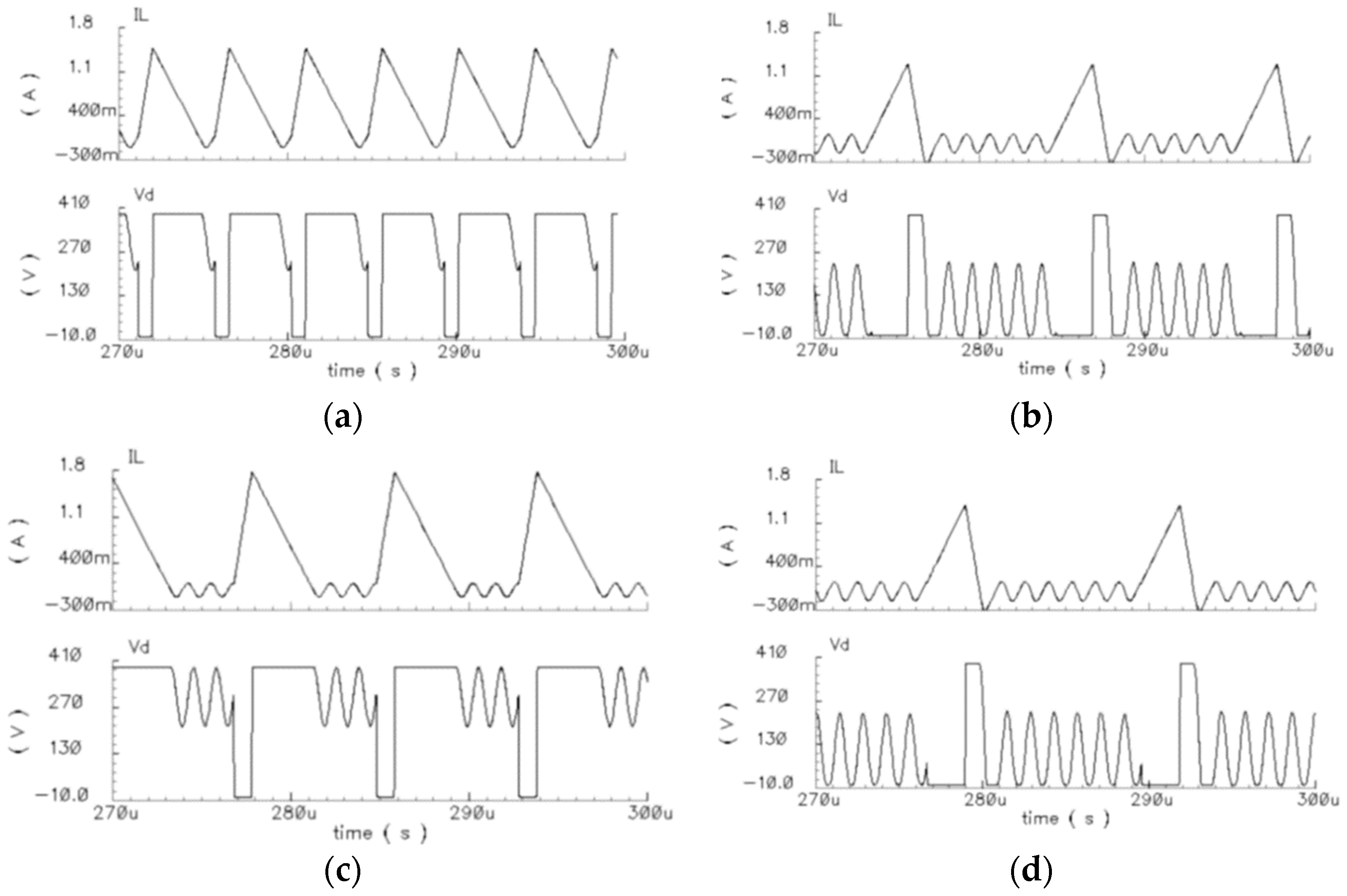

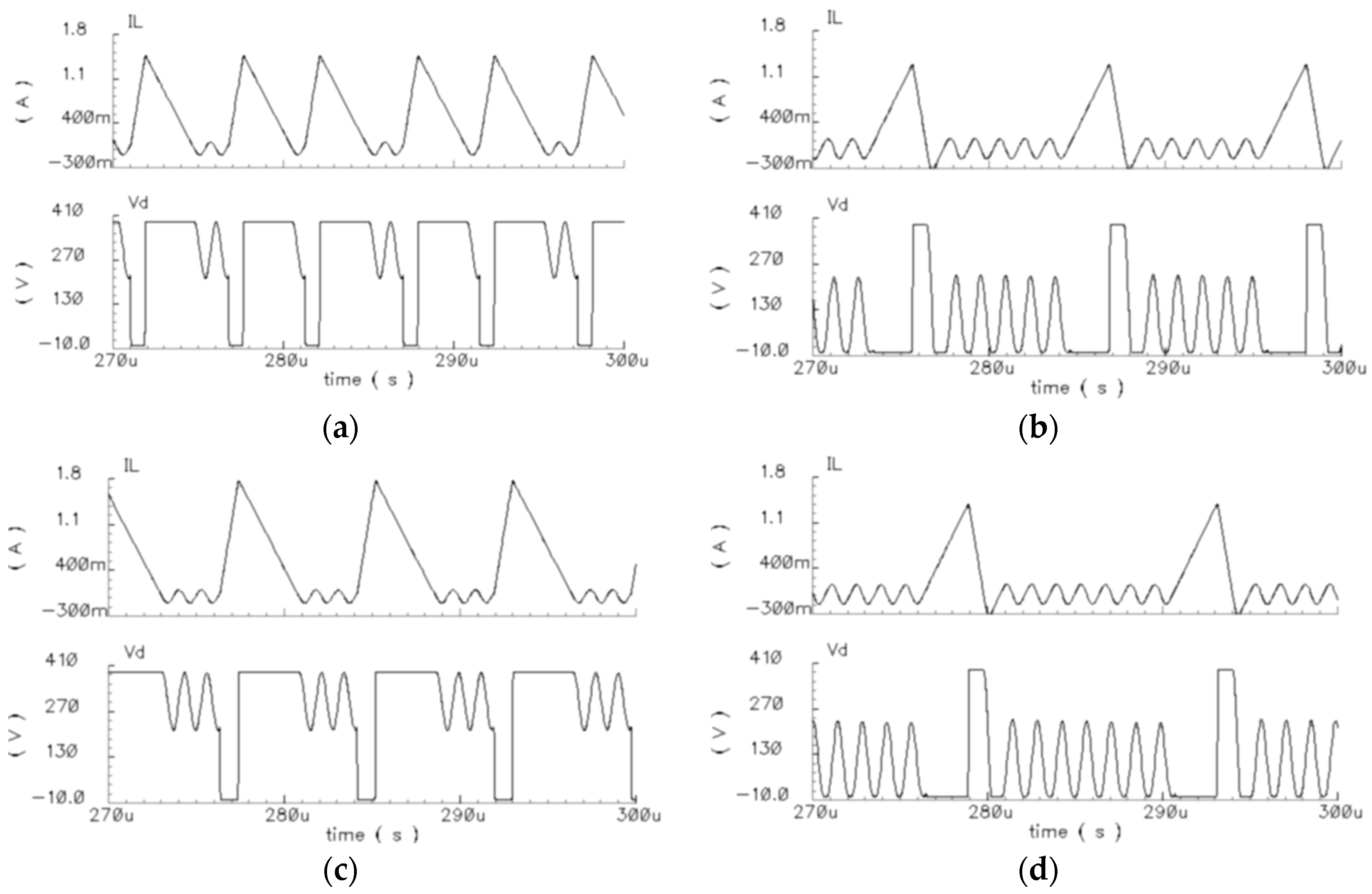

5.1. Simualtion Results

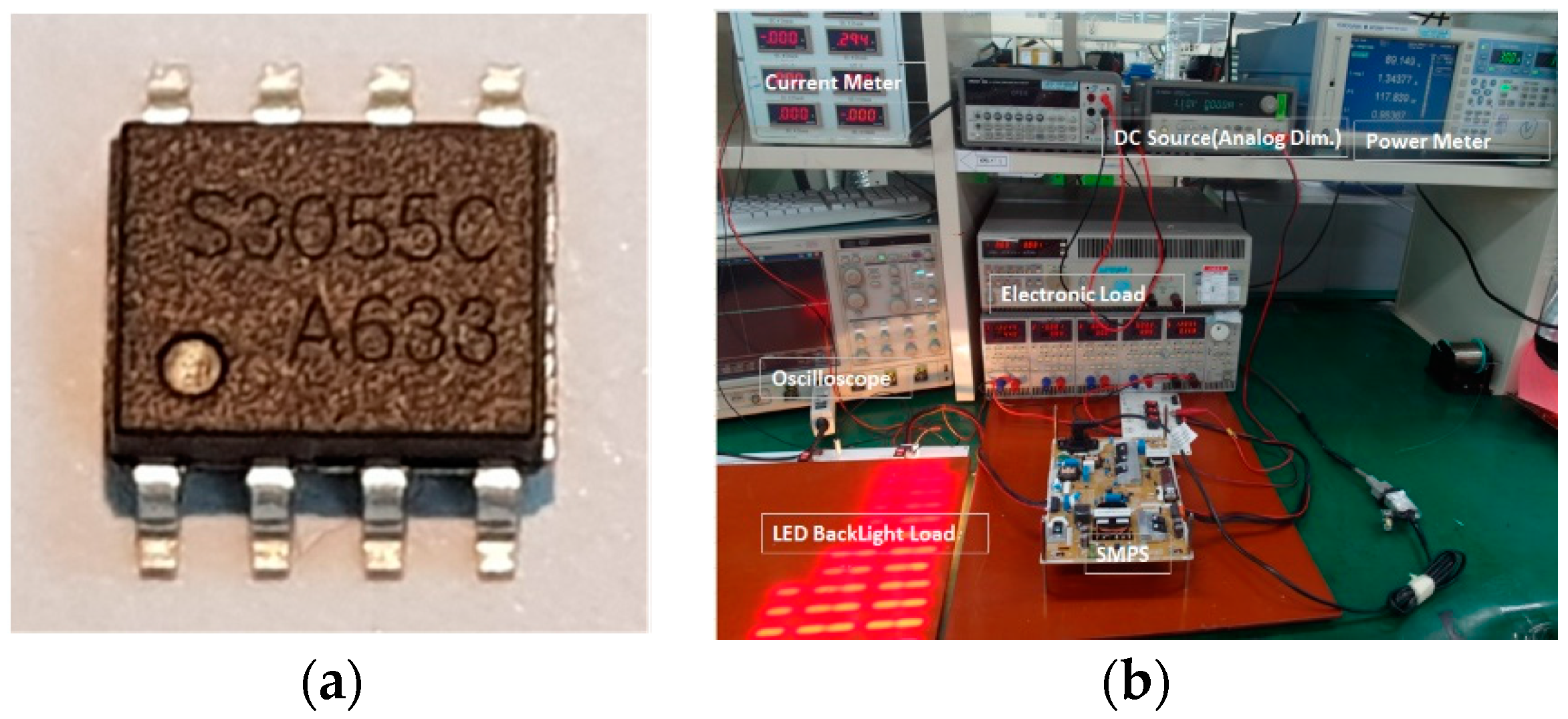

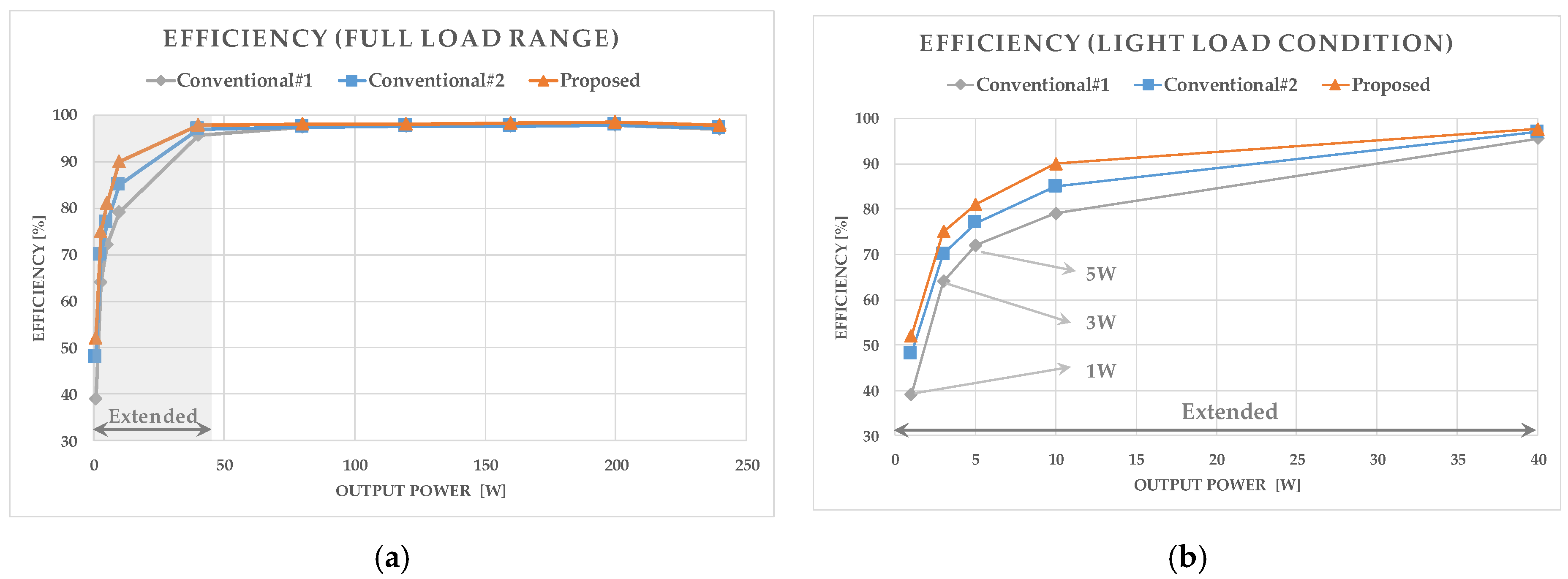

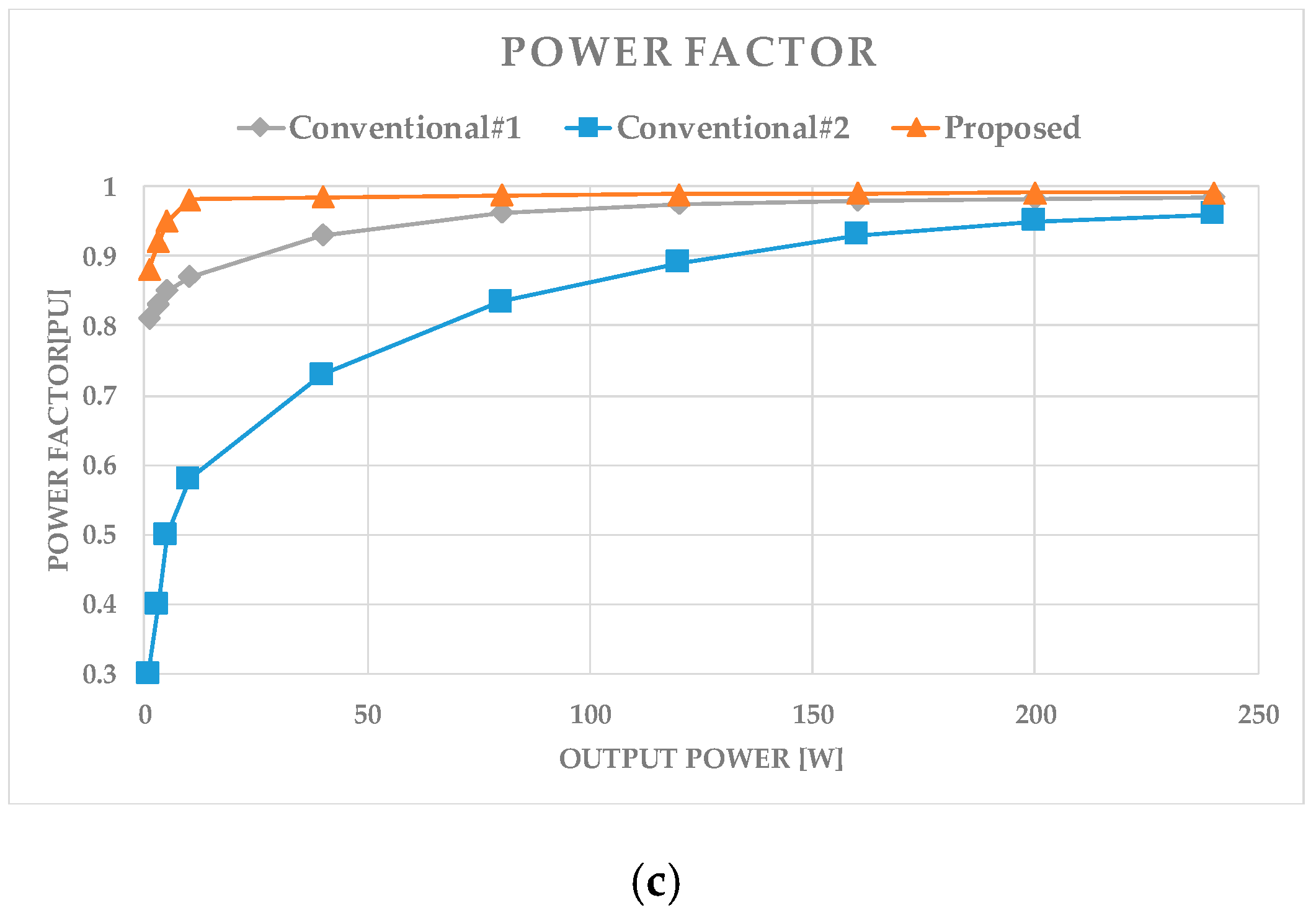

5.2. Experimental Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| Coss | Drain–source parasitic capacitance of the switch |

| CRM | Critical mode |

| IL | Inductor current |

| Iint | Signal generator generates an output current |

| K | Constant value |

| LC | Inductance and capacitance |

| MOSFET | Metal oxide semiconductor field effect transistor |

| PFC | Power factor correction |

| SMPS | Switch mode power supply |

| Ton | Switch ON-time |

| Tono | ON-time before it is extended |

| Tsw | Switching period |

| Tzcd | Inductor current returns to zero |

| Vcs | Current sense voltage |

| Vcsmin | Minimum level of the inductor current |

| Vds | Drain–source voltage of the switch |

| Vea | Generates an output voltage |

| VFB | Voltage feedback signal |

| Vin | Input voltage |

| Vout | Output voltage |

| Vramp | Ramp signal voltage |

| Vref | Reference voltage |

| VVAL | Differentiation of the divided voltage |

References

- Erickson, R.W.; Maksimovic, D. Line-Commutated Rectifier. In Fundamental of Power Electronics, 2nd ed.; Springer: New York, NY, USA, 2001; pp. 609–630. ISBN 978-0-7923-7270-7. [Google Scholar]

- Lai, J.; Chen, D. Design consideration for power factor correction boost converter operating at the boundary of continuous conduction mode. In Proceedings of the 1993 Eighth Annual IEEE Applied Power Electronics Conference and Exposition, San Diego, CA, USA, 7–11 March 1993; pp. 267–273. [Google Scholar]

- Buso, S.; Mattavelli, P.; Rossetto, L.; Spiazzi, G. Simple digital control improving dynamic performance of power factor pre regulators. IEEE Trans. Power Electron. 1998, 13, 814–823. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanovic, M.M. Light-load efficiency optimization method. IEEE Trans. Power Electron. 2010, 25, 67–74. [Google Scholar] [CrossRef]

- Li, Q.; Lee, F.C.; Xu, M.; Wang, C. Light-load efficiency improvement for PFC. In Proceedings of the 2009 Annual IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 3755–3760. [Google Scholar]

- Lee, F.C.; Xu, M.; Wang, S.; Lu, B. Topologies and design considerations for distributed power system applications. Proc. IEEE 2001, 89, 939–950. [Google Scholar] [CrossRef]

- Zhang, Z.; Yao, K.; Ma, C.; Chen, J.; Li, L.; Guan, C.; Wu, C. All-Fixed Switching Frequency Control of CRM Boost PFC Converter based on Variable Inductor in a Wide Input Voltage Range. In Proceedings of the 2019 Annual IEEE Energy Conversion Congress and Exposition, Baltimore, MD, USA, 29 September–3 October 2019; pp. 1434–1441. [Google Scholar]

- Yoa, K.; Wang, Y.; Guo, J.; Chen, K. Critical Conduction Mode Boost PFC Converter With Fixed Switching Frequency Control. IEEE Trans. Power Electron. 2018, 33, 6845–6857. [Google Scholar]

- Ma, C.; Yao, K.; Wu, C.; Chen, J.; Li, L.; Guan, C.; Zhang, Z. Optimal Dual Constant Switching Frequency Control for CRM Buck-Buck/Boost PFC Converter. In Proceedings of the 2019 Annual IEEE Energy Conversion Congress and Exposition, Baltimore, MD, USA, 29 September–3 October 2019; pp. 1459–1465. [Google Scholar]

- Ye, Z.; Sun, B. PFC efficiency improvement and THD reduction at light loads with ZVS and valley switching. In Proceedings of the 2012 Annual IEEE Applied Power Electronics Conference and Exposition, Orlando, FL, USA, 2–5 February 2012; pp. 802–806. [Google Scholar]

- Jiang, C.; Nene, H.; Choudhury, S. Efficiency and THD Optimization Based on an Interleaved PFC Converter Using Digital Controller with Integrated Valley Switching Control Feature. In Proceedings of the 2019 IEEE Texas Power and Energy Conference, College Station, TX, USA, 7–8 February 2019; pp. 1–5. [Google Scholar]

- Nene, H.; Jiang, C.; Choudhury, S. Digital controller with integrated valley switching control for light load efficiency and THD improvements in PFC converter. In Proceedings of the 2017 Annual IEEE Applied Power Electronics Conference and Exposition, Tampa, FL, USA, 26–30 March 2017; pp. 1785–1788. [Google Scholar]

- Cheng, W.; Chen, C. A zero-current detection circuit with optimal ZVS/VS for boundary mode boost PFC converter. In Proceedings of the 2012 IEEE International Symposium on Industrial Electronics, Hangzhou, China, 28–31 May 2012; pp. 137–142. [Google Scholar]

- Cong, L.; Lee, H. A 2MHz 150-to-400V input isolated DC-DC bus converter with monolithic slope-sensing ZVS detection achieving 13ns turn-on delay and 1.6W power saving. In Proceedings of the 2018 IEEE International Solid—State Circuits Conference, San Francisco, CA, USA, 11–15 February 2018; pp. 382–384. [Google Scholar]

- Ren, X.; Wu, Y.; Guo, Z.; Zhang, Z.; Chen, Q. An online monitoring method of circuit parameters for variable on-time control in CRM boost PFC converters. IEEE Trans. Power Electron. 2019, 34, 1786–1797. [Google Scholar] [CrossRef]

- Ryan, R.T.; Hayes, J.G.; Morrison, R.; Hogan, D. A digital closed-loop control strategy for maintaining the 180° phase shift of an interleaved BCM boost converter for PFC applications. In Proceedings of the 2017 Annual IEEE Energy Conversion Congress and Exposition, Cincinnati, OH, USA, 1–5 October 2017; pp. 4927–4934. [Google Scholar]

- Liu, Z.; Ruan, X.; Yang, Y.; Ye, Z. Interleaved Critical Current Mode Boost PFC Converter with Coupled Inductor. IEEE Trans. Power Electron. 2011, 26, 2404–2413. [Google Scholar]

- Liu, Z.; Huang, Z.; Lee, F.C.; Li, Q. Digital-Based Interleaving Control for GaN-Based MHz CRM Totem-Pole PFC. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 808–814. [Google Scholar] [CrossRef]

- Roh, Y.; Moon, Y.; Park, J.; Yoo, C. A Two-Phase Interleaved Power Factor Correction Boost Converter with a Variation-Tolerant Phase Shifting Technique. IEEE Trans. Power Electron. 2014, 29, 1032–1040. [Google Scholar]

- Hosen, T.; Yanagisawa, K. “FA5590 Series” of 2nd Generation Critical Mode PFC Control ICs. Fuji Electr. 2010, 83, 68–71. Available online: https://www.fujielectric.co.jp/approximately/company/jihou_2010/pdf/83-06/FEJ-83-06-405-2010.pdf (accessed on 7 August 2019).

- Enhanced, High-Efficiency Power Factor Controller, Datasheet NCP1602. Available online: https://www.onsemi.com/pub/Collateral/NCP1602-D.pdf (accessed on 11 December 2019).

- Huber, L.; Irving, B.T.; Jovanovic, M.M. Effect of valley switching and switching-frequency limitation on line-current distortions of DCM/CCM boundary boost PFC converters. IEEE Trans. Power Electron. 2009, 24, 339–347. [Google Scholar] [CrossRef]

- Le, H.P.; Chae, C.S.; Lee, M.C.; Wang, S.W.; Kim, S.I.; Cho, G.-H. Integrated zero-inductor-current detection circuit for step-up DC-DC converters. IET Electron. Lett. 2006, 42, 943–944. [Google Scholar]

- Sivakumar, S.; Natarajan, K.; Gudelewicz, R. Control of power factor correcting boost converter without instantaneous measurement of input current. IEEE Trans. Power Electron. 1995, 10, 435–445. [Google Scholar] [CrossRef]

- Sun, J.; Xu, M.; Ren, Y.; Lee, F.C. Light-load efficiency improvement for buck voltage regulators. IEEE Trans. Power Electron. 2009, 24, 742–751. [Google Scholar]

- Mohammadi, F.; Zheng, C. A Precise SVM Classification Model for Predictions with Missing Data. In Proceedings of the 4th National Conference on Applied Research in Electrical, Mechanical Computer and IT Engineering, Tehran, Iran, 4 October 2018; pp. 3594–3606. [Google Scholar]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cho, K.-S.; Lee, B.-K.; Kim, J.-S. CRM PFC Converter with New Valley Detection Method for Improving Power System Quality. Electronics 2020, 9, 38. https://doi.org/10.3390/electronics9010038

Cho K-S, Lee B-K, Kim J-S. CRM PFC Converter with New Valley Detection Method for Improving Power System Quality. Electronics. 2020; 9(1):38. https://doi.org/10.3390/electronics9010038

Chicago/Turabian StyleCho, Kwang-Seung, Byoung-Kuk Lee, and Jong-Soo Kim. 2020. "CRM PFC Converter with New Valley Detection Method for Improving Power System Quality" Electronics 9, no. 1: 38. https://doi.org/10.3390/electronics9010038