Simulation of 50-nm Gate Graphene Nanoribbon Transistors

Abstract

:1. Introduction

2. Simulation Framework and GNR Models

2.1. Models for Bangap and Carrier Effective Mass

2.2. Transport Model

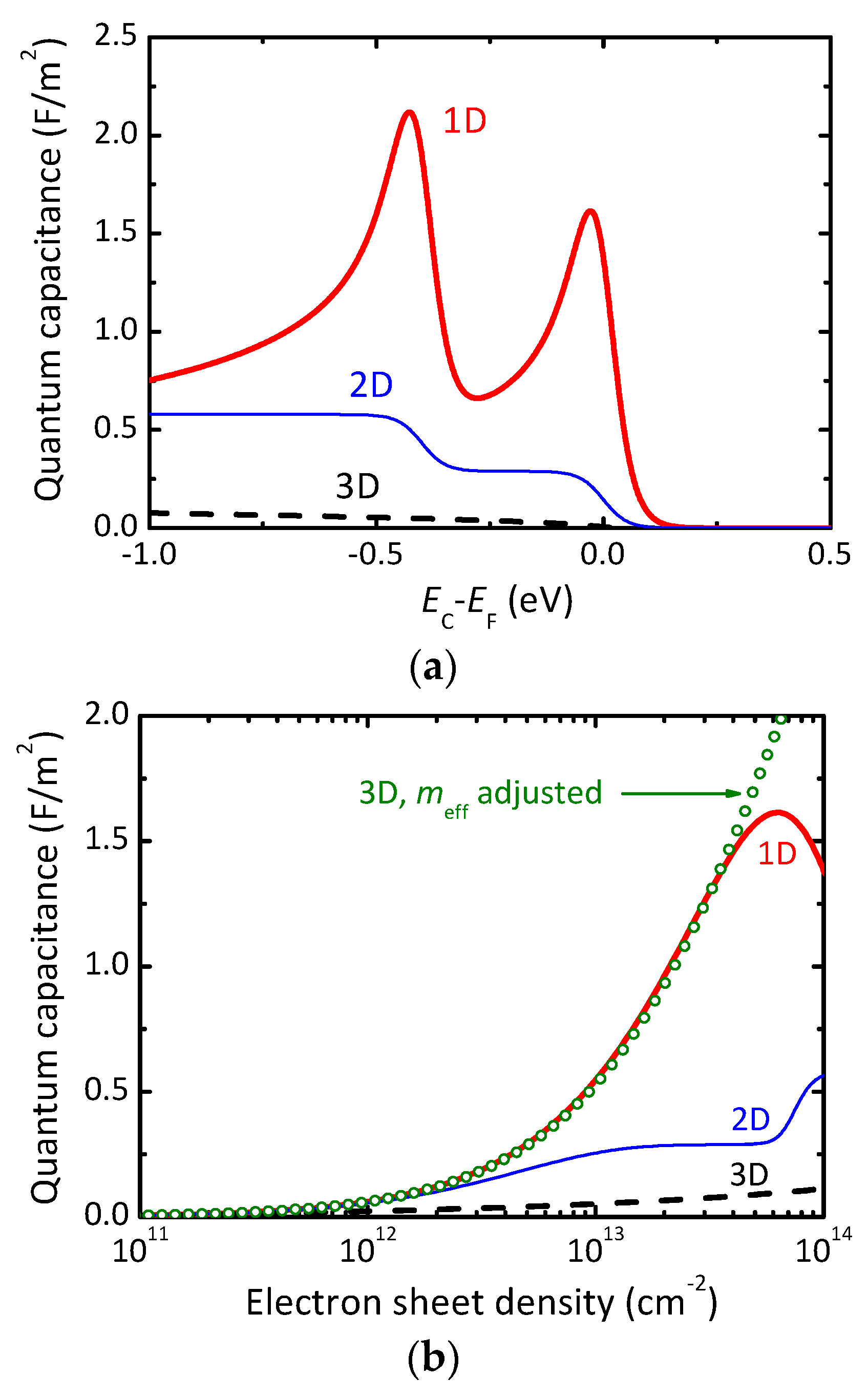

2.3. Modeling the Density of States and Quantum Capacitance of 1D Systems

3. Simulated Transistor Structures, Simulation Results, and Discussion

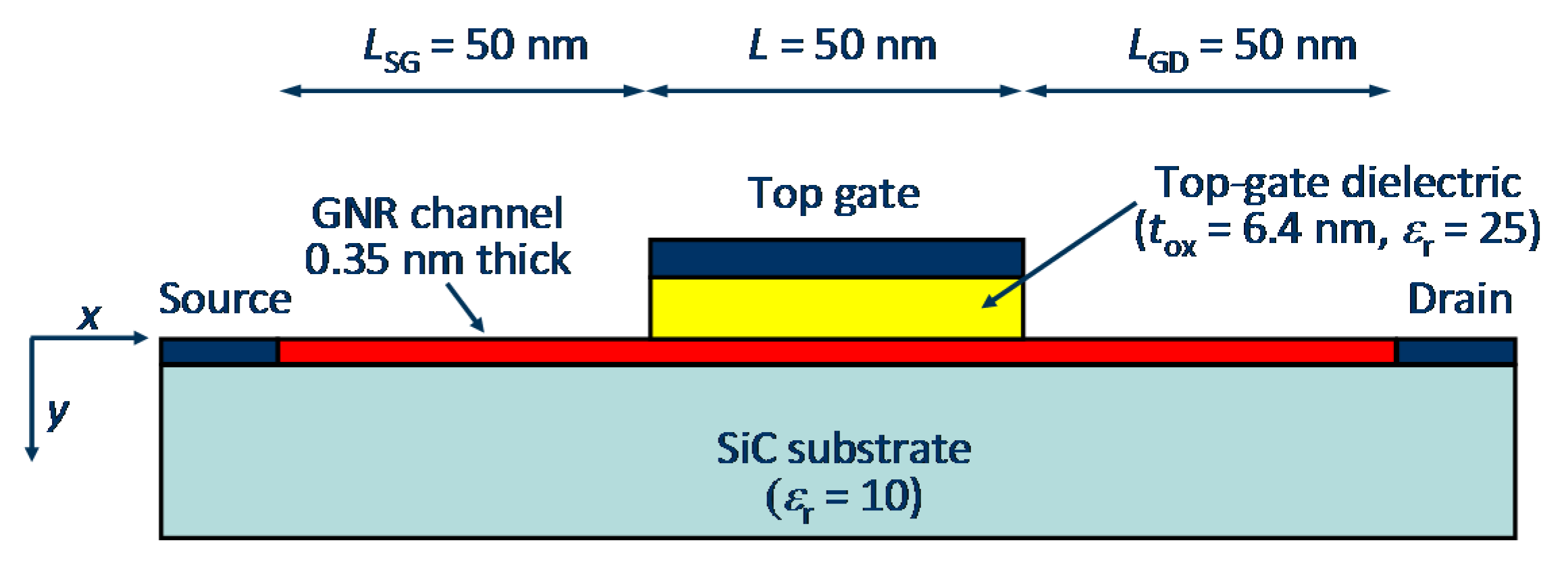

3.1. Simulated Transistor Structures

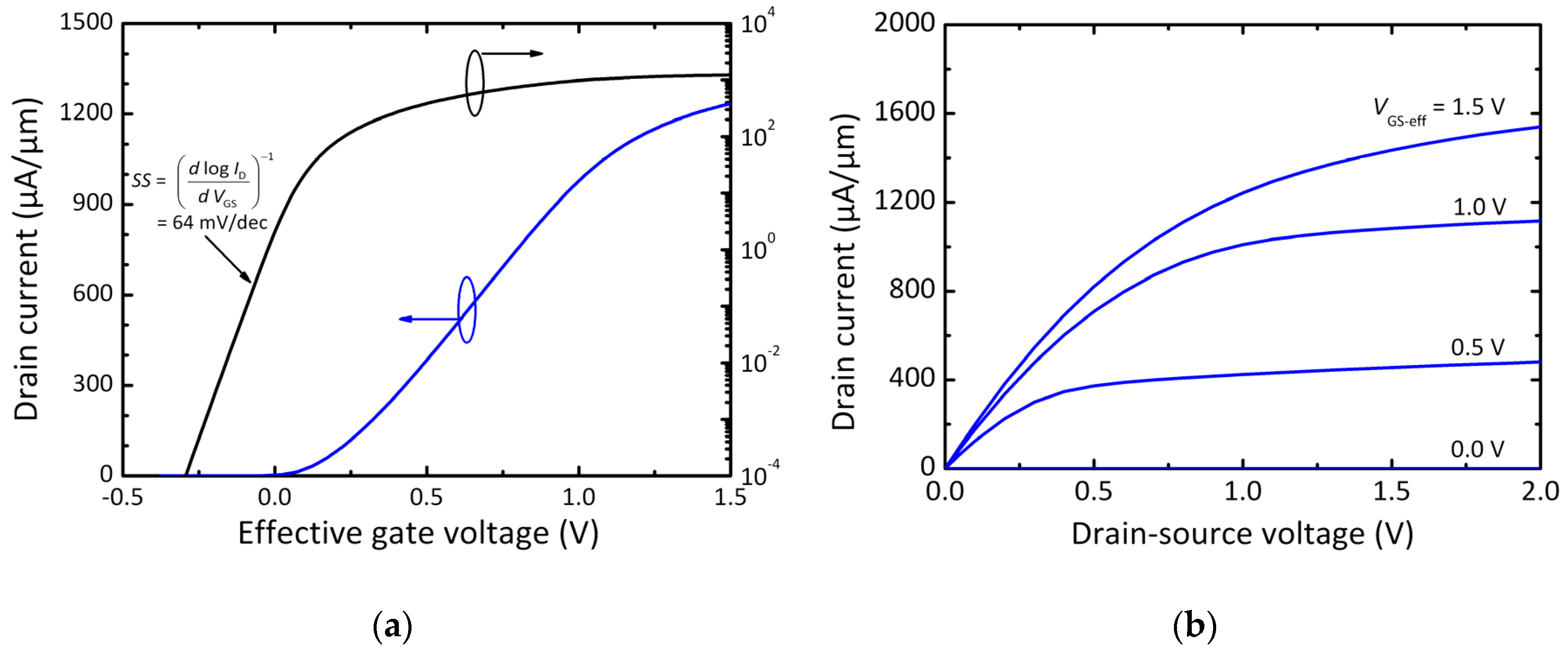

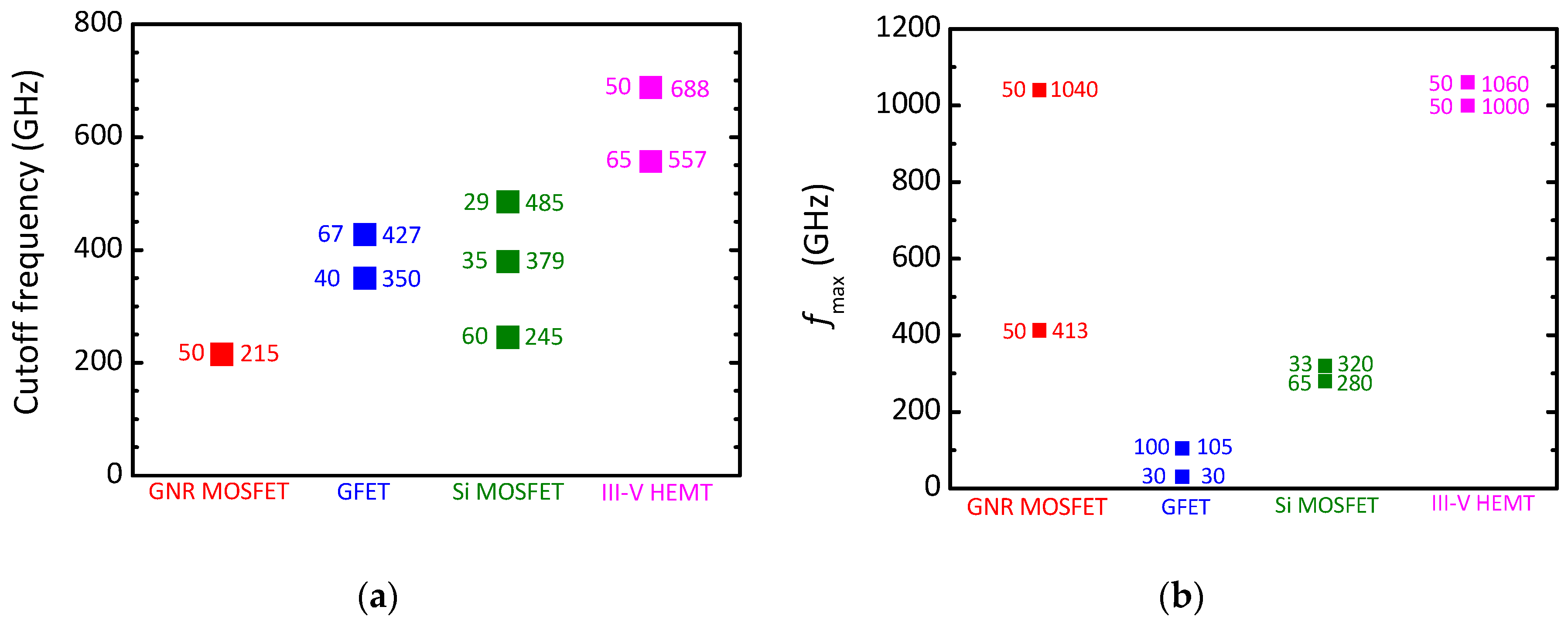

3.2. Simulation Results for Single-Channel GNR MOSFETs

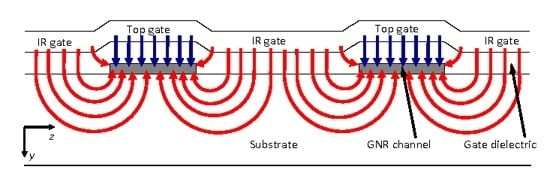

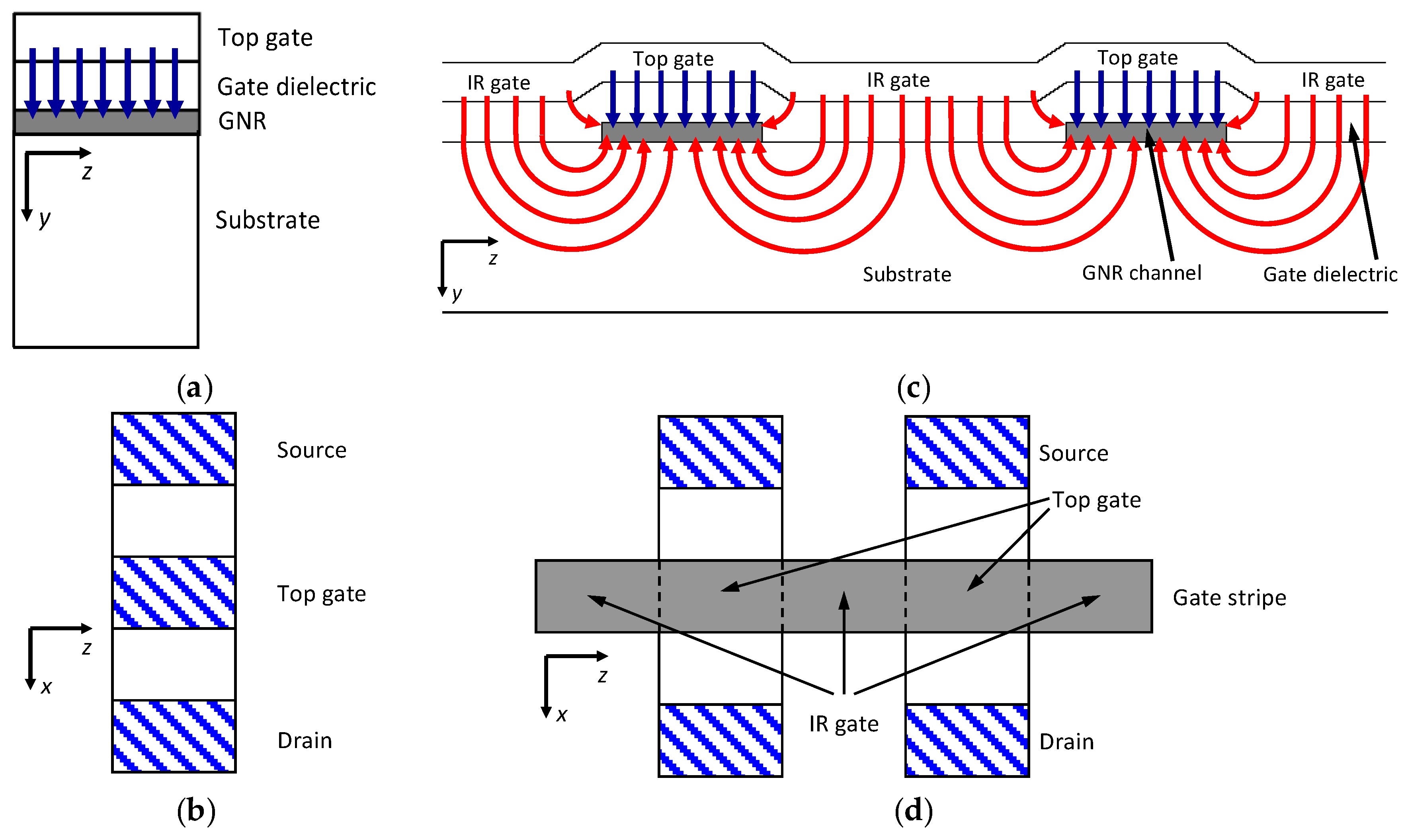

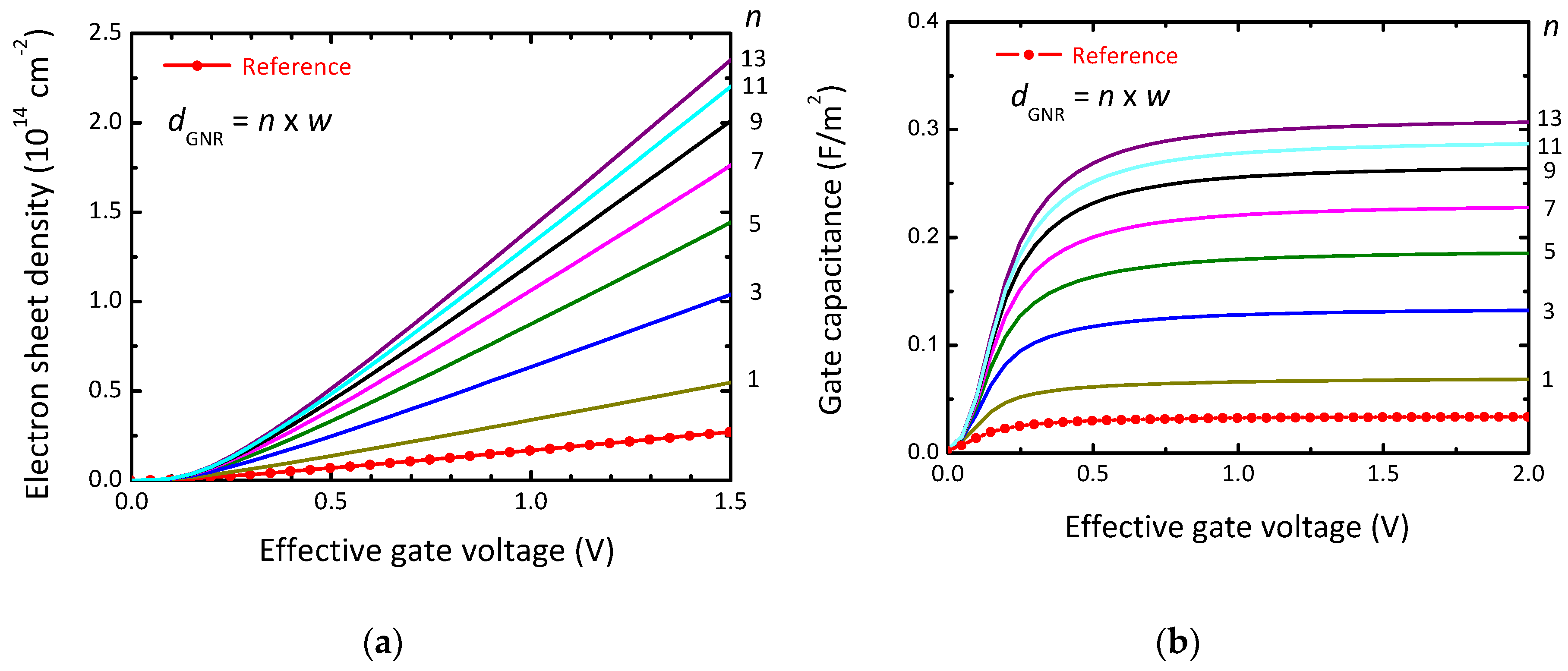

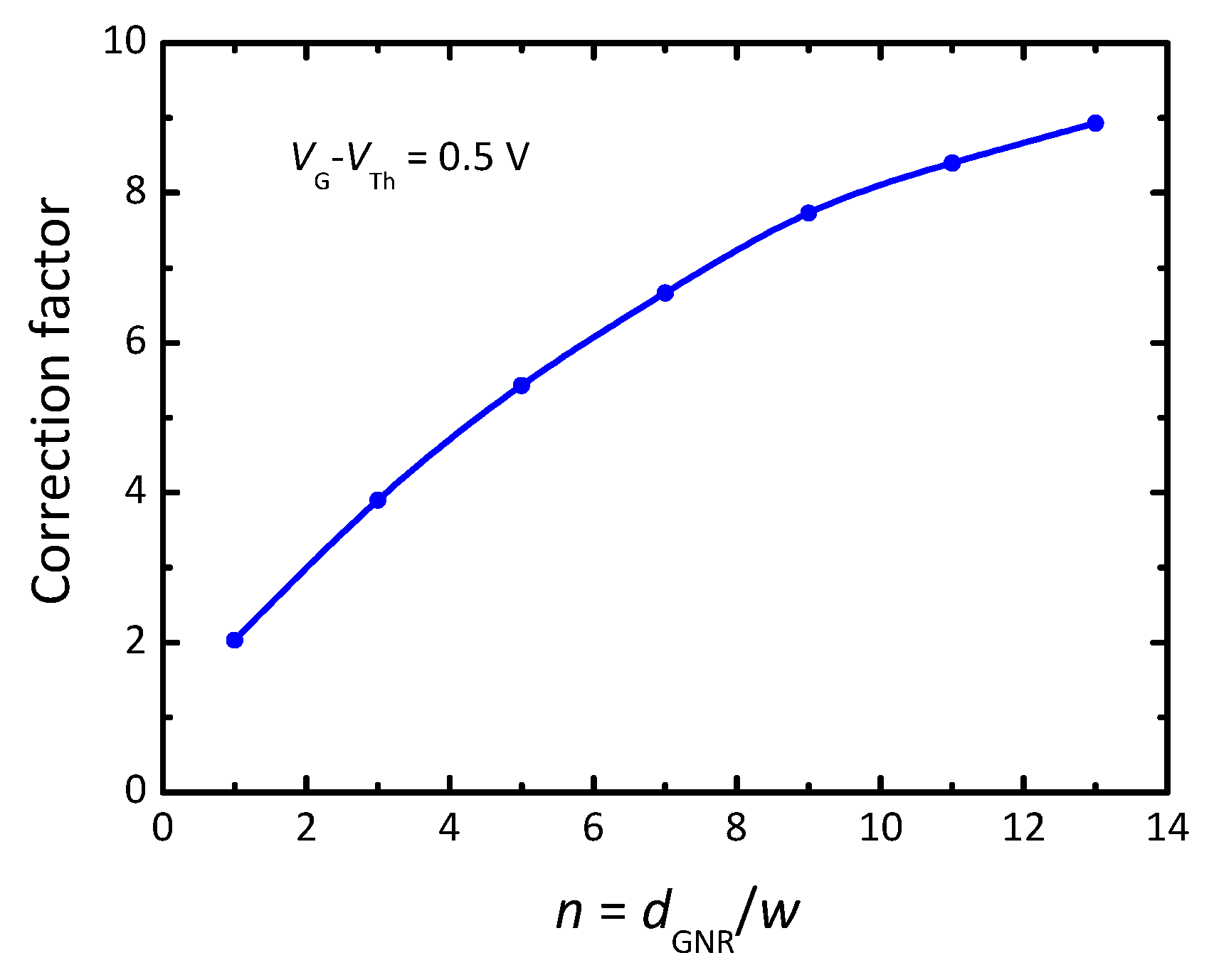

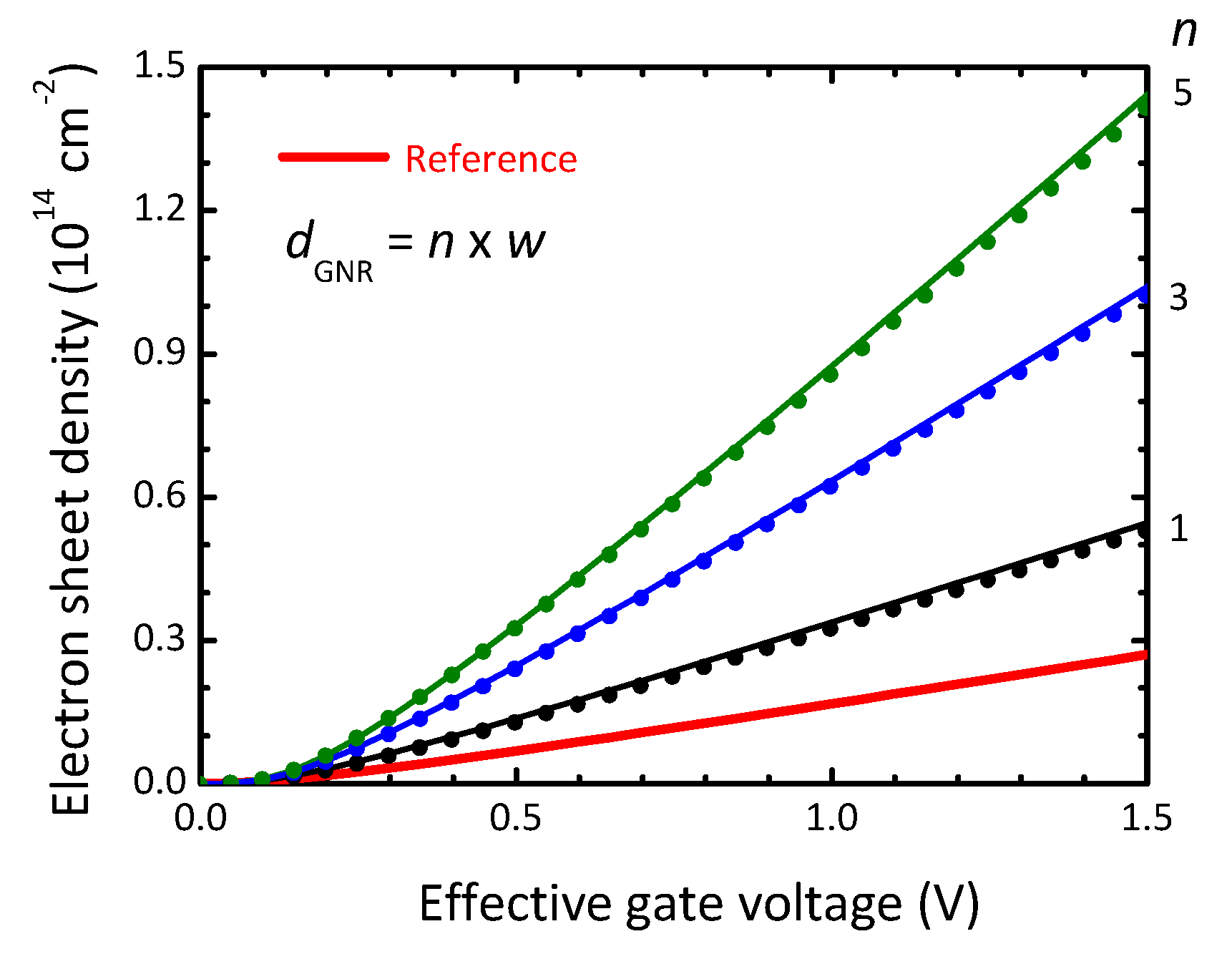

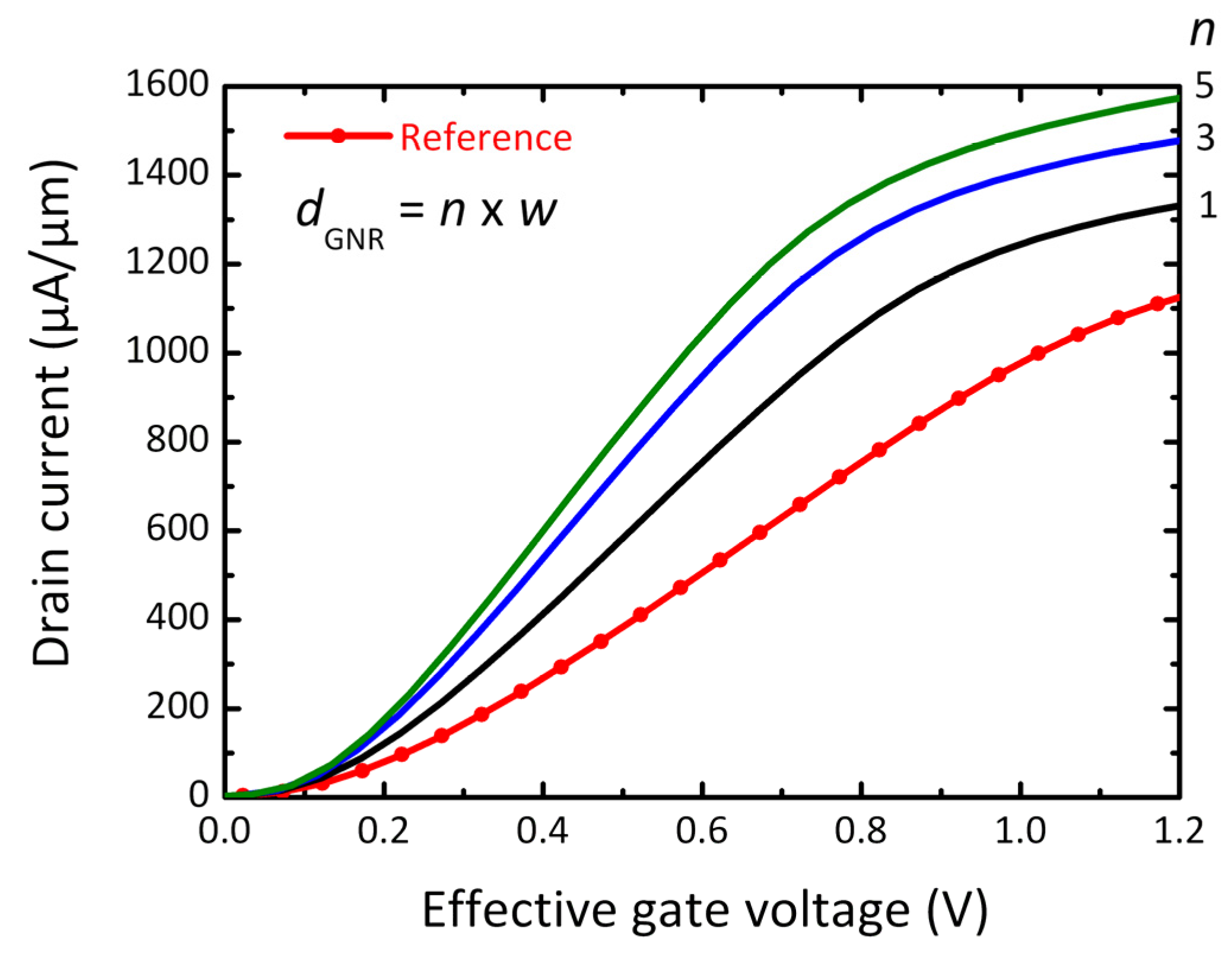

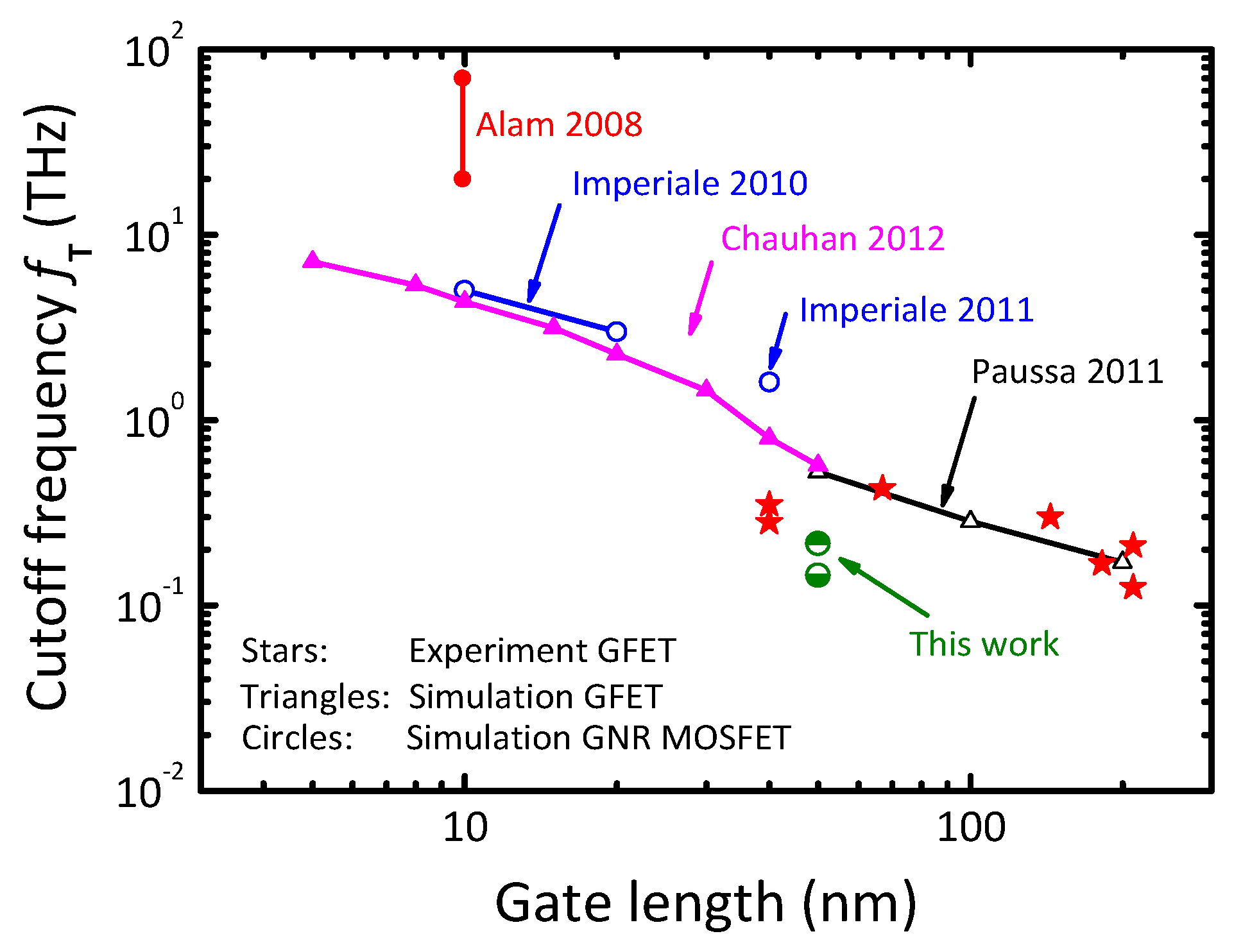

3.3. Simulation Results for Multiple-Channel GNR MOSFETs with Interribbon Gates

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Appendix

References

- Geim, A.K.; Novoselov, K.S. The rise of graphene. Nat. Mater. 2007, 6, 183–191. [Google Scholar] [CrossRef] [PubMed]

- Wu, Y.; Jenkins, K.A.; Valdes-Garcia, A.; Farmer, D.B.; Zhu, Y.; Bol, A.A.; Dimitrakopoulos, C.; Zhu, W.; Xia, F.; Avouris, P.; et al. State-of-the-art graphene high-frequency electronics. Nano Lett. 2012, 2, 3062–3067. [Google Scholar] [CrossRef] [PubMed]

- Cheng, R.; Bai, J.; Liao, L.; Zhou, H.; Chen, Y.; Liu, L.; Lin, Y.-C.; Jiang, S.; Huang, Y.; Duan, X. High-frequency self-aligned graphene transistors with transferred gate stacks. Proc. Natl. Acad. Sci. USA 2012, 109, 11588–11592. [Google Scholar] [CrossRef] [PubMed]

- Schwierz, F. Graphene transistors. Nat. Nanotechnol. 2010, 5, 487–496. [Google Scholar] [CrossRef] [PubMed]

- Schwierz, F. Graphene transistors: Status, prospects, and problems. Proc. IEEE 2013, 101, 1567–1584. [Google Scholar] [CrossRef]

- Lemme, M.C.; Li, L.-J.; Palacios, T.; Schwierz, F. Two-dimensional materials for electronic applications. MRS Bull. 2014, 39, 711–718. [Google Scholar] [CrossRef]

- Castro, E.V.; Novoselov, K.S.; Morozov, S.V.; Peres, N.M.R.; Lopes-dos-Santos, J.M.B.; Nilsson, J.; Guinea, F.; Geim, A.K.; Castro-Neto, A.H. Biased bilayer graphene: Semiconductor with a gap tunable by the electric field effect. Phys. Rev. Lett. 2007, 99, 216802. [Google Scholar] [CrossRef] [PubMed]

- Szafranek, B.N.; Fiori, G.; Schall, D.; Neumaier, D.; Kurz, H. Current saturation and voltage gain in bilayer graphene field effect transistors. Nano Lett. 2012, 12, 1324–1328. [Google Scholar] [CrossRef] [PubMed]

- Han, M.Y.; Özyilmaz, B.; Zhang, Y.; Kim, P. Energy band-gap engineering of graphene nanoribbons. Phys. Rev. Lett. 2007, 98, 206805. [Google Scholar] [CrossRef] [PubMed]

- Linden, S.; Zhong, D.; Timmer, A.; Aghdassi, N.; Franke, J.H.; Zhang, H.; Feng, X.; Müllen, K.; Fuchs, H.; Chi, L.; et al. Electronic structure of spatially aligned graphene nanoribbons on Au(788). Phys. Rev. Lett. 2012, 108, 216801. [Google Scholar] [CrossRef] [PubMed]

- Liang, X.; Jung, Y.-S.; Wu, S.; Ismach, A.; Olynick, D.L.; Cabrini, S.; Bokor, J. Formation of bandgap and subbands in graphene nanomeshes with sub-10 nm ribbon width fabricated via nanoimprint lithography. Nano Lett. 2010, 10, 2454–2460. [Google Scholar] [CrossRef] [PubMed]

- Berrada, S.; Nguyen, V.H.; Querlioz, D.; Saint-Martin, J.; Alarcon, A.; Chassat, C.; Bournel, A.; Dollfus, P. Graphene nanomesh transistor with high on/off ratio and good saturation behavior. Appl. Phys. Lett. 2013, 103, 183509. [Google Scholar] [CrossRef]

- Raza, H.; Kan, E.C. Armchair graphene nanoribbons: Electronic structure and electric-field modulation. Phys. Rev. B 2008, 77, 245434. [Google Scholar] [CrossRef]

- Yang, L.; Park, C.-H.; Son, Y.-W.; Cohen, M.L.; Louie, S.G. Quasiparticle energies and band gaps in graphene nanoribbons. Phys. Rev. Lett. 2007, 99, 186801. [Google Scholar] [CrossRef] [PubMed]

- Gunlycke, D.; White, C.T. Tight-binding energy dispersions of armchair-edge graphene nanostripes. Phys. Rev. B 2008, 77, 115116. [Google Scholar] [CrossRef]

- The International Technology Roadmap for Semiconductors. Available online: http://www.itrs.net (accessed on 15 October 2015).

- Li, X.; Wang, X.; Zhang, L.; Lee, S.; Dai, H. Chemically derived, ultrasmooth graphene nanoribbon semiconductors. Science 2008, 319, 1229–1232. [Google Scholar] [CrossRef] [PubMed]

- Wang, X.; Ouyang, Y.; Li, X.; Wang, H.; Guo, J.; Dai, H. Room-temperature all-semiconducting sub-10-nm graphene nanoribbon field-effect transistors. Phys. Rev. Lett. 2008, 100, 206803. [Google Scholar] [CrossRef] [PubMed]

- Bai, J.; Duan, X.; Huang, Y. Rational fabrication of graphene nanoribbons using a nanowire etch mask. Nano Lett. 2009, 9, 2083–2087. [Google Scholar] [CrossRef] [PubMed]

- Liao, L.; Bai, J.; Cheng, R.; Lin, Y.-C.; Jiang, S.; Huang, Y.; Duan, X. Top-gated graphene nanoribbon transistors with ultrathin high-k dielectrics. Nano Lett. 2010, 10, 1917–1921. [Google Scholar] [CrossRef] [PubMed]

- Alam, K. Gate dielectric scaling of top gate carbon nanoribbon on insulator transistors. J. Appl. Phys. 2008, 104, 074313. [Google Scholar] [CrossRef]

- Imperiale, I.; Gnudi, A.; Gnani, E.; Reggiani, S.; Baccarani, G. High-frequency analog GNR-FET design criteria. In Proceedings of the 2011 European Solid-State Device Research Conference (ESSDERC), Helsinki, Finland, 12–16 September 2011; pp. 303–306.

- Harada, N.; Sato, S.; Yokoyama, N. Theoretical investigation of graphene nanoribbon field-effect transistors designed for digital applications. Jpn. J. Appl. Phys. 2013, 52, 094301. [Google Scholar] [CrossRef]

- Liang, G.; Neophytou, N.; Lundstrom, M.S.; Nikonov, D.E. Ballistic graphene nanoribbon metal-oxide-semiconductor field-effect transistors: A full real-space quantum transport simulation. J. Appl. Phys. 2007, 102, 054307. [Google Scholar] [CrossRef]

- Imperiale, I.; Bonsignore, S.; Gnudi, A.; Gnani, E.; Reggiani, S.; Baccarani, G. Computational study of graphene nanoribbon FETs for RF applications. In Proceedings of the 2010 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010; pp. 732–735.

- Fiori, G.; Iannaccone, G. Simulation of graphene nanoribbon field-effect transistors. IEEE Electron Device Lett. 2007, 8, 760–762. [Google Scholar] [CrossRef]

- Goharrizi, A.Y.; Pourfarth, M.; Fathipour, M.; Kosina, H. Device performance of graphene nanoribbon field-effect transistors in the presence of edge-line roughness. IEEE Trans. Electron Devices 2012, 59, 3527–3532. [Google Scholar] [CrossRef]

- Kliros, G.S. Gate capacitance modeling and width-dependent performance of graphene nanoribbon transistors. Microelctron. Eng. 2013, 112, 220–226. [Google Scholar] [CrossRef]

- Bruzzone, S.; Iannaccone, G.; Marzari, N.; Fiori, G. An open-source multiscale framework for the simulation of nanoscale devices. IEEE Trans. Electron Devices 2014, 61, 48–53. [Google Scholar] [CrossRef]

- ATLAS User’s Manual—Device Simulation Software, Silvaco. Available online: http://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silentmanuals&nm=atlas (accessed on 15 October 2015).

- Schwierz, F.; Pezoldt, J.; Granzner, R. Two-dimensional materials and their prospects in transistor applications. Nanoscale 2015, 7, 8261–8283. [Google Scholar] [CrossRef] [PubMed]

- Ruffieux, P.; Cai, J.; Plumb, N.; Patthey, L.; Prezzi, D.; Ferretti, A.; Molinari, E.; Feng, X.; Müllen, K.; Pignedoli, C.A.; et al. Electronic structure of atomically precise graphene nanoribbons. ACS Nano 2012, 6, 6930–6935. [Google Scholar] [CrossRef] [PubMed]

- Chen, Y.-C.; de Oteyza, D.G.; Pedramrazi, Z.; Chen, C.; Fischer, F.R.; Crommie, M.F. Tuning the band gap of graphene nanoribbons synthesized from molecular precursors. ACS Nano 2013, 7, 6123–6128. [Google Scholar] [CrossRef] [PubMed]

- Fang, T.; Konar, A.; Xing, H.; Jena, D. Carrier statistics and quantum capacitance of graphene sheets and ribbons. Appl. Phys. Lett. 2007, 91, 092109. [Google Scholar] [CrossRef]

- Granzner, R.; Polyakov, V.M.; Schwierz, F.; Kittler, M.; Luyken, R.J.; Rösner, W.; Städele, M. Simulation of nanoscale MOSFETs using modified drift-diffusion and hydrodynamic models and comparison with Monte Carlo results. Microelectron. Eng. 2006, 83, 241–246. [Google Scholar] [CrossRef]

- Szabo, A.; Rhyner, R.; Luisier, M. Ab-initio simulations of MoS2 transistors: From mobility calculation to device performance evaluation. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 725–728.

- Cao, W.; Kang, J.; Sarkar, D.; Liu, W.; Banerjee, K. Performance evaluation and design considerations of 2D semiconductor based FETs for sub-10 nm VLS. In Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 729–732.

- Liu, L.; Lu, Y.; Guo, J. On monolayer MoS2 field-effect transistors at the scaling limit. IEEE Trans. Electron Devices 2013, 60, 4133–4139. [Google Scholar] [CrossRef]

- Ancona, M.G. Electron transport in graphene from a diffusion-drift perspective. IEEE Trans. Electron Devices 2010, 57, 681–689. [Google Scholar] [CrossRef]

- Betti, A.; Fiori, G.; Iannaccone, G. Drift velocity peak and negative differential mobility in high field transport in graphene nanoribbons explained by numerical simulations. Appl. Phys. Lett. 2011, 99, 242108. [Google Scholar] [CrossRef]

- Caughey, D.M.; Thomas, R.E. Carrier mobilities in silicon empirically related to doping and field. Proc. IEEE 1967, 52, 2192–2193. [Google Scholar] [CrossRef]

- Granzner, R.; Thiele, S.; Schippel, C.; Schwierz, F. Quantum effects on the gate capacitance of trigate SOI MOSFETs. IEEE Trans. Electron Devices 2010, 57, 3231–3237. [Google Scholar] [CrossRef]

- Unluer, D.; Tseng, F.; Ghosh, A.W.; Stan, M.R. Monolithically patterned wide-narrow-wide all-graphene devices. IEEE Trans. Nanotechnol. 2011, 10, 931–939. [Google Scholar] [CrossRef]

- Schwierz, F.; Liou, J.J. Modern Microwave Transistors; John Wiley & Sons: Hoboken, NJ, USA, 2003. [Google Scholar]

- Schwierz, F. Microwave Transistors: State of the Art in the 1980s, 1990s, 2000s, and 2010s. A Compilation of 1500 Top References; TU Ilmenau: Ilmenau, Germany, 2015; unpublished. [Google Scholar]

- Kranti, A.; Raskin, J.-P.; Armstrong, G.A. Optimizing FinFET geometry and parasitics for RF applications. In Proceedings of the IEEE International SOI Conference, New Paltz, NY, USA, 6–9 October 2008; pp. 123–124.

- Chauhan, J.; Liu, L.; Lu, Y.; Guo, J. A computational study of high-frequency behavior of graphene field-effect transistors. J. Appl. Phys. 2012, 111, 094313. [Google Scholar] [CrossRef]

- Paussa, A.; Geromel, M.; Palestri, P.; Bresciani, M.; Esseni, D.; Selmi, L. Simulation of graphene nanoscale RF transistors including scattering and generation/recombination mechanisms. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 271–274.

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nanmeni Bondja, C.; Geng, Z.; Granzner, R.; Pezoldt, J.; Schwierz, F. Simulation of 50-nm Gate Graphene Nanoribbon Transistors. Electronics 2016, 5, 3. https://doi.org/10.3390/electronics5010003

Nanmeni Bondja C, Geng Z, Granzner R, Pezoldt J, Schwierz F. Simulation of 50-nm Gate Graphene Nanoribbon Transistors. Electronics. 2016; 5(1):3. https://doi.org/10.3390/electronics5010003

Chicago/Turabian StyleNanmeni Bondja, Cedric, Zhansong Geng, Ralf Granzner, Jörg Pezoldt, and Frank Schwierz. 2016. "Simulation of 50-nm Gate Graphene Nanoribbon Transistors" Electronics 5, no. 1: 3. https://doi.org/10.3390/electronics5010003