Active Disturbance Rejection Control of Full-Bridge DC–DC Converter for a Pulse Power Supply with Controllable Charging Time

Abstract

:1. Introduction

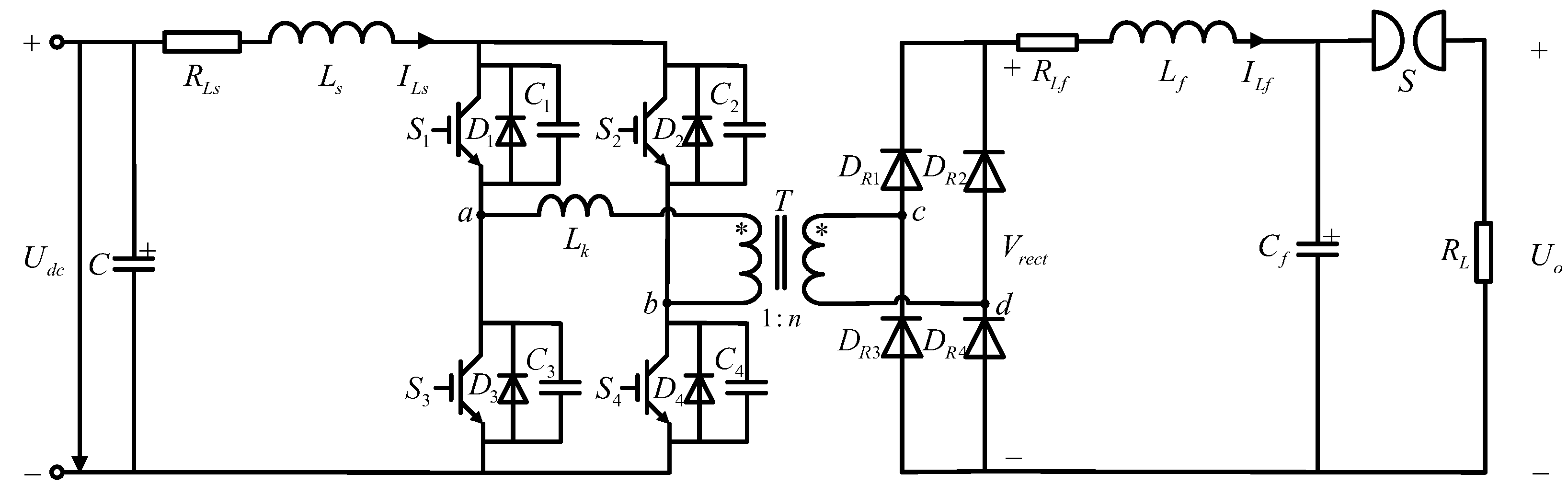

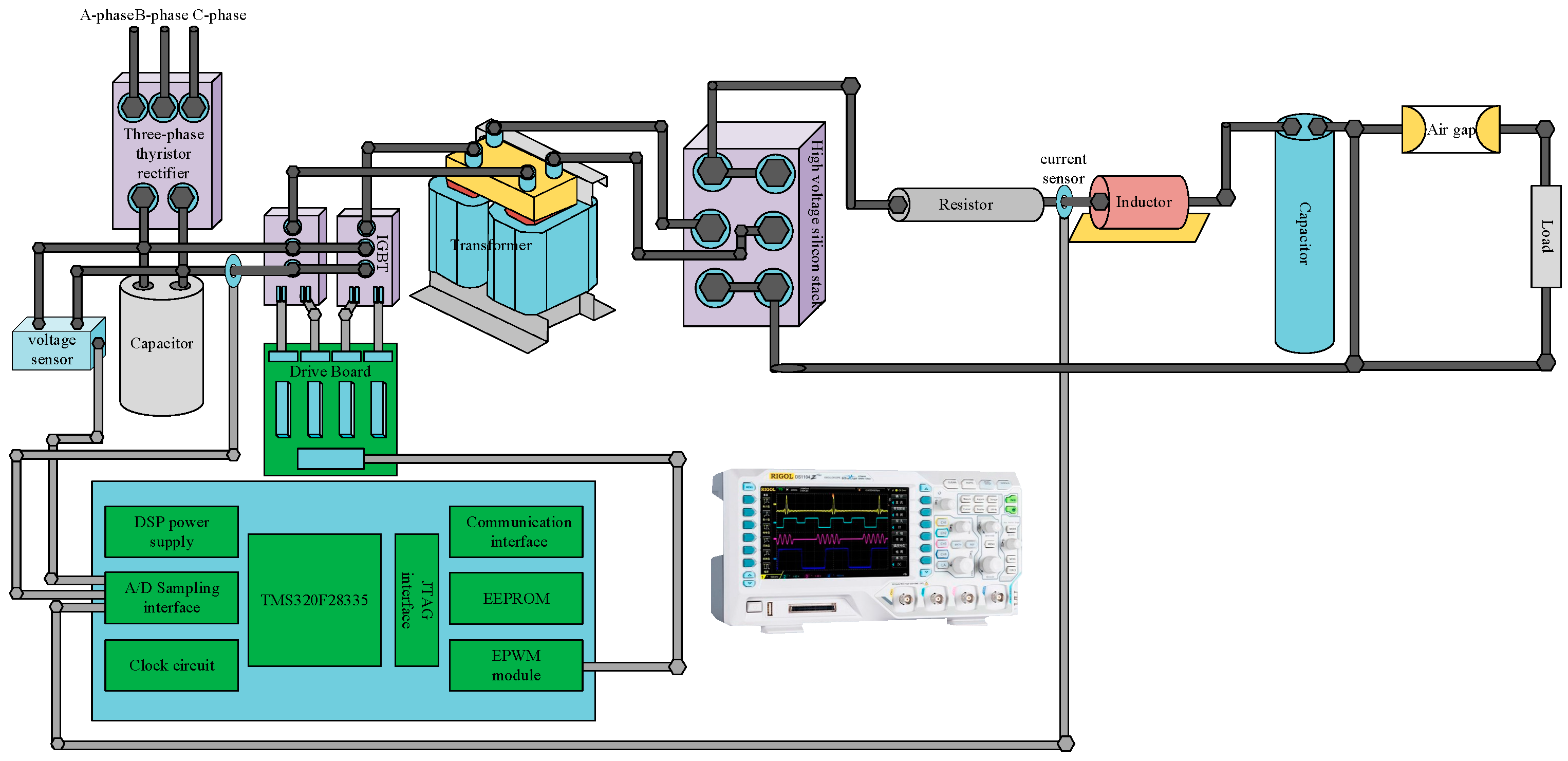

2. Topology and Operation Principle

2.1. Topology

2.2. Operation Principle

- All components are considered ideal;

- Input voltage is a constant;

- Regardless of the transformer saturation effect.

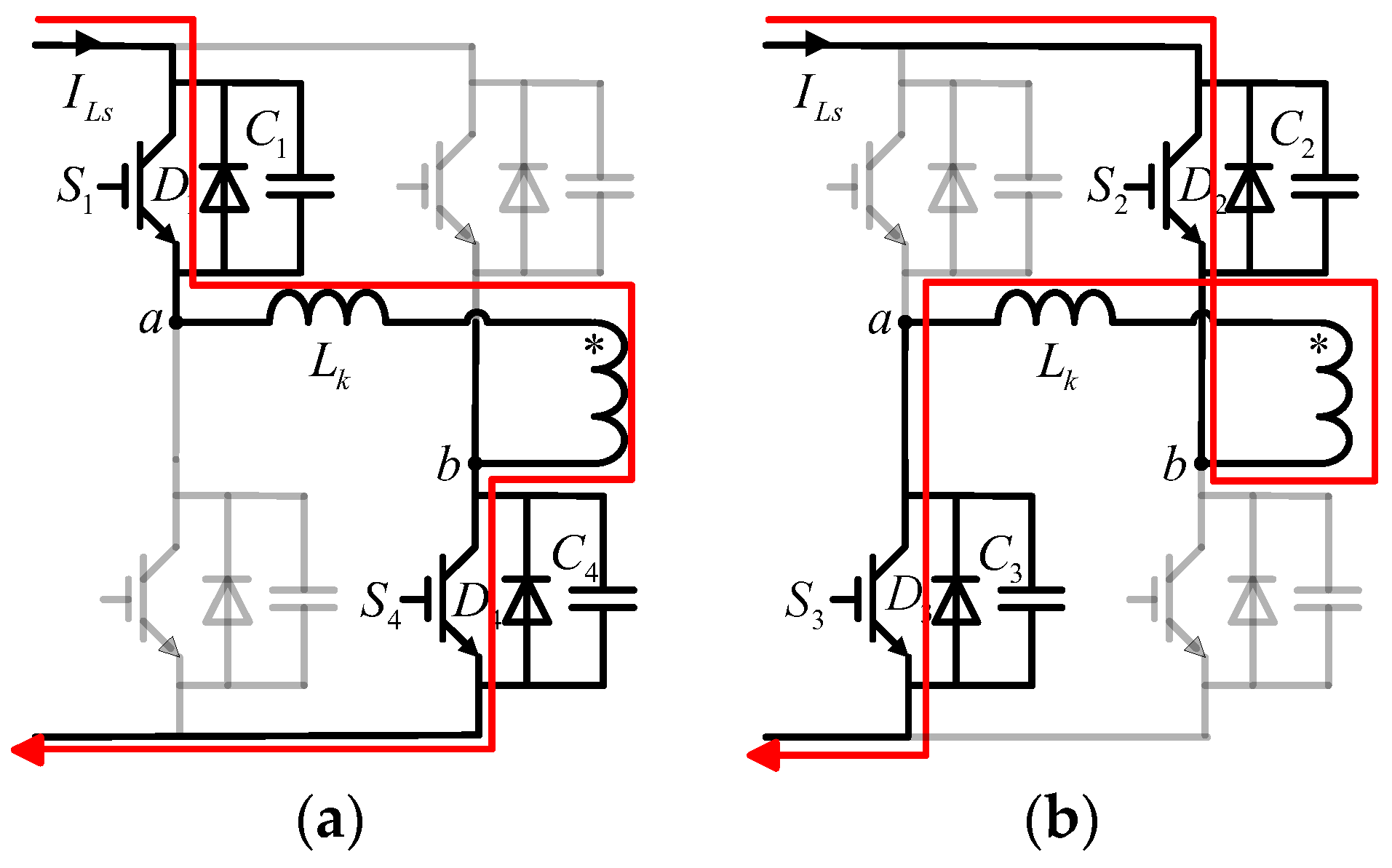

- Interval 1 ( − )

- Interval 2 ()

- Supplying Stage

- Discharging Stage

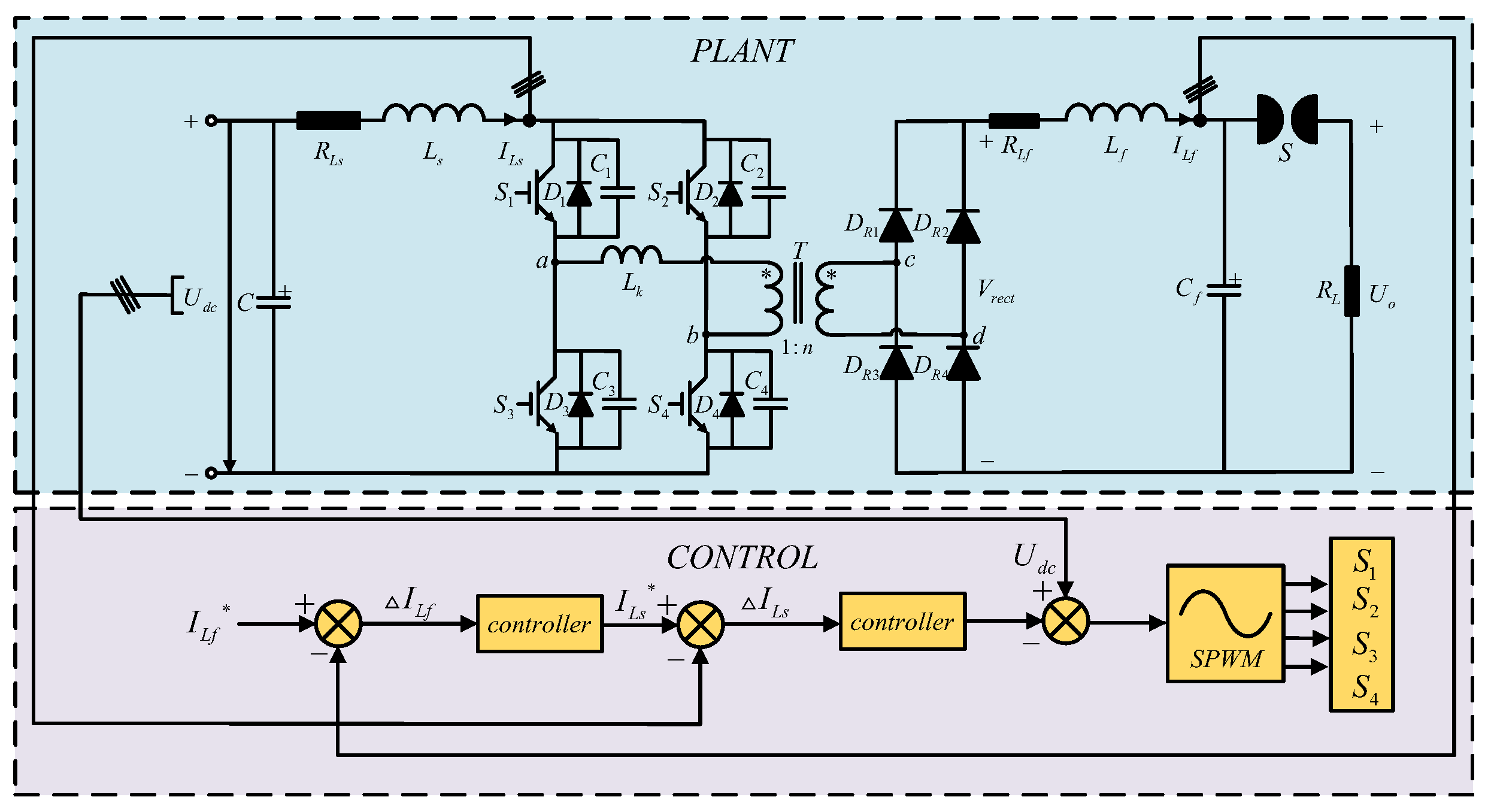

3. System Structure

4. ADRC-Based Current Control

4.1. Formation of ADRC-Based Current Controller

4.2. Stability Analysis

5. Simulation Results and Experimental Verification

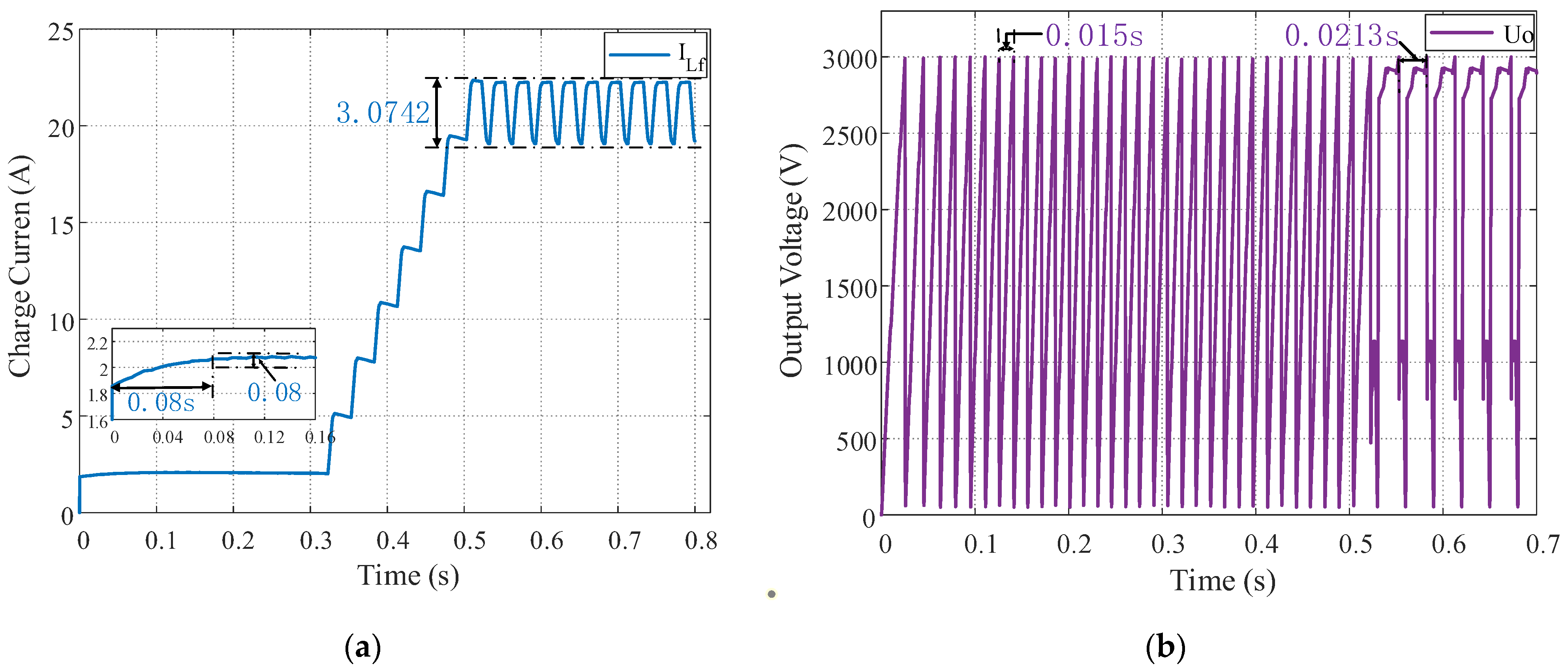

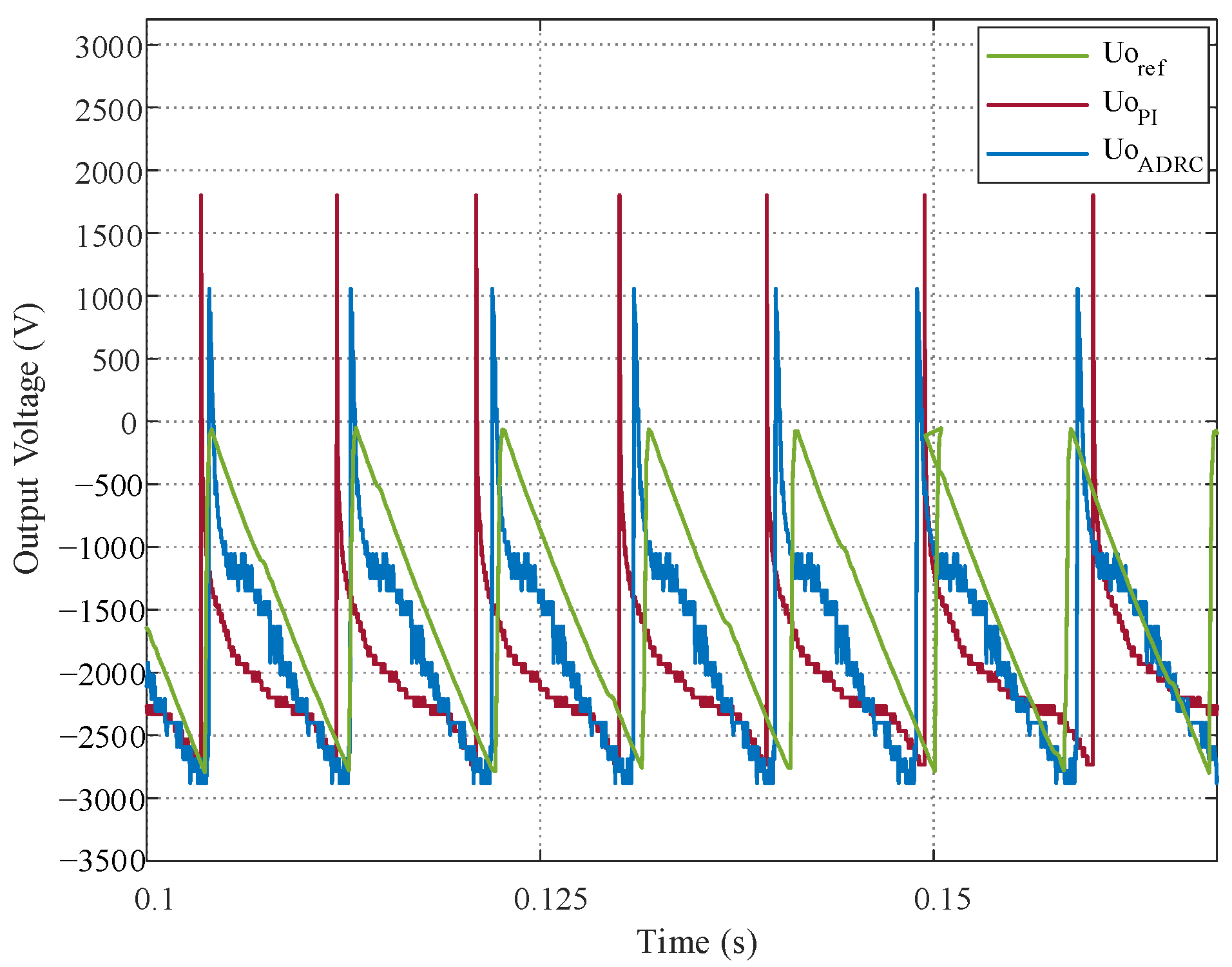

5.1. Simulation Results

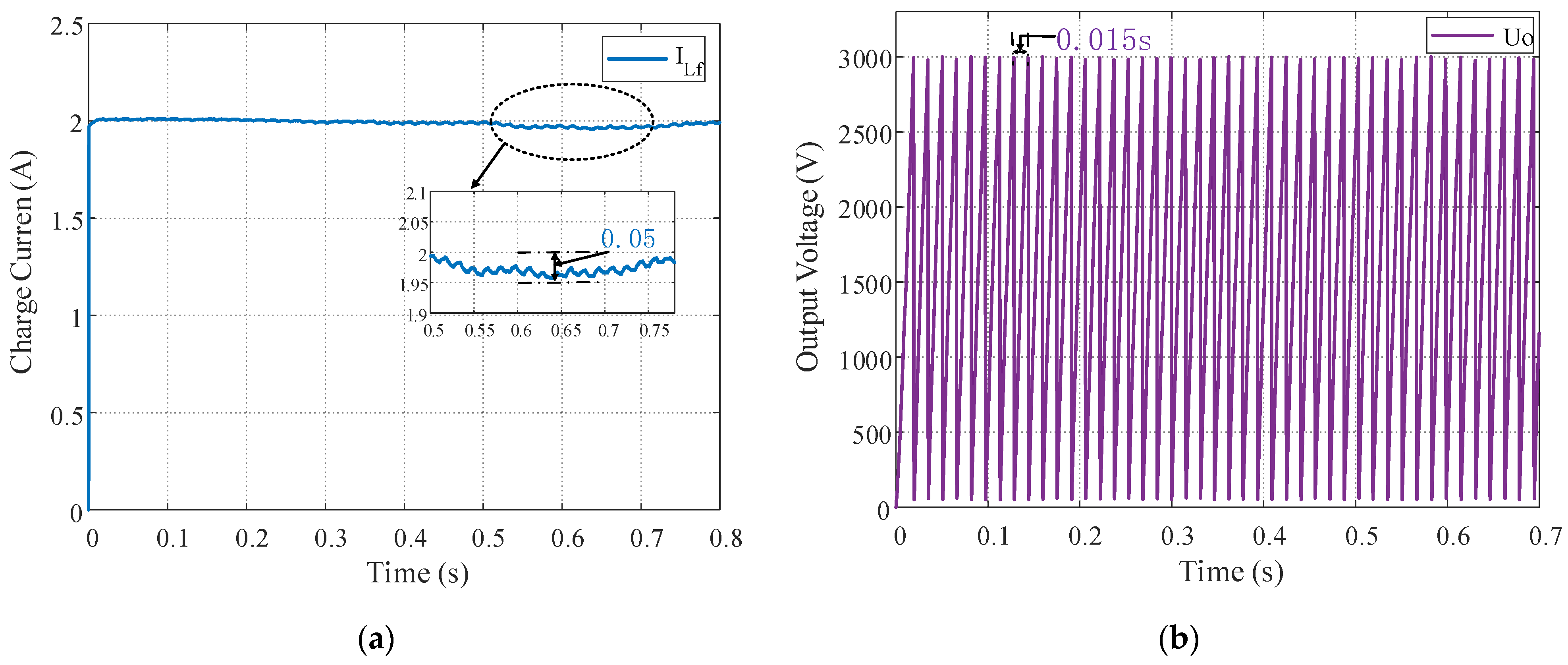

5.1.1. Steady-State Performance

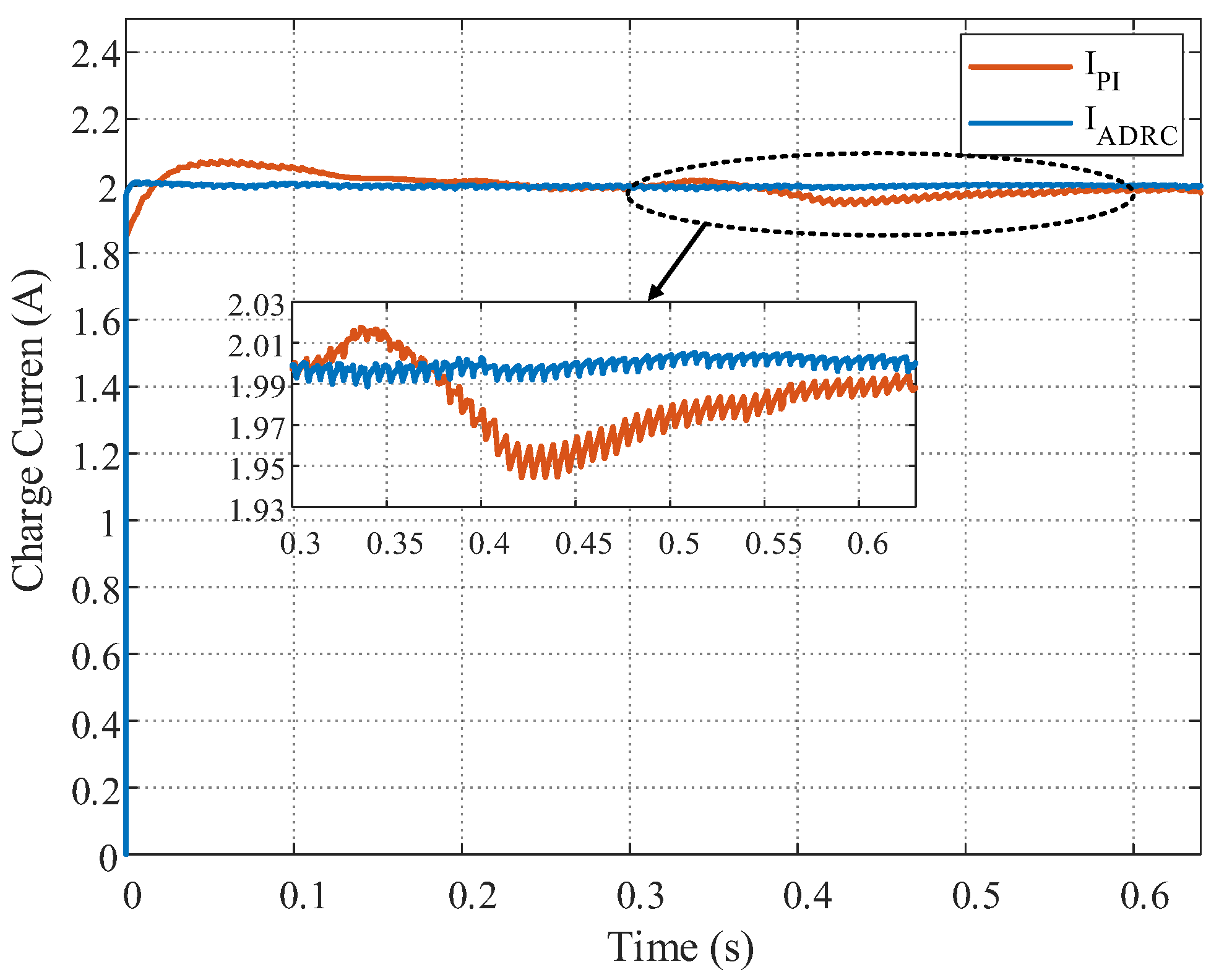

5.1.2. Robustness under Parameter Variations

5.1.3. Transient Performance

5.1.4. Anti-Disturbance Performance

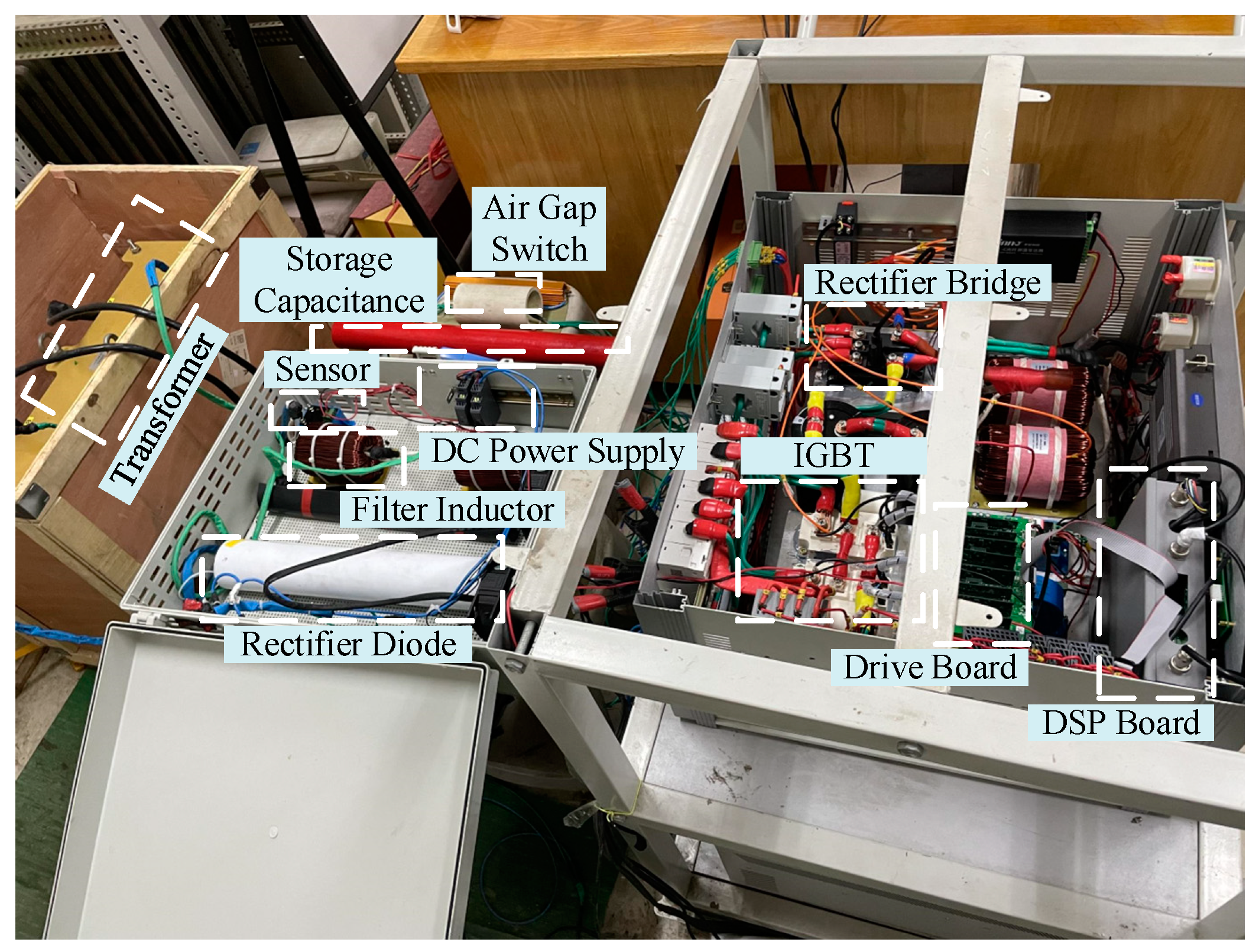

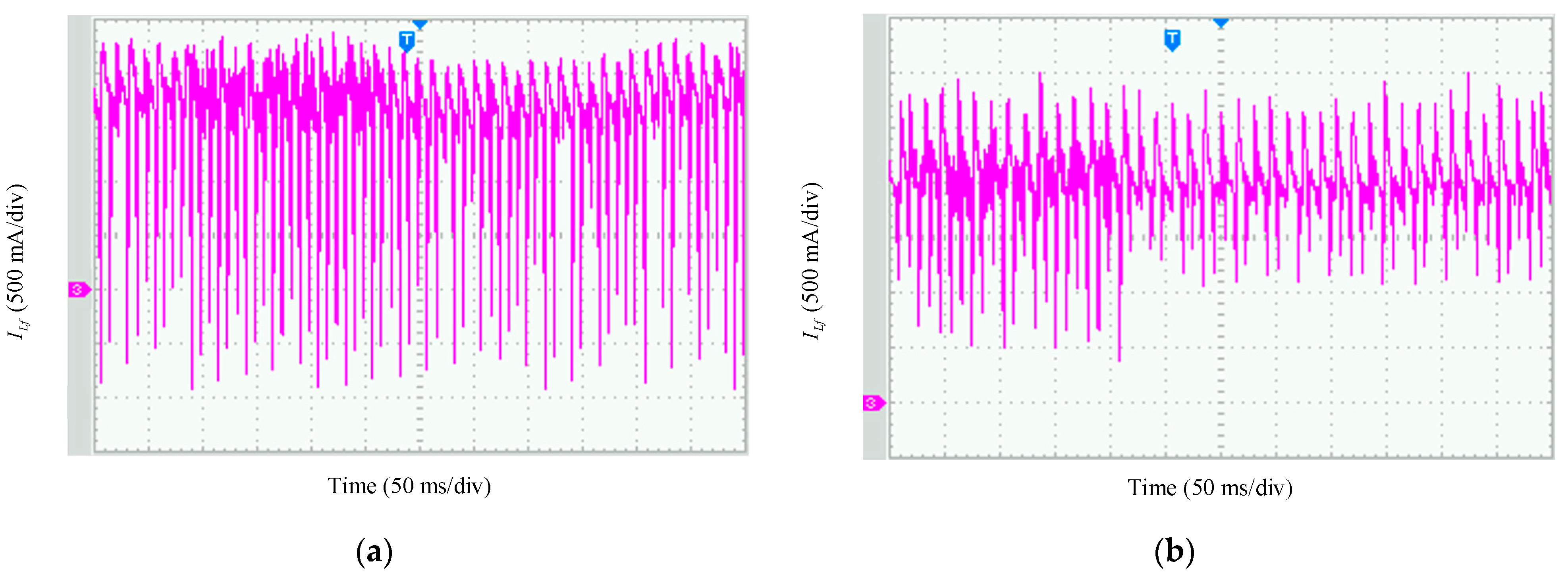

5.2. Experimental Results

6. Conclusions

- If the system is applied to long-line applications, the stray parameters existing in the line will cause changes in the system parameters, which will bring difficulties to the design of the controller.

- Since the pulse discharge is used by the gas spark switch, continuous discharge will cause the ablation of the switching electrode, resulting in fluctuations in the discharge voltage.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Davari, P.; Zare, F.; Ghosh, A.; Akiyama, H. High-Voltage Modular Power Supply Using Parallel and Series Configurations of Flyback Converter for Pulsed Power Applications. IEEE Trans. Plasma Sci. 2012, 40, 2578–2587. [Google Scholar] [CrossRef]

- Akiyama, H.; Sakugawa, T.; Namihira, T.; Takaki, K.; Minamitani, Y.; Shimomura, N. Industrial Applications of Pulsed Power Technology. IEEE Trans. Dielectr. Electr. Insul. 2007, 14, 1051–1064. [Google Scholar] [CrossRef]

- Elserougi, A.; Ahmed, S.; Massoud, A. High voltage pulse generator based on DC-to-DC boost converter with capacitor-diode voltage multipliers for bacterial decontamination. In Proceedings of the IECON 2015—41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015. [Google Scholar]

- Nuccitelli, R. Nanosecond pulsed electric fields cause melanomas to self-destruct. In Proceedings of the Conference Record of the 2006 Twenty-Seventh International Power Modulator Symposium, Arlington, VA, USA, 14–18 May 2006. [Google Scholar]

- Sethian, J.D. Pulsed power for a rep-rate, electron beam pumped KrF laser. IEEE Trans. Plasma Sci. 2000, 28, 1333–1337. [Google Scholar] [CrossRef]

- Tsoi, T.; Whitworth, C.; Kim, M.; Bayne, S.; O’Brien, H.; Ogunniyi, A. SiC GTOs Thyristor for Long Term Reliability on Pulsed Power Application Test. In Proceedings of the 2021 IEEE Pulsed Power Conference (PPC), Denver, CO, USA, 12–16 December 2021. [Google Scholar]

- Collier, L.; Kajiwara, T.; Dickens, J.; Mankowski, J.; Neuber, A. Fast SiC Switching Limits for Pulsed Power Applications. IEEE Trans. Plasma Sci. 2019, 47, 5306–5313. [Google Scholar] [CrossRef]

- Nakayama, K.; Tanaka, Y.; Kato, T.; Kojima, K.; Sometani, M.; Yonezawa, Y. 10 kV SiC thyristor for High Voltage Pulsed Power Generators. In Proceedings of the 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 19–23 March 2023. [Google Scholar]

- Liang, S.; Guo, J.; Liu, H.; Wang, J. Evaluation of High-Voltage 4H-SiC Gate Turn-off Thyristor for Pulsed Power Application. In Proceedings of the 2021 IEEE 1st International Power Electronics and Application Symposium (PEAS), Shanghai, China, 13–15 November 2021. [Google Scholar]

- Ren, X.; Xu, Z.-W.; Xu, K.; Zhang, Z.; Chen, Q. SiC Stacked-Capacitor Converters for Pulse Applications. IEEE Trans. Power Electron. 2019, 34, 4450–4464. [Google Scholar] [CrossRef]

- Redondo, L.M. A DC Voltage-Multiplier Circuit Working as a High-Voltage Pulse Generator. IEEE Trans. Plasma Sci. 2010, 38, 2725–2729. [Google Scholar] [CrossRef]

- Ahn, S.-H.; Ryoo, H.-J.; Gong, J.-W.; Jang, S.-R. Low-Ripple and High-Precision High-Voltage DC Power Supply for Pulsed Power Applications. IEEE Trans. Plasma Sci. 2014, 42, 3023–3033. [Google Scholar] [CrossRef]

- Zabihi, S.; Zare, F.; Ledwich, G.; Ghosh, A.; Akiyama, H. A new pulsed power supply topology based on positive buck-boost converters concept. IEEE Trans. Dielectr. Electr. Insul. 2010, 17, 1901–1911. [Google Scholar] [CrossRef]

- Zabihi, S.; Zare, F.; Ledwich, G.; Ghosh, A.; Akiyama, H. A Novel High-Voltage Pulsed-Power Supply Based on Low-Voltage Switch–Capacitor Units. IEEE Trans. Plasma Sci. 2010, 38, 2877–2887. [Google Scholar] [CrossRef]

- Yao, Y.; Krishnamoorthy, H.S.; Yerra, S. Linear Assisted DC/DC Converter for Pulsed Mode Power Applications. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Smart Grid and Renewable Energy (PESGRE2020), Cochin, India, 2–4 January 2020. [Google Scholar]

- Safaee, A.; Jain, P.K.; Bakhshai, A. An Adaptive ZVS Full-Bridge DC–DC Converter With Reduced Conduction Losses and Frequency Variation Range. IEEE Trans. Power Electron. 2015, 30, 4107–4118. [Google Scholar] [CrossRef]

- Xie, Y.; Ghaemi, R.; Sun, J.; Freudenberg, J.S. Implicit Model Predictive Control of a Full Bridge DC–DC Converter. IEEE Trans. Power Electron. 2009, 24, 2704–2713. [Google Scholar] [CrossRef]

- He, H.; Si, T.; Sun, L.; Liu, B.; Li, Z. Linear Active Disturbance Rejection Control for Three-Phase Voltage-Source PWM Rectifier. IEEE Access 2020, 8, 45050–45060. [Google Scholar] [CrossRef]

- Su, Y.; Ge, X.; Xie, D.; Wang, K. An Active Disturbance Rejection Control-Based Voltage Control Strategy of Single-Phase Cascaded H-Bridge Rectifiers. IEEE Trans. Ind. Appl. 2020, 56, 5182–5193. [Google Scholar] [CrossRef]

- Tiwari, N.; Agarwal, P.; Srivastava, S.P. Performance investigation of modified hysteresis current controller with the permanent magnet synchronous motor drive. IET Electr. Power Appl. 2020, 4, 101–108. [Google Scholar] [CrossRef]

- Kang, B.J.; Liaw, C.M. A robust hysteresis current-controlled PWM inverter for linear PMSM driven magnetic suspended positioning system. IEEE Trans. Ind. Electron. 2021, 48, 956–967. [Google Scholar] [CrossRef]

- Zhang, X.; Hou, B.; Mei, Y. Deadbeat Predictive Current Control of Permanent-Magnet Synchronous Motors with Stator Current and Disturbance Observer. IEEE Trans. Power Electron. 2017, 32, 3818–3834. [Google Scholar] [CrossRef]

- Türker, T.; Buyukkeles, Y.; Bakan, A.F. A Robust Predictive Current Controller for PMSM Drives. IEEE Trans. Ind. Electron. 2016, 63, 3906–3914. [Google Scholar] [CrossRef]

- Liu, X.; Yu, H.; Yu, J.; Zhao, L. Combined Speed and Current Terminal Sliding Mode Control With Nonlinear Disturbance Observer for PMSM Drive. IEEE Access 2018, 6, 29594–29601. [Google Scholar] [CrossRef]

- Wang, L.; Chai, T.; Zhai, L. Neural-Network-Based Terminal Sliding-Mode Control of Robotic Manipulators Including Actuator Dynamics. IEEE Trans. Ind. Electron. 2009, 56, 3296–3304. [Google Scholar] [CrossRef]

- Qu, L.; Qiao, W. Active-Disturbance-Rejection-Based Sliding-Mode Current Control for Permanent-Magnet Synchronous Motors. IEEE Trans. Power Electron. 2021, 36, 751–760. [Google Scholar] [CrossRef]

- Chen, W. Indirect Input-Series Output-Parallel DC–DC Full Bridge Converter System Based on Asymmetric Pulse width Modulation Control Strategy. IEEE Trans. Power Electron. 2019, 34, 3164–3177. [Google Scholar] [CrossRef]

- Li, C.; Zhang, Y.; Cao, Z.; XU, D. Single-Phase Single-Stage Isolated ZCS Current-Fed Full-Bridge Converter for High-Power AC/DC Applications. IEEE Trans. Power Electron. 2017, 32, 6800–6812. [Google Scholar] [CrossRef]

- Kulasekaran, S.; Ayyanar, R. Analysis, Design, and Experimental Results of the Semidual-Active-Bridge Converter. IEEE Trans. Power Electron. 2014, 29, 5136–5147. [Google Scholar] [CrossRef]

- Jin, H.; Chen, Y.; Lan, W. Replacing PI Control With First-Order Linear ADRC. In Proceedings of the 2019 IEEE 8th Data Driven Control and Learning Systems Conference (DDCLS), Dali, China, 24–27 May 2019. [Google Scholar]

- Tian, G.; Gao, Z. Frequency Response Analysis of Active Disturbance Rejection Based Control System. In Proceedings of the 2007 IEEE International Conference on Control Applications, Singapore, 1–3 October 2007. [Google Scholar]

| System Parameters | Symbols | Value |

| Input side DC voltage | 300 V | |

| Input side capacitor | 2350 | |

| Leakage induction of transformer | 10 | |

| Transformer ratio reciprocal | 36 | |

| Output side line impedance | 50 | |

| Output side inductor | 1.0 | |

| Output side capacitor | 10 | |

| Control Parameters | Symbols | Value |

| Proportional gain | 20 | |

| Integral gain | 100 | |

| Controller bandwidth | 500 | |

| Observer bandwidth | 1000 | |

| Compensation factor | 10 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kang, Z.; Li, Y. Active Disturbance Rejection Control of Full-Bridge DC–DC Converter for a Pulse Power Supply with Controllable Charging Time. Electronics 2023, 12, 5018. https://doi.org/10.3390/electronics12245018

Kang Z, Li Y. Active Disturbance Rejection Control of Full-Bridge DC–DC Converter for a Pulse Power Supply with Controllable Charging Time. Electronics. 2023; 12(24):5018. https://doi.org/10.3390/electronics12245018

Chicago/Turabian StyleKang, Zhongjian, and Yuntong Li. 2023. "Active Disturbance Rejection Control of Full-Bridge DC–DC Converter for a Pulse Power Supply with Controllable Charging Time" Electronics 12, no. 24: 5018. https://doi.org/10.3390/electronics12245018