Design of a 0.4 V, 8.43 ENOB, 5.29 nW, 2 kS/s SAR ADC for Implantable Devices

Abstract

:1. Introduction

2. SAR ADC Architecture

3. Implementation of Key CMOS Blocks

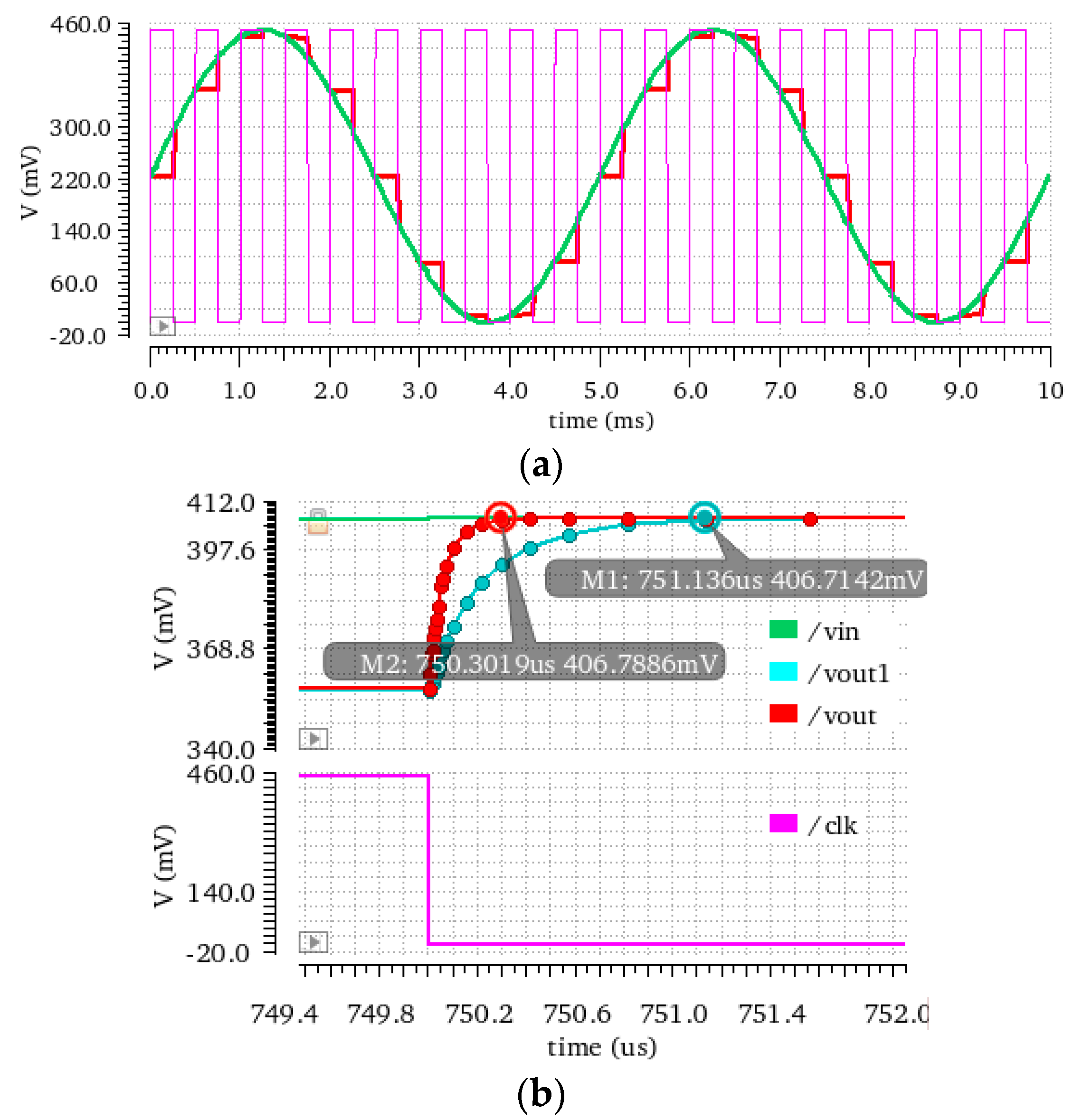

3.1. Proposed Bootstrap Switch

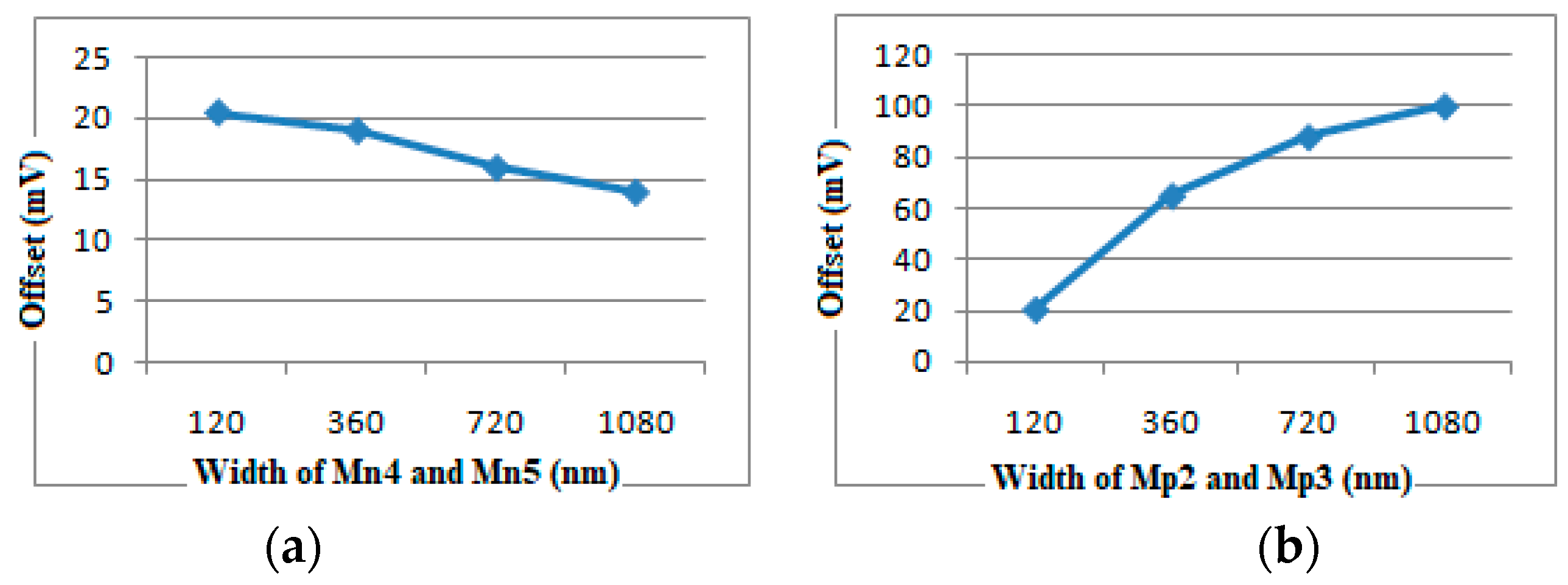

3.2. Dynamic Comparator

- Increasing the transistor sizes of the differential pair;

- Matched capacitors can be added at the output nodes to reduce the relative mismatch;

- Constant current can be generated into the output nodes.

3.3. Modified Distributed Attenuation Capacitor Split-Capacitive DAC

3.4. SAR Logic

4. Simulation Results of the Proposed ADC

4.1. Static Performance

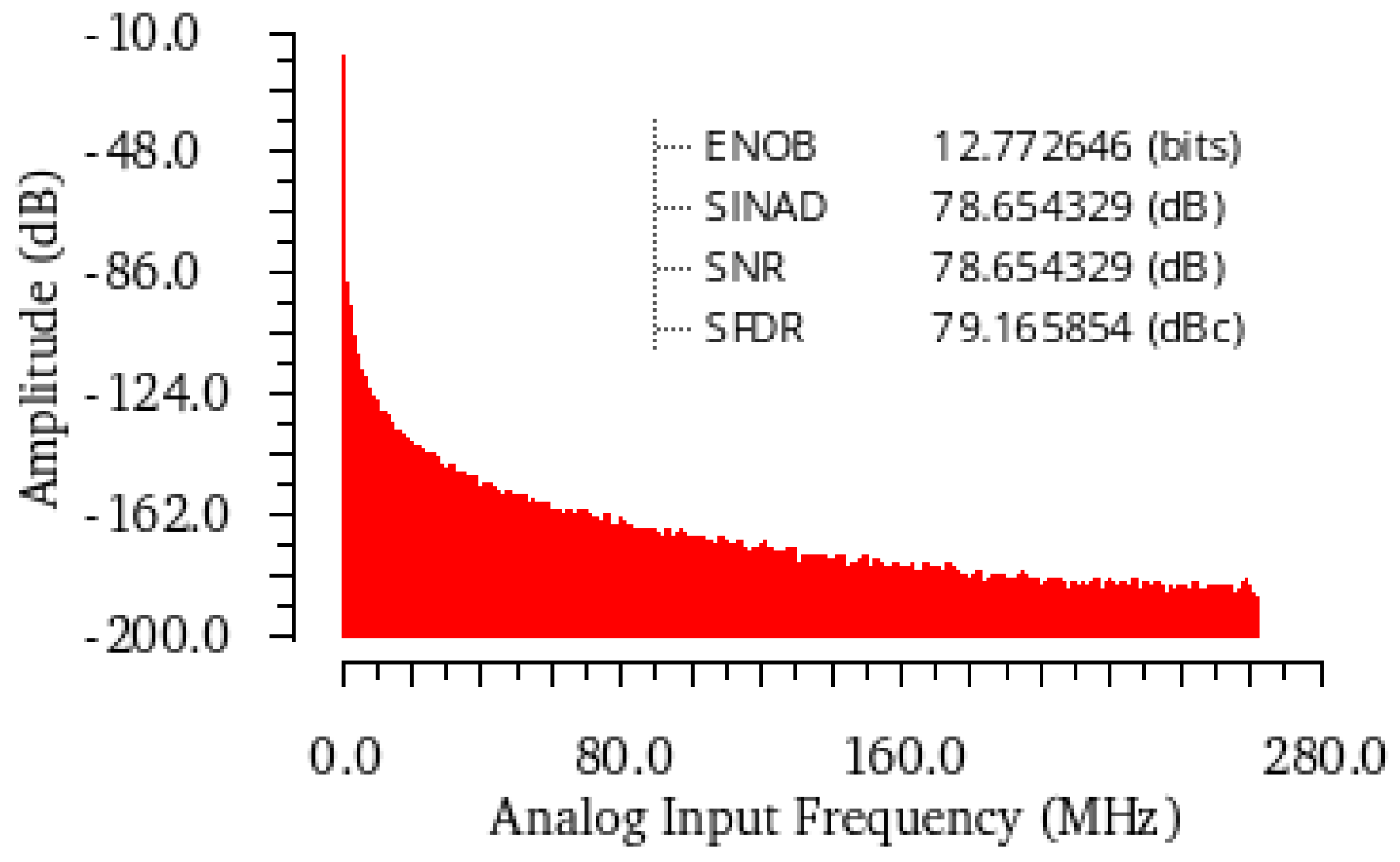

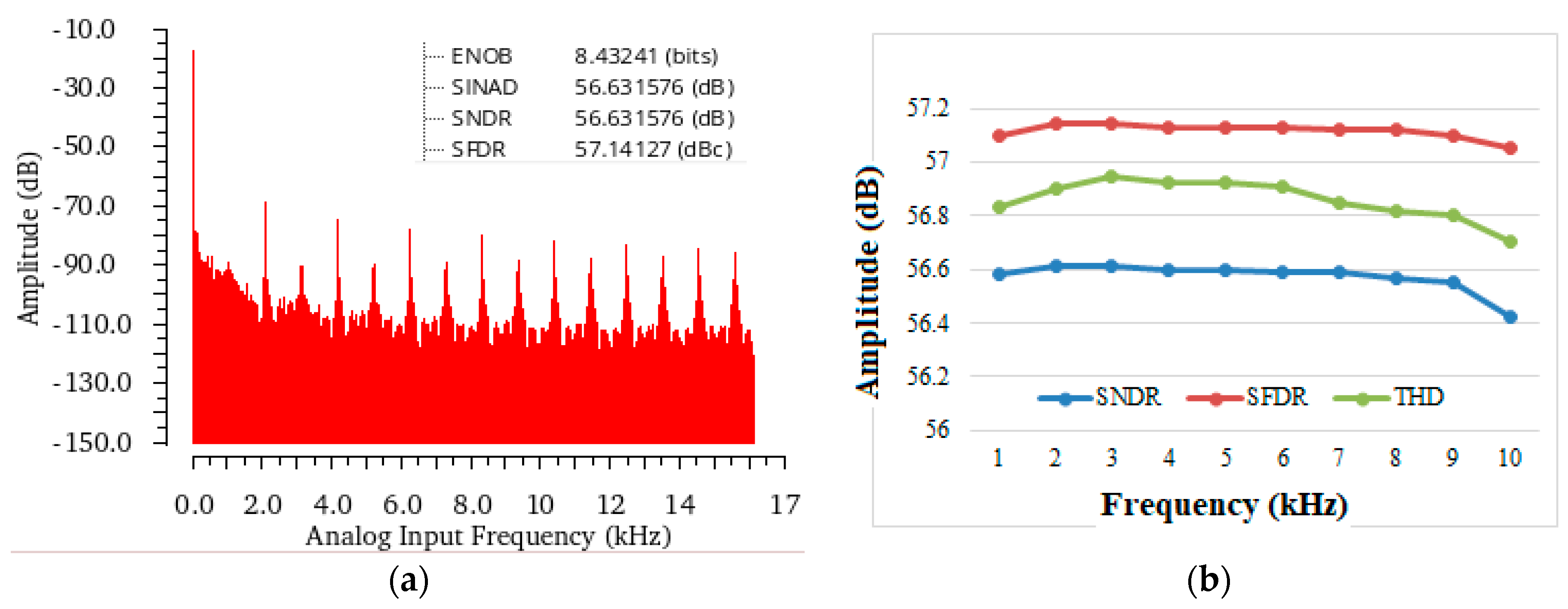

4.2. Dynamic Performance

4.3. Power Performance

5. Conclusions

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Gregoire, B.R.; Musah, T.; Maghari, N.; Weaver, S.; Moon, U. A 30% beyond VDD signal swing 9-ENOB pipelined ADC using a 1.2V 30dB loop-gain opamp. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Jeju, Republic of Korea, 14–16 November 2011; pp. 345–348. [Google Scholar] [CrossRef]

- Maghari, N.; Moon, U. A Third-Order DT ∆Ʃ Modulator Using Noise-Shaped Bi-Directional Single-Slope Quantizer. IEEE J. Solid-State Circuits 2011, 46, 2882–2891. [Google Scholar] [CrossRef]

- Chahardori, M.; Sharifkhani, M.; Sadughi, S. A 4-Bit, 1.6 GS/s Low Power Flash ADC, Based on Offset Calibration and Segmentation. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2285–2297. [Google Scholar] [CrossRef]

- Huang, G.; Chang, S.; Liu, C.; Lin, Y. A 1-µW 10-bit 200-kS/s SAR ADC With a Bypass Window for Biomedical Applications. IEEE J. Solid-State Circuits 2012, 47, 2783–2795. [Google Scholar] [CrossRef]

- Navidi, S.M.; Ehsanian, M. A 9-bit Low-Power Fully Differential SAR ADC Using Adaptive Supply and Reference Voltages. In Proceedings of the Iranian Conference on Electrical Engineering (ICEE), Mashhad, Iran, 8–10 May 2018; pp. 205–210. [Google Scholar] [CrossRef]

- Yaul, F.M.; Chandrakasan, A.P. 11.3 A 10b 0.6nW SAR ADC with data-dependent energy savings using LSB-first successive approximation. In Proceedings of the International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 198–199. [Google Scholar] [CrossRef]

- Yadav, K.; Patra, P.; Dutta, A. A 43-nW 10-bit 1-kS/s SAR ADC in 180nm CMOS for biomedical applications. In Proceedings of the Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), Hyderabad, India, 27–29 November 2015; pp. 21–25. [Google Scholar] [CrossRef]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 0.92mW 10-bit 50-MS/s SAR ADC in 0.13μm CMOS process. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2009; pp. 236–237. [Google Scholar]

- Chen, Y.; Zhu, X.; Tamura, H.; Kibune, M.; Tomita, Y.; Hamada, T.; Yoshioka, M.; Ishikawa, K.; Takayama, T.; Ogawa, J.; et al. Split capacitor DAC mismatch calibration in successive approximation ADC. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 13–16 September 2009; pp. 279–282. [Google Scholar] [CrossRef]

- Baker, R.J. CMOS: Circuit Design, Layout and Simulation; John Wiley & Sons: Hoboken, NJ, USA, 2011; Volume 18. [Google Scholar]

- Maloberti, F. Data Converters 1; Springer: Berlin/Heidelberg, Germany, 2007; Available online: www.springer.com/gp/book/9780387324852 (accessed on 31 January 2023).

- Osipov, D.; Guscv, A.; Paul, S. By Design Correction of Capacitors Mismatch in SAR ADC with Split Capacitor DAC. In Proceedings of the 2021 IEEE 32nd International Conference on Microelectronics (MIEL), Nis, Serbia, 12–14 September 2021; pp. 209–212. [Google Scholar] [CrossRef]

- Nazari, M.; Aghajani, A.; Hashemipour, O. Design of a new split-capacitive-array DAC based on distribution of attenuation capacitor. In Proceedings of the 23rd Iranian Conference on Electrical Engineering, Tehran, Iran, 10–14 May 2015; pp. 1370–1373. [Google Scholar] [CrossRef]

- Segantini, M.; Parmeggiani, M.; Ballesio, A.; Palmara, G.; Frascella, F.; Marasso, S.L.; Cocuzza, M. Design of a Portable Microfluidic Platform for EGOT-Based in Liquid Biosensing. Sensors 2022, 22, 969. [Google Scholar] [CrossRef] [PubMed]

- Tran, D.P.; Pham, T.T.T.; Wolfrum, B.; Offenhäusser, A.; Thierry, B. CMOS-Compatible Silicon Nanowire Field-Effect Transistor Biosensor: Technology Development toward Commercialization. Materials 2018, 11, 785. [Google Scholar] [CrossRef]

- Hamza, M.N.; Abdulkarim, Y.I.; Saeed, S.R.; Altıntaş, O.; Mahmud, R.H.; Appasani, B.; Ravariu, C. Low-Cost Antenna-Array-Based Metamaterials for Non-Invasive Early-Stage Breast Tumor Detection in the Human Body. Biosensors 2022, 12, 828. [Google Scholar] [CrossRef] [PubMed]

- Zhang, M.; Adkins, M.; Wang, Z. Recent Progress on Semiconductor-Interface Facing Clinical Biosensing. Sensors 2021, 21, 3467. [Google Scholar] [CrossRef]

- Angotzi, G.N.; Boi, F.; Lecomte, A.; Miele, E.; Malerba, M.; Zucca, S.; Casile, A.; Berdondini, L. SiNAPS: An implantable active pixel sensor CMOS-probe for simultaneous large-scale neural recordings. Biosens. Bioelectron. 2019, 126, 355–364. [Google Scholar] [CrossRef]

- Harpaz, D.; Alkan, N.; Eltzov, E. The Incorporation of Amplified Metal-Enhanced Fluorescence in a CMOS-Based Biosensor Increased the Detection Sensitivity of a DNA Marker of the Pathogenic Fungus Colletotrichum gloeosporioides. Biosensors 2020, 10, 204. [Google Scholar] [CrossRef]

- Martínez-Pérez-Cejuela, H.; Calabretta, M.M.; Bocci, V.; D’Elia, M.; Michelini, E. Super-Stable Metal–Organic Framework (MOF)/Luciferase Paper-Sensing Platform for Rapid ATP Detection. Biosensors 2023, 13, 451. [Google Scholar] [CrossRef]

- Zhu, Z.; Liang, Y. A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18-µm CMOS for Medical Implant Devices. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2167–2176. [Google Scholar] [CrossRef]

- He, J.; Zhan, S.; Chen, D.; Geiger, R.L. Analyses of Static and Dynamic Random Offset Voltages in Dynamic Comparators. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 911–919. [Google Scholar] [CrossRef]

- Yu, L.; Wang, X.; Wang, L. A low-power fully differential reconfigurable biomedical electronics interface to detect heart signals. In Proceedings of the Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), Shanghai, China, 22–24 September 2010; pp. 400–403. [Google Scholar] [CrossRef]

- Chen, H.; He, L.; Deng, H.; Yin, Y.; Lin, F. A high-performance bootstrap switch for low voltage switched-capacitor circuits. In Proceedings of the IEEE International Symposium on Radio-Frequency Integration Technology, Hefei, China, 27–30 August 2014; pp. 1–3. [Google Scholar] [CrossRef]

- Liu, S.; Shen, Y.; Zhu, Z. A 12-Bit 10 MS/s SAR ADC With High Linearity and Energy-Efficient Switching. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1616–1627. [Google Scholar] [CrossRef]

- Babayan-Mashhadi, S.; Lotfi, R. Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 343–352. [Google Scholar] [CrossRef]

- Gao, J.; Li, G.; Li, Q. High-speed low-power common-mode insensitive dynamic comparator. Electron. Lett. 2015, 51, 134–136. [Google Scholar] [CrossRef]

- Diaz-Madrid, J.A.; Domenech-Asensi, G.; Hauer, J.; Mateu, L. A low kickback fully differential dynamic comparator for pipeline analog-to-digital converters. Eng. Rep. 2019, 1, e12055. [Google Scholar] [CrossRef]

- Rodrigues, S.; Bhat, M.S. Impact of Process Variation Induced Transistor Mismatch on Sense Amplifier Performance. In Proceedings of the International Conference on Advanced Computing and Communications, Surathkal, Mangalore, India, 20–23 December 2006; pp. 497–502. [Google Scholar] [CrossRef]

- Pinto, A.; Fernandes, J.D.S.R. A Study on the Offset Voltage of Dynamic Comparators. Des. Circuits Integr. Syst. 2012, 347–352. [Google Scholar]

- Hu, J.; Li, D.; Liu, M.; Zhu, Z. A 10-kS/s 625-Hz-Bandwidth 65-dB SNDR Second-Order Noise-Shaping SAR ADC for Biomedical Sensor Applications. IEEE Sens. J. 2020, 20, 13881–13891. [Google Scholar] [CrossRef]

- Yan, N.; Kang, C.; Mu, G.; Chen, S.; Wang, M.; Min, H. A 10-bit 16-MS/s Ultra Low Power SAR ADC for IoT Applications. In Proceedings of the 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Qingdao, China, 31 October–3 November 2018; pp. 1–3. [Google Scholar] [CrossRef]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Akbari, M.; Hashemipour, O.; Nazari, M.; Moradi, F. A charge sharing–based switching scheme for SAR ADCs. Int. J. Circuit Theory Appl. 2019, 47, 1188–1198. [Google Scholar] [CrossRef]

- Rahimi, E.; Yavari, M. Energy-efficient high-accuracy switching method for SAR ADCs. Electron. Lett. 2014, 50, 499–501. [Google Scholar] [CrossRef]

- Zhu, Z.; Xiao, Y.; Wang, W. A 0.6 V 100 kS/s 8–10b resolution configurable SAR ADC in 0.18μm CMOS. Analog. Integr. Circuits Signal Process 2013, 75, 335–342. [Google Scholar] [CrossRef]

- Guo, W.; Zhu, Z. A 0.3 V 8-bit 8.9 fJ/con.-step SAR ADC with sub-DAC merged switching for bio-sensors. Microelectron. J. 2017, 68, 44–54. [Google Scholar] [CrossRef]

- Chen, W.; Zeng, Y.; Li, Z.; Yang, J.; Li, Y. A 41-nW SAR ADC with a FIA-based Comparator and a Bulk-driven Latch for ECG Applications. In Proceedings of the 2022 IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), Shenzhen, China, 11–13 November 2022; pp. 54–58. [Google Scholar] [CrossRef]

- Rosòŀ, M.; Kmon, P. 8-bit Low-Power, Low-Area SAR ADC for Biomedical Multichannel Integrated Recording System in CMOS 40nm. In Proceedings of the 2022 29th International Conference on Mixed Design of Integrated Circuits and System (MIXDES), Wrocław, Poland, 23–24 June 2022; pp. 63–67. [Google Scholar] [CrossRef]

- Narasimaiah, J.D.; Bhat, M.S. 14.5 fJ/conversion-step 9-bit 100-kS/s non-binary weighted dual capacitor array based area and energy efficient SAR ADC in 90 nm CMOS. IET Circuits Devices Syst. 2018, 12, 671–680. [Google Scholar] [CrossRef]

- Sekimoto, R.; Shikata, A.; Yoshioka, K.; Kuroda, T.; Ishikuro, H. A 0.5-V 5.2-fJ/Conversion-Step Full Asynchronous SAR ADC With Leakage Power Reduction Down to 650 pW by Boosted Self-Power Gating in 40-nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 2628–2636. [Google Scholar] [CrossRef]

- Sekimoto, R.; Shikata, A.; Kuroda, T.; Ishikuro, H. A 40nm 50S/s–8MS/s ultra low voltage SAR ADC with timing optimized asynchronous clock generator. In Proceedings of the ESSCIRC (ESSCIRC), Helsinki, Finland, 12–16 September 2011; pp. 471–474. [Google Scholar] [CrossRef]

- Hu, W.; Liu, Y.; Nguyen, T.; Lie, D.C.; Ginsburg, B.P. An 8-Bit Single-Ended Ultra-Low-Power SAR ADC with a Novel DAC Switching Method and a Counter-Based Digital Control Circuitry. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1726–1739. [Google Scholar] [CrossRef]

- Tang, H.; Sun, Z.C.; Chew, K.W.R.; Siek, L. A 5.8 nW 9.1-ENOB 1-kS/s Local Asynchronous Successive Approximation Register ADC for Implantable Medical Device. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 2221–2225. [Google Scholar] [CrossRef]

- Sailakshmi, T.; Srinivasulu, A.; Bizon, N. A Power Efficient 5-bit 5-GS/s Parallel Comparator Analogue-To-Digital Converter. In Proceedings of the IEEE International Conference on Electronics, Computers and Artificial Intelligence, Isai, Romania, 28 June–1 July 2018; p. 6. [Google Scholar] [CrossRef]

- Sailakshmi, T.; Srinivasulu, A.; Shaker, P.C. Implementation of power efficient flash Analogue-to-Digital Converter, Active and Passive Electronic Components. Int. J. 2014, 2014, 723053. [Google Scholar] [CrossRef]

| Mp1 | Mp2, Mp3 | Mn2, Mn3 | Mn4, Mn5 | Mn1 | |

|---|---|---|---|---|---|

| W (nm) | 120 | 240 | 120 | 1000 | 120 |

| L (nm) | 45 | 45 | 45 | 45 | 45 |

| S. No. | [33] | [21] | [32] | [31] | Proposed |

|---|---|---|---|---|---|

| Technology (nm) | 45 | 45 | 45 | 45 | 45 |

| Supply Voltage (V) | 0.4 | 0.4 | 0.4 | 0.4 | 0.4 |

| No. of Transistors | 12 | 17 | 13 | 23 | 8 |

| Offset Voltage (mV) | 35.6 | 25 | 43 | 42 | 20 |

| Kickback Noise (mV) | 3.37 | 2.99 | 2.5 | 1.3 | 2 |

| Power (nW) | 6.77 | 4.6 | 1.97 | 10 | 1.07 |

| Leakage power (W) | 384 p | 1.33 n | 1.04 n | 33.2 p | 51.4 p |

| Delay (ns) | 15.14 | 6.75 | 5.15 | 15 | 7.16 |

| Binary Code | Thermometer Code | |||

|---|---|---|---|---|

| D2 | D1 | T3 | T2 | T1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 |

| Binary Code | New Code | |||

|---|---|---|---|---|

| D2 | D1 | C3 | C2 | C1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 |

| Reference | Leakage Power (pW) |

|---|---|

| [36] | 56.08 |

| [37] | 41.8 |

| Modified | 38.4 |

| Technology | 45 nm |

| Power Supply | 0.4 V |

| Reference Voltage | 0.2 V |

| DAC Size | 620 fF |

| SAR logic complexity | 271 transistors |

| Unit Capacitor | 20 fF |

| Input Range | [0, 0.4] V |

| DNL | −0.10/+0.13 LSB |

| INL | −0.8/+0.5 LSB |

| ENOB | 8.43 bits @ 2 kS/s |

| SNDR | 56.63 dB |

| SFDR | 57.14 dB |

| Power | 5.29 nW |

| Leakage Power | 1.5 nW |

| FOM | 7.66 fJ/conv.step @ 2 kS/s |

| [25] 2016 | [27] 2015 | [28] 2019 | [29] 2006 | [30] 2012 | [33] 2010 | [31] 2020 | [38] 2022 | Proposed | |

|---|---|---|---|---|---|---|---|---|---|

| Technology (nm) | 180 | 90 | 40 | 40 | 180 | 65 | 180 | 180 | 45 |

| Result | Sim. | Sim. | Fab. | Fab. | Fab. | Fab. | Fab. | Sim. | Sim. |

| Resolution (bit) | 9 | 9 | 9 | 9 | 8 | 10 | 8 | 10 | 9 |

| Supply (V) | 0.6 | 1 | 0.4 | 0.6 | 1.1 | 0.9 | 1 | 0.6 | 0.4 |

| Sampling Rate (kS/s) | 100 | 100 | 1 | 1 | 2 | 1 | 10 | 10 | 2 |

| Power (nW) | 399 | 473 | 1.8 | 130 | 27 | 5.8 | 90 | 41 | 5.29 |

| DNL (LSB) | - | +0.8/−0.6 | +0.36/−0.35 | +0.8/−0.65 | +0.28/−0.17 | +0.59/−0.62 | - | - | +0.13/−0.10 |

| INL (LSB) | - | +0.5/−0.7 | +0.44/−0.35 | +0.85/−0.6 | +0.81/−0.27 | +0.89/−0.41 | - | - | +0.5/−0.8 |

| SNDR (dB) | 53.5 | 53.55 | 50.1 | - | 46.3 | 56.5 | 65 | 61 | 56.63 |

| SFDR (dB) | 61.7 | 60.16 | 59.5 | - | 61.9 | 75.3 | 69 | 57.14 | |

| ENOB (bit) | 8.59 | 8.35 | 7.9 | 7.6 | 7.4 | 9.1 | 7 | 10 | 8.43 |

| FOM (fJ/conv.step) | 10.4 | 14.5 | 7.7 | 666 | 79.9 | 10.94 | 50 | 4.14 | 7.66 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lakshmi, P.V.; Musala, S.; Srinivasulu, A.; Ravariu, C. Design of a 0.4 V, 8.43 ENOB, 5.29 nW, 2 kS/s SAR ADC for Implantable Devices. Electronics 2023, 12, 4691. https://doi.org/10.3390/electronics12224691

Lakshmi PV, Musala S, Srinivasulu A, Ravariu C. Design of a 0.4 V, 8.43 ENOB, 5.29 nW, 2 kS/s SAR ADC for Implantable Devices. Electronics. 2023; 12(22):4691. https://doi.org/10.3390/electronics12224691

Chicago/Turabian StyleLakshmi, Posani Vijaya, Sarada Musala, Avireni Srinivasulu, and Cristian Ravariu. 2023. "Design of a 0.4 V, 8.43 ENOB, 5.29 nW, 2 kS/s SAR ADC for Implantable Devices" Electronics 12, no. 22: 4691. https://doi.org/10.3390/electronics12224691