Ultra High-Density SOT-MRAM Design for Last-Level On-Chip Cache Application

Abstract

:1. Introduction

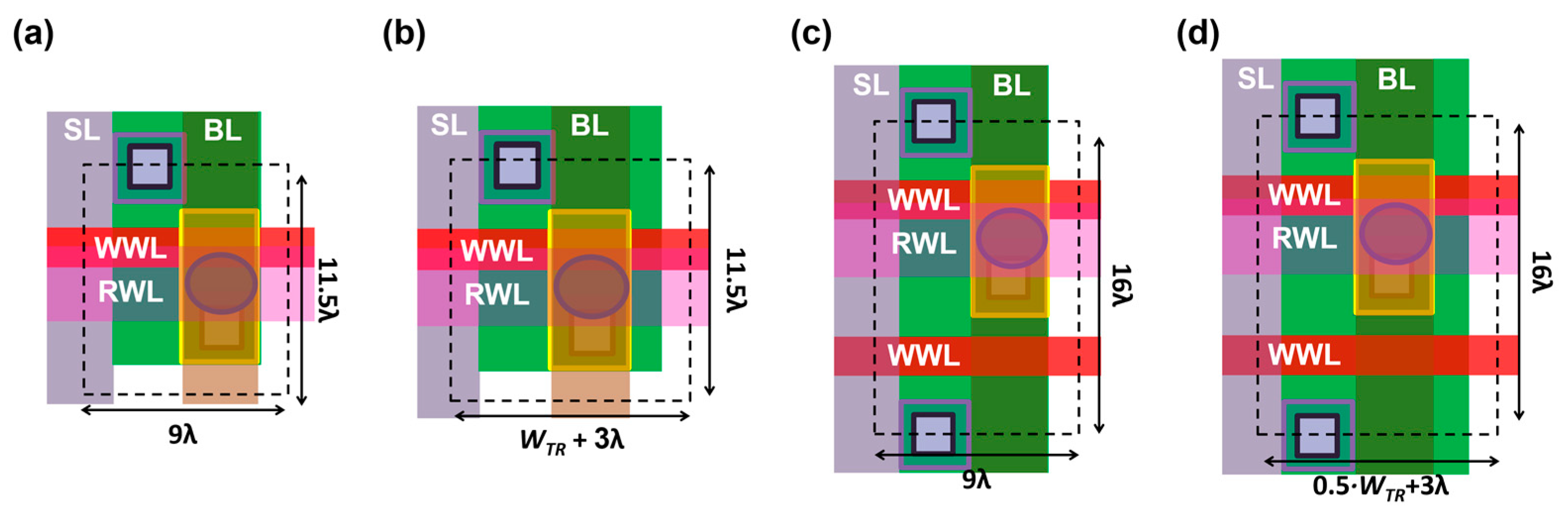

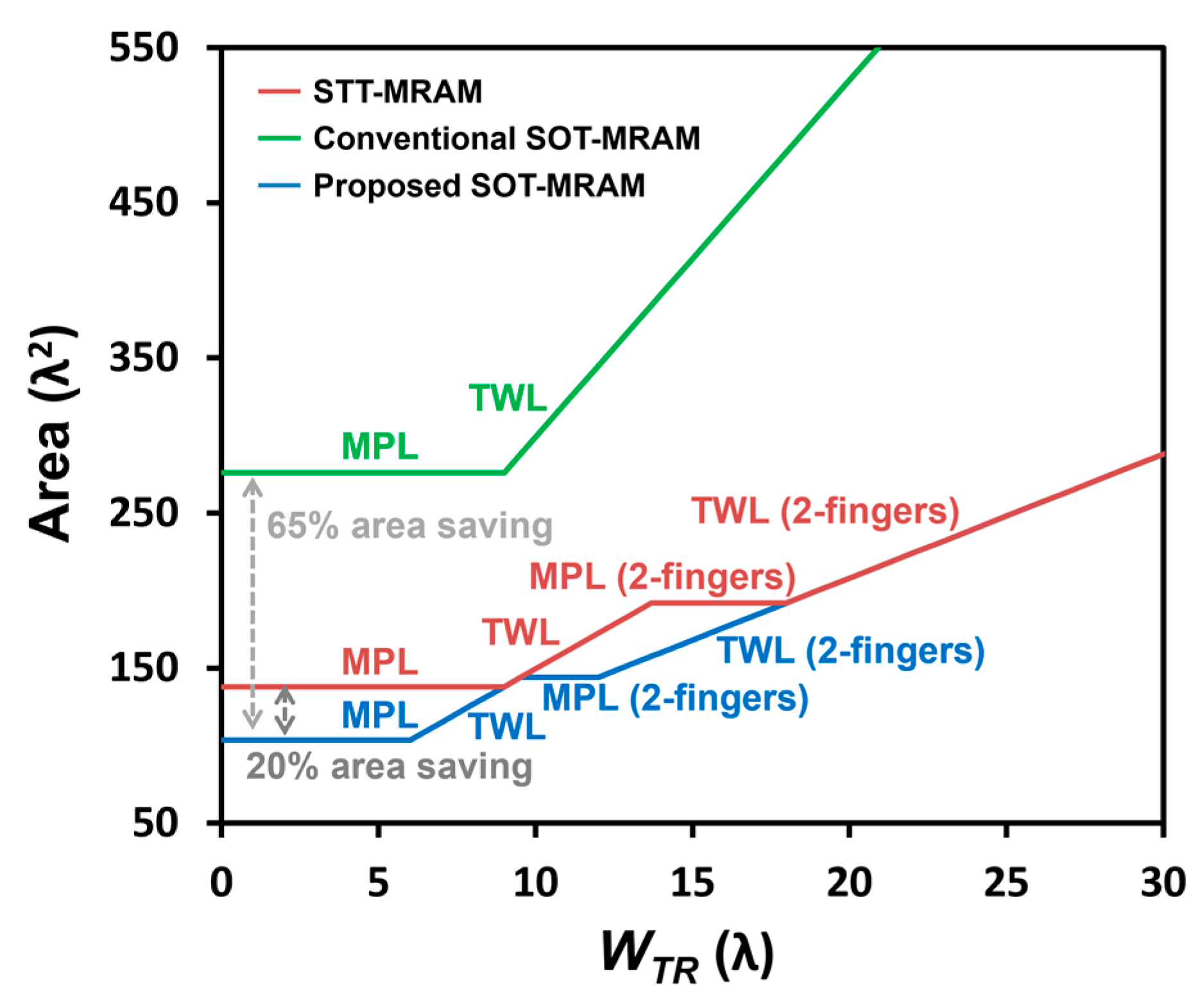

2. Conventional SOT-MRAM Design

3. Proposed SOT-MRAM Design

4. Simulations and Results

- The simulation program integrated circuit emphasis (SPICE) simulator modeled the MRAM bit-cells.

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, Y.; Kang, W.; Zhou, K.; Qiu, K.; Zhao, W. Experimental Demonstration of STT-MRAM-based Nonvolatile Instantly On/Off System for IoT Applications: Case Studies. ACM Trans. Embed. Comput. Syst. 2023, 22, 1–24. [Google Scholar] [CrossRef]

- Yazigy, N.; Postel-Pellerin, J.; Della Marca, V.; Terziyan, K.; Sousa, R.C.; Canet, P.; Di Pendina, G. Real-Time Switching Dynamics in STT-MRAM. IEEE J. Electron Devices Soc. 2022, 10, 490–494. [Google Scholar] [CrossRef]

- Chun, K.C.; Zhao, H.; Harms, J.D.; Kim, T.-H.; Wang, J.-P.; Kim, C.H. A scaling roadmap and performance evaluation of in-plane and perpendicular mtj based stt-mrams for high-density cache memory. IEEE J. Solid-State Circuits 2013, 48, 598–610. [Google Scholar] [CrossRef]

- Augustine, C.; Mojumder, N.; Fong, X.; Choday, H.; Park, S.P.; Roy, K. STT-MRAMs for future universal memories: Perspective and prospective. In Proceedings of the 2012 28th International Conference on Microelectronics Proceedings, Nis, Serbia, 13–16 May 2012; pp. 349–355. [Google Scholar] [CrossRef]

- Seo, Y.; Kwon, K.-W. Area Optimization Techniques for High-Density Spin-Orbit Torque MRAMs. Electronics 2021, 10, 792. [Google Scholar] [CrossRef]

- Wang, C.-Y.; Shih, M.-C.; Weng, C.-H.; Chen, C.-H.; Chang, C.-Y.; Wang, W.; Chiang, T.W.; Hung, A.; Chuang, H.; Gallagher, W.J. Reliability demonstration of reflow qualified 22 nm stt-mram for embedded memory applications. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; p. TM3.2. [Google Scholar] [CrossRef]

- Li, J.; Ndai, P.; Goel, A.; Salahuddin, S.; Roy, K. Design Paradigm for Robust Spin-Torque Transfer Magnetic RAM (STT MRAM) From Circuit/Architecture Perspective. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2009, 18, 1710–1723. [Google Scholar] [CrossRef]

- Sun, G.; Dong, X.; Xie, Y.; Li, J.; Chen, Y. A novel architecture of the 3D stacked MRAM L2 cache for CMPs. In Proceedings of the 2009 IEEE 15th International Symposium on High Performance Computer Architecture, Raleigh, NC, USA, 14–18 February 2009; pp. 239–249. [Google Scholar]

- Fong, X.; Kim, Y.; Choday, S.H.; Roy, K. Failure Mitigation Techniques for 1T-1MTJ Spin-Transfer Torque MRAM Bit-cells. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 384–395. [Google Scholar] [CrossRef]

- Lin, C.; Kang, S.; Wang, Y.; Lee, K.; Zhu, X.; Li, X.; Hsu, W.; Kao, Y.; Liu, M.; Chen, W.; et al. 45nm low power CMOS logic compatible embedded STT MRAM utilizing a reverse-connection 1T/1MTJ cell. In Proceedings of the IEEE International Electron Devices Meeting, Baltimore, MD, USA, 7–9 December 2009; pp. 11.6.1–11.6.4. [Google Scholar] [CrossRef]

- Seo, Y.; Kwon, K.-W.; Fong, X.; Roy, K. High Performance and Energy-Efficient On-Chip Cache Using Dual Port (1R/1W) Spin-Orbit Torque MRAM. IEEE J. Emerg. Sel. Top. Circuits Syst. 2016, 6, 293–304. [Google Scholar] [CrossRef]

- Cai, K.; Talmelli, G.; Fan, K.; Van Beek, S.; Kateel, V.; Gupta, M.; Monteiro, M.; Ben Chroud, M.; Jayakumar, G.; Trovato, A.; et al. First demonstration of field-free perpendicular SOT-MRAM for ultrafast and high-density embedded memories. In Proceedings of the 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2022; pp. 36.2.1–36.2.4. [Google Scholar] [CrossRef]

- Song, M.Y.; Lee, C.M.; Yang, S.Y.; Chen, G.L.; Chen, K.M.; Wang, I.J.; Hsin, Y.C.; Chang, K.T.; Hsu, C.F.; Lin, S.J. High speed (1ns) and low voltage (1.5V) demonstration of 8Kb SOT-MRAM array. In Proceedings of the IEEE Symposium on VLSI Technology and Circuits, Honolulu, HI, USA, 12–17 June 2022; pp. 377–378. [Google Scholar] [CrossRef]

- Kim, T.; Jang, Y.; Kang, M.-G.; Park, B.-G.; Lee, K.-J.; Park, J. SOT-MRAM Digital PIM Architecture With Extended Parallelism in Matrix Multiplication. IEEE Trans. Comput. 2022, 71, 2816–2828. [Google Scholar] [CrossRef]

- Seo, Y.; Kwon, K.-W. Area-optimized design of SOT-MRAM. IEICE Electron. Express 2020, 17, 20200314. [Google Scholar] [CrossRef]

- Manipatruni, S.; Nikonov, D.E.; Young, I.A. Voltage and Energy-Delay Performance of Giant Spin Hall Effect Switching for Magnetic Memory and Logic. arXiv 2013, arXiv:1301.5374. [Google Scholar]

- Pai, C.-F.; Liu, L.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin transfer torque devices utilizing the giant spin Hall effect of tungsten. Appl. Phys. Lett. 2012, 101, 122404. [Google Scholar] [CrossRef]

- Liu, L.; Pai, C.-F.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin-Torque Switching with the Giant Spin Hall Effect of Tantalum. Science 2012, 336, 555–558. [Google Scholar] [CrossRef] [PubMed]

- Cai, K.; Van Beek, S.; Rao, S.; Fan, K.; Gupta, M.; Nguyen, V.D.; Jayakumar, G.; Talmelli, G.; Couet, S.; Kar, G.S. Selective operations of multi-pillar SOT-MRAM for high density and low power embedded memories. In Proceedings of the IEEE Symposium on VLSI Technology and Circuits, Honolulu, HI, USA, 12–17 June 2022; pp. 375–376. [Google Scholar] [CrossRef]

- Endoh, T.; Honjo, H.; Nishioka, K.; Ikeda, S. Recent Progresses in STT-MRAM and SOT-MRAM for Next Generation MRAM. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; p. TMFS.1. [Google Scholar] [CrossRef]

- Natsui, M.; Tamakoshi, A.; Honjo, H.; Watanabe, T.; Nasuno, T.; Zhang, C.; Tanigawa, T.; Inoue, H.; Niwa, M.; Yoshiduka, T.; et al. Dual-Port SOT-MRAM Achieving 90-MHz Read and 60-MHz Write Operations Under Field-Assistance-Free Condition. IEEE J. Solid-State Circuits 2021, 56, 1116–1128. [Google Scholar] [CrossRef]

- Seo, Y.; Kwon, K.-W.; Roy, K. Area-Efficient SOT-MRAM With a Schottky Diode. IEEE Electron Device Lett. 2016, 37, 982–985. [Google Scholar] [CrossRef]

- Jang, Y.; Park, J. Area and energy efficient joint 2T SOT-MRAM-based on diffusion region sharing with adjacent cells. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 1622–1626. [Google Scholar] [CrossRef]

- Hoffmann, A. Spin Hall effects in metals. IEEE Trans. Magn. 2013, 49, 5172–5193. [Google Scholar] [CrossRef]

- Kim, Y.; Fong, X.; Kwon, K.-W.; Chen, M.-C.; Roy, K. Multilevel Spin-Orbit Torque MRAMs. IEEE Trans. Electron Devices 2014, 62, 561–568. [Google Scholar] [CrossRef]

- Gupta, S.K.; Park, S.P.; Mojumder, N.N.; Roy, K. Layout-aware optimization of stt mrams. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition, Dresden, Germany, 12–16 March 2012; pp. 1455–1458. [Google Scholar] [CrossRef]

- Liebmann, L. DfM, the teenage years. In Proceedings of the SPIE Advanced Lithography, San Jose, CA, USA, 24–29 February 2008; Volume 6925, p. 692502. [Google Scholar] [CrossRef]

- Li, Y.T.; Long, S.B.; Lv, H.B.; Liu, Q.; Wang, M.; Xie, H.W.; Zhang, K.W.; Yang, X.Y.; Liu, M. Novel self-compliance Bipolar 1D1R memory device for high-density RRAM application. In Proceedings of the 2013 5th IEEE International Memory Workshop, Monterey, CA, USA, 26–29 May 2013; pp. 184–187. [Google Scholar] [CrossRef]

- Nayak, D.; Acharya, D.P.; Rout, P.K.; Nanda, U. A high stable 8T-SRAM with bit interleaving capability for minimization of soft error rate. Microelectron. J. 2018, 73, 43–51. [Google Scholar] [CrossRef]

- Shi, Y.Q.; Zhang, X.M.; Ni, Z.-C.; Ansari, N. Interleaving for combating bursts of errors. IEEE Circuits Syst. Mag. 2004, 4, 29–42. [Google Scholar] [CrossRef]

- Fong, X.; Gupta, S.K.; Mojumder, N.N.; Choday, S.H.; Augustine, C.; Roy, K. KNACK: A hybrid spin-charge mixed-mode simulator for evaluating different genres of spin-transfer torque MRAM bit-cells. In Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices, Osaka, Japan, 8–10 September 2011; pp. 51–54. [Google Scholar] [CrossRef]

- Slonczewski, J.C. Current-driven excitation of magnetic multilayers. J. Magn. Magn. Mater. 1996, 159, L1–L7. [Google Scholar] [CrossRef]

- Gilbert, T. A phenomenological theory of damping in ferromagnetic materials. IEEE Trans. Magn. 2004, 40, 3443–3449. [Google Scholar] [CrossRef]

- Datta, D.; Behin-Aein, B.; Salahuddin, S.; Datta, S. Quantitative model for TMR and spin-transfer torque in MTJ devices. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 22.8.1–22.8.4. [Google Scholar] [CrossRef]

| Device Parameters | STT Device | SOT Device |

|---|---|---|

| Gilbert damping, α | 0.007 | 0.0122 |

| Saturation magnetization, MS | 1000 × 103 A/m | 1000 × 103 A/m |

| FL dimension (WFL × LFL × tFL) | 120 × 40 × 2 nm a | 120 × 40 × 2 nm a |

| HM dimension (WHM × LHM × tHM) | - | 120 × 80 × 2.5 nm |

| HM resistivity | - | 200 µΩ·cm |

| Spin hall angle, θSH | - | 0.3 |

| Spin flip length, λsf | - | 1.40 nm |

| MgO thickness, tMgO | 1.15 nm | 1.40 nm |

| Critical current for 10-ns switching time | 139 µA | 87 µA |

| STT-MRAM | Conventional SOT-MRAM | Proposed SOT-MRAM | |

|---|---|---|---|

| Transistor width (nm) | 380 | 120 (WTR-R) 120 (WTR-W) | 120 |

| Bit-cell area (µm2) | 0.0800 | 0.1104 | 0.0414 |

| VWRITE (V) | 1.0 | 0.6 | 0.6 |

| VREAD (V) | 0.2 | 0.2 | 0.8 |

| Write power (µW) | 193.48 | 61.08 | 61.07 |

| Read power (µW) | 10.14 | 1.84 | 7.21 |

| Read-disturb margin (%) | 51 | 94 | 95 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seo, Y.; Kwon, K.-W. Ultra High-Density SOT-MRAM Design for Last-Level On-Chip Cache Application. Electronics 2023, 12, 4223. https://doi.org/10.3390/electronics12204223

Seo Y, Kwon K-W. Ultra High-Density SOT-MRAM Design for Last-Level On-Chip Cache Application. Electronics. 2023; 12(20):4223. https://doi.org/10.3390/electronics12204223

Chicago/Turabian StyleSeo, Yeongkyo, and Kon-Woo Kwon. 2023. "Ultra High-Density SOT-MRAM Design for Last-Level On-Chip Cache Application" Electronics 12, no. 20: 4223. https://doi.org/10.3390/electronics12204223