Millimeter-Wave Substrate Integrated Waveguide Using Micromachined Tungsten-Coated Through Glass Silicon Via Structures

Abstract

:1. Introduction

2. Design and Simulation of SIW with Tungsten-Coated TGSVs

2.1. Structure of the SIW

2.2. Design and Simulation of the SIW

3. Fabrication Process

4. Experimental Results and Discussion

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Knickerbocker, J.U.; Andry, P.S.; Dang, B.; Horton, R.R.; Patel, C.S.; Polastre, R.J.; Sakuma, K.; Sprogis, E.S.; Tsang, C.K.; Webb, B.C.; et al. 3D Silicon Integration. In Proceedings of the IEEE 58th Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 538–543. [Google Scholar]

- Sunohara, M.; Tokunaga, T.; Kunihara, T.; Higashi, M. Silicon Interposer with TSVs (Through Silicon Vias) and Fine Multilayer Wiring. In Proceedings of the IEEE 58th Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 847–852. [Google Scholar]

- Töpper, M.; Ndip, I.; Erxleben, R.; Brusberg, L.; Nissen, N.; Schröder, H.; Yamamoto, H.; Todt, G.; Reichl, H. 3-D Thin Film Interposer Based on TGV (Through Glass Vias): An alternative to Si-Interposer. In Proceedings of the IEEE 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 66–73. [Google Scholar]

- Sridharan, V.; Min, S.; Sundaram, V.; Sukumaran, V.; Hwang, S.; Chan, H.; Liu, F.; Nopper, C.; Tummala, R. Design and Fabrication of Bandpass Filters in Glass Interposer with Through-Package-Vias (TPV). In Proceedings of the IEEE 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 530–535. [Google Scholar]

- Sukumaran, V.; Chen, Q.; Liu, F.; Kumbhat, N.; Bandyopadhyay, T.; Chan, H.; Min, S.; Nopper, C.; Sundaram, V.; Tummala, R. Through-Package-Via Formation and Metallization of Glass Interposers. In Proceedings of the IEEE 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 557–563. [Google Scholar]

- Sun, Y.; Yu, D.; Yang, S.; Sun, X.; Zhang, J.; Wei, X.; Wan, L. Development of Through Glass Tungsten Via Interconnect for 3D MEMS Packaging. In Proceedings of the IEEE 13th Electronics Packaging Technology Conference (EPTC), Singapore, 7–9 December 2011; pp. 774–776. [Google Scholar]

- Shorey, A.; Pollard, S.; Streltsov, A.; Piech, G.; Wagner, R. Development of Substrates for Through Glass Vias (TGV) for 3DS-IC Integration. In Proceedings of the IEEE 62nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2012; pp. 289–291. [Google Scholar]

- Lai, W.C.; Chuang, H.H.; Tsai, C.H.; Yeh, E.H.; Lin, C.H.; Peng, T.H.; Yen, L.J.; Liao, W.S.; Hung, J.N.; Sheu, C.C.; et al. 300mm Size Ultra-Thin Glass Interposer Technology and High-Q Embedded Helical Inductor (EHI) for Mobile Application. In Proceedings of the IEEE International Electron Device Meeting (IEDM), Washington, DC, USA, 9–11 December 2013; pp. 357–360. [Google Scholar]

- Kim, J.; Shenoy, R.; Lai, K.-Y.; Kim, J. High-Q 3D RF Solenoid Inductors in Glass. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Tampa, FL, USA, 1–3 June 2014; pp. 199–200. [Google Scholar]

- Yook, J.-M.; Kim, D.; Kim, J.C. High Performance IPDs (Integrated Passive Devices) and TGV (Through Glass Via) Interposer Technology using the Photosensitive Glass. In Proceedings of the IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 41–46. [Google Scholar]

- Ostholt, R.; Ambrosius, N.; Krüger, R.A. High Speed Through Glass Via Manufacturing Technology for Interposer. In Proceedings of the 5th Electronic System-Integration Conference (ESTC), Helsinki, Finland, 16–18 September 2014. [Google Scholar] [CrossRef]

- Yan, J.; Ma, S.; Ma, F.; Xia, Y.; Luo, R.; Jin, Y.; Chen, J. Process Development of Through-Glass-Via (TGV) Interposer for Radio Frequency (RF) Applications. In Proceedings of the IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Chengdu, China, 20–22 July 2016. [Google Scholar] [CrossRef]

- Hwangbo, S.; Shorey, A.B.; Yoon, Y.-K. Millimeter-Wave Intra-/Inter Chip Communications in 3D Integrated Circuits Using Through Glass Via (TGV) Disc-Loaded Patch Antenna. In Proceedings of the IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 2507–2512. [Google Scholar]

- Hwangbo, S.; Fang, S.-P.; An, H.; Yoon, Y.-K.; Shorey, A.B.; Kazmi, A.M. Directional Through Glass Via (TGV) Antennas for Wireless Point-to-Point Interconnects in 3D Integration and Packaging. In Proceedings of the IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 260–265. [Google Scholar]

- Lin, C.-W.; Hsu, C.-P.; Yang, H.-A.; Wang, W.C.; Fang, W. Implementation of Silicon-on-Glass MEMS Devices with Embedded Through-Wafer Silicon Vias Using the Glass Reflow Process for Wafer-Level Packaging and 3D Chip Integration. J. Micromech. Microeng. 2008, 18, 025018. [Google Scholar] [CrossRef]

- Haque, R.M.; Najafi, K. An Intraocular Pressure Sensor Based on a Glass Reflow Process. In Proceedings of the Solid-State Sensors, Actuators, and Microsystems Workshop, Hilton Head, SC, USA, 6–10 June 2010; pp. 49–52. [Google Scholar]

- Lee, J.-Y.; Yoo, S.-H.; Yoo, B.-W.; Kim, Y.-K. A Wafer-Level Vacuum Package Using Glass-Reflowed Silicon Through-Wafer Interconnection for Nano/Micro Devices. J. Nanosci. Nanotechnol. 2012, 12, 5252–5262. [Google Scholar] [CrossRef]

- Deslandes, D.; Wu, K. Single-Substrate Integration Technique of Planar Circuits and Waveguide Filters. IEEE Trans. Microwav. Theory Tech. 2003, 51, 593–596. [Google Scholar] [CrossRef]

- Bozzi, M.; Georgiadis, A.; Wu, K. Review of Substrate-Integrated Waveguide Circuits and Antennas. IET Microw. Antennas Propag. 2011, 5, 909–920. [Google Scholar] [CrossRef]

- Hyeon, I.-J.; Park, W.-Y.; Lim, S.; Baek, C.-W. Fully Micromachined, Silicon-Compatible Substrate Integrated Waveguide for Millimetre-Wave Applications. Electron. Lett. 2011, 47, 328–330. [Google Scholar] [CrossRef]

- Hyeon, I.-J.; Baek, C.-W. Micromachined Substrate Integrated Waveguides with Electroplated Copper Vias in Reflowed Glass Substrate for Millimeter-Wave Applications. Microelectron. Eng. 2015, 131, 19–23. [Google Scholar] [CrossRef]

- Pozar, D.M. Microwave Engineering, 4th ed.; Wiley: Hoboken, NJ, USA, 2011; p. 113. ISBN 978-0-470-63155-3. [Google Scholar]

- Xu, F.; Wu, K. Guided-Wave and Leakage Characteristics of Substrate Integrated Waveguide. IEEE Trans. Microw. Theory Tech. 2005, 53, 66–73. [Google Scholar] [CrossRef]

- Tong, J.; Sundaram, V.; Shorey, A.; Tummala, R. Substrate-Integrated Waveguides in Glass Interposers with Throug-Package-Vias. In Proceedings of the IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 26–29 May 2015; pp. 2222–2227. [Google Scholar]

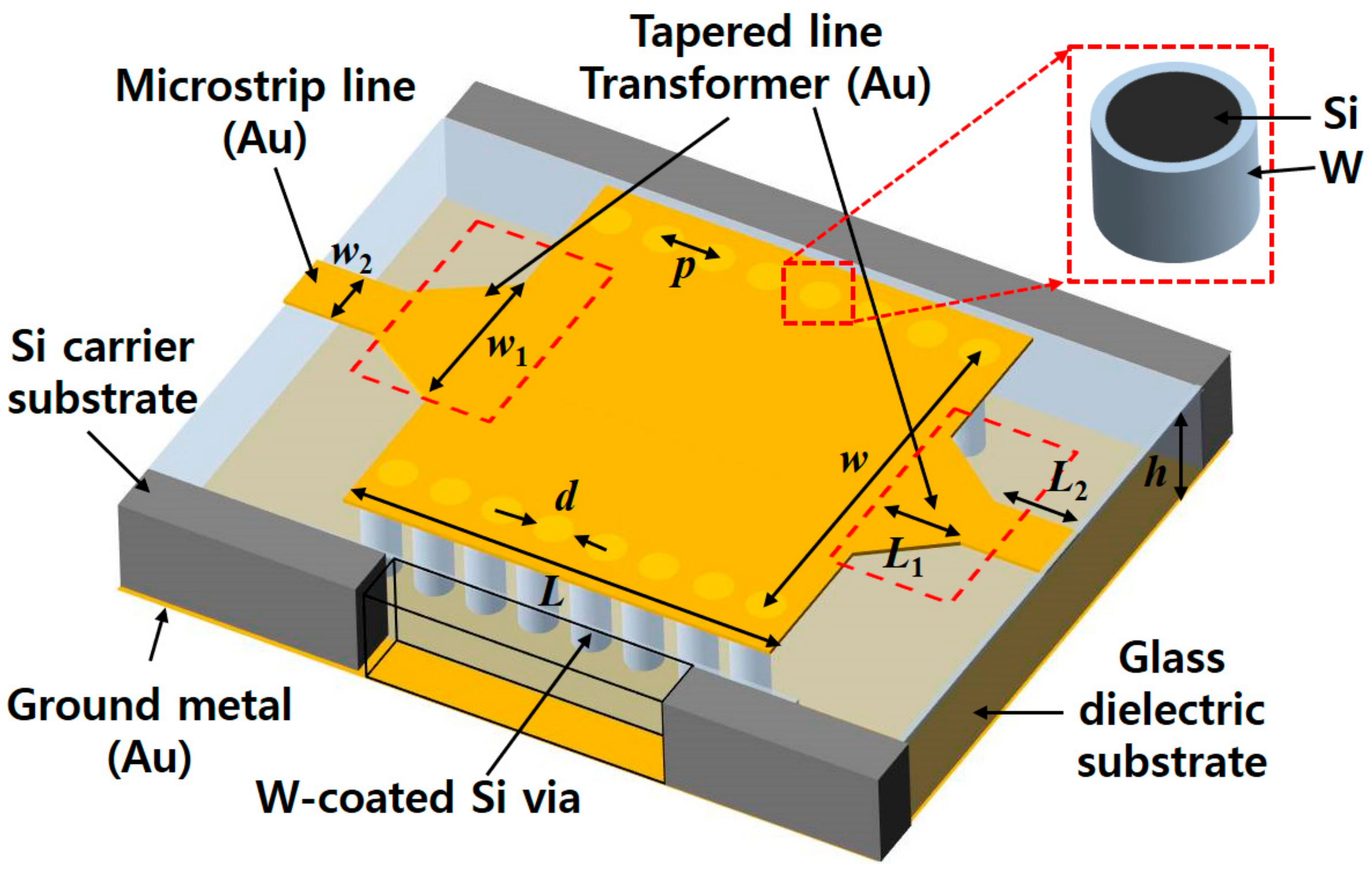

| Parameter | Dimensions [mm] | Description |

|---|---|---|

| d | 0.3 | Diameter of the vias |

| p | 0.4 | (Center-to-center) pitch between the vias |

| w | 4 | Width of the SIW |

| w1 | 1.5 | Larger width of the tapered transformer |

| w2 | 0.5 | Width of the microstrip line |

| L | 4.4 | Lenth of the SIW |

| L1 | 0.8 | Length of the tapered transformer |

| L2 | 0.5 | Length of the microstrip line |

| h | 0.35 | Thickness of the substrate |

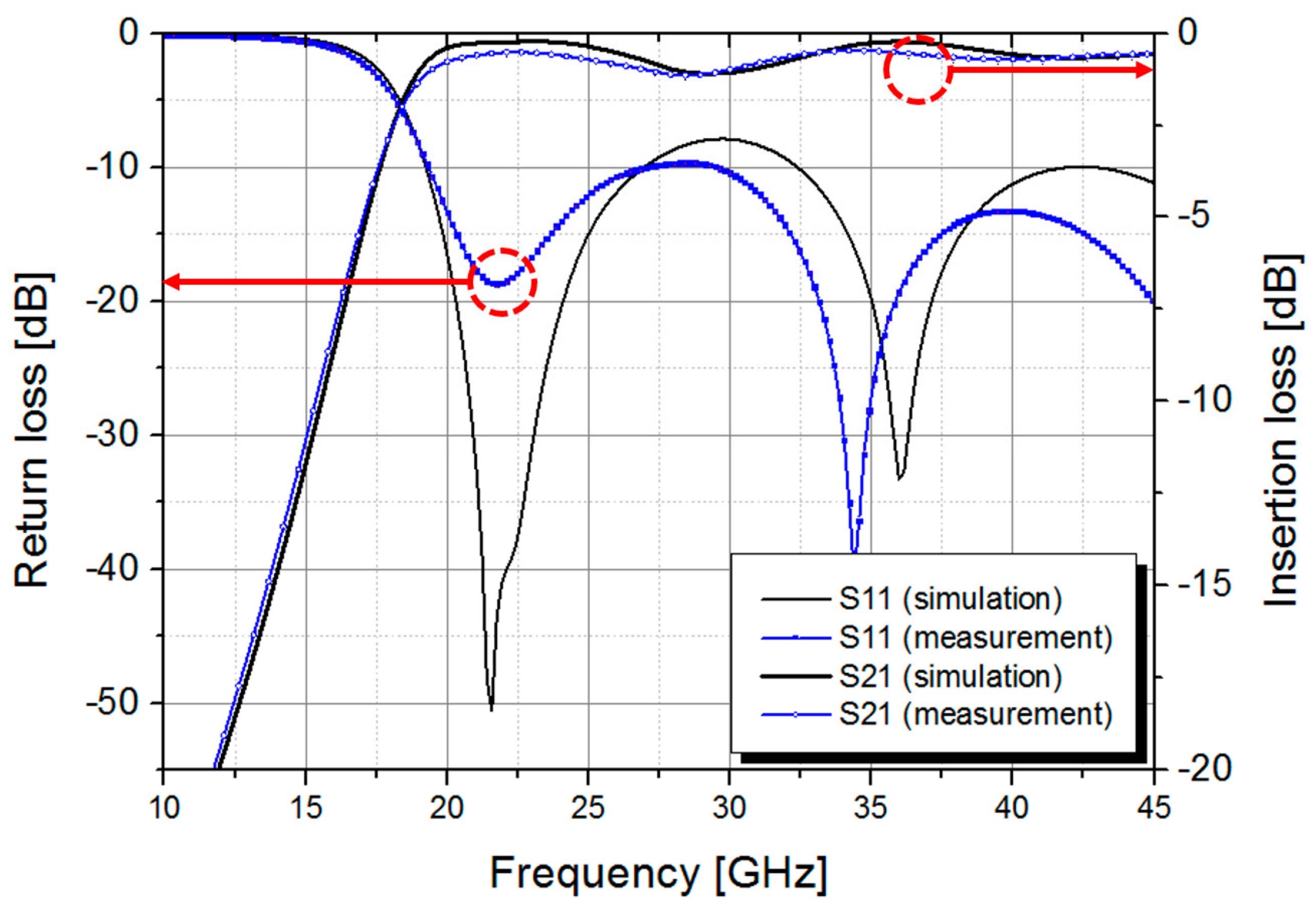

| Reference | Dielectric Material (Thickness [μm]) | Via Material | Frequency [GHz] | Device Length [mm] | Insertion Loss [dB] |

|---|---|---|---|---|---|

| [20] | BCB/400 | Au-Coated Si | 25–40 | 12.6 1 | <1.4 |

| [21] | Borosilicate Glass/350 | Electroplated Cu | 20–45 | 10.0 1 | <0.95 |

| [24] 2 | Boroaluminosilicate Glass/130 | Electroplated Cu 3 | 20 | N/A | 0.67/cm |

| This work | Borosilicate Glass/350 | W-coated Si | 20–45 | 7.0 1 | <1.15 (Avg. 0.69 ± 0.18) |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hyeon, I.-J.; Baek, C.-W. Millimeter-Wave Substrate Integrated Waveguide Using Micromachined Tungsten-Coated Through Glass Silicon Via Structures. Micromachines 2018, 9, 172. https://doi.org/10.3390/mi9040172

Hyeon I-J, Baek C-W. Millimeter-Wave Substrate Integrated Waveguide Using Micromachined Tungsten-Coated Through Glass Silicon Via Structures. Micromachines. 2018; 9(4):172. https://doi.org/10.3390/mi9040172

Chicago/Turabian StyleHyeon, Ik-Jae, and Chang-Wook Baek. 2018. "Millimeter-Wave Substrate Integrated Waveguide Using Micromachined Tungsten-Coated Through Glass Silicon Via Structures" Micromachines 9, no. 4: 172. https://doi.org/10.3390/mi9040172