Fixed Switching Frequency Digital Sliding-Mode Control of DC-DC Power Supplies Loaded by Constant Power Loads with Inrush Current Limitation Capability

Abstract

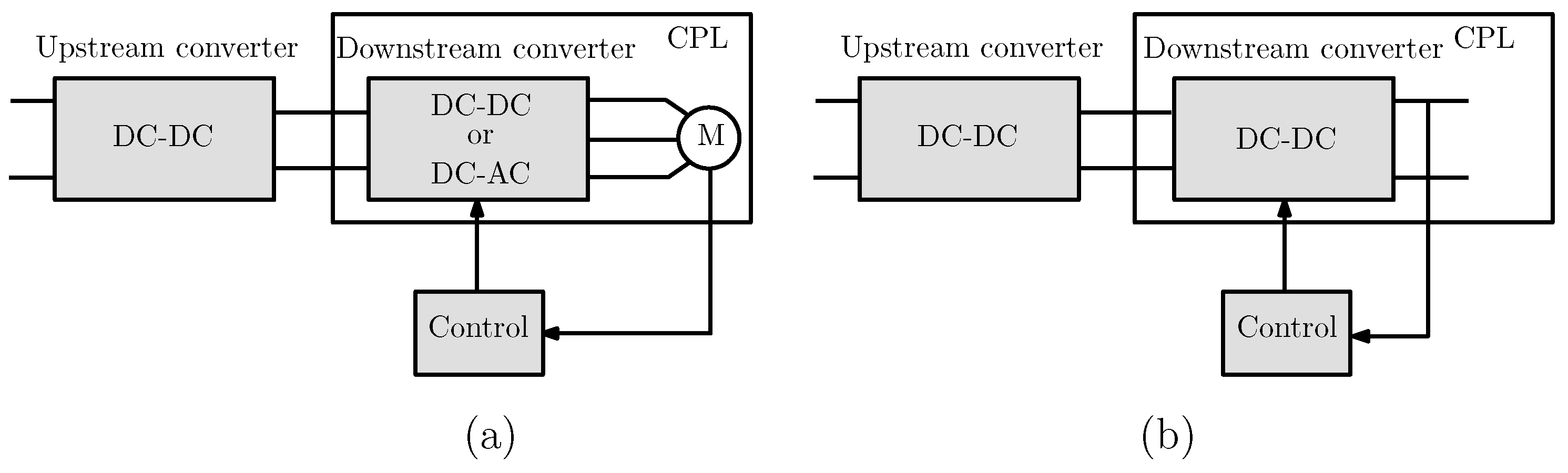

:1. Introduction

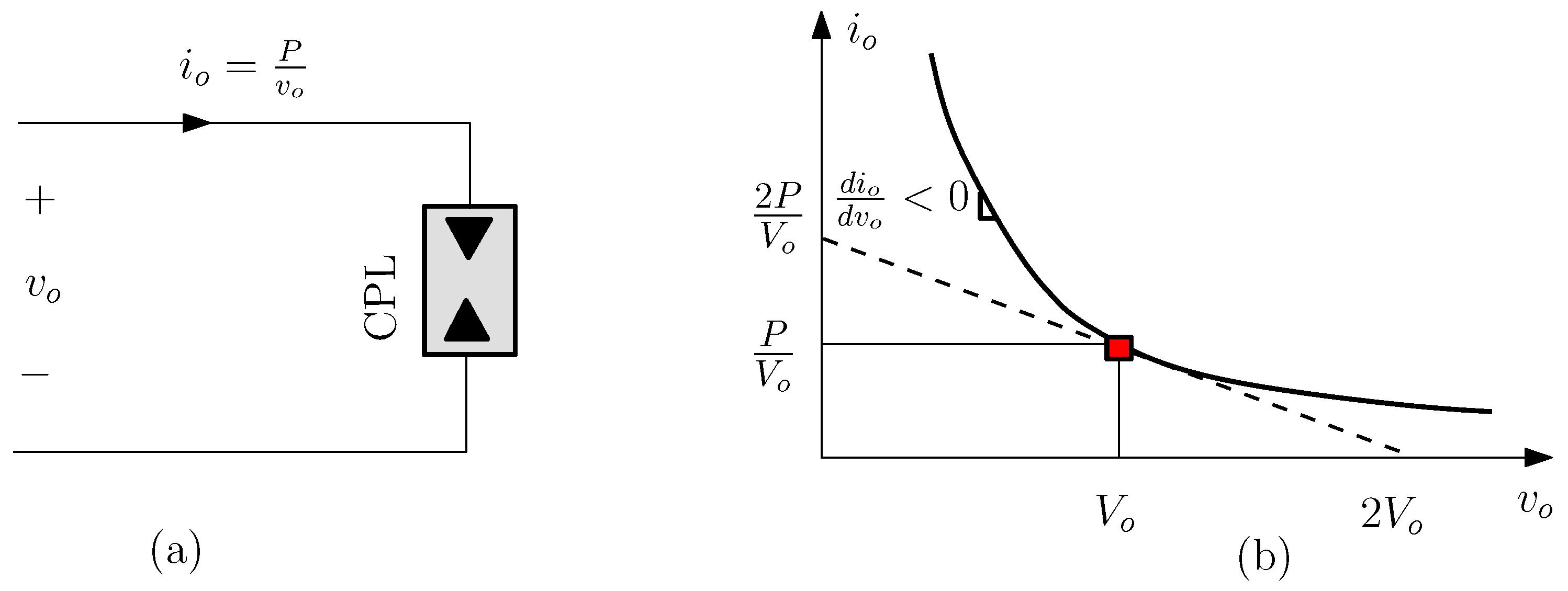

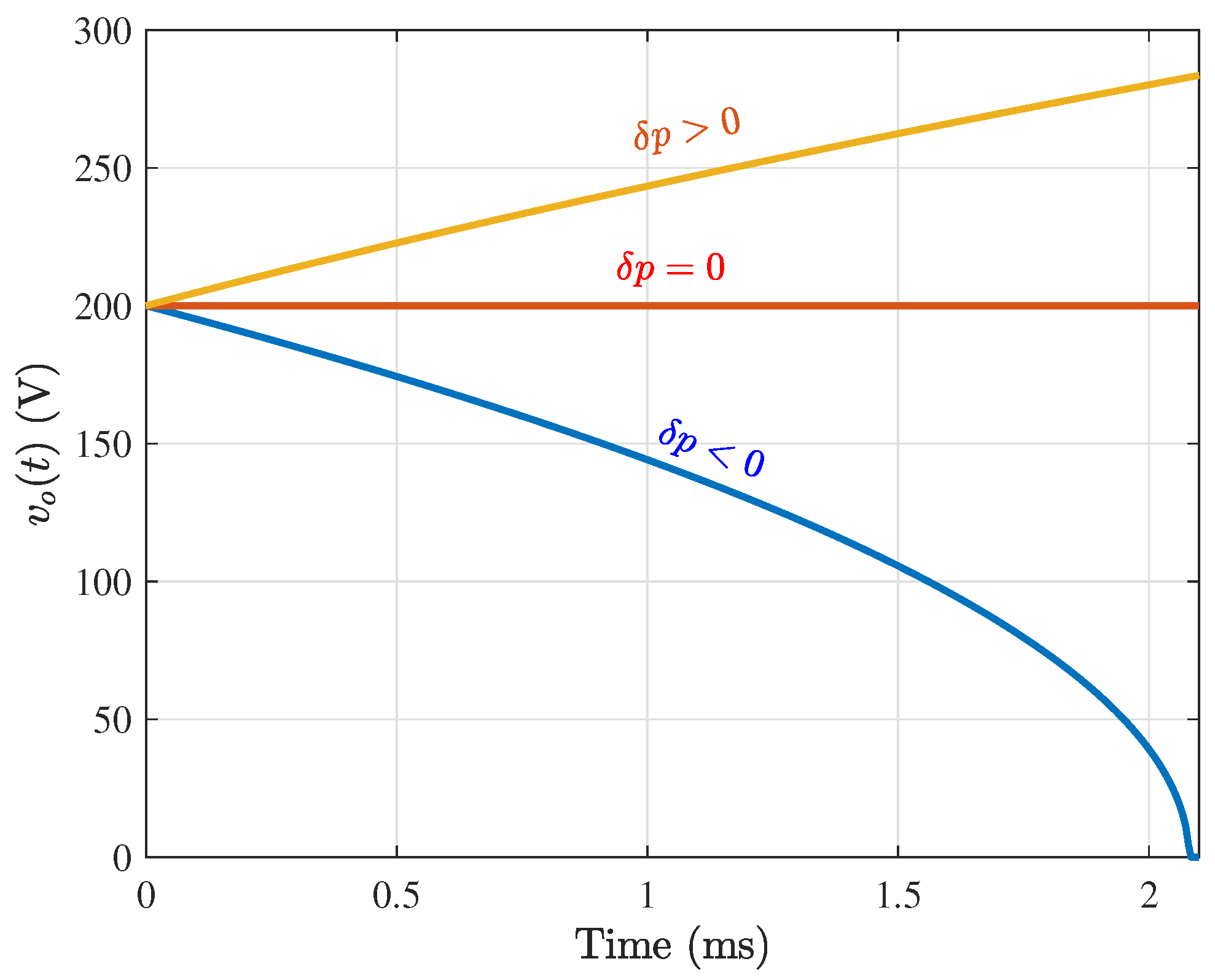

2. The Destabilizing Effect Associated with the Negative Impedance Due to the CPL Behavior

- , the response is unbounded, and therefore the system is unstable.

- , the response is bounded but present an infinite number of equilibria depending on the initial condition . Indeed, in this case, one has .

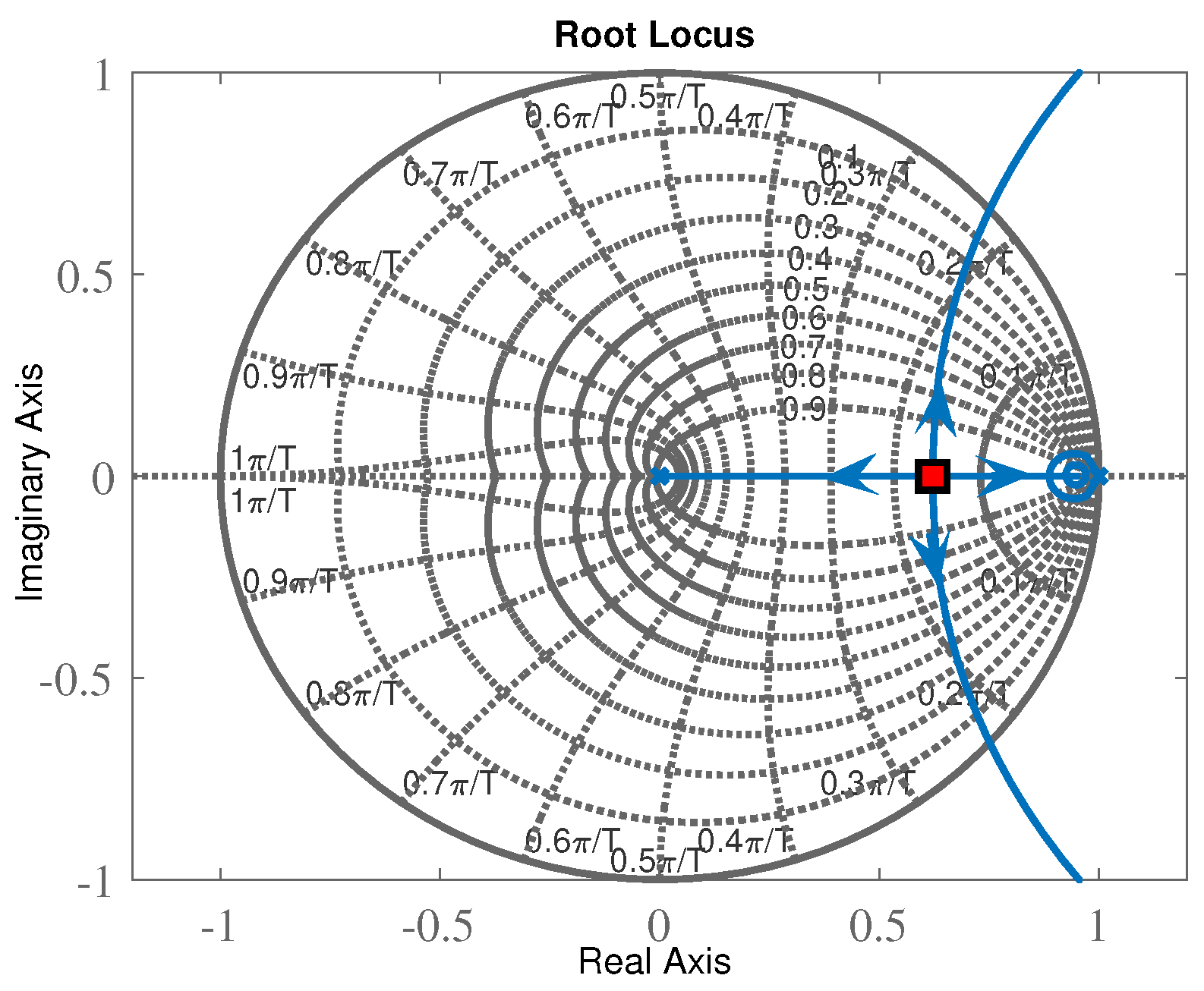

- , the response collapses at a certain time instant given by

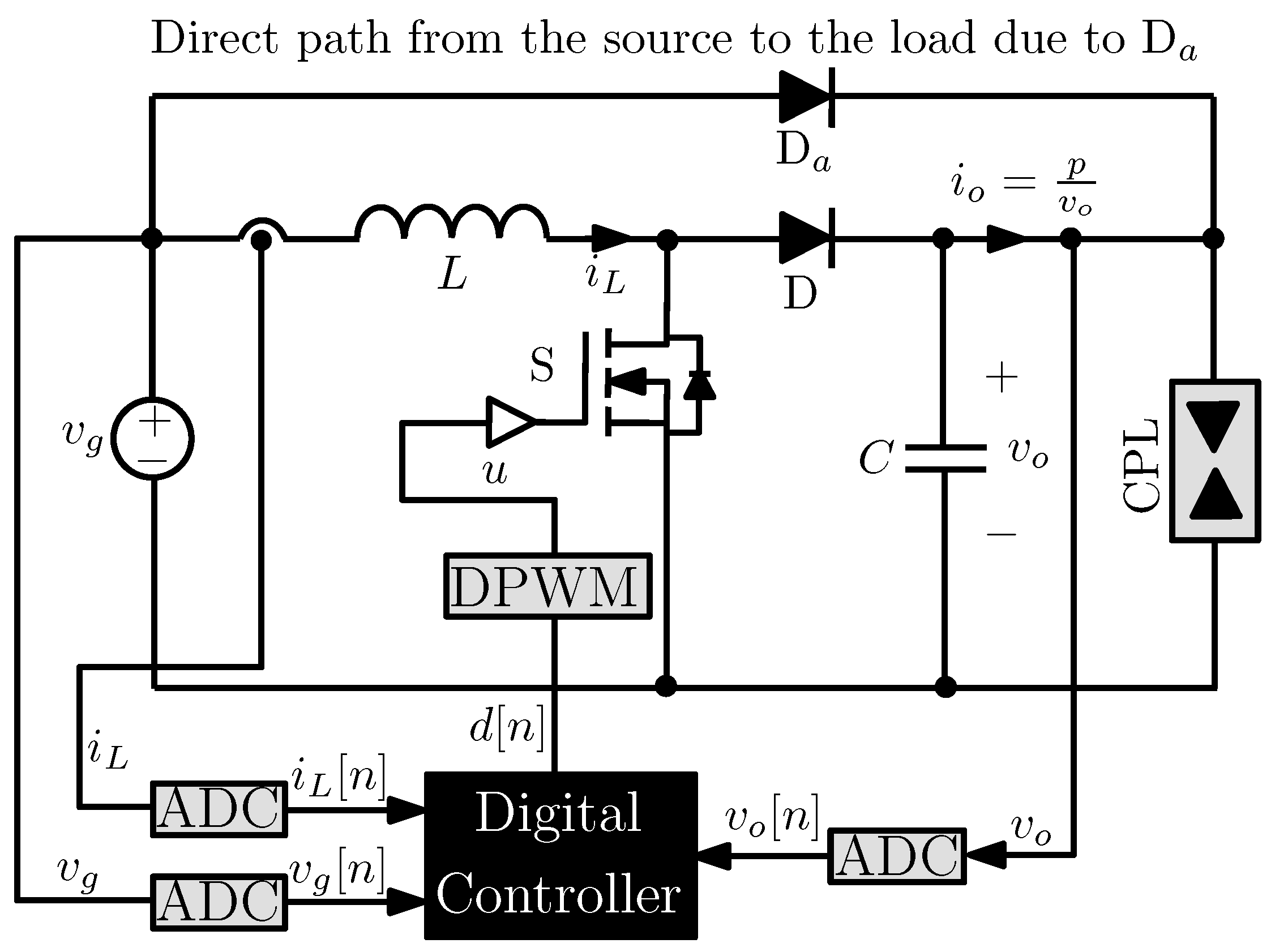

3. Discrete-Time Modeling of a Boost Converter Loaded by a CPL

3.1. System Description

3.2. Discrete-Time Mathematical Modeling

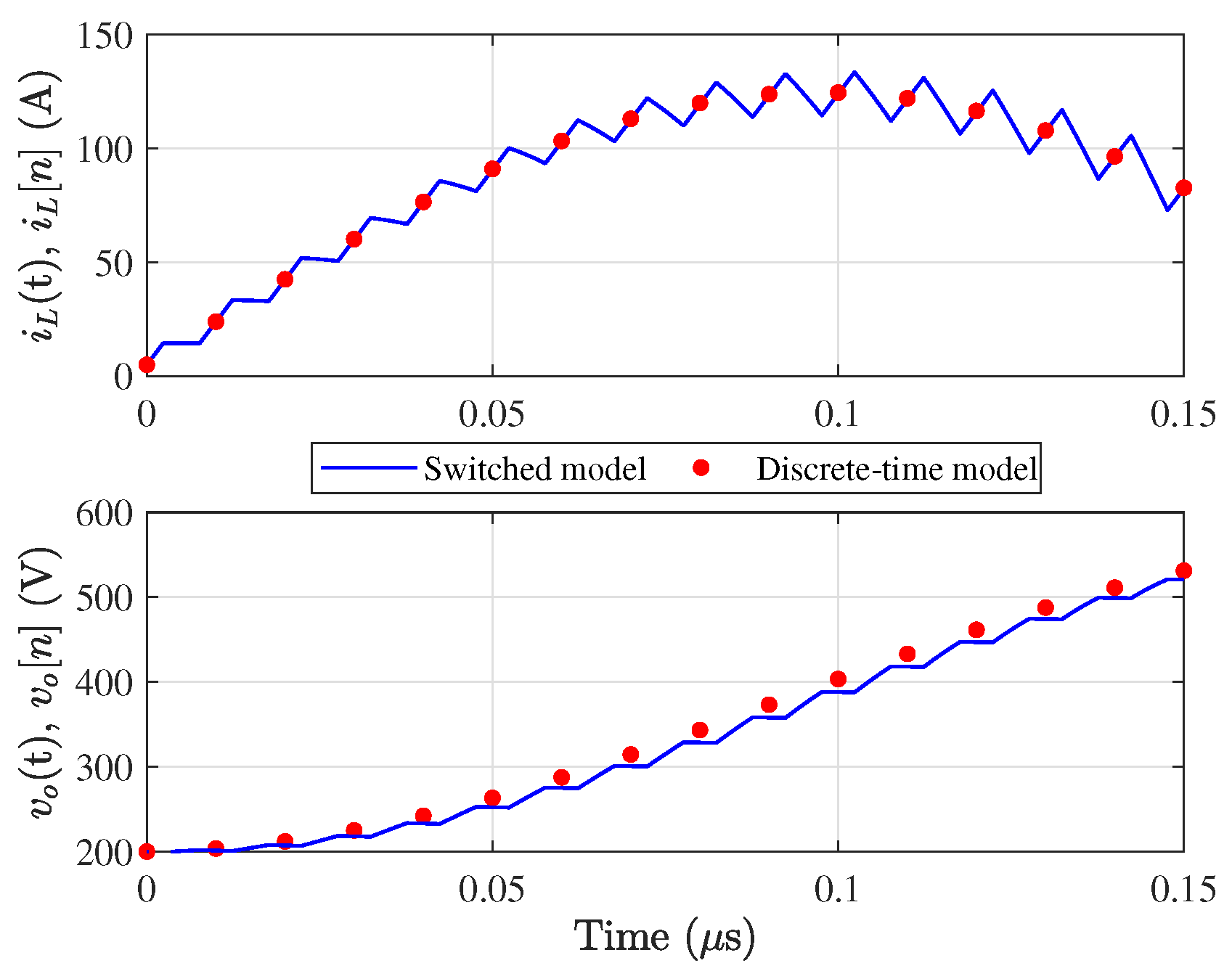

3.3. Open-Loop Model Validation

4. Digital Sliding-Mode Inner Loop Control Design

4.1. Large-Signal Model with Voltage Loop Open

4.2. Equivalent Control

4.3. Comparison with State-of-Art Digital Predictive Control

4.4. DSMC Design

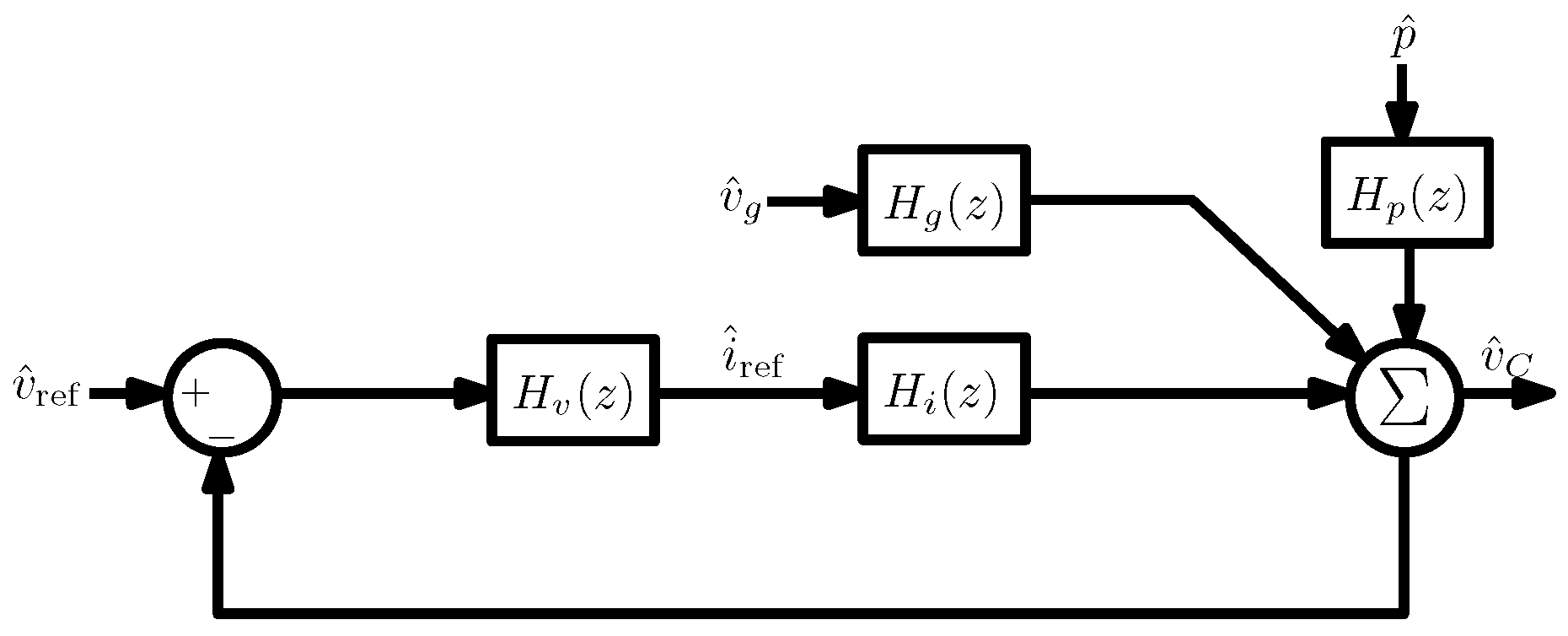

4.5. Control-Oriented Full-Order Discrete-Time Small-Signal Model

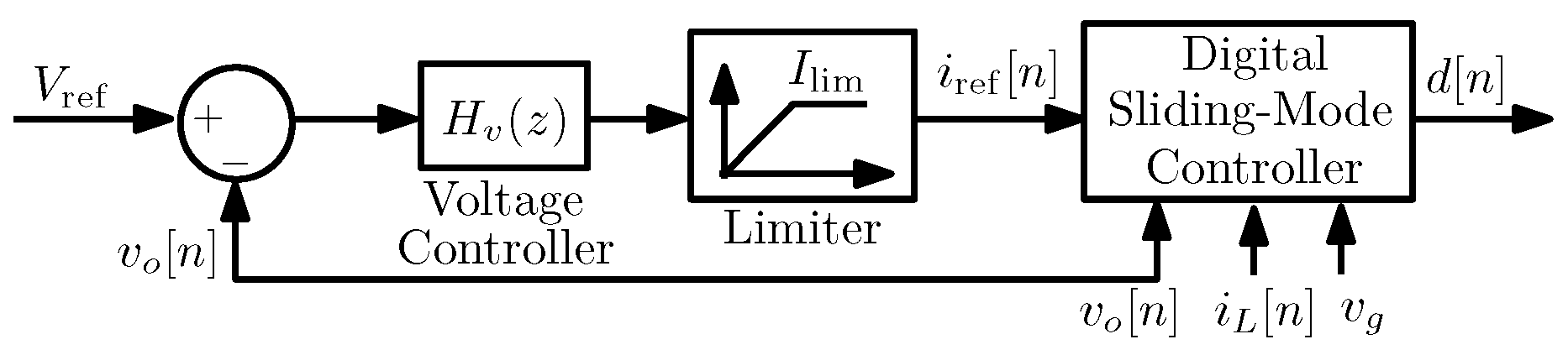

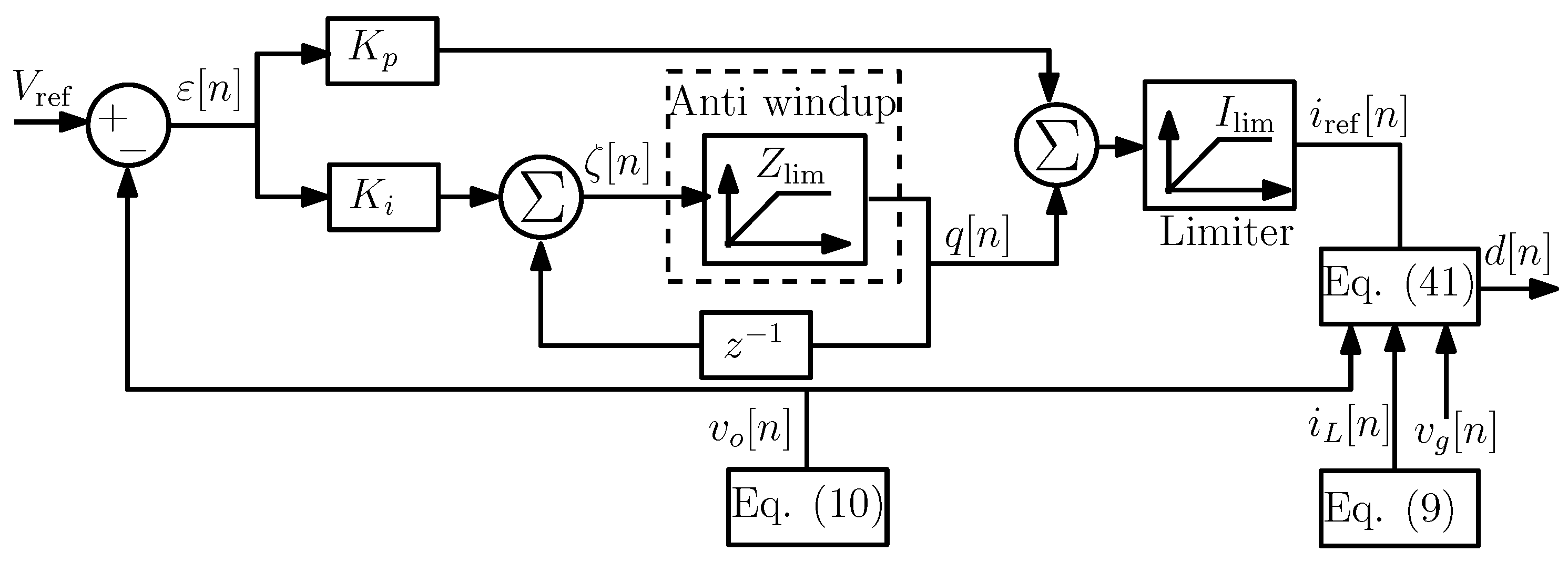

5. Digital Control for Output Voltage Regulation

6. Design of the Output Voltage Feedback Loop Using the Root-Locus Technique

7. Numerical Simulations and Model Validation

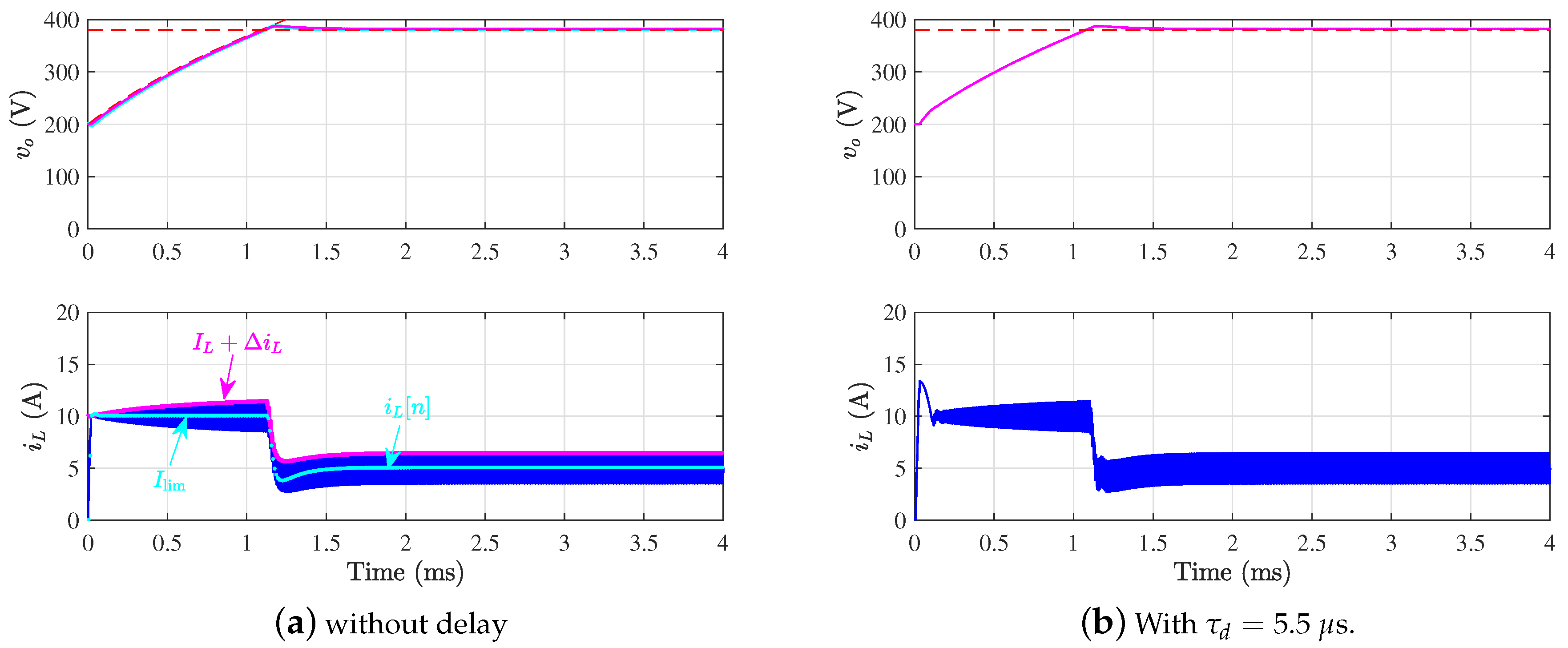

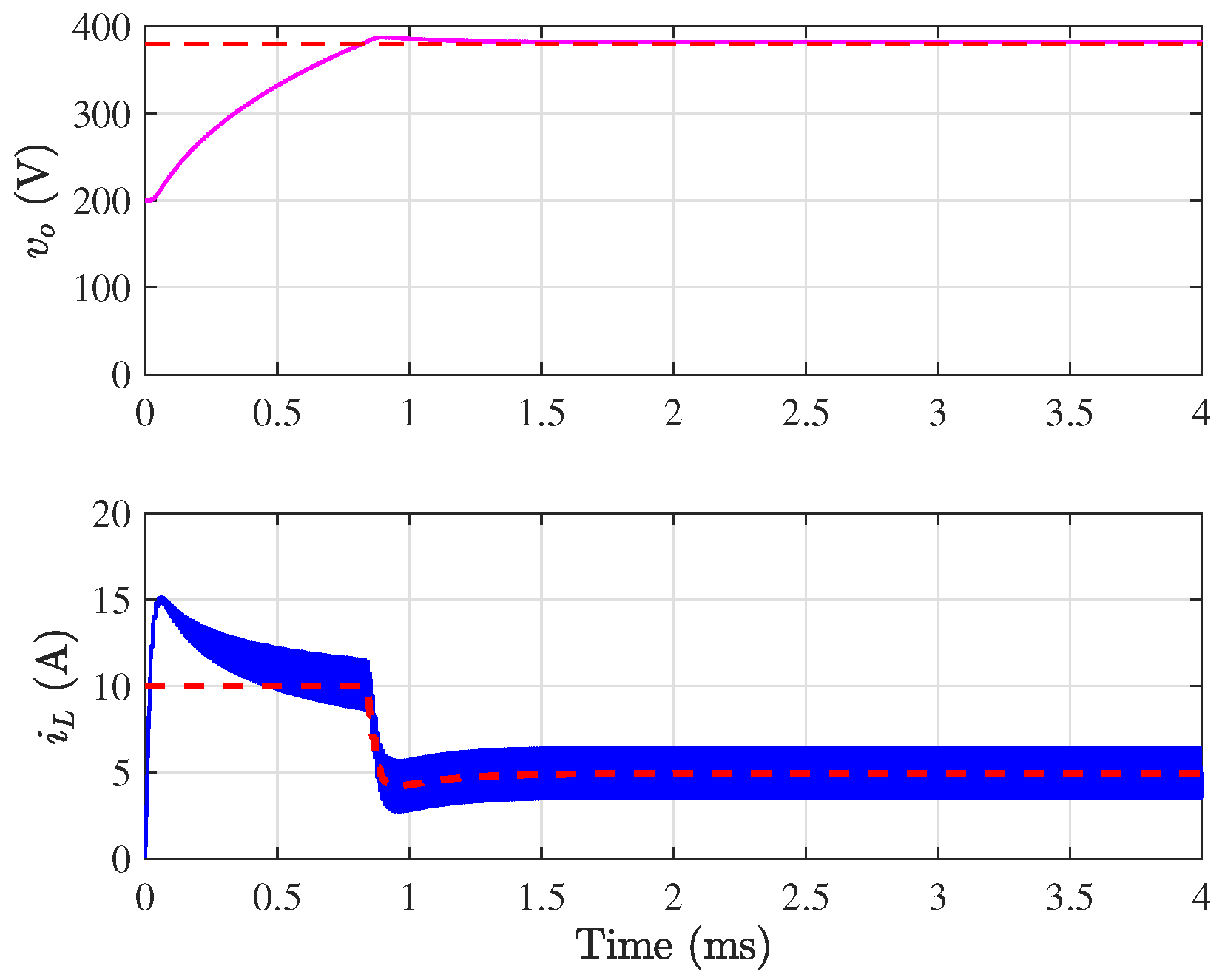

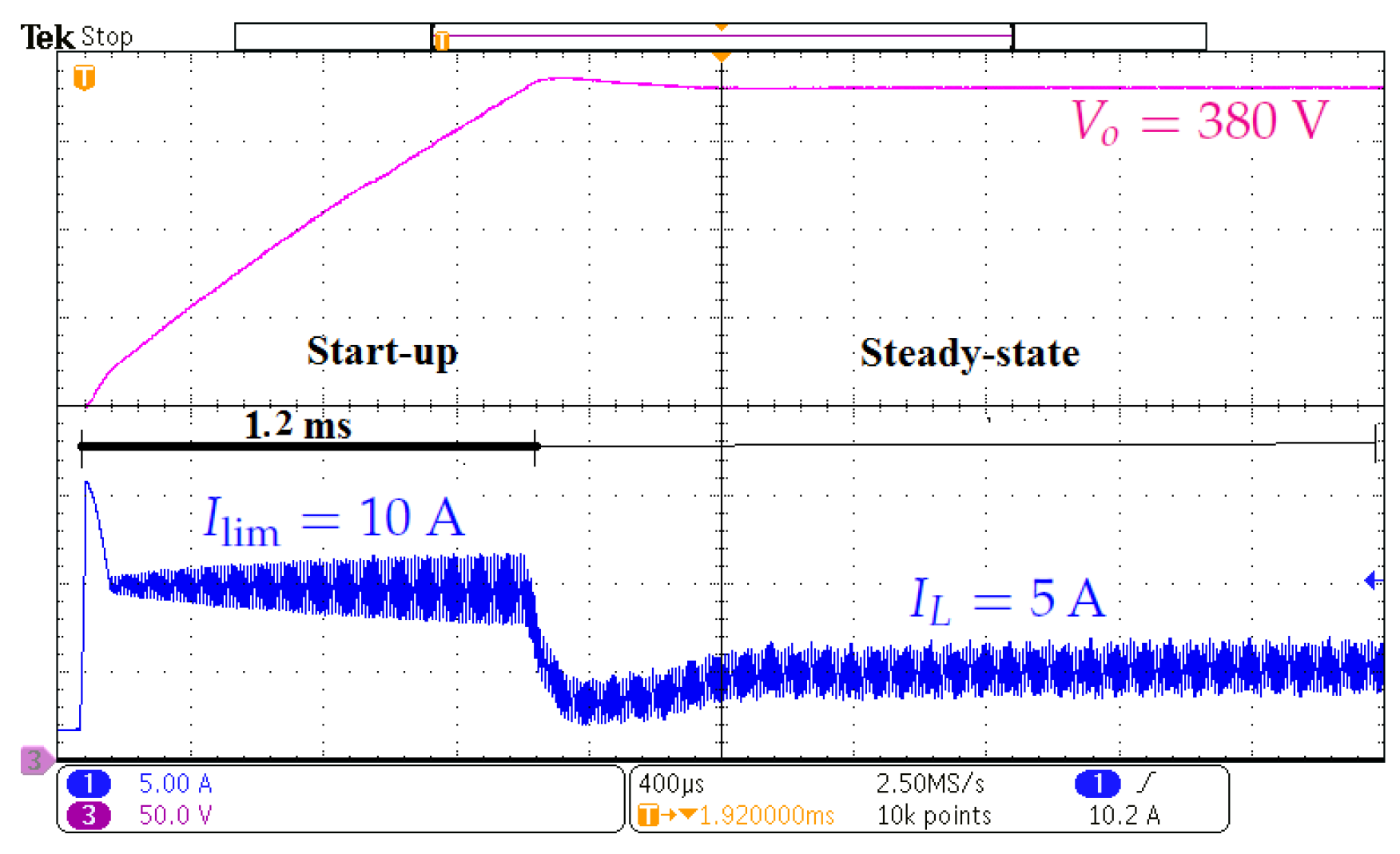

7.1. System Startup and Steady-State Operation

7.1.1. Validation of the Closed-Loop Large-Signal Model and Guaranteeing the Sliding-Mode Operation

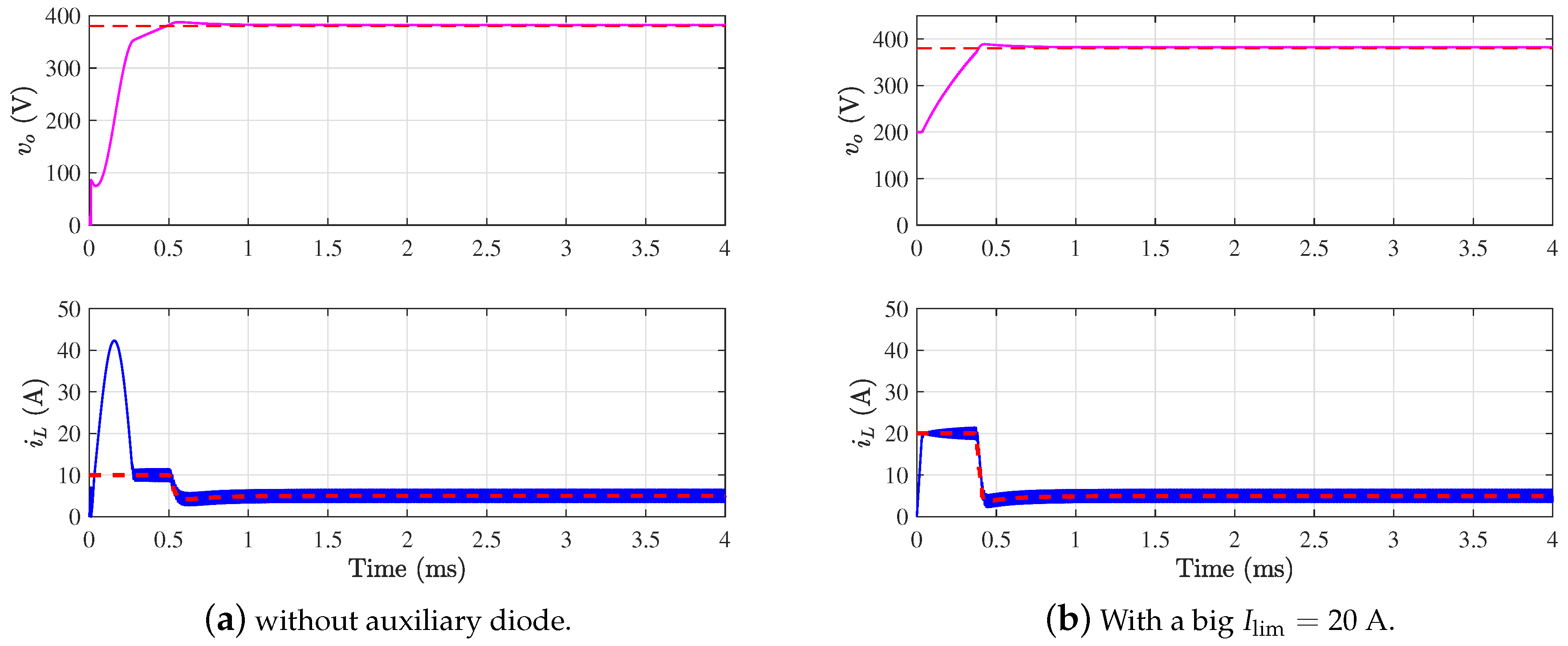

7.1.2. The Importance of Operating in Sliding-Mode Regime for Inrush Current Limitation

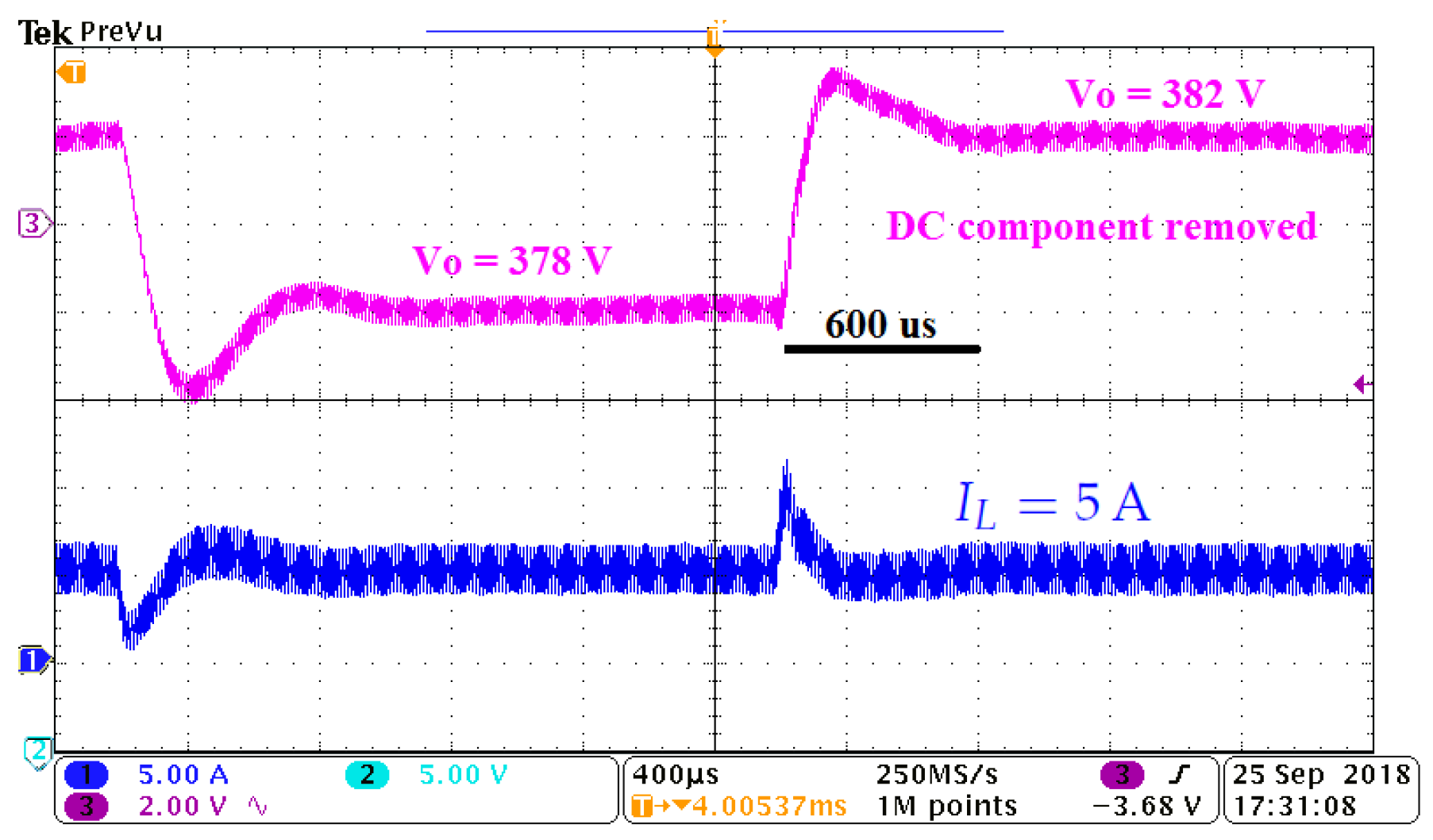

7.2. Small-Signal Response to Output Voltage Variation. Non-Minimum Phase Behavior

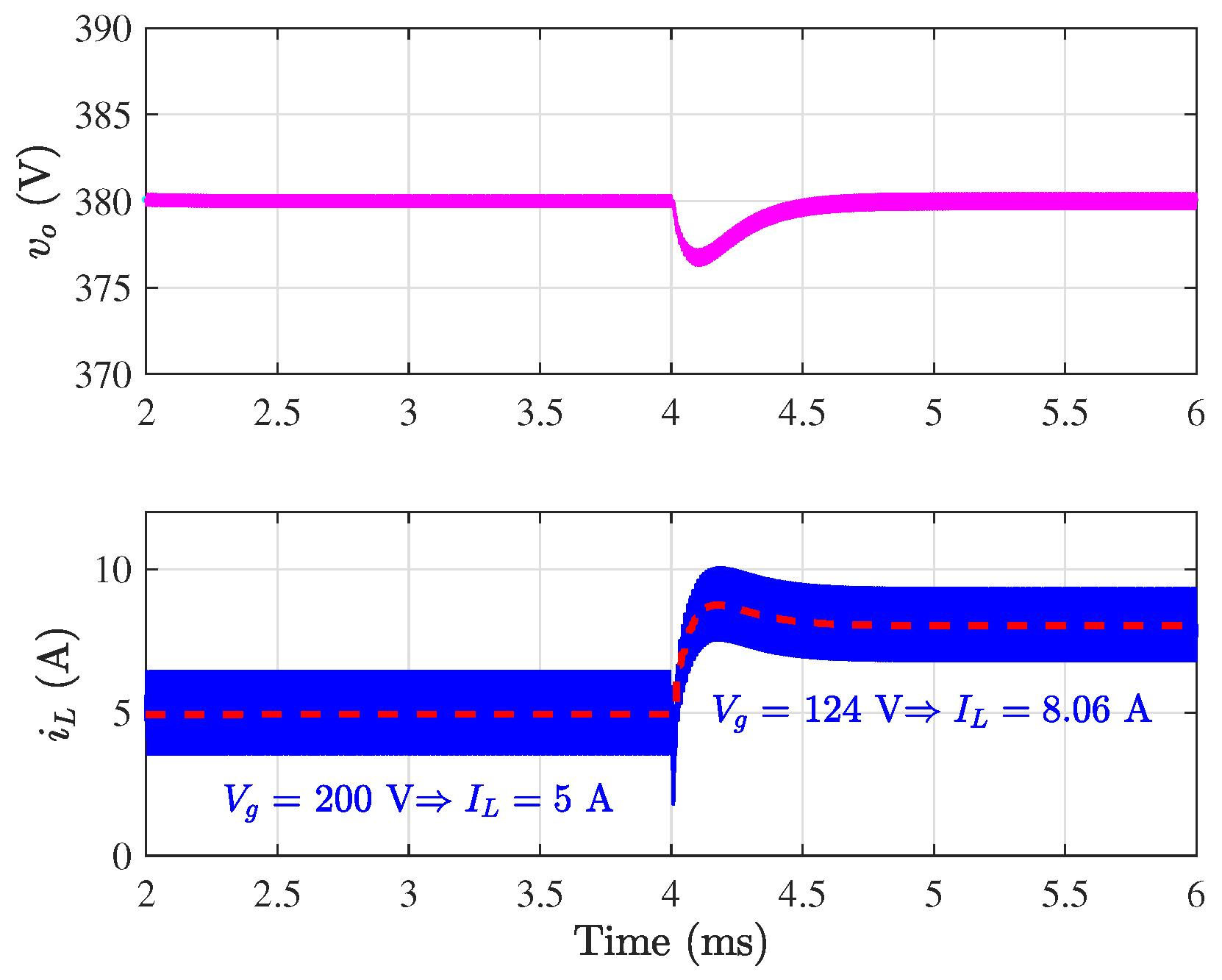

7.3. Small-Signal Response to Input Voltage Disturbance

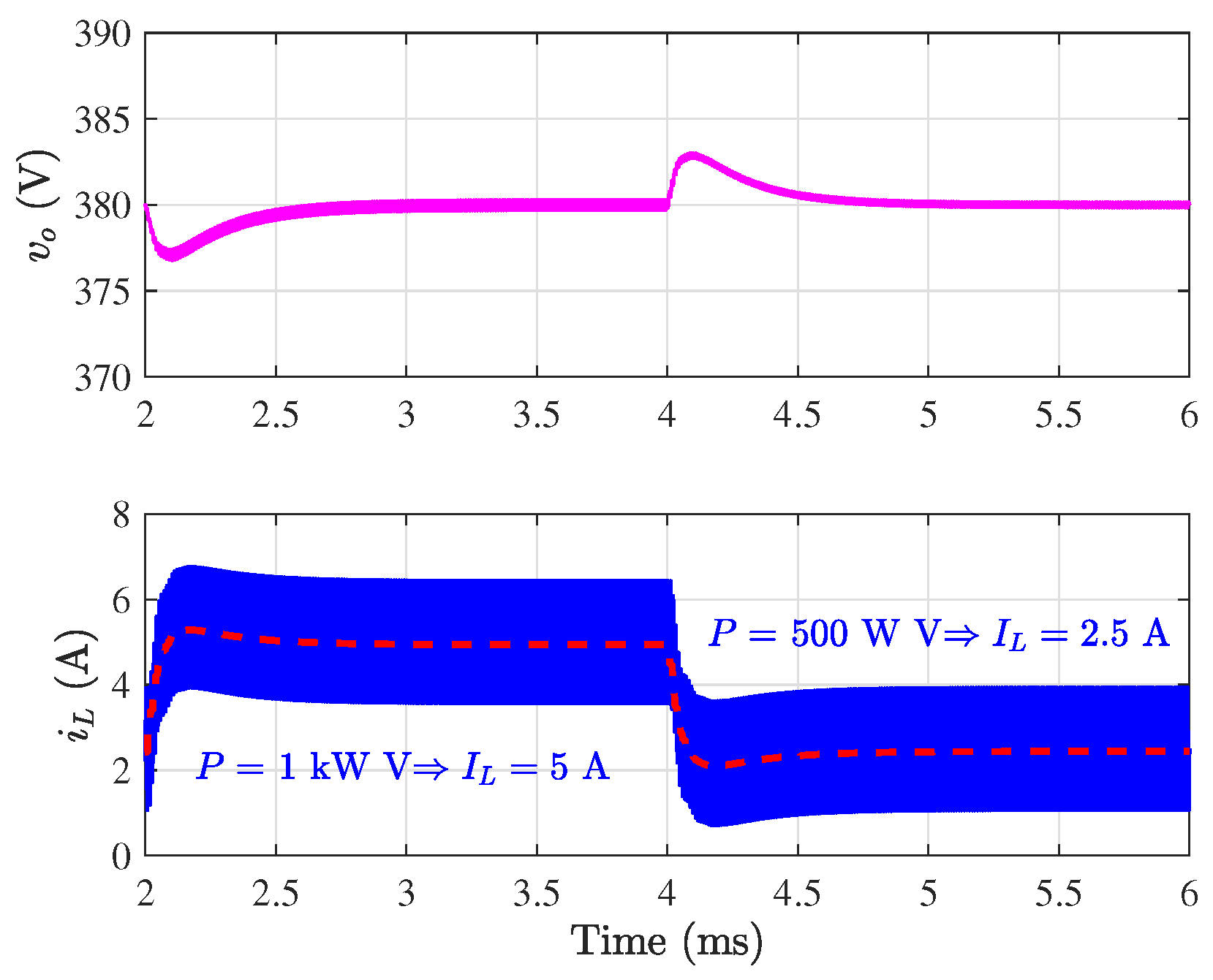

7.4. Small-Signal Response to Power Disturbance

8. Experimental Results

8.1. Experimental Setup

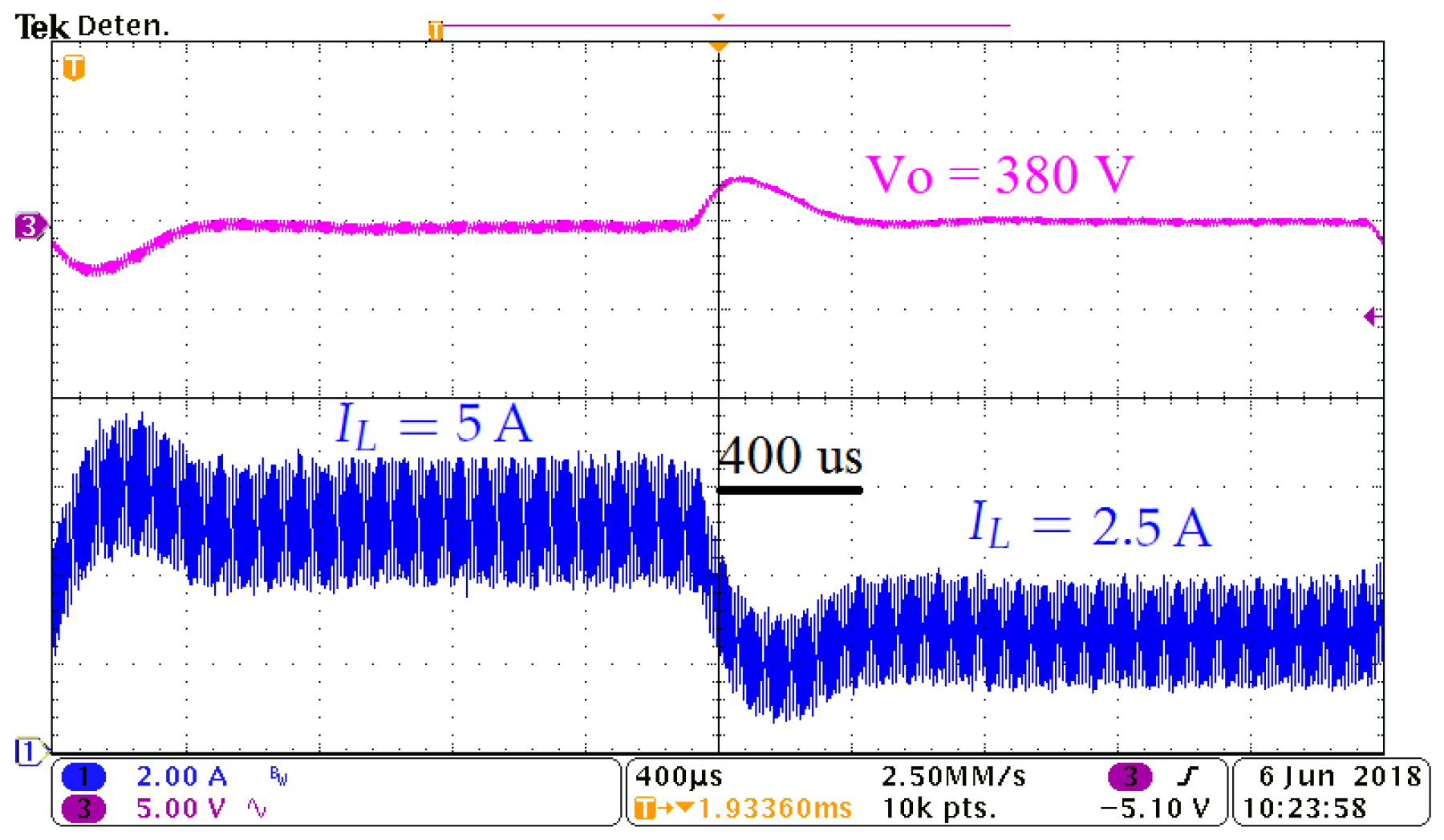

8.2. Results

9. Conclusions

- The boost converter loaded with CPL is unstable in open loop.

- The boost converter loaded with CPL is unstable with digital sliding-mode current-mode control in a clear-cut contrast with the same converter with resistive load. With an appropriate choice of the outer voltage loop, the system can be stabilized to its desired operating point.

- The operation under sliding-mode regime helps in the inrush current limitation at startup

- The presence of propagation delay worsens the inrush current and the problem can be relieved by forcing a non-saturated value of the duty cycle within the few initial switching cycles. This can be accomplished either by scaling down the value of the duty cycle obtained by the control law or by limiting the rate of change of the current reference at startup.

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| ADC | Analog-to-digital converter |

| CPL | Constant power load |

| CPS | Constant power source |

| DPC | Digital predictive control |

| DPWM | Digital pulse width modulation |

| DSMC | Digital sliding mode control |

| EV | Electric vehicle |

| KCL | Kirchhof current law |

| PWM | Pulse width modulation |

| SMC | Sliding mode control |

References

- Belkhayat, M.; Cooley, R.; Witulski, A. Large signal stability criteria for distributed systems with constant power loads. In Proceedings of the 26th Annual IEEE Power Electronics Specialists Conference, PESC ’95 Record, Atlanta, GA, USA, 18–22 June 1995; Volume 2, pp. 1333–1338. [Google Scholar]

- Emadi, A.; Fahimi, B.; Ehsani, M. On the Concept of Negative Impedance Instability in the More Electric Aircraft Power Systems with Constant Power Loads. SAE Technol. Pap. 01-2545 1999. [Google Scholar] [CrossRef]

- Choi, B.; Cho, B.; Hong, S.-S. Dynamics and control of dc-to-dc converters driving other converters downstream. IEEE Trans. Circuit Syst. I Fund. Theory Appl. 1999, 46, 1240–1248. [Google Scholar] [CrossRef]

- Emadi, A.; Ehsani, A. Dynamics and control of multi-converter dc power electronic systems. In Proceedings of the 2001 IEEE 32nd Annual Power Electronics Specialists Conference, Vancouver, BC, Canada, 17–21 June 2001; Volume 1, pp. 248–253. [Google Scholar]

- Khaligh, A. Realization of parasitics in stability of DC-DC converters loaded by constant power loads in advanced multiconverter automotive systems. IEEE Trans. Ind. Electron. 2008, 55, 2295–2305. [Google Scholar] [CrossRef]

- Rivetta, C.; Emadi, A.; Williamson, G.; Jayabalan, R.; Fahimi, B. Analysis and control of a buck DC-DC converter operating with constant power load in sea and undersea vehicles. IEEE Trans. Ind. Appl. 2004, 2, 1146–1153. [Google Scholar]

- Kwasinski, A.; Onwuchekwa, C. Dynamic Behavior and Stabilization of DC microgrids with instantaneous constant-power loads. IEEE Trans. Power Electron. 2011, 26, 822–834. [Google Scholar] [CrossRef]

- Lu, X.; Sun, K.; Guerrero, J.M.; Vasquez, J.C.; Huang, L.; Wang, J. Stability enhancement based on virtual impedance for DC microgrids with constant power loads. IEEE Trans. Smart Grid 2015, 6, 2770–2783. [Google Scholar] [CrossRef]

- Al-Nussairi, M.; Bayindir, R.; Padmanaban, S.; Siano, L.M.P.P. Constant Power Loads (CPL) with Microgrids: Problem Definition, Stability Analysis and Compensation Techniques. Energies 2017, 10, 1656. [Google Scholar] [CrossRef]

- Singh, S.; Fulwani, D. Constant power loads: A solution using sliding-mode control. In Proceedings of the IECON 2014—40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; pp. 1989–1995. [Google Scholar]

- Emadi, A.; Khaligh, A.; Rivetta, C.; Williamson, G. Constant power loads and negative impedance instability in automotive systems: Definition, modeling, stability, and control of power electronic converters and motor drives. IEEE Trans. Veh. Technol. 2006, 55, 1112–1125. [Google Scholar] [CrossRef]

- Smithson, S.; Williamson, S. Constant power loads in more electric vehicles—An overview. In Proceedings of the IECON 2012—38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 2914–2922. [Google Scholar]

- Cespedes, M.; Xing, L.; Sun, J. Constant-Power Load System Stabilization by Passive Damping. IEEE Trans. Power Electron. 2011, 26, 1832–1836. [Google Scholar] [CrossRef]

- Rahimi, A.M.; Emadi, A. Active damping in DC-DC power electronic converters: A novel method to overcome the problems of constant power loads. IEEE Trans. Ind. Electron. 2009, 56, 1428–1439. [Google Scholar] [CrossRef]

- Sulligoi, G.; Bosich, D.; Giadrossi, G.; Zhu, L.; Cupelli, M.; Monti, A. Multiconverter medium voltage DC power systems on ships, Constant power loads instability solution using linearization via state feedback control. IEEE Trans. Smart Grids 2014, 5, 2543–2552. [Google Scholar] [CrossRef]

- Li, Y.; Vannorsdel, K.; Zirger, A.; Norris, M.; Maksimović, A. Current mode control for boost converters with constant power loads. IEEE Trans. Circuit Syst. I Fund. Theory Appl. 2012, 59, 19206. [Google Scholar] [CrossRef]

- Rahimi, A.M.; Emadi, A. Discontinuous conduction mode DC-DC converters feeding constant power loads. IEEE Trans. Ind. Electron. 2010, 57, 1318–1329. [Google Scholar] [CrossRef]

- Rodríguez-Licea, M.-A.; Pérez-Pinal, F.-J.; Nu nez-Perez, J.-C.; Herrera-Ramirez, C.A. Nonlinear Robust Control for Low Voltage Direct-Current Residential Microgrids with Constant Power Loads. Energies 2018, 11, 1130. [Google Scholar] [CrossRef]

- Marcillo, K.-E.L.; Guingla, D.-A.P.; Barra, W.; de Medeiros, R.L.P.; Rocha, E.-M.; Vaca-Benavides, D.A.; Nogueira, F.G. Interval Robust Controller to Minimize Oscillations Effects Caused by Constant Power Load in a DC Multi-Converter Buck-Buck System. IEEE Access 2018, 6. [Google Scholar] [CrossRef]

- Hossain, E.; Perez, R.; Nasiri, A.; Padmanaban, S. A Comprehensive Review on Constant Power Loads Compensation Techniques. IEEE Access 2018, 6, 33285–33305. [Google Scholar] [CrossRef]

- Utkin, V.; Guldner, J.; Shi, J. Sliding Mode Control In Electro-Mechanical Systems, (Automation and Control Engineering); CRC Press: Boca Raton, FL, USA, 2009. [Google Scholar]

- Utkin, V. Sliding mode control of dc/dc converters. J. Frankl. Inst. 2013, 350, 2146–2165. [Google Scholar] [CrossRef]

- Venkataramanan, R. Sliding Mode Control of Power Converters. Ph.D. Thesis, California Institute of Technology Pasadena, Pasadena, CA, USA, 1986. [Google Scholar]

- Utkin, V.I. Sliding mode control design principles and applications to electric drives. IEEE Trans. Ind. Electron. 1993, 40, 23–36. [Google Scholar] [CrossRef] [Green Version]

- Calvente, J.; El Aroudi, A.; Giral, R.; Cid-Pastor, A.; Vidal-Idiarte, E.; Martínez-Salamero, L. Design of Current Programmed Switching Converters Using Sliding-Mode Control Theory. Energies 2018, 11, 2034. [Google Scholar] [CrossRef]

- Martinez-Salamero, L.; Cid-Pastor, A.; El Aroudi, A.; Giral, R.; Calvente, J. Sliding-mode control of DC-DC switching converters. IFAC Proc. Vol. 2011, 44, 1910–1916. [Google Scholar] [CrossRef]

- Cid-Pastor, A.; Giral, R.; Calvente, J.; Utkin, V.; Martinez-Salamero, L. Interleaved converters based on sliding-mode control in a ring configuration. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 2566–2577. [Google Scholar] [CrossRef]

- Haroun, R.; El Aroudi, A.; Cid-Pastor, A.; Garcia, G.; Olalla, C.; Garcia, G. Impedance matching in photovoltaic systems using cascaded boost converters and sliding-mode control. IEEE Trans. Power Electron. 2015, 30, 3185–3199. [Google Scholar] [CrossRef]

- Cid-Pastor, A.; Martinez-Salamero, L.; El Aroudi, A.; Giral, R.; Calvente, J.; Leyva, R. Synthesis of loss-free resistors based on sliding-mode control and its applications in power processing. Control Eng. Pract. 2013, 21, 689–699. [Google Scholar] [CrossRef]

- Bodetto, M.; El Aroudi, A.; Cid-Pastor, A.; Calvente, J.; Martinez-Salamero, L. Design of AC-DC PFC high-order converters with regulated output current for low-power applications. IEEE Trans. Power Electron. 2016, 31, 2012–2025. [Google Scholar] [CrossRef]

- Benadero, L.; Cristiano, R.; Pagano, D.; Ponce, E. Nonlinear analysis of interconnected power converters: A case study. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 326–335. [Google Scholar] [CrossRef]

- Singh, S.; Fulwani, D.; Kumar, V. Robust sliding-mode control of dc/dc boost converter feeding a constant power load. IET Power Electron. 2015, 8, 1230–1237. [Google Scholar] [CrossRef]

- Gao, W.; Wang, Y.; Homaifa, A. Discrete-time variable structure control systems. IEEE Trans. Ind. Electron. 1995, 42, 117–122. [Google Scholar]

- Bartoszewicz, A. Discrete-time quasi-sliding-mode control strategies. IEEE Trans. Ind. Electron. 1998, 45, 63637. [Google Scholar] [CrossRef]

- Schirone, L.; Celani, F.; Macellari, M. Discrete-time control for DC-AC converters based on sliding-mode design. IET Power Electron. 2012, 5, 833–840. [Google Scholar] [CrossRef]

- Vidal-Idiarte, E.; Carrejo, C.E.; Calvente, J.; Martinez-Salamero, L. Two-loop digital sliding-mode control of DC-DC power converters based on predictive interpolation. IEEE Trans. Ind. Electron. 2011, 58, 2491–2501. [Google Scholar] [CrossRef]

- Utkin, V.; Guldner, J.; Shi, J. Sliding Mode Control in Electromechanical Systems; Taylor & Francis: Boca Raton, FL, USA, 1999. [Google Scholar]

- Vidal-Idiarte, E.; Marcos-Pastor, A.; Garcia, G.; Cid-Pastor, A.; Martinez-Salamero, L. Discrete-time sliding-mode -based digital pulse width modulation control of a boost converter. IET Power Electron. 2015, 8, 708–714. [Google Scholar] [CrossRef]

- Vidal-Idiarte, E.; Marcos-Pastor, A.; Giral, R.; Calvente, J.; Martinez-Salamero, L. Direct digital design of a sliding mode-based control of a PWM synchronous buck converter. IET Power Electron. 2017, 10, 1714–1720. [Google Scholar] [CrossRef]

- Marcos-Pastor, A.; Vidal-Idiarte, E.; Cid-Pastor, A. Interleaved digital power factor correction based on sliding-mode approach. IEEE Trans. Power Electron. 2016, 31, 4641–4653. [Google Scholar] [CrossRef]

- Ogata, K. Discrete-Time Control Systems; Prentice-Hall, Inc.: Upper Saddle River, NJ, USA, 1987. [Google Scholar]

- Chen, J.; Prodic, A.; Erickson, R.W.; Maksimovic, D. Predictive digital current programmed control. IEEE Trans. Power Electron. 2003, 18, 411–419. [Google Scholar] [CrossRef] [Green Version]

| L | C | P | |||

|---|---|---|---|---|---|

| 326 H | 20.8 F | 1 kW | 200 V | 380 V | 100 kHz |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

El Aroudi, A.; Martínez-Treviño, B.A.; Vidal-Idiarte, E.; Cid-Pastor, A. Fixed Switching Frequency Digital Sliding-Mode Control of DC-DC Power Supplies Loaded by Constant Power Loads with Inrush Current Limitation Capability. Energies 2019, 12, 1055. https://doi.org/10.3390/en12061055

El Aroudi A, Martínez-Treviño BA, Vidal-Idiarte E, Cid-Pastor A. Fixed Switching Frequency Digital Sliding-Mode Control of DC-DC Power Supplies Loaded by Constant Power Loads with Inrush Current Limitation Capability. Energies. 2019; 12(6):1055. https://doi.org/10.3390/en12061055

Chicago/Turabian StyleEl Aroudi, Abdelali, Blanca Areli Martínez-Treviño, Enric Vidal-Idiarte, and Angel Cid-Pastor. 2019. "Fixed Switching Frequency Digital Sliding-Mode Control of DC-DC Power Supplies Loaded by Constant Power Loads with Inrush Current Limitation Capability" Energies 12, no. 6: 1055. https://doi.org/10.3390/en12061055