Wide Load Range Capacitor Clamped ZVZCS Half Bridge Three-Level DC-DC Converter with Two Unsymmetrical Bi-directional Switches

Abstract

:1. Introduction

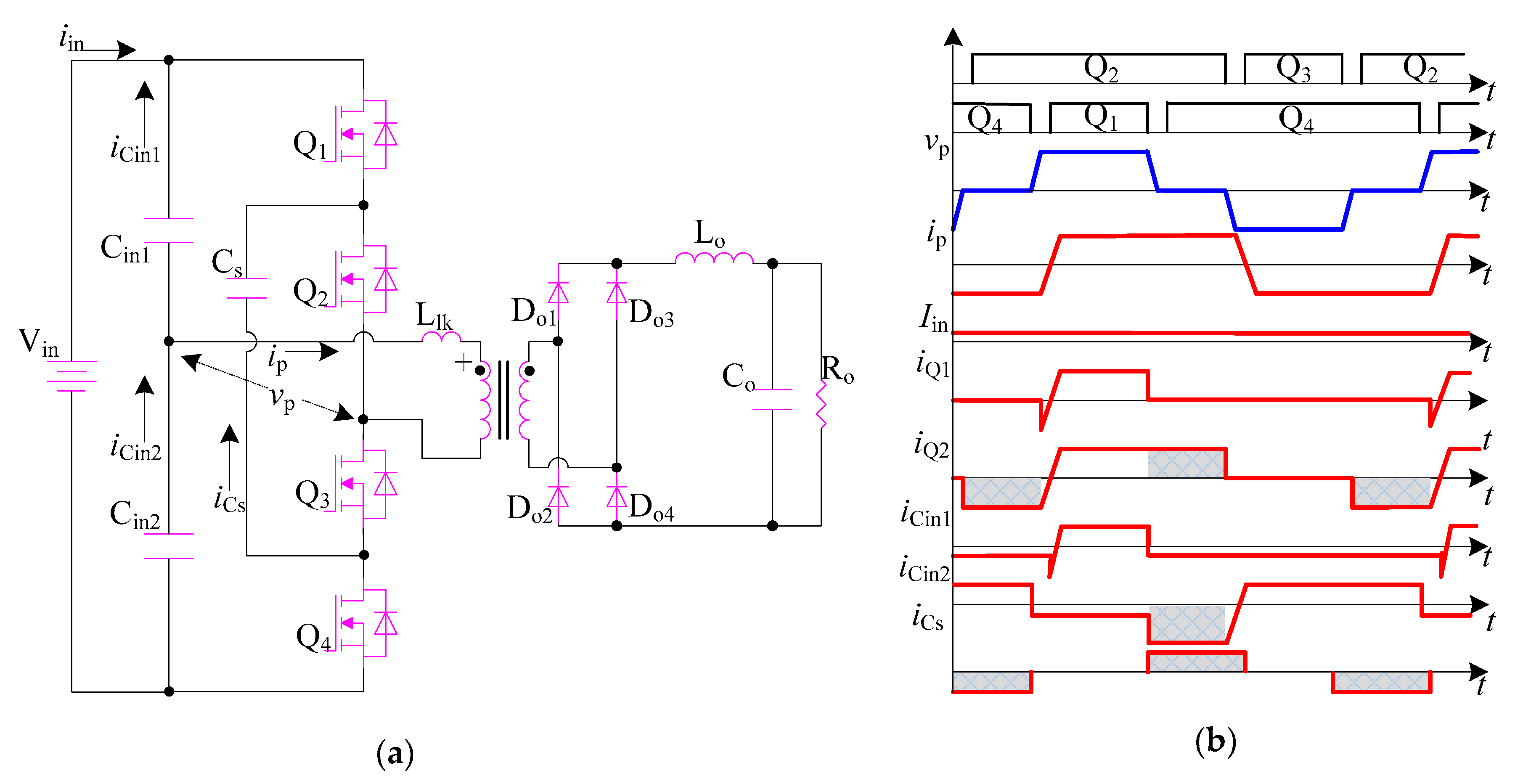

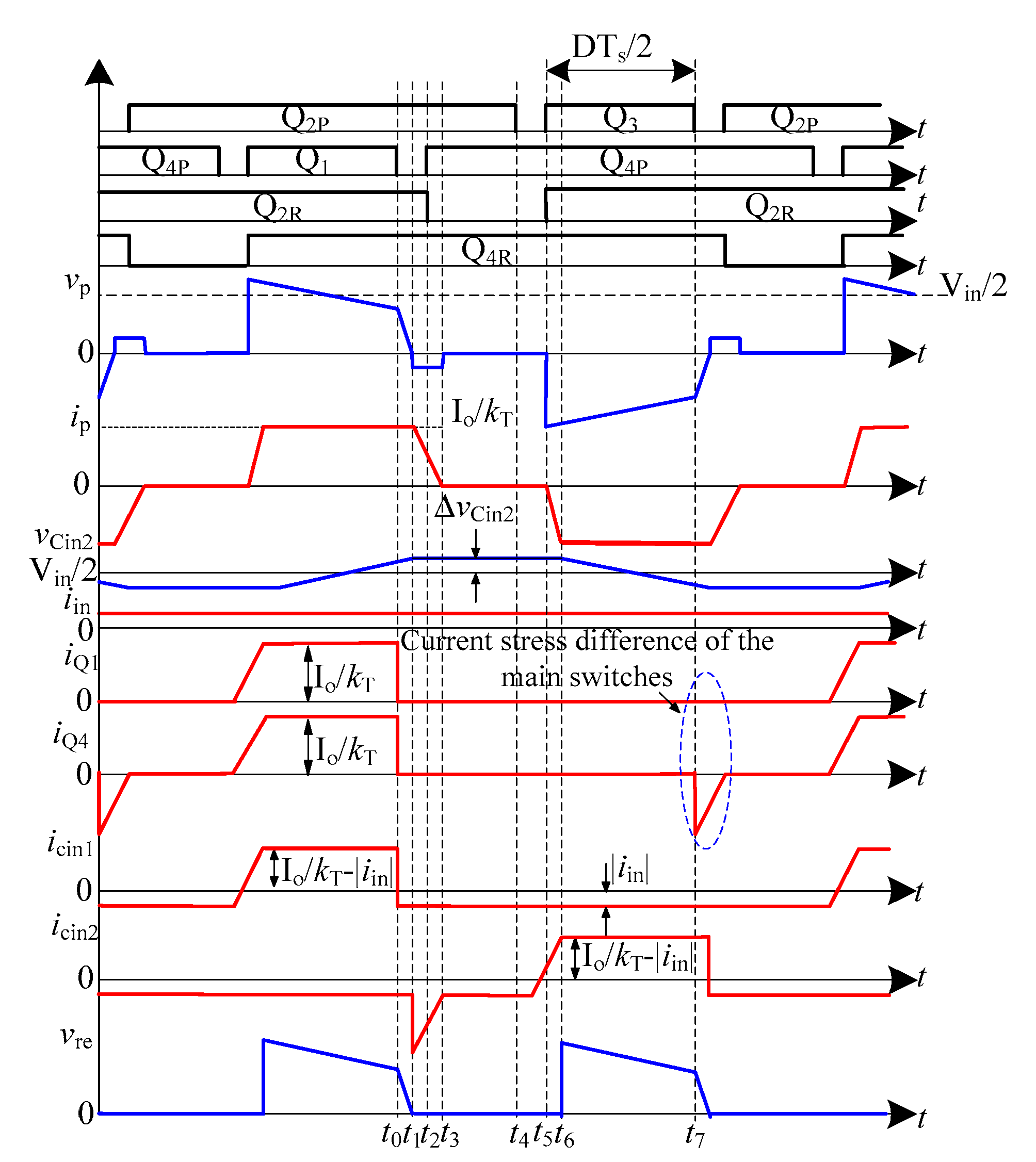

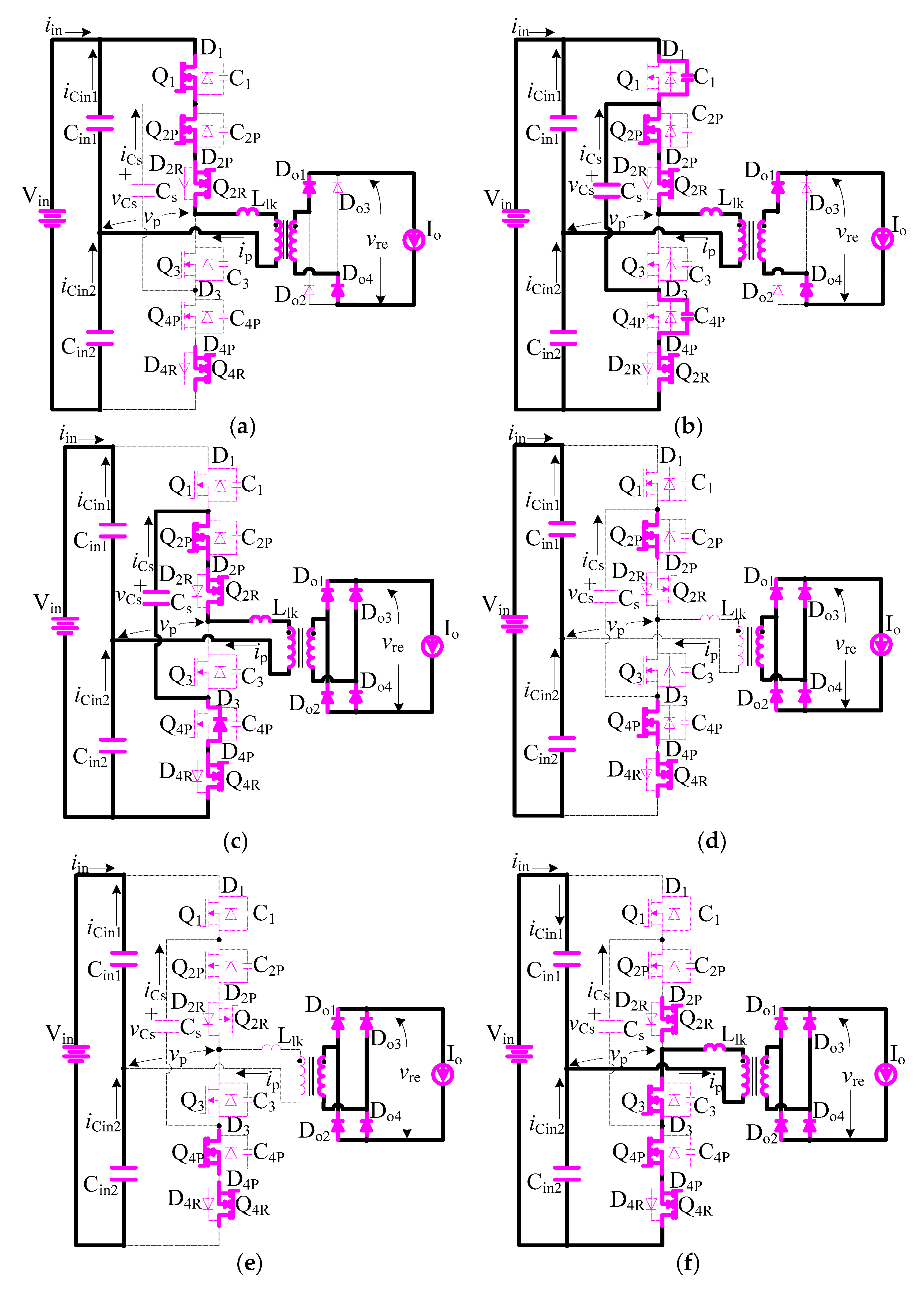

2. Circuits and Principle of Operation

3. Technical Analysis

3.1. Soft Switching of Q2P and Q4P

3.1.1. Turn-on Instants

3.1.2. Turn-off Instants

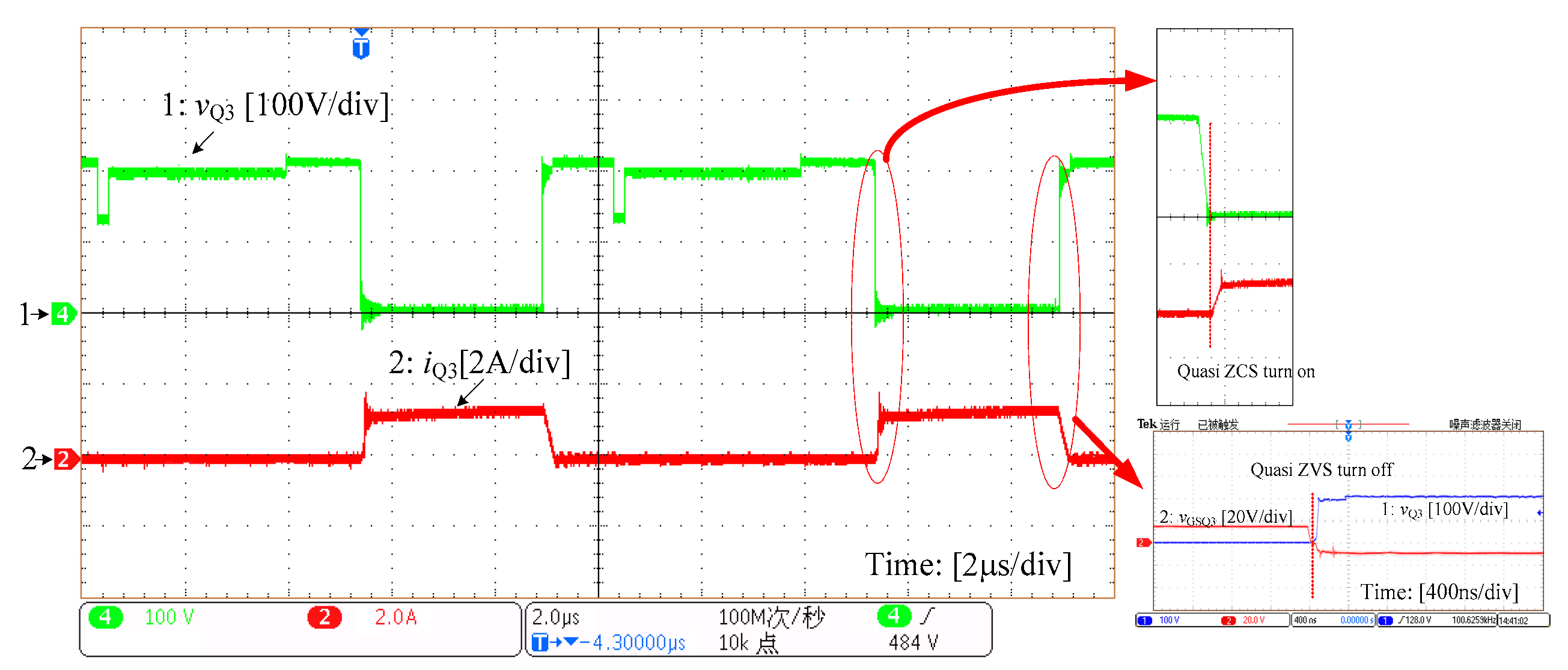

3.2. Soft Switching of Q1 and Q3

3.2.1. Turn-on Instants

3.2.2. Turn-off Instants

3.3. Soft Switching of Q2R and Q4R

3.4. Voltage Balance of the Primary Capacitors

3.4.1. Input Capacitors

3.4.2. Flying Capacitors

3.5. Current Stress of the Primary Component

3.5.1. S2 and S4

3.5.2. Q1 and Q3

3.5.3. Cin1

3.5.4. Cin2

3.5.5. Cs

3.6. Comparison with the Conventional Capacitor Clamped TL dc-dc Converter

3.6.1. Main Switches

3.6.2. Primary Capacitors

3.6.3. Soft Switching Load Range

3.7. Brief Comparison with Other Typical HB TLDCs

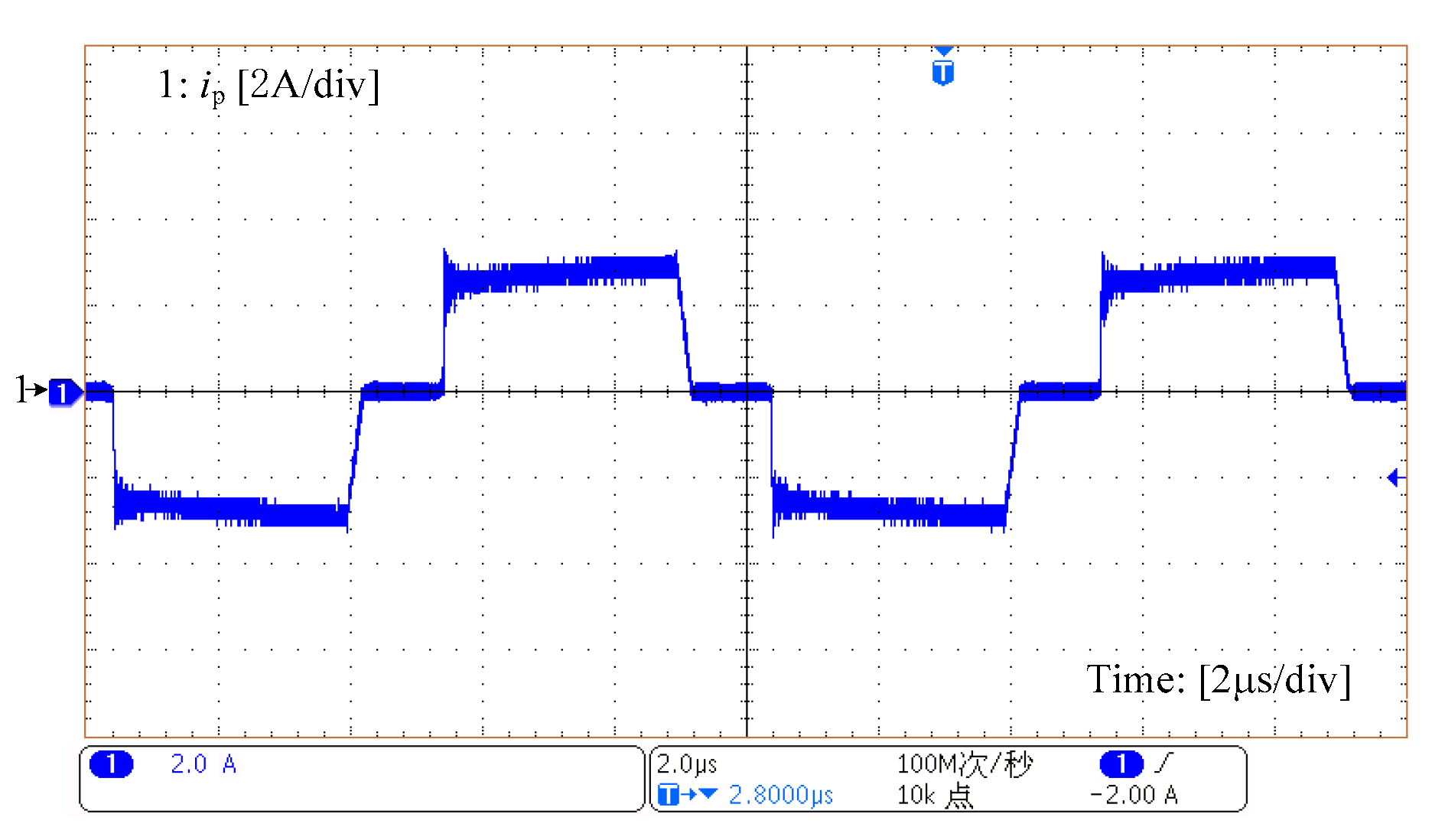

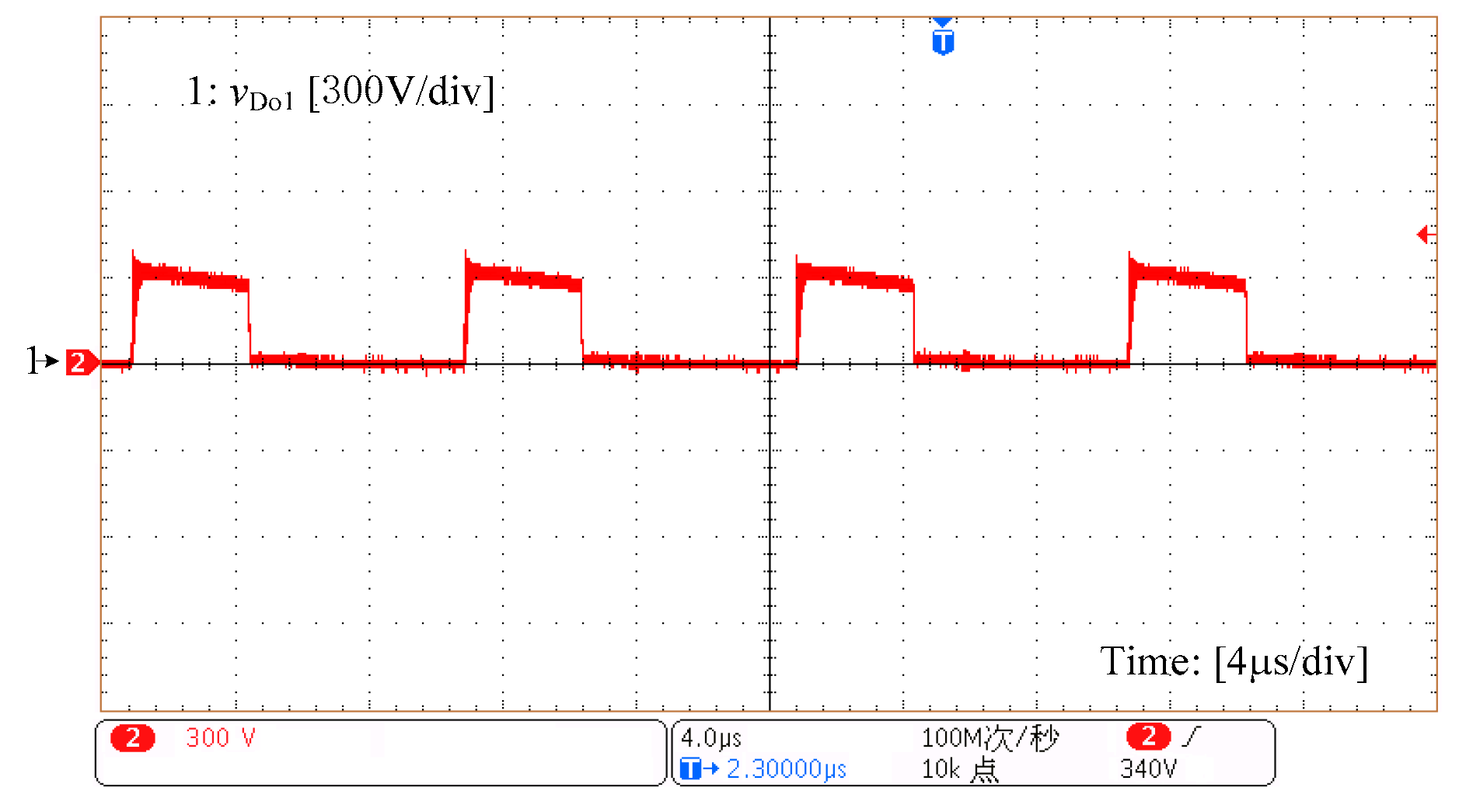

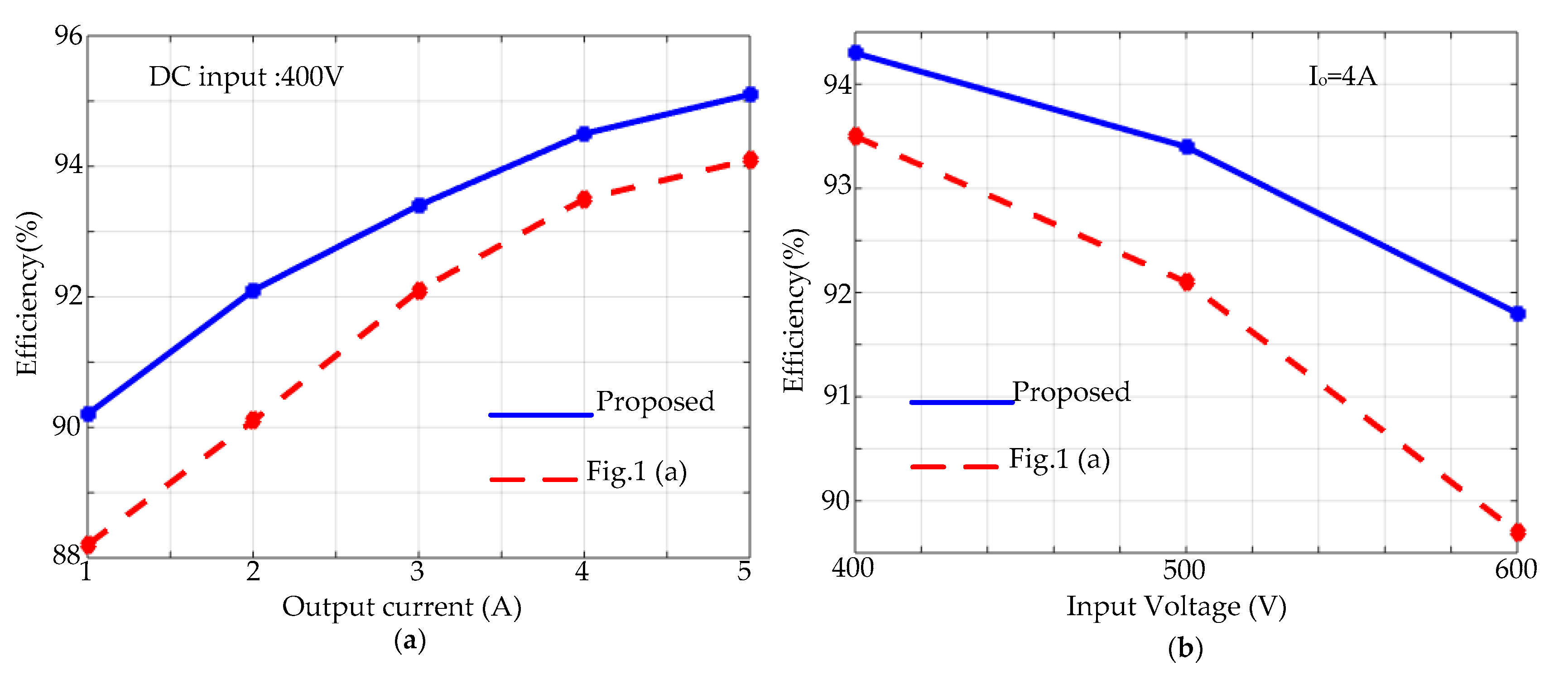

4. Experimental Results

5. Conclusions

Funding

Conflicts of Interest

References

- Pinheiro, J.R.; Barbi, I. The three-level ZVS PWM converter—A new concept in high-voltage DC-to-DC conversion. In Proceedings of the IEEE IECON, San Diego, CA, USA, 13 November 1992; pp. 173–178. [Google Scholar]

- Barbosa, P.M.; Lee, F.C. Design aspects of parallel three-phase DCM boost rectifiers. In Proceedings of the IEEE PESC, Charleston, SC, USA, 1 July 1999; pp. 331–336. [Google Scholar]

- Blaabjerg, F.; Chen, Z.; Kjaer, S.B. Power electronics as efficient interface in dispersed power generation systems. IEEE Trans. Power Electron. 2004, 19, 1184–1194. [Google Scholar] [CrossRef]

- Mohsenian, H.; Davoudi, A. Towards building an optimal demand response framework for DC distribution network. IEEE Trans. Smart Grid 2014, 5, 2626–2634. [Google Scholar] [CrossRef]

- Deschamps, E.; Barbi, I. A comparison among three-level ZVS-PWM isolated DC-to-DC converters. In Proceedings of the IEEE IECON, Aachen, Germany, 31 August–4 September 1998; pp. 1024–1029. [Google Scholar]

- Canales, F.; Barbosa, P.M.; Lee, F.C. A zero-voltage and zero current-switching three level DC/DC converter. IEEE Trans. Power Electron. 2002, 17, 898–904. [Google Scholar] [CrossRef]

- Ruan, X.; Zhou, L.; Yan, Y. Soft-switching PWM three-level converters. IEEE Trans. Power Electron. 2001, 16, 612–622. [Google Scholar] [CrossRef]

- Lin, B. Hybrid DC/DC converter based on dual three-level circuit and half-bridge circuit. IET Power Electron. 2016, 9, 817–824. [Google Scholar] [CrossRef]

- Lin, B.; Zhang, S. Analysis and implementation of a three-level hybrid dc–dc converter with the balanced capacitor voltages. IET Power Electron. 2016, 9, 457–465. [Google Scholar] [CrossRef]

- Lu, S.; Mu, M.; Jiao, Y.; Lee, F.C.; Zhao, Z. Coupled inductors in interleaved multiphase three-level DC–DC converter for high-power applications. IEEE Trans. Power Electron. 2016, 31, 120–134. [Google Scholar] [CrossRef]

- Zhang, Y.; Shi, J.; Zhou, L. Wide input-voltage range boost three-level DC–DC converter with quasi-Z source for fuel cell vehicles. IEEE Trans. Power Electron. 2017, 32, 6728–6738. [Google Scholar] [CrossRef]

- Jin, L.; Duan, S. Comparative analysis of three-level dual active bridge DC–DC converter between reflux-power-optimised and current-stress-optimised phase shift control. IET Power Electron. 2018, 11, 1681–1688. [Google Scholar] [CrossRef]

- Hong, F.; Li, L.; Wu, Y.; Ji, B.; Zhou, Y. 1500 V three-level forward converter with phase-shifted control. IET Power Electron. 2018, 11, 1547–1555. [Google Scholar] [CrossRef]

- Manoranjan, S.; Sivakumar, K. Fault tolerant three-level boost inverter with reduced source and LC count. IET Power Electron. 2018, 11, 399–405. [Google Scholar]

- Ruan, X.; Chen, Z.; Chen, W. Zero-voltage-switching PWM hybrid full-bridge three-level converter. IEEE Trans. Power Electron. 2005, 20, 395–404. [Google Scholar] [CrossRef]

- Ruan, X.; Li, B. Zero-voltage and zero-current-switching PWM hybrid full-bridge three-level converter. IEEE Trans. Ind. Electron. 2005, 52, 213–220. [Google Scholar] [CrossRef]

- Shi, Y.; Wang, X.; Xi, J.; Gui, X.W.; Yang, X. Wide load range ZVZCS three-level DC-DC converter with compact structure. IEEE Trans. Power Electron. 2019, 34, 5032–5037. [Google Scholar] [CrossRef]

- Kim, D.-Y.; Kim, J.-K.; Moon, G.-W. A three-level converter with reduced filter size using two transformers and flying capacitors. IEEE Trans. Power Electron. 2013, 28, 46–53. [Google Scholar] [CrossRef]

- Shi, Y.; Yang, X. Soft switching PWM cascaded three-level combined DC–DC converters with reduced filter size and wide ZVS load range. IEEE Trans. Power Electron. 2015, 30, 6604–6616. [Google Scholar] [CrossRef]

- Shi, Y. Full ZVS load range diode clamped three-level DC–DC converter with secondary modulation. J. Power Electron. 2016, 16, 93–101. [Google Scholar] [CrossRef]

- Liu, D.; Deng, F.; Zhang, Q.; Chen, Z. Zero-voltage switching PWM strategy based capacitor current-balancing control for half-bridge three-level DC/DC converter. IEEE Trans. Power Electron. 2018, 33, 357–369. [Google Scholar] [CrossRef]

- Liu, D.; Deng, F.; Gong, Z.; Chen, Z. Input-parallel output-parallel three-level DC/DC converters with interleaving control strategy for minimizing and balancing capacitor ripple currents. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1122–1132. [Google Scholar] [CrossRef]

- Liu, W.; Jin, H.; Yao, W.; Lu, Z. An interleaved PWM method with better voltage-balancing ability for half-bridge three-level DC/DC converter. IEEE Trans. Power Electron. 2018, 33, 4594–4598. [Google Scholar] [CrossRef]

| Item | Q1 | Q2 | Q3 | Q4 |

|---|---|---|---|---|

| Proposed | ZCZVS, easy | ZVZCS, easy | ZCZVS, easy | ZVZCS, easy |

| Figure 1a | ZVS, hard | ZVS, easy | ZVS, hard | ZVS, easy |

| Converter | Power Devices High Voltage | Power Devices Low Voltage | Capacitors Large Value | Capacitors Small Value |

|---|---|---|---|---|

| Proposed | 4 | 2 | 0 | 3 |

| [1] | 6 | 0 | 2 | 0 |

| [6] | 6 | 1 | 2 | 1 |

| [7] | 6 | 2 | 2 | 2 |

| Converter | Soft Switching Primary Switches | Soft Switching Extra Power Devices | Current Stress Primary Components | Duty Ratio Loss |

|---|---|---|---|---|

| Proposed | Good | Good | Small (even) | Small |

| [1] | Worse | NA | Large (uneven) | Large |

| [6] | Medium | Worse | Small (even) | Small |

| [7] | Medium | Good | Small (even) | Small |

| Item | Parameter |

|---|---|

| Vin | 400 V–600 V |

| Rated Vo | 200 V |

| Rated Io | 5 A |

| fs | 100 kHz |

| Q1, Q3, Q2p and Q4p | 20 A/600 V |

| Q2R, Q4R | 20 A/25 V |

| Do1 to Do4 | 20 A/600 V |

| kT | 1:1.15 |

| Cin1, Cin2 | 200 μF |

| Cs | 1.5 μF |

| Lo | 20 μH/5 A |

| Co | 200 μF |

© 2019 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shi, Y. Wide Load Range Capacitor Clamped ZVZCS Half Bridge Three-Level DC-DC Converter with Two Unsymmetrical Bi-directional Switches. Energies 2019, 12, 2362. https://doi.org/10.3390/en12122362

Shi Y. Wide Load Range Capacitor Clamped ZVZCS Half Bridge Three-Level DC-DC Converter with Two Unsymmetrical Bi-directional Switches. Energies. 2019; 12(12):2362. https://doi.org/10.3390/en12122362

Chicago/Turabian StyleShi, Yong. 2019. "Wide Load Range Capacitor Clamped ZVZCS Half Bridge Three-Level DC-DC Converter with Two Unsymmetrical Bi-directional Switches" Energies 12, no. 12: 2362. https://doi.org/10.3390/en12122362