Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review

Abstract

:1. Introduction

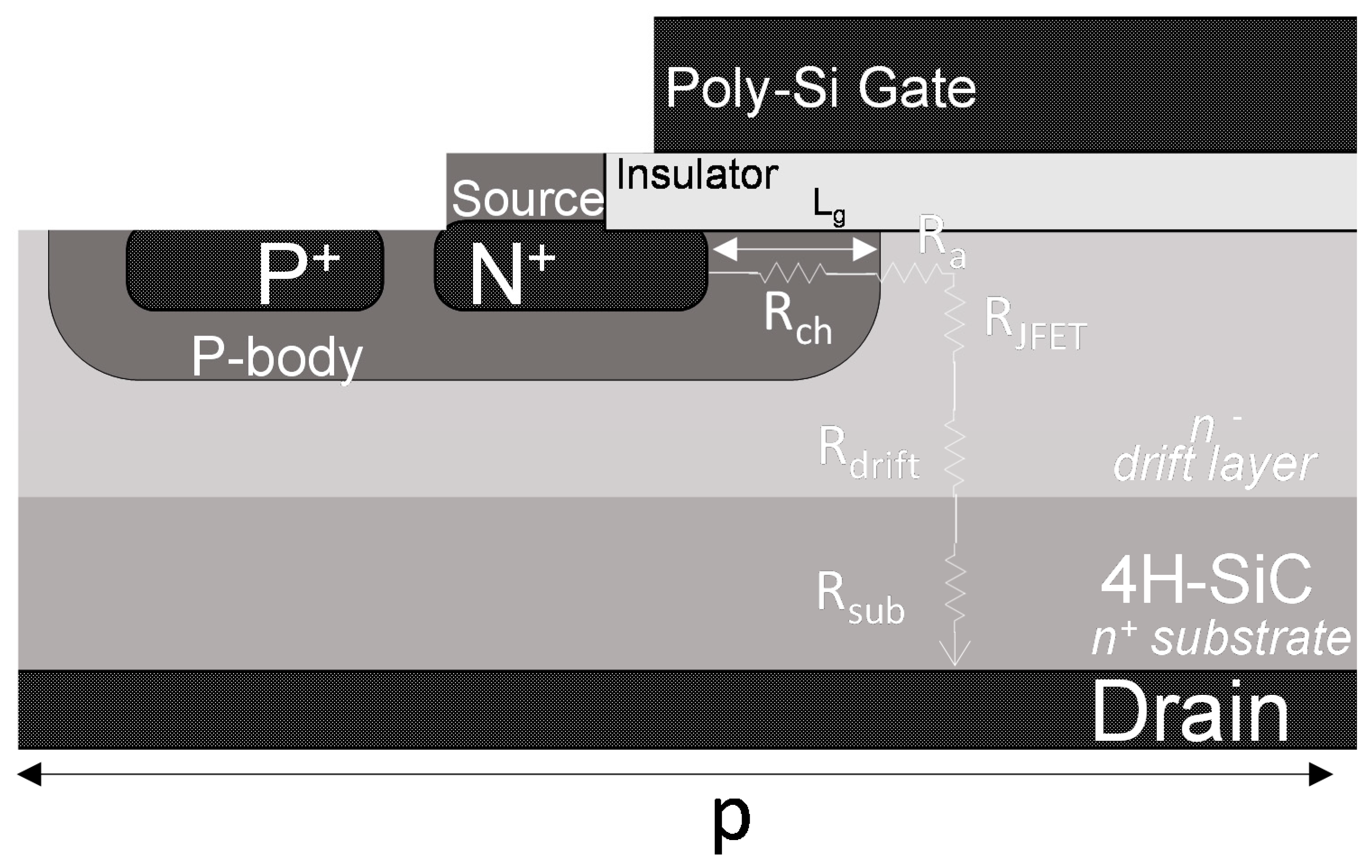

2. Interface States Density and Channel Mobility in 4H-SiC MOS-Based Devices

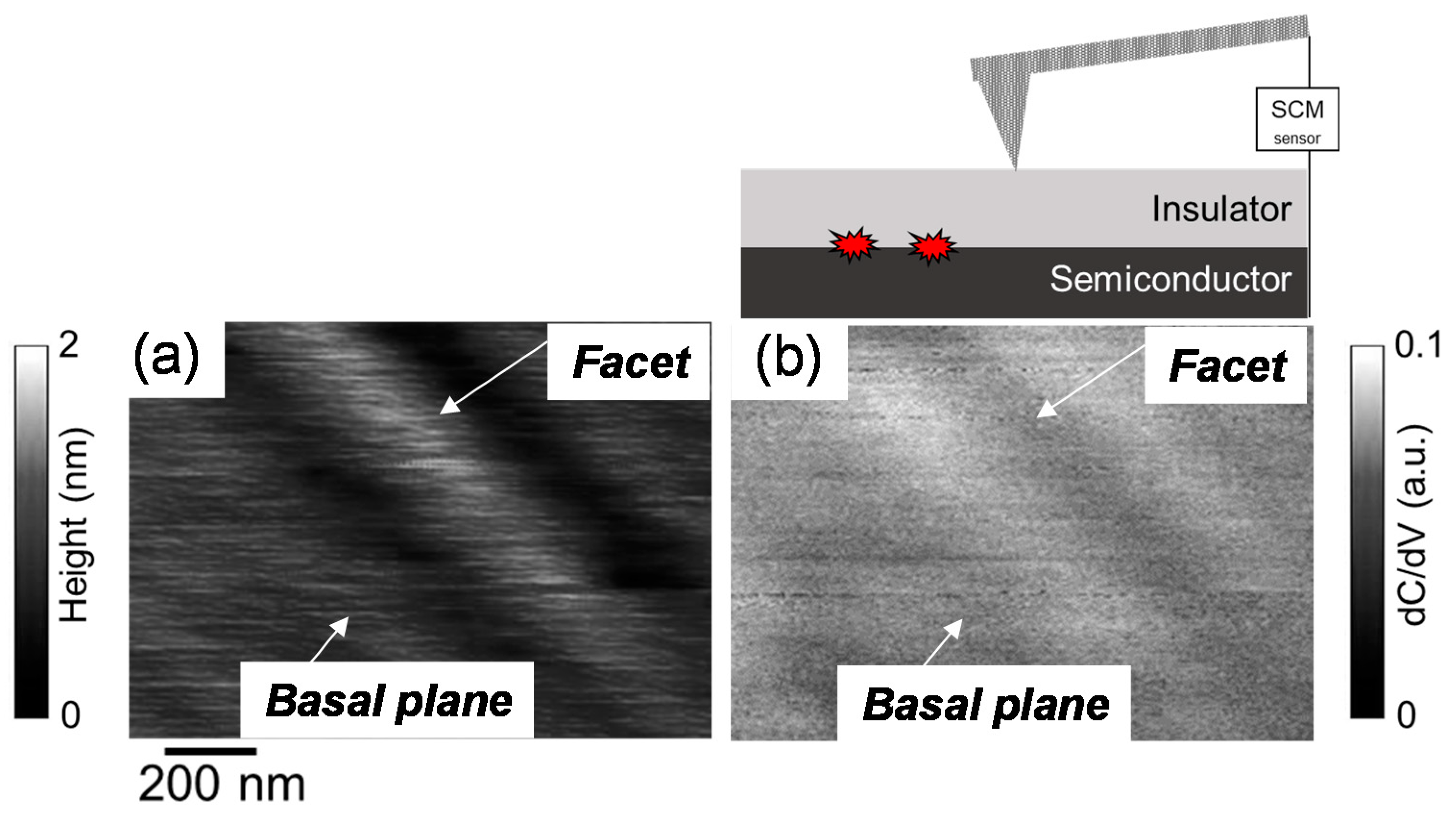

3. Nanoscale Electrical Properties of SiO2/4H-SiC Interfaces

3.1. Electrical Characterization

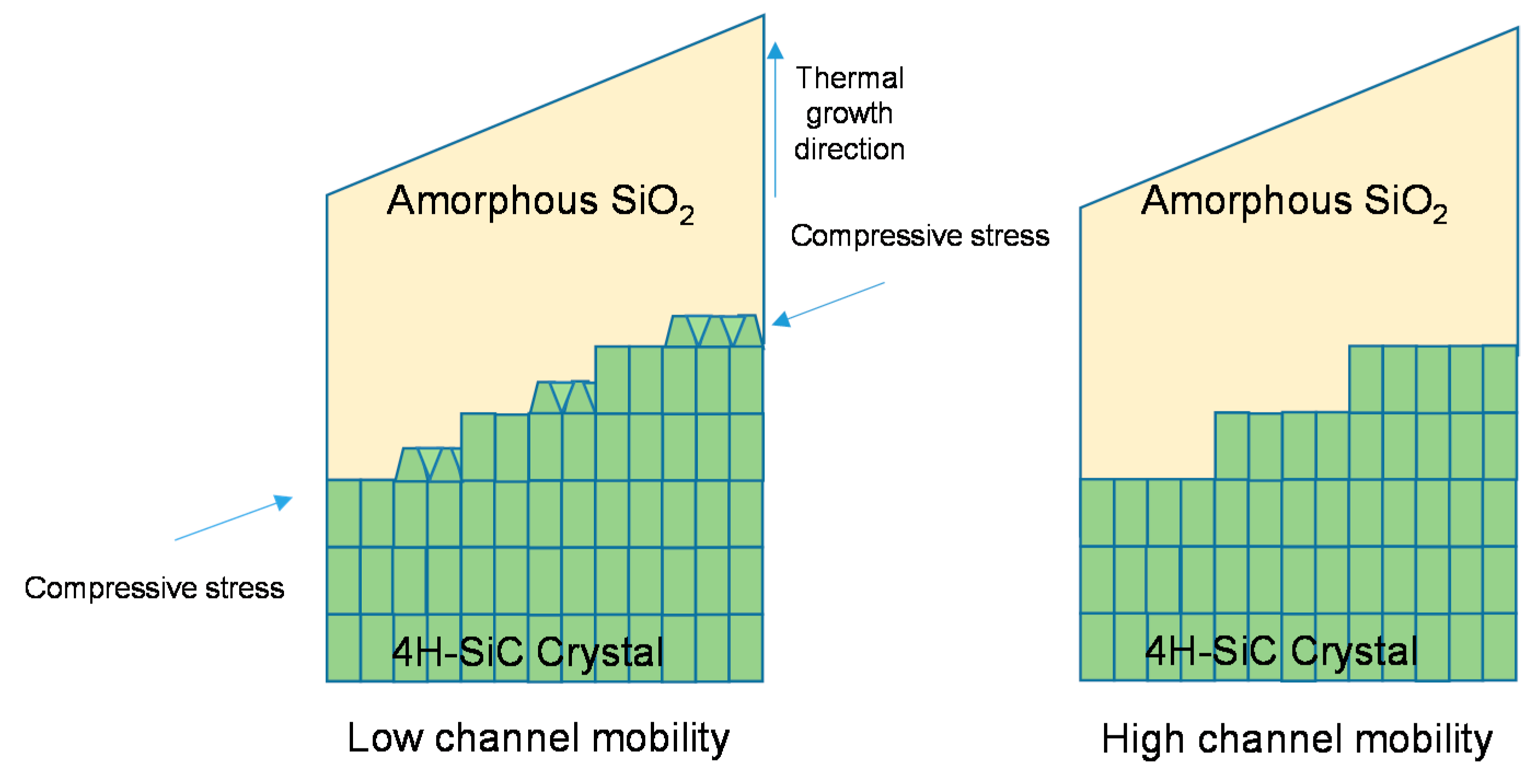

3.2. Effects of Counter Doping and Interface Stress

4. Threshold Voltage (Vth) Instability

4.1. Charge Trapping Phenomena

4.2. Chemical Nature of the NIOTs

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Cooper, J.A.; Islam, N.; Ramamurthy, R.P.; Sampath, M.; Morisette, D.T. Vertical Tri-Gate Power MOSFETs in 4H-SiC. Mater. Sci. Forum 2018, 924, 680–683. [Google Scholar] [CrossRef]

- Ohashi, H. Power devices then and now, strategy of Japan. In Proceedings of the 24th International Symposium on Power Semiconductor Devices and ICs (ISPSD2012), Bruges, Belgium, 3–7 June 2012; pp. 9–12. [Google Scholar] [CrossRef]

- Baliga, B.J. Silicon Carbide Power Devices; World Scientific Co. Pte. Ltd.: Singapore, Singapore, 2005. [Google Scholar]

- Schilirò, E.; Lo Nigro, R.; Fiorenza, P.; Roccaforte, F. Negative charge trapping effects in Al2O3 films grown by atomic layer depositiononto thermally oxidized 4H-SiC. AIP Adv. 2016, 6, 075021. [Google Scholar] [CrossRef]

- Hosoi, T.; Azumo, S.; Kashiwagi, Y.; Hosaka, S.; Nakamura, R.; Mitani, S.; Nakano, Y.; Asahara, H.; Nakamura, T.; Kimoto, T.; et al. Performance and Reliability Improvement in SiC Power MOSFETs by Implementing AlON High-k Gate Dielectrics. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012. [Google Scholar] [CrossRef]

- Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. Jpn. J. Appl. Phys. 2015, 54, 040103. [Google Scholar] [CrossRef]

- Cabello, M.; Soler, V.; Rius, G.; Montserrat, J.; Rebollo, J.; Godignon, P. Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review. Mater. Sci. Semicon. Proc. 2018, 78, 22–31. [Google Scholar] [CrossRef]

- Roccaforte, F.; Fiorenza, P.; Greco, G.; Lo Nigro, R.; Giannazzo, F.; Iucolano, F.; Saggio, M. Emerging trends in wide band gap semiconductors (SiC and GaN) technology for power devices. Microelectron. Eng. 2018, 187–188, 66–77. [Google Scholar] [CrossRef]

- Yano, H.; Kanafuji, N.; Osawa, A.; Hatayama, T.; Fuyuki, T. Threshold Voltage Instability in 4H-SiC MOSFETs With Phosphorus-Doped and Nitrided Gate Oxides. IEEE Trans. Electron. Devices 2015, 62, 324–332. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B.; El, M. Basic Mechanisms of Threshold-Voltage Instability and Implications for Reliability Testing of SiC MOSFETs. IEEE Trans. Electron Devices 2015, 62, 316–323. [Google Scholar] [CrossRef]

- Afanas’ev, V.V.; Stesmans, A. Interfacial Defects in SiO2 Revealed by Photon Stimulated Tunneling of Electrons. Phys. Rev. Lett. 1997, 78, 2437. [Google Scholar] [CrossRef]

- Pensl, G.; Ciobanu, F.; Frank, T.; Kirmse, D.; Krieger, M.; Reshanov, S.; Schmid, F.; Weidner, M.; Ohshima, T.; Itoh, H.; et al. Defect-engineering in SiC by ion implantation and electron irradiation. Microelectron. Eng. 2006, 83, 146–149. [Google Scholar] [CrossRef]

- Zhang, X.; Okamoto, D.; Hatakeyama, T.; Sometani, M.; Harada, S.; Kosugi, R.; Iwamuro, N.; Yano, H. Characterization of near-interface traps at 4H-SiC metal–oxide–semiconductor interfaces using modified distributed circuit model. Appl. Phys. Express 2017, 10, 064101. [Google Scholar] [CrossRef]

- Fujino, Y.; Kita, K. Quantitative Characterization of Near-Interface Oxide Traps in 4H-SiC MOS Capacitors by Transient Capacitance Measurements. ECS Trans. 2015, 69, 219–225. [Google Scholar] [CrossRef]

- Umeda, T.; Esaki, K.; Kosugi, R.; Fukuda, K.; Ohshima, T.; Morishita, N.; Isoya, J. Behavior of nitrogen atoms in SiC-SiO2 interfaces studied by electrically detected magnetic resonance. Appl. Phys. Lett. 2011, 99, 142105. [Google Scholar] [CrossRef]

- Roccaforte, F.; Fiorenza, P.; Greco, G.; Lo Nigro, R.; Giannazzo, F.; Patti, A.; Saggio, M. Challenges for energy efficient wide band gap semiconductor power devices. Phys. Status Solidi A 2014, 211, 2063–2071. [Google Scholar] [CrossRef]

- Li, H.-F.; Dimitrijev, S.; Harrison, H.B.; Sweatman, D. Interfacial characteristics of N2O and NO nitrided SiO2 grown on SiC by rapid thermal processing. Appl. Phys. Lett. 1997, 70, 2028. [Google Scholar] [CrossRef]

- Chung, G.Y.; Tin, C.C.; Williams, J.R.; McDonald, K.; Di Ventra, M.; Pantelides, S.T.; Feldman, L.C.; Weller, R.A. Effect of nitric oxide annealing on the interface trap densities near the band edges in the 4H polytype of silicon carbide. Appl. Phys. Lett. 2000, 76, 1713. [Google Scholar] [CrossRef]

- Lipkin, L.A.; Das, M.K.; Palmour, J.W. N2O Processing Improves the 4H-SiC:SiO2 Interface. Mater. Sci. Forum 2002, 389–393, 985–988. [Google Scholar] [CrossRef]

- Lu, C.-Y.; Cooper, J.A.; Tsuji, T.; Chung, G.; Williams, J.R.; McDonald, K.; Feldman, L.C. Effect of process variations and ambient temperature on electron mobility at the SiO2/4H-SiC interface. IEEE Trans. Electron Devices 2003, 50, 1582–1588. [Google Scholar]

- Harada, S.; Kosugi, R.; Senzaki, J.; Cho, W.-J.; Fukuda, K.; Arai, K. Relationship between channel mobility and interface state density in SiC metal–oxide–semiconductor field-effect transistor. J. Appl. Phys. 2002, 91, 1568. [Google Scholar] [CrossRef]

- Pérez-Tomás, A.; Brosselard, P.; Godignon, P.; Millán, J.; Mestres, N.; Jennings, M.R.; Covington, J.A.; Mawby, P.A. Field-effect mobility temperature modeling of 4H-SiC metal-oxide-semiconductor transistors. J. Appl. Phys. 2006, 100, 114508. [Google Scholar] [CrossRef]

- Jamet, P.; Dimitrijev, S.; Tanner, P. Effects of nitridation in gate oxides grown on 4H-SiC. J. Appl. Phys. 2001, 90, 5058. [Google Scholar] [CrossRef]

- Dhar, S.; Ahyi, A.C.; Williams, J.R.; Ryu, S.-H.; Agarwal, A.K. Temperature Dependence of Inversion Layer Carrier Concentration and Hall Mobility in 4H-SiC MOSFETs. Mater. Sci. Forum 2012, 717–720, 713. [Google Scholar] [CrossRef]

- Chung, G.Y.; Tin, C.C.; Williams, J.R.; McDonald, K.; Chanana, R.K.; Weller, R.A.; Pantelides, S.T.; Feldman, L.C.; Holland, O.W.; Das, M.K.; et al. Improved Inversion Channel Mobility for 4H-SiC MOSFETs Following High Temperature Anneals in Nitric Oxide. IEEE Electron Devices Lett. 2001, 22, 176–178. [Google Scholar] [CrossRef]

- Kosugi, R.; Fukuda, K.; Arai, K. High Temperature Rapid Thermal Oxidation and Nitridation of 4H-SiC in Diluted N2O and NO Ambient. Mater. Sci. Forum 2005, 483–485, 669–672. [Google Scholar] [CrossRef]

- Wang, Y.; Tang, K.; Khan, T.; Balasubramanian, M.K.; Naik, H.; Wang, W.; Chow, T.P. The effect of gate oxide processes on the performance of 4H-SiC MOSFETs and gate-controlled diodes. IEEE Trans. Electron Devices 2008, 55, 2046–2053. [Google Scholar] [CrossRef]

- Rozen, J.; Ahyi, A.C.; Zhu, X.; Williams, J.R.; Feldman, L.C. Scaling Between Channel Mobility and Interface State Density in SiC MOSFETs. IEEE Trans. Electron Devices 2011, 58, 3808–3811. [Google Scholar] [CrossRef]

- Frazzetto, A.; Giannazzo, F.; Fiorenza, P.; Raineri, V.; Roccaforte, F. Limiting mechanism of inversion channel mobility in Al-implanted lateral 4H-SiC metal-oxide semiconductor field-effect transistors. Appl. Phys. Lett. 2011, 99, 072117. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Frazzetto, A.; Roccaforte, F. Influence of the surface morphology on the channel mobility of lateral implanted 4H-SiC(0001) metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 2012, 112, 084501. [Google Scholar] [CrossRef] [Green Version]

- Dhar, S.; Wang, S.; Williams, J.; Pantelides, S.; Feldman, L. Interface Passivation for Silicon Dioxide Layers on Silicon Carbide. MRS Bull. 2005, 30, 288–292. [Google Scholar] [CrossRef]

- Kobayashi, T.; Suda, J.; Kimoto, T. Reduction of interface state density in SiC (0001) MOS structures by post-oxidation Ar annealing at high temperature. AIP Adv. 2017, 7, 045008. [Google Scholar] [CrossRef] [Green Version]

- Hatakeyama, T.; Kiuchi, Y.; Sometani, M.; Harada, S.; Okamoto, D.; Yano, H.; Yonezawa, Y.; Okumura, H. Characterization of traps at nitrided SiO2/SiC interfaces near the conduction band edge by using Hall effect measurements. Appl. Phys. Express 2017, 10, 046601. [Google Scholar] [CrossRef]

- Asaba, S.; Schimizu, T.; Nakabayashi, Y.; Fukatsu, S.; Ito, T.; Iijima, R. Novel Gate Insulator Process by Nitrogen Annealing for Si-Face SiC MOSFET with High-Mobility and High-Reliability. Mater. Sci. Forum 2018, 924, 457. [Google Scholar] [CrossRef]

- Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Martens, K.; On Chui, C.; Brammertz, G.; De Jaeger, B.; Kuzum, D.; Meuris, M.; Heyns, M.M.; Krishnamohan, T.; Saraswat, K.; Maes, H.E.; et al. On the Correct Extraction of Interface Trap Density of MOS Devices with High-Mobility Semiconductor Substrates. IEEE Trans. Electron Devices 2008, 55, 547. [Google Scholar] [CrossRef]

- Yoshioka, H.; Nakamura, T.; Kimoto, T. Generation of very fast states by nitridation of the SiO2/SiC interface. J. Appl. Phys. 2012, 111, 014502. [Google Scholar] [CrossRef]

- Nakazawa, S.; Okuda, T.; Suda, J.; Nakamura, T.; Kimoto, T. Interface Properties of 4H-SiC (11¯20) and (1¯100) MOS Structures Annealed in NO. IEEE Trans. Electron Devices 2015, 62, 309. [Google Scholar] [CrossRef]

- Groeseneken, G.; Maes, H.E.; Beltran, N.; DeKeersmaecker, R.F. A reliable approach to charge-pumping measurements in MOS transistors. IEEE Trans. Electron Devices 1984, ED-31, 42–53. [Google Scholar] [CrossRef]

- Okamoto, D.; Yano, H.; Hatayama, T.; Uraoka, Y.; Fuyuki, T. Analysis of Anomalous Charge-Pumping Characteristics on 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2008, 55, 2013. [Google Scholar] [CrossRef]

- Salinaro, A.; Pobegen, G.; Aichinger, T.; Zippelius, B.; Peters, D.; Friedrichs, P.; Frey, L. Charge Pumping Measurements on Differently Passivated Lateral 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2015, 62, 155. [Google Scholar] [CrossRef]

- Saks, N.S.; Agarwal, A.K. Hall mobility and free electron density at the SiC/SiO2 interface in 4H-SiC. Appl. Phys. Lett. 2000, 77, 3281–3283. [Google Scholar] [CrossRef]

- Uhnevionak, V.; Burenkov, A.; Strenger, C.; Ortiz, G.; Bedel-Pereira, E.; Mortet, V.; Cristiano, F.; Bauer, A.J.; Pichler, P. Comprehensive Study of the Electron Scattering Mechanisms in 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2015, 62, 2562–2570. [Google Scholar] [CrossRef]

- Hauck, M.; Lehmeyer, J.; Pobegen, G.; Weber, H.B.; Krieger, M. An adapted method for analyzing 4H silicon carbide metal-oxide-semiconductor field-effect transistors. Commun. Phys. 2019, 2, 5. [Google Scholar]

- Cabello, M.; Soler, V.; Haasmann, D.; Montserrat, J.; Rebollo, J.; Godignon, P. Evidence of Channel Mobility Anisotropy on 4H-SiC MOSFETs with Low Interface Trap Density Invited Poster ECSCRM 2018. Available online: https://warwick.ac.uk/fac/sci/eng/ecscrm2018/programme/ecscrm_programme_2018.pdf (accessed on 20 May 2019).

- Fiorenza, P.; Di Franco, S.; Giannazzo, F.; Roccaforte, F. Nanoscale probing of the lateral homogeneity of donors concentration in nitridated SiO2/4H-SiC interfaces. Nanotechnology 2016, 27, 315701. [Google Scholar] [CrossRef] [PubMed]

- Fiorenza, P.; Giannazzo, F.; Swanson, L.K.; Frazzetto, A.; Lorenti, S.; Alessandrino, M.S.; Roccaforte, R. A look underneath the SiO2/4H-SiC interface after N2O thermal treatments. Beilstein J. Nanotechnol. 2013, 4, 249–254. [Google Scholar] [CrossRef] [PubMed]

- Saitoh, H.; Seki, A.; Manabe, A.; Kimoto, T. Interface Properties of SiO2/4H-SiC(0001) with Large Off-Angles Formed by N2O Oxidation. Mater. Sci. Forum 2007, 556–557, 659–662. [Google Scholar] [CrossRef]

- Kosugi, R.; Umeda, T.; Sakuma, Y. Fixed nitrogen atoms in the SiO2/SiC interface region and their direct relationship to interface trap density. Appl. Phys. Lett. 2011, 99, 182111. [Google Scholar] [CrossRef]

- Swanson, L.K.; Fiorenza, P.; Giannazzo, F.; Frazzetto, A.; Roccaforte, F. Correlating macroscopic and nanoscale electrical modifications of SiO2/4H-SiC interfaces upon post-oxidation-annealing in N2O and POCl3. Appl. Phys. Lett. 2012, 101, 193501. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Vivona, M.; La Magna, A.; Roccaforte, F. SiO2/4H-SiC interface doping during post-deposition-annealing of the oxide in N2O or POCl3. Appl. Phys. Lett. 2013, 103, 153508. [Google Scholar] [CrossRef]

- Fiorenza, P.; Iucolano, F.; Nicotra, G.; Bongiorno, C.; Deretzis, I.; La Magna, A.; Giannazzo, F.; Saggio, M.; Spinella, C.; Roccaforte, F. Electron trapping at SiO2/4H-SiC interface probed by transient capacitance measurements and atomic resolution chemical analysis. Nanotechnology 2018, 29, 395702. [Google Scholar] [CrossRef] [PubMed]

- Regoutz, A.; Pobegen, G.; Aichinger, T. Interface chemistry and electrical characteristics of 4H-SiC/SiO2 after nitridation in varying atmospheres. J. Mater. Chem. C 2018, 6, 12079. [Google Scholar] [CrossRef]

- Giannazzo, F.; Fiorenza, P.; Raineri, V. Carrier transport in advanced semiconductor materials. In Applied Scanning Probe Methods X; Springer: Berlin/Heidelberg, Germany, 2008; pp. 63–103. [Google Scholar]

- Fiorenza, P.; Vivona, M.; Iucolano, F.; Severino, A.; Lorenti, S.; Nicotra, G.; Bongiorno, C.; Giannazzo, F.; Roccaforte, F. Temperature-dependent Fowler-Nordheim electron barrier height in SiO2/4H-SiC MOS capacitors. Mater. Sci. Semicon. Process. 2018, 78, 38–42. [Google Scholar] [CrossRef]

- Okamoto, D.; Yano, H.; Hirata, K.; Hatayama, T.; Fuyuki, T. Improved Inversion Channel Mobility in 4H-SiC MOSFETs on Si Face Utilizing Phosphorus-Doped Gate Oxide. IEEE Electron Devices Lett. 2010, 31, 710–712. [Google Scholar] [CrossRef]

- Yano, H.; Araoka, T.; Hatayama, T.; Fuyuki, T. Improved Stability of 4H-SiC MOS Device Properties by Combination of NO and POCl3 Annealing. Mater. Sci. Forum 2013, 740–742, 727–732. [Google Scholar] [CrossRef]

- Sharma, Y.K.; Ahyi, A.C.; Isaacs-Smith, T.; Modic, A.; Park, M.; Xu, Y.; Garfunkel, E.L.; Dhar, S.; Feldman, L.C.; Williams, J.R. High-Mobility Stable 4H-SiC MOSFETs Using a Thin PSG Interfacial Passivation Layer. IEEE Electron Devices Lett. 2013, 34, 175–177. [Google Scholar] [CrossRef]

- Modic, A.; Liu, G.; Ahyi, A.C.; Zhou, Y.; Xu, P.; Hamilton, M.C.; Williams, J.R.; Feldman, L.C.; Dhar, S. High Channel Mobility 4H-SiC MOSFETs by Antimony Counter-Doping. IEEE Electron Devices Lett. 2014, 35, 894. [Google Scholar] [CrossRef]

- Lichtenwalner, D.J.; Cheng, L.; Dhar, S.; Agarwal, A.; Palmour, J.W. High mobility 4H-SiC (0001) transistors using alkali and alkaline earth interface layers. Appl. Phys. Lett. 2014, 105, 182107. [Google Scholar] [CrossRef]

- Okamoto, D.; Sometani, M.; Harada, S.; Kosugi, R.; Yonezawa, Y.; Yano, H. Improved Channel Mobility in 4H-SiC MOSFETs by Boron Passivation. IEEE Electron Devices Lett. 2014, 35, 1176–1178. [Google Scholar] [CrossRef]

- Huston Dycus, J.; Xu, W.; Lichtenwalner, D.J.; Hull, B.; Palmour, J.W.; LeBeau, J.M. Structure and chemistry of passivated SiC/SiO2 interfaces. Appl. Phys. Lett. 2016, 108, 201607. [Google Scholar] [CrossRef]

- Yang, X.; Lee, B.; Misra, V. High Mobility 4H-SiC Lateral MOSFETs Using Lanthanum Silicate and Atomic Layer Deposited SiO2. IEEE Electron Devices Lett. 2015, 36, 312–314. [Google Scholar] [CrossRef]

- Li, X.; Ermakov, A.; Amarasinghe, V.; Garfunkel, E.; Gustafsson, T.; Feldman, L.C. Oxidation induced stress in SiO2/SiC structures. Appl. Phys. Lett. 2017, 110, 141604. [Google Scholar] [CrossRef]

- Lichtenwalner, D.J.; Cheng, L.; Dhar, S.; Agarwal, A.K.; Allen, S.; Palmour, J.W. High-Mobility SiC MOSFETs with Chemically Modified Interfaces. Mater. Sci. Forum 2015, 821–823, 749. [Google Scholar] [CrossRef]

- Fiorenza, P.; Swanson, L.K.; Vivona, M.; Giannazzo, F.; Bongiorno, C.; Frazzetto, A.; Roccaforte, F. Comparative study of gate oxide in 4H-SiC lateral MOSFETs subjected to post-deposition-annealing in N2O and POCl3. Appl. Phys. A 2014, 115, 333. [Google Scholar] [CrossRef]

- Aviñó Salvadó, O.; Morel, H.; Buttay, C.; Labrousse, D.; Lefebvre, S. Threshold voltage instability in SiC MOSFETs as a consequence of current conduction in their body diode. Microelectron. Reliab. 2018, 88–90, 636. [Google Scholar]

- Fiorenza, P.; Greco, G.; Giannazzo, F.; Iucolano, F.; Roccaforte, F. Effects of interface states and near interface traps on the threshold voltage stability of GaN and SiC transistors employing SiO2 as gate dielectric. J. Vacuum Sci. Technol. B 2017, 35, 01A101. [Google Scholar] [CrossRef]

- Fiorenza, P.; Frazzetto, A.; Guarnera, A.; Saggio, M.; Roccaforte, F. Fowler-Nordheim tunneling at SiO2/4H-SiC interfaces in metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 2014, 105, 142108. [Google Scholar] [CrossRef]

- Fiorenza, P.; La Magna, A.; Vivona, M.; Roccaforte, F. Near interface traps in SiO2/4H-SiC metal-oxide-semiconductor field effect transistors monitored by temperature dependent gate current transient measurements. Appl. Phys. Lett. 2016, 109, 012102. [Google Scholar] [CrossRef]

- Hayashi, M.; Sometani, M.; Hatakeyama, T.; Yano, H.; Harada, S. Hole trapping in SiC-MOS devices evaluated by fast-capacitance–voltage method. Jpn. J. Appl. Phys. 2018, 57, 04FR15. [Google Scholar] [CrossRef]

- Bauza, D.; Ghibaudo, G. Analytical study of the contribution of fast and slow oxide traps to the charge pumping current in MOS structures. Solid-State Electron. 1996, 39, 563–570. [Google Scholar] [CrossRef]

- Paulsen, R.E.; Siergiej, R.R.; French, M.L.; White, M.H. Observation of Near-Interface Oxide Traps with the Charge-Pumping Technique. IEEE Electron Device Lett. 1992, 13, 627–629. [Google Scholar] [CrossRef]

- Chanana, R.K.; McDonald, K.; Di Ventra, M.; Pantelides, S.T.; Feldman, L.C.; Chung, G.Y.; Tin, C.C.; Williams, J.R.; Weller, R.A. Fowler–Nordheim hole tunneling in p-SiC/SiO2 structures. Appl. Phys. Lett. 2000, 77, 2560. [Google Scholar] [CrossRef]

- Aichinger, T.; Rescher, G.; Pobegen, G. Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs. Microelectron. Reliab. 2018, 80, 68–78. [Google Scholar] [CrossRef]

- Pande, P.; Dimitrijev, S.; Haasmann, D.; Amini Moghadam, H.; Tanner, P.; Han, J. Direct Measurement of Active Near-Interface Traps in the Strong-Accumulation Region of 4H-SiC MOS Capacitors. IEEE J. Electron Devices Soc. 2018, 6, 468. [Google Scholar] [CrossRef]

- Knaup, J.M.; Deák, P.; Frauenheim, T.; Gali, A.; Hajnal, Z.; Choyke, W.J. Defects in SiO2 as the possible origin of near interface traps in the SiC/SiO2 system: A systematic theoretical study. Phys. Rev. B 2005 72, 115323.

- Devynck, F.; Alkauskas, A.; Broqvist, P.; Pasquarello, A. Charge transition levels of carbon-, oxygen-, and hydrogen-related defects at the SiC/SiO2 interface through hybrid functionals. Phys. Rev. B 2011, 84, 235320. [Google Scholar] [CrossRef]

- Zheleva, T.; Lelis, A.; Duscher, G.; Liu, F.; Levin, I.; Das, M. Transition layers at the SiO2/Si C interface. Appl. Phys. Lett. 2008, 93, 022108. [Google Scholar] [CrossRef]

- Biggerstaff, T.L.; Reynolds, C.L., Jr.; Zheleva, T.; Lelis, A.; Habersat, D.; Haney, S.; Ryu, S.-H.; Agarwal, A.; Duscher, G. Relationship between 4H-SiC/SiO2 transition layer thickness and mobility. Appl. Phys. Lett. 2009, 95, 032108. [Google Scholar] [CrossRef]

| Process | Temperature (°C) | µ (cm2V−1s−1) | Dit (cm−2eV−1) | Methods | NA (cm−3) | Ref. |

|---|---|---|---|---|---|---|

| Dry | 1175 | 4 | 9 × 1012 | Gp/ω | 1 × 1016 epi | [19,21] |

| NO | 1175 | 32 | N.A. | N.A. | 8 × 1015 epi | [20,25] |

| NO 10 min | 1250 | 20 | 2 × 1014 | Hall | 1.3 × 1015 | [33] |

| NO 60 min | 1250 | 38 | 8 × 1013 | Hall | 2.3 × 1015 | [28,33] |

| NO 120 min | 1250 | 34 | 5–6 × 1013 | Hall | 2.7 × 1015 | [33] |

| N2O | 1300 | 55-99 | 4 × 1011 | Gp/ω | 1 × 1016 epi | [19,24] |

| N2O | 1150 | 24-40 | 4–8 × 1011 | Gp/ω | 1 × 1017 imp | [29,30] |

| N2O | 1410 | N.A. | 1 × 1012 | High-low | 5 × 1015 epi | [26] |

| O2 + N2 | 900 + 1300 | 50 | 3 × 1011 | High-low | 5 × 1015 epi | [34] |

| Ar | 1500 | N.A. | 2 × 1012 | C–ψ | ND = 1 × 1016 epi | [22,32] |

| Characterisation Methods | Device Typology | Advantages | Limitations | Dit Range (cm−2eV−1) | Ref. |

|---|---|---|---|---|---|

| High-low | MOS | Precise in devices with low Dit values | It can be affected by insulator traps | 1010–1012 | [35] |

| Gp/ω | MOS/ MOSFETs | Able to separate the frequency response of slow and fast states | Unable to probe fast states at frequency >100MHz | >1 × 109 | [35] |

| C-ψ | MOS/ MOSFETs | Accurate on large Dit value and on a broad frequency range | Need of a precise knowledge of the doping | >1 × 1011 | [37] |

| Sub-threshold | MOSFET | Quick method to qualitatively compare different processes | Difficult to estimate the absolute Dit value | >2 × 1011 | [35] |

| Charge pumping | MOSFET | Access to acceptor and Dit states | Difficult estimation of Dit near the conduction band edge | >1 × 1011 | [40,41] |

| Characterisation Methods | Device Typology | Advantages | Disadvantages | Reference |

|---|---|---|---|---|

| Effective mobility () | Lateral MOSFET | Fast comparison of different processes. Wafer level characterization | Incorrect estimation of the amount of the free carriers | [35] |

| Field effect mobility () | ||||

| Hall effect | MOSFET Hall bars | Separation of the trapped and free carriers | Need for multi terminal structures. Characterization on discrete devices only | [33,34] |

| Gate Oxide Interface Contamination | Temperature (°C) | µ (cm2V−1s−1) | Element Group | Counter Doping | Dit (cm−2eV−1) | Ref. |

|---|---|---|---|---|---|---|

| Lanthanum | NA | 133 | Lanthanides | N.A. | NA | [63] |

| Boron | 950 | 100 | III | No | 9 × 1010 | [61,64] |

| Phosphorous | 1000 | 108 | V | Yes | 5 × 1011 | [51] |

| Antimony | 1150 | 65–110 | V | Yes | NA | [59] |

| Barium | 950 | 85 | II | No | 3 × 1011 | [60] |

| Calcium | 950 | 1–5 | II | No | NA | [60] |

| Strontium | 950 | 40 | II | No | 3 × 1011 | [60] |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fiorenza, P.; Giannazzo, F.; Roccaforte, F. Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review. Energies 2019, 12, 2310. https://doi.org/10.3390/en12122310

Fiorenza P, Giannazzo F, Roccaforte F. Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review. Energies. 2019; 12(12):2310. https://doi.org/10.3390/en12122310

Chicago/Turabian StyleFiorenza, Patrick, Filippo Giannazzo, and Fabrizio Roccaforte. 2019. "Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review" Energies 12, no. 12: 2310. https://doi.org/10.3390/en12122310