1. Introduction

Photovoltaic (PV) energy has become an attractive renewable energy source due to its user-friendly operation, straightforward structure, easy installation, and close setup to the user. In PV energy conversion and distribution systems, three-phase four-leg inverters are becoming popular in specific applications such as standalone [

1] and Uninterruptible power supply (UPS) systems [

2], as well as in islanded mode when the grid supply has failed [

3]. A standalone PV system has to provide uninterrupted and balanced/unbalanced power for utilities such as data communication, aircraft, home appliances, satellite stations, and railway systems [

4]. However, delivering an unbalanced load is a commercial and industrial issue in an energy conversion system. A four-wire three-leg inverter can be used to deliver unbalanced power, but it has the drawback of low utilization DC-link voltage. The potential difference between the star point and the midpoint of DC-link capacitors is forced to zero; therefore, the star point of the load is not free [

5,

6]. Thus, four-leg inverters have been introduced that can provide zero sequence paths, and are thus preferred over three-leg inverters to distribute power to the balanced/unbalanced loads. Moreover, three-phase four-leg inverters can overcome the low voltage DC-link utilization of the three-phase four-wire system [

7]. Due to the additional leg, the control vectors increase from 8 (2

3) to 16 (2

4), which increases the number of switching actions in every switching period [

8,

9,

10]. However, the common mode voltage (CMV) between the load-neutral point and the midpoint of the DC-link capacitors of the three-phase four-leg inverter causes radiation in the electromagnetic interference, system losses, and threats to personal safety [

11].

In order to overcome these problems, the CMV has to be mitigated or reduced. This can be achieved actively or passively. In active mitigation, active circuits such as transistors and capacitors are used. Meanwhile, passive components are used in passive mitigation [

12]. Owing to hardware additions or modifications, these methods lead to increases in size and higher costs, and thus cannot be directly applicable to high-voltage systems. Thus, research is progressing towards software invention or modification through improving the control algorithm. The improvement in software can be divided into two main types. The first type is achieved with a modulation-based control algorithm. In a three-phase four-leg inverter, CMV can be kept constant at ±

(

is the DC-link voltage) by improving the modulation mode with the Boolean logic function [

13]. A pulse width modulation (PWM) block that avoids the zero-voltage vector has been introduced to alleviate the CMV in [

14]. A control scheme with six switching states for the three-phase four-leg inverter is proposed to ensure the zero CMV in [

15]. However, this switching scheme cannot be practically implemented for the unbalanced condition due to the utilization of the restricted voltage vector in a conventional method. The aforementioned PWM-based control algorithms consist of a modulation stage and an inner control loop with proportional–integral (PI) controllers. In the second type of improvement scheme, an easier and more powerful control method, the finite control set model predictive control (FCS-MPC) is used. The FCS-MPC considers a finite number of valid switching states to predict the behavior of the system through a discrete model in every sampling period [

16,

17,

18,

19]. The FCS-MPC uses a cost function to carry out the optimization in the prediction. The predefined cost function is used to compare each prediction with its respective reference, and the switching state that produces the minimum value of the cost function is applied to the inverter. This process is repeated in every sampling period as mentioned in [

9,

20,

21,

22], and thus, no modulation stage is required in this technique. The implementation of the FCS-MPC is very easy and simple, and it has fast a dynamic response in spite of its constraints and nonlinearity inclusion [

8,

23,

24,

25]. However, since the FCS-MPC algorithm predicts the control variables based on the system model, it puts a high computational burden on the controller [

20,

26,

27]. This FCS-MPC-based control technique also can be used to restrict the CMV within ±

by utilizing six non-zero voltage vectors in the three-phase three-leg inverter [

28]. The FCS-MPC method can reduce the CMV and control the load current for the three-phase three-leg inverter, as mentioned in [

28,

29,

30]. Meanwhile, in [

29], the load current ripple and CMV are reduced, but the process of selecting two non-zero voltage vectors in each sampling period and determining each vector duration is very complex. This greatly increases the computation complexity. Guo et al. [

31] proposed the use of four non-zero voltage vectors in order to reduce the CMV for three-phase three-leg inverters to ±

, but the complicated switching selection between opposite voltage vectors increases the switching losses. In [

32], the CMV factor is inserted into the cost function in order to reduce the CMV, but this increases the ripple content in the load current. In recent works, there is a lack of CMV mitigation with reduced computational burden, and most of the research studies have focused on the three-phase three-leg inverter. Thus, further research work is required for the three-phase four-leg inverter.

In this paper, a near state vector selection-based MPC (NSV-MPC) is proposed in order to reduce the CMV with reduced computational burden for a three-phase four-leg inverter. Based on near state voltage vector, a cost function is used in the predictive model to determine the optimal switching voltage vector from the vectors that surround the future reference voltage vector. The reference voltage vector and its NSV are determined by the future reference currents. In order to reduce the CMV, the zero-switching voltage vector has to be eliminated from the switching state, because it is causing a high CMV. Thus, only six switching states are required to predict the future voltage vector. Consequently, only six repeated iterations are required in every sampling period, which reduces the computational burden.

The rest of this paper is structured as follows: the mathematical models for the inverter-load system are derived in

Section 2. Then, the model predictive control for three-phase four-leg inverter is explained in

Section 3, and the proposed control technique is described in

Section 4. The proposed system is then validated through simulation, and the experimental results are given in

Section 5. Afterwards, the robustness and performance analysis are discussed in

Section 6. Then, the appropriate conclusions are drawn in

Section 7.

2. Three-Phase Four-Leg Inverter Model

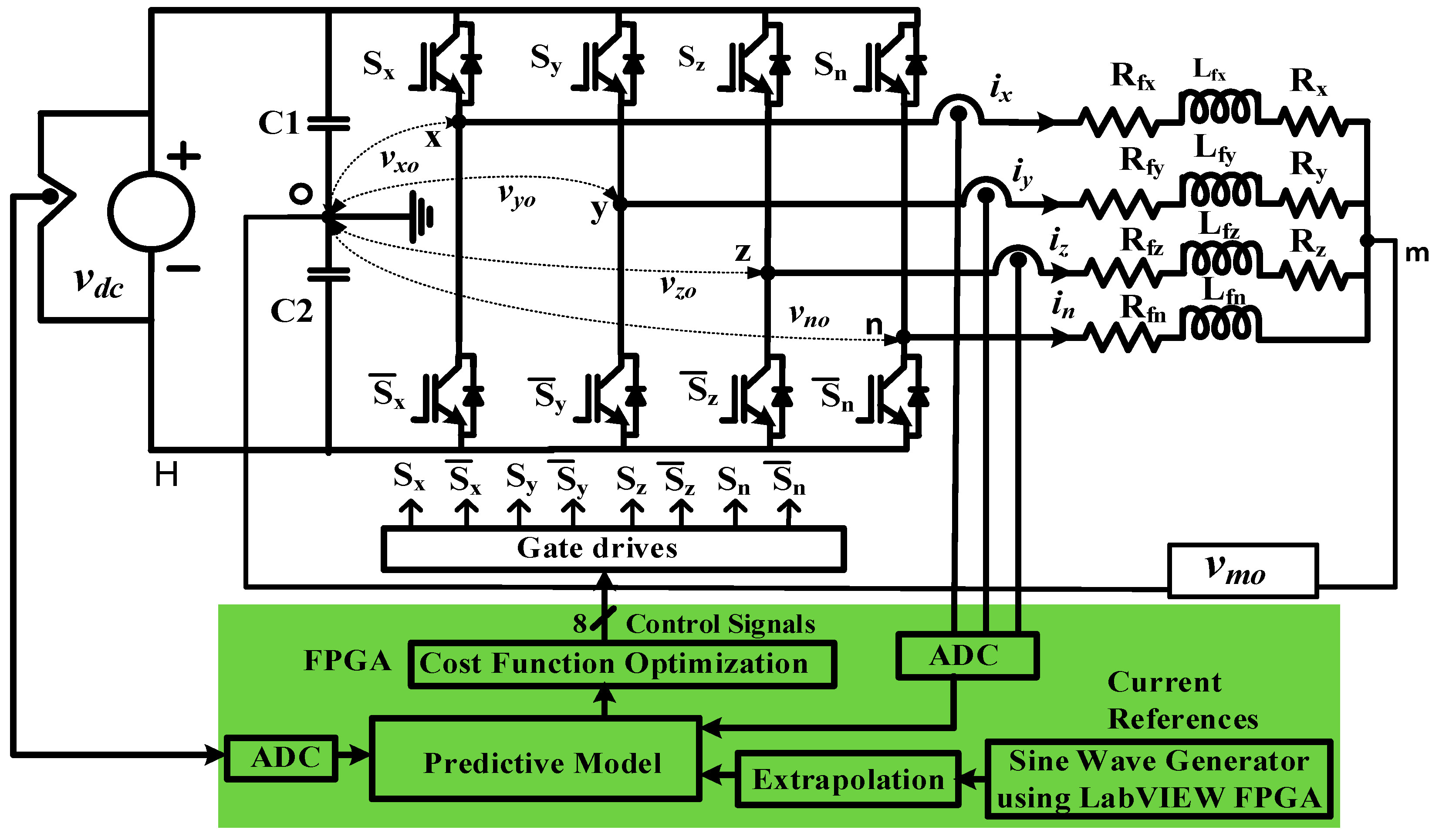

A three-phase four-leg inverter topology with the output resistive-inductive (R-L) filter is shown in

Figure 1. The neutral leg in the inverter topology is used to control the zero-sequence current. The neutral inductor is introduced in the fourth leg to attenuate the switching current ripple to be the same as the other legs. Besides, the neutral inductor limits the fault current during short circuit or unbalanced loading conditions [

15,

33]. Therefore, neutral inductance

is connected at the neutral leg in the practical applications [

34,

35].

The paired insulated-gate bipolar transistor (IGBT) switches in each of the four legs turn on and off in a complementary mode. If the upper switch of one leg is turned on, the lower one is turned off, and vice versa. The CMV is the potential difference between the midpoint of the DC-link capacitors and the load-neutral point (

vmo), as shown in

Figure 1. The CMV can be expressed in terms of the voltage on each leg, as shown in [

36]:

where

,

, and

are the voltages between the terminal and the midpoint of the DC-link. Based on the switching states, the phase voltages can have either voltages level

or

. Therefore, depending on the 16 switching states of the three-phase four-leg inverter, the CMV can have the values

.

According to Kirchhoff’s voltage law, the inverter’s output voltages can be written as follows:

where:

where,

v is the load voltage vector,

i is the load vector current,

is the filter resistance,

R is the load resistance,

is the filter inductance, and

is the voltage between the load-neutral and the DC-link negative point (H).

The voltages of each leg from the DC-link negative point (H) can be written as:

where

is the DC-link voltage, and

is the switching state of leg

j. The derivative from Equation (2) can be written in continuous form in terms of the load current vector, as shown in Equation (4):

The load-neutral voltage (

) can be expressed from Equations (3) and (4) as:

with

.

The system state space representation from Equation (2) is as follows, as seen in [

26]:

with

and

, where

x is the state variable vector,

u is the input variable vector, and

y is the output variable vector. Matrix

A,

B, and

C are as follows:

3. Model Predictive Control Method of Three-Phase Four-Leg Inverter

In order to implement the FCS-MPC algorithm on a microprocessor-based hardware, the discrete model has to be used in the analysis of the FCS-MPC algorithm. In the digital implementation, a discrete time model is used to predict the future current’s value at a sampling interval (

k). The inverter output current

i at

kth and (

k + 1)th instant with sampling time

can be calculated by using the solution of Equation (6) at the initial and final time as follows:

can be obtained by solving Equations (7) and (8) as below:

Then, Equation (10) is obtained by changing the variable of integration in Equation (9):

The output current can be obtained at (

k + 1)th from Equation (10) as:

where:

The identity matrix , the inverse of matrix A, and matrices G and Q are calculated offline in MATLAB (R2014a, MathWorks, Natick, MA, USA). The load current and DC-link voltage are required to predict the output current.

Each predicted future current is compared with its respective current reference in order to select the optimal switching state by using the cost function according to the following equation:

The Sinusoidal current references are obtained by Sine Wave Generator using LabVIEW field programmable gate array (FPGA) at

kth instant. Then, the required extrapolation can be achieved by using the fourth-order Lagrange extrapolation method [

20].

When the sampling period is very small (

< 20 μs), no extrapolation is required. In that case,

. The fourth leg has to change the switching state according to the switching state changes of three phases in order to control the zero-sequence current. Hence, the changing rate of the switching state in the fourth leg is higher, and it operates at a higher switching frequency as compared with the average switching frequency. Therefore, the switching loss of the fourth leg is higher. In order to compensate for the losses caused by the neutral-leg switching frequency, its constrain has been included in the cost function as follows:

where

is the weighting factor. The guidelines of weighting factor selection have been given in [

37]. Equation (14) must be achieved in order to improve the performance in reference current tracking and reduce the switching losses. Hence,

is important in order to empirically achieve the improvement in performance. The number of switching in the fourth leg can be achieved as follows [

38]:

where

is the predicted neutral leg gate signal, and

is the optimal gate signal in the previous sample,

k. The objective of Equation (15) is to force the predicted switching signal to remain at the same signal as the previous state. Then, the overall cost function can be expressed as follows:

The objective of this cost function is to optimize the error close towards zero.

4. Near State Vector Selection-Based Model Predictive Control

The lines to neutral voltages for all of the 16 switching vectors of a three-phase four-leg inverter are shown in

Table 1. The lines to neutral voltages are transformed from

abc into

αβγ coordinates by using Equation (17). The results of the transformation are shown in

Table 2.

In the three-dimensional coordinate system of a three-phase four-leg inverter, there are six prisms to represent the switching voltage vectors. These prisms can be divided into six sectors (from I to VI) such that each sector is combined with half of the two adjacent prisms, as shown in

Figure 2a. The projection of the reference vector on the

αβ coordinate is used to determine the sector of the reference vector. There are six active vectors and two zeros vectors in each sector.

In order to reduce the CMV and utilize high DC-link voltage, six active switching vectors are selected to synthesize the reference in each sector. As shown in

Figure 2b, all of the sectors occupied 60° on the

αβ plane, with sector I in the range of 330° to 30°, and followed by the other sectors. In order to minimize the current and harmonic content, near state switching vectors should be selected that are adjacent to the reference vector. It is seen that two prisms in each sector consist of two tetrahedrons, and there are eight switching vectors adjacent to the reference vector, four of which are selected based on the minimization of CMV and switching loss. The position of the reference vector is determined by the NSV-MPC at every sampling period. The active voltage vectors surrounding the determined reference vector are selected based on the position of the reference voltage vector. The optimal vector candidate is included among the selected voltage vectors. As shown in

Figure 2c, if the reference switching vector is in sector I, four non-zero switching vectors are required to synthesize the reference vector. Therefore, two sets (Set-

a and Set-

b) of four switching vectors are selected in each sector. It is clear that two switching vectors (

PNNP and

PNNN) are chosen in both sets. Hence, there are six different switching vectors in one sector.

The voltage vector closest to the reference voltage vector is selected by evaluating the six active vectors through the predictive model mentioned in

Section 3. The optimal voltage vector is selected from the six active vectors by using the cost function in Equation (15).

The model predictive control technique based on the near state voltage vector can be employed to find the closest voltage vector, which reduces the error between the desired and reference currents. From the predefined sectors, the proposed control method predicts the reference vector in each sampling time. Six active vectors are selected from the 14 active vectors that surround the reference vector based on the near state vectors listed in

Table 3. This ensures that the CMV is confined within ±

, and at the same time reduces the computational burden, as only six active vectors are used, instead of 14 vectors. However, this increases the ripple content marginally in the load current as conventional MPC. In order to overcome the problem, one zero vector—either

PPPP or

NNNN—can be used together with the six active vectors at each control cycle, and this causes the CMV to vary between

+ and −

or −

and +

. Therefore, seven voltage vectors are selected to determine the voltage vector that is closest to the reference vector in the proposed NSV-MPC. In both cases, the computational burden is also reduced due to the reduction of switching vectors from 16 to six (considering only active vectors), and seven (including one zero vector), as shown

Figure 3. As a result, NSV-MPC demonstrates the better performance with reduced computational burden.

A step-by-step implementation procedure for NSV-MPC is summarized below:

- Step 1.

Measure the load currents i(k) and calculate the reference currents i*(k + 1) by using Equation (13)

- Step 2.

Identify the sector on the αβ plane in the αβγ coordinate and the corresponding voltage vectors at every sampling period.

- Step 3.

Predict the future voltage vector for all of the possible switching states from the identified sector from

Table 3.

- Step 4.

Predict the load currents i(k + 1) of all of the possible switching states from the identified sector at the next sampling time by using Equation (11).

- Step 5.

Evaluate the cost function g(k + 1) by using Equation (16).

- Step 6.

7Select the switching state that optimizes the cost function.

- Step 7.

7Apply the selected switching action to fire the inverter switches.