A Quadrature Single Side-Band Mixer with Passive Negative Resistance in Software-Defined Frequency Synthesizer

Abstract

:1. Introduction

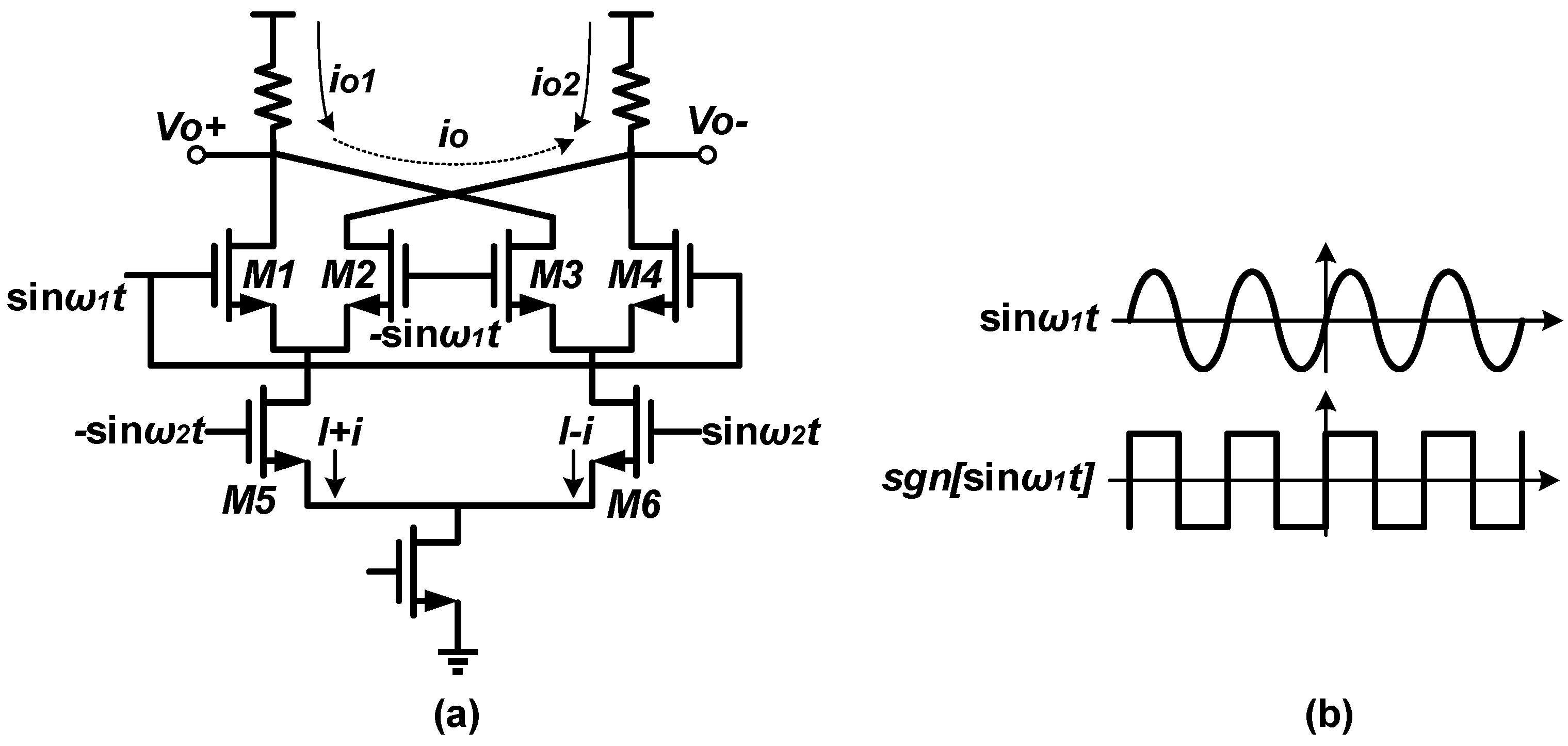

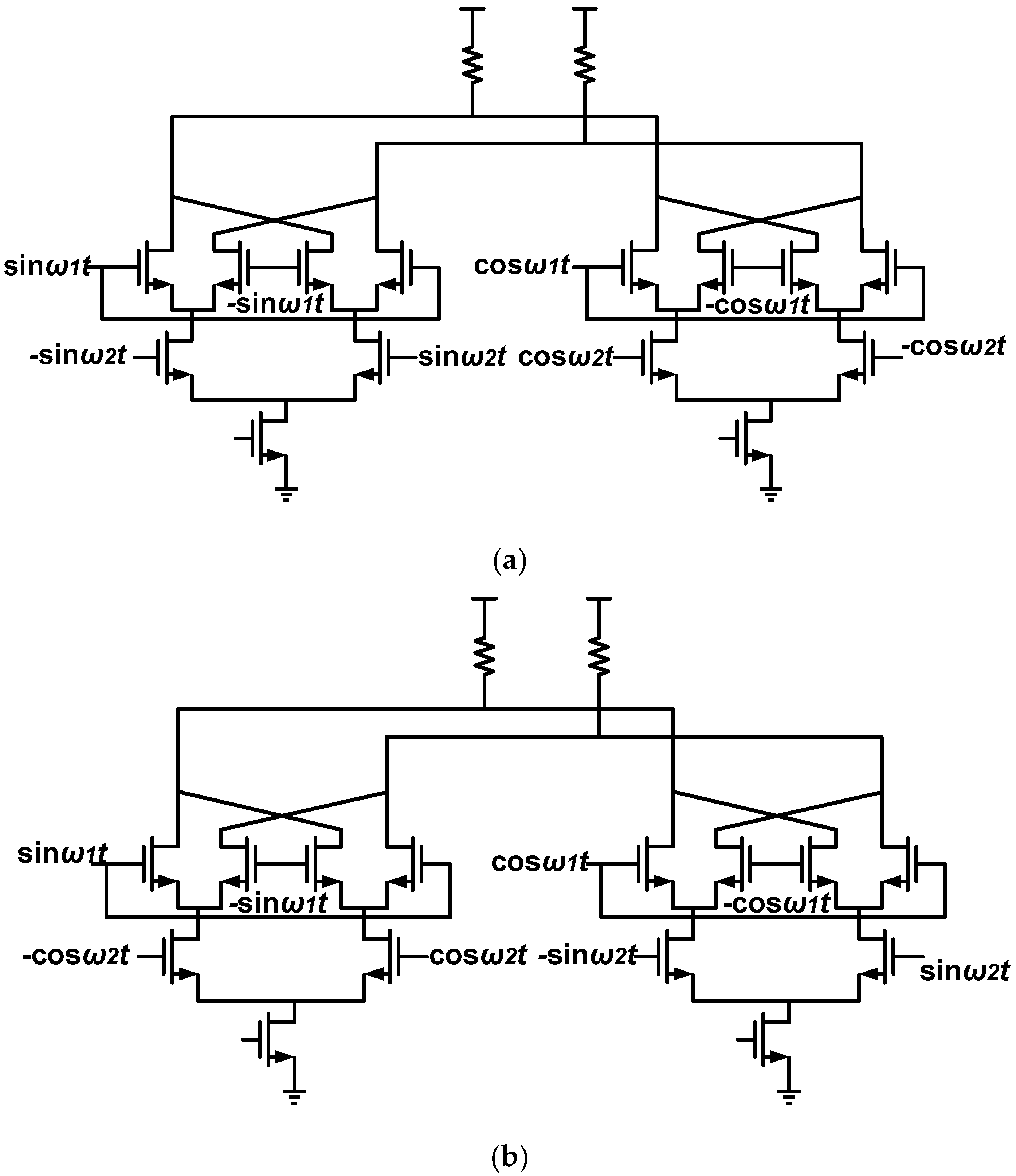

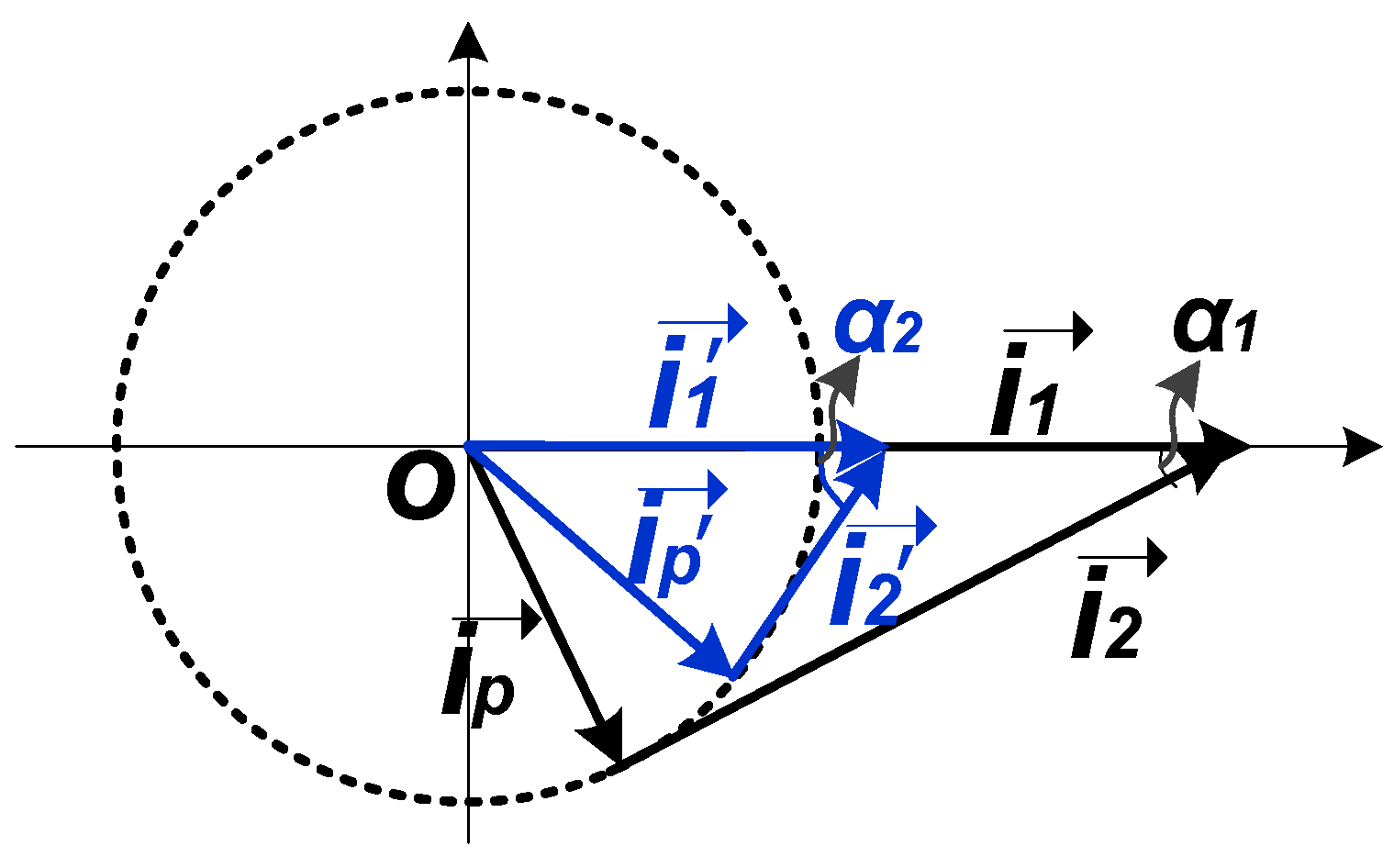

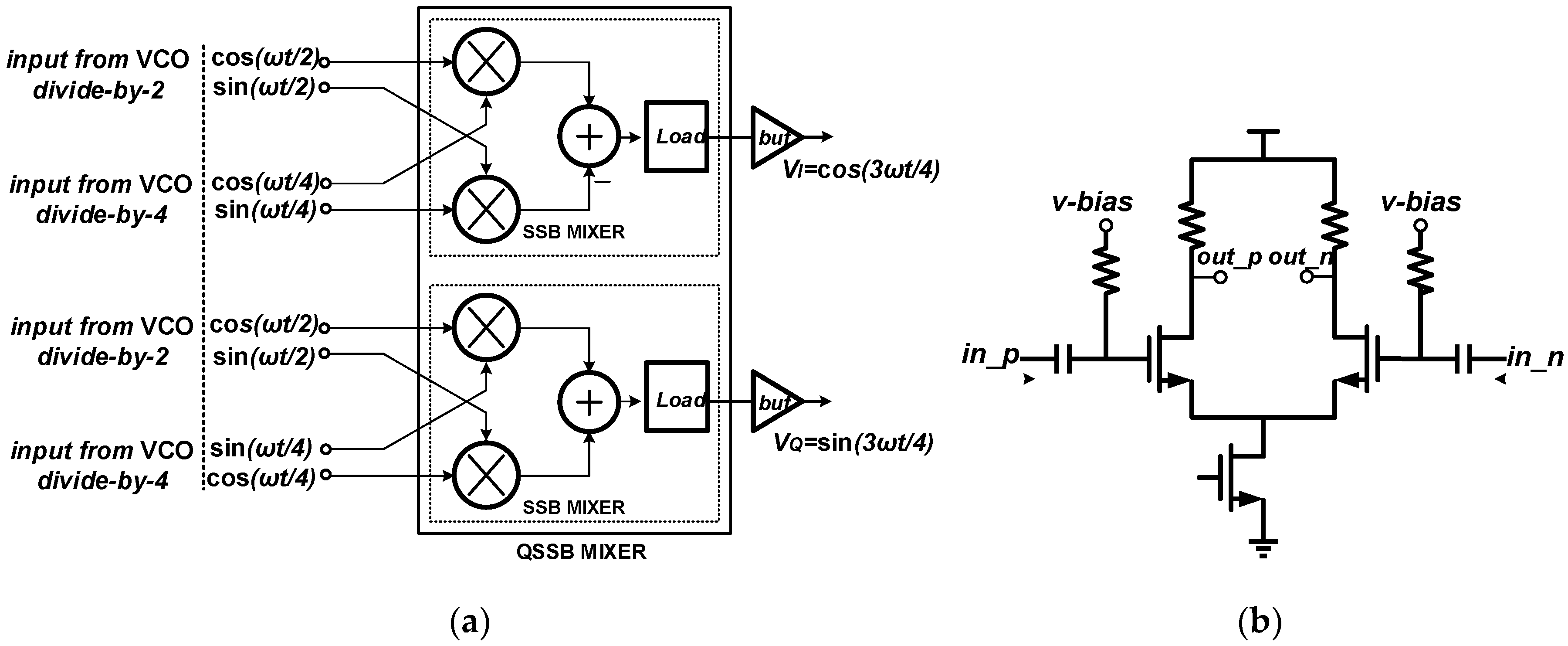

2. Quadrature Single Side-Band Mixer

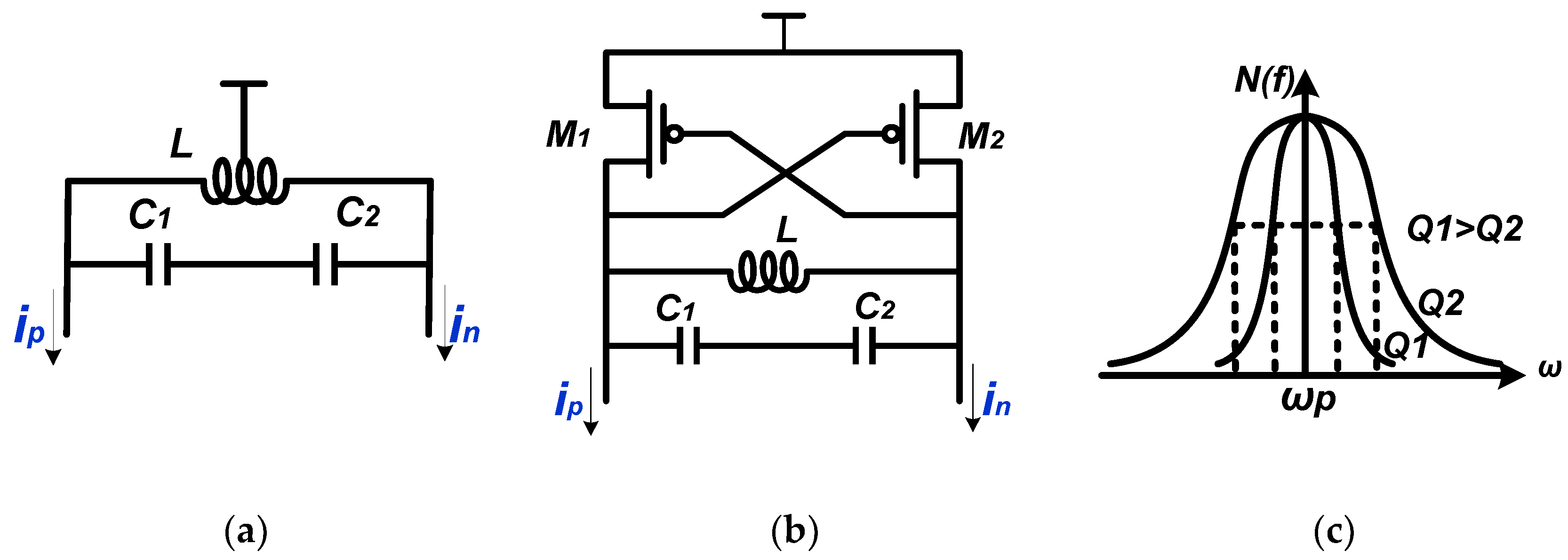

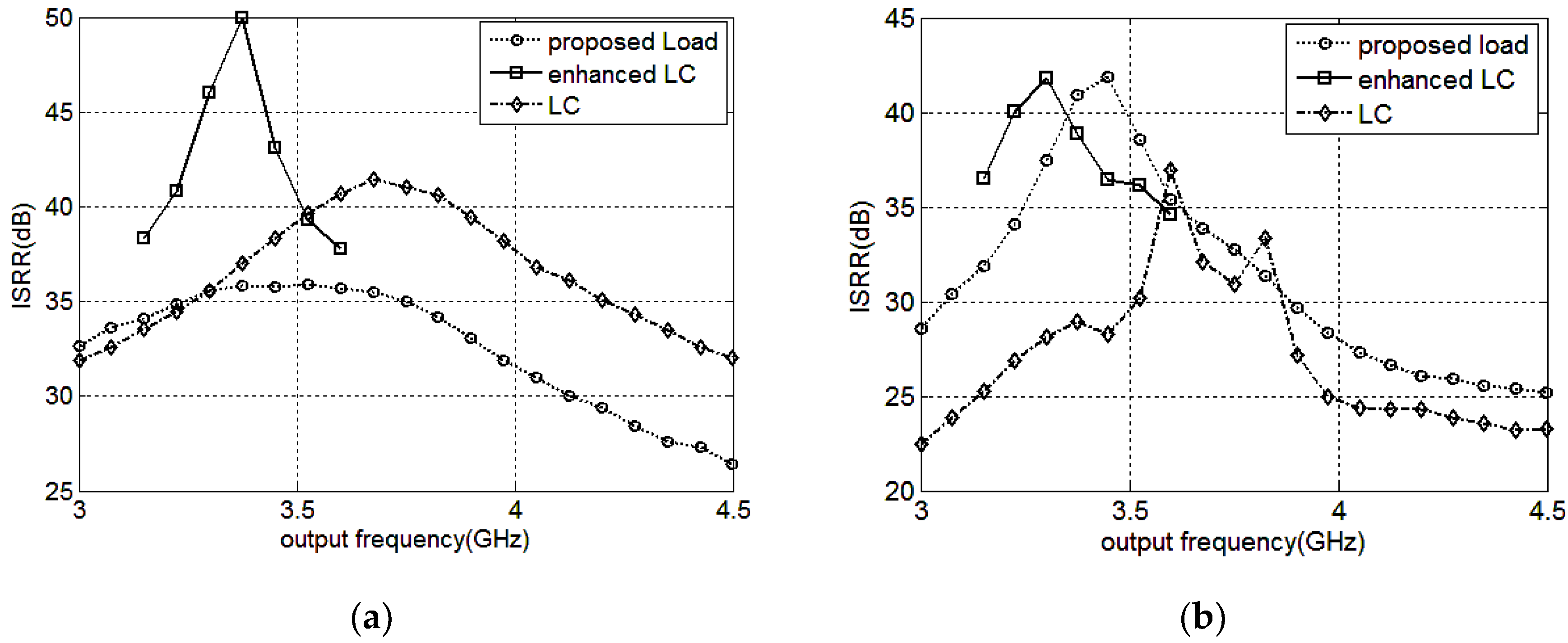

3. Proposed PNR and QSSB Mixer

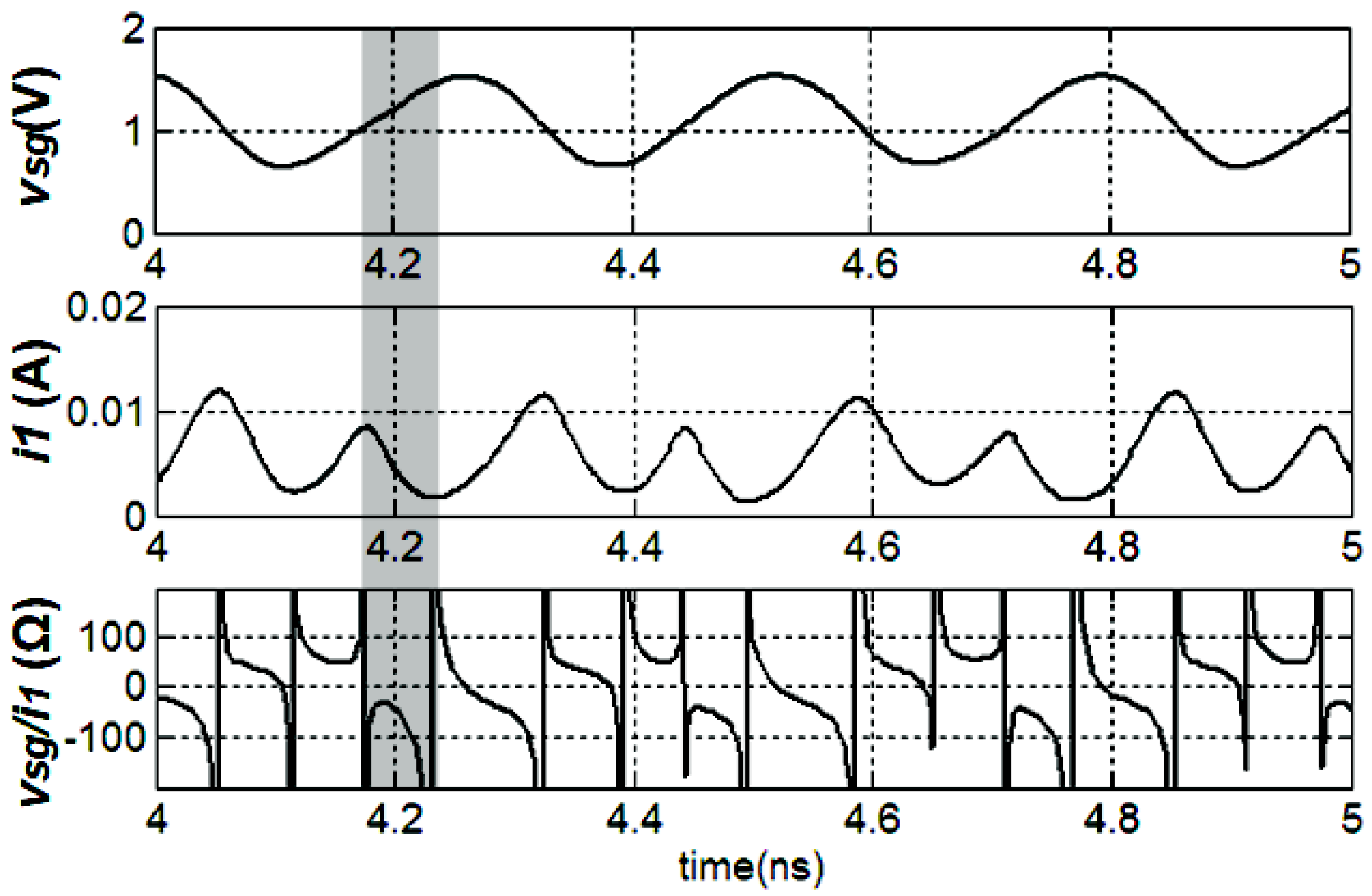

3.1. The Proposed PNR

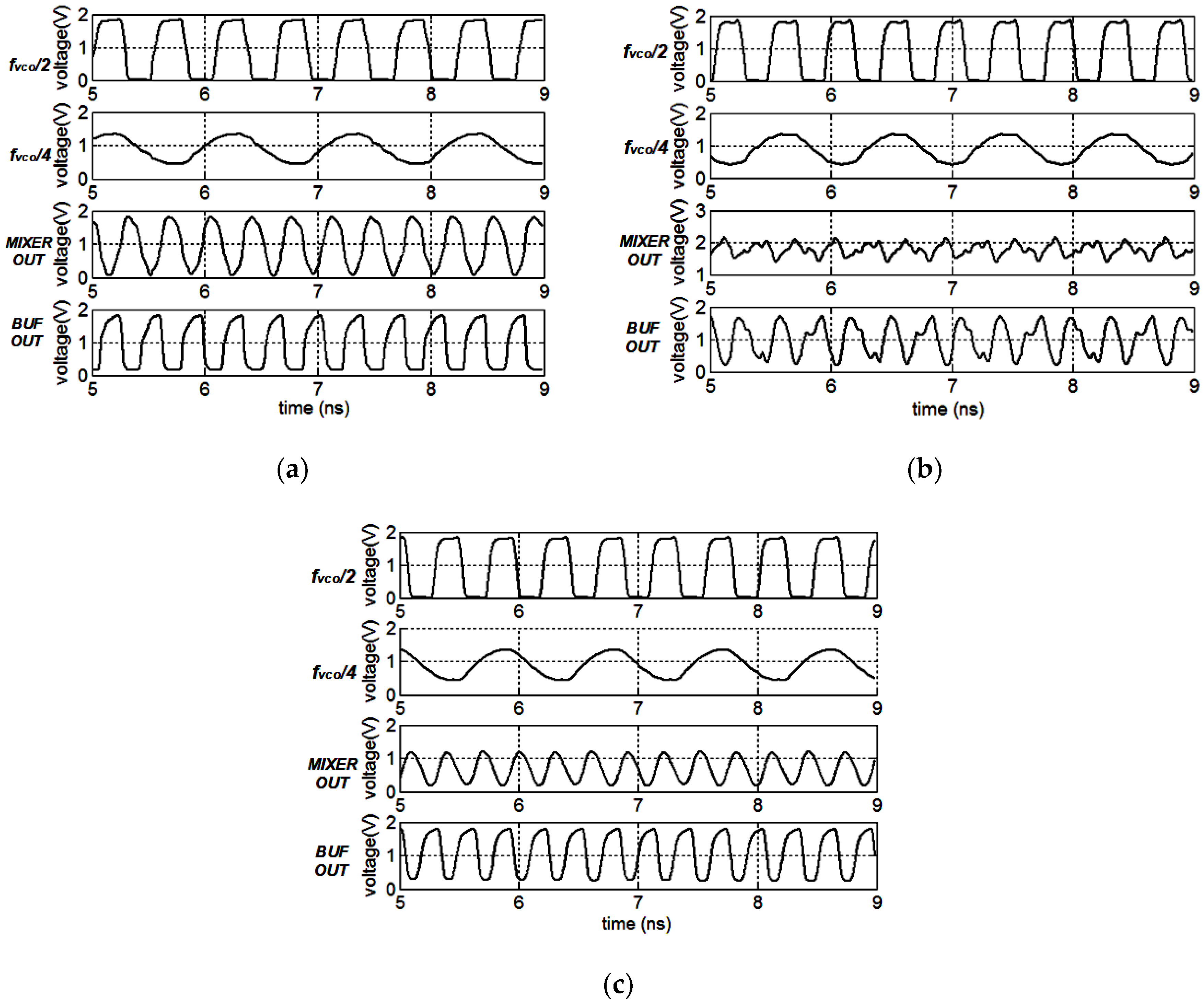

3.2. The Proposed QSSB Mixer

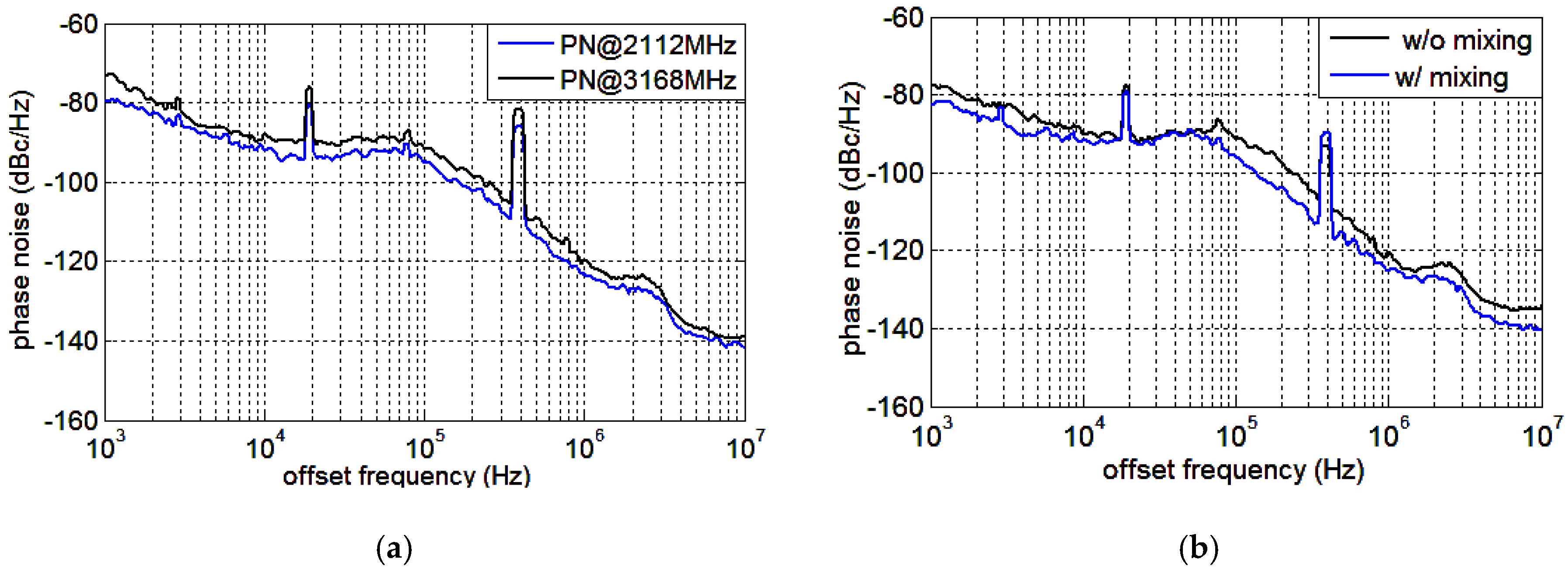

4. Measurement Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Giannini, V.; Nuzzo, P.; Soens, C.; Vengattaramane, K.; Ryckaert, J.; Goffioul, M.; Debaillie, B.; Borremans, J.; Van Driessche, J.; Craninckx, J.; et al. A 2-mm2 0.1–5 GHz Software-Defined Radio Receiver in 45-nm Digital CMOS. IEEE J. Solid-State Circuits 2009, 44, 3486–3498. [Google Scholar] [CrossRef]

- Deng, W.; Hara, S.; Musa, A.; Okada, K.; Matsuzawa, A. A Compact and Low-Power Fractionally Injection-Locked Quadrature Frequency Synthesizer Using a Self-Synchronized Gating Injection Technique for Software-De fined Radios. IEEE J. Solid-State Circuits 2014, 49, 1984–1994. [Google Scholar] [CrossRef]

- Yu, S.; Baeyens, Y.; Weiner, J.; Koc, U.; Rambaud, M.; Liao, F.; Chen, Y.; Kinget, P.R. A Single-Chip 125-MHz to 32-GHz Signal Source in 0.18-um SiGeBi CMOS. IEEE J. Solid-State Circuits 2011, 46, 598–614. [Google Scholar] [CrossRef]

- Osmany, S.A.; Herzel, F.; Scheytt, J.C. An Integrated 0.6–4.6 GHz, 5–7 GHz, 10–14 GHz and 20–28 GHz Frequency Synthesizer for Software-Defined Radio Applications. IEEE J. Solid-State Circuits 2010, 45, 1657–1688. [Google Scholar] [CrossRef]

- Rong, S.; Yin, J.; Luong, H.C. A 0.05- to 10-GHz, 19- to 22-GHz, and 38- to 44-GHz Frequency Synthesizer for Software-Defined Radios in 0.13-μm CMOS Process. IEEE Trans. Circuits Syst. II 2016, 63, 109–113. [Google Scholar] [CrossRef]

- Zhou, J.; Li, W.; Huang, D.; Lian, C.; Li, N.; Ren, J.; Chen, J. A 0.4–6-GHz Frequency Synthesizer Using Dual-Mode VCO for Software-Defined Radio. IEEE Trans. Microw. Theory Technol. 2013, 61, 848–859. [Google Scholar] [CrossRef]

- Lu, T.; Chen, W. A 3–10 GHz, 14 Bands CMOS Frequency Synthesizer with Spurs Reduction for MB-OFDM UWB System. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 20, 948–958. [Google Scholar] [CrossRef]

- Lee, J. A 3-to-8-GHz Fast-Hopping Frequency Synthesizer in 0.18-um CMOS Technology. IEEE J. Solid-State Circuits 2006, 41, 566–573. [Google Scholar] [CrossRef]

- Liang, C.; Liu, S.; Chen, Y.; Yang, T.; Ma, G. A 14-band Frequency Synthesizer for MB-OFDM UWB Application. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 6–9 February 2006; pp. 428–437. [Google Scholar]

- Kim, N.-S.; Rabaey, J.M. A 3.1–10.6-GHz 57-Bands CMOS Frequency Synthesizer for UWB-Based Cognitive Radios. IEEE Trans. Microw. Theory Tech. 2018, 66, 4134–4146. [Google Scholar] [CrossRef]

- Shanthi, T.; Krishnamurthi, V. FPGA Based Frequency Synthesizer for 14-Band MB-OFDM UWB Transceivers. In Proceedings of the International Conference on Emerging Trends in Engineering, Technology and Science (ICETETS), Pudukkottai, India, 24–26 February 2016; pp. 1–4. [Google Scholar]

- Ismaili, Z.; Ajib, W.; Gagnon, F.; Nabki, F. A 0.13 μm CMOS Fully Integrated 0.1∼12 GHz Frequency Synthesizer for Avionic SDR Applications. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Ko, J.; Gharpurey, R. A Pulsed UWB Transceiver in 65 nm CMOS with Four-Element Beam forming f or 1 Gbps Meter-Range WPAN Applications. IEEE J. Solid-State Circuits 2016, 51, 1177–1187. [Google Scholar] [CrossRef]

- Peng, Y.; Zhang, L.; Fu, J.; Wang, Y. Analysis and Design of a Broadband SiGe HBT Image-Reject Mixer Integrating Quadrature Signal Generator. IEEE Trans. Microw. Theory Tech. 2016, 64, 688–698. [Google Scholar] [CrossRef]

- Lee, S.; Lai, C.; Chiou, H. A Filter-based, SSB Mixer for UWB Application. In Proceedings of the IEEE International Workshop on Radio-Frequency Integration Technology (RFIT), Singapore, 30 November–2 December 2005; pp. 109–112. [Google Scholar]

- Li, W.; Cheng, K.M. A CMOS Transformer-Based Current Reused SSBM and QVCO for UWB Application. IEEE Trans. Microw. Theory Tech. 2013, 61, 2395–2401. [Google Scholar] [CrossRef]

- Li, W.; Cheng, K.K.M. A Single-PLL UWB Frequency Synthesizer Using Current Reusing SSB Mixer. In Proceedings of the IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 16 August 2010; pp. 1–4. [Google Scholar]

- Wang, C.; Li, W.; Wang, C.K.; Shih, H.; Yang, T. A 3–10 GHz Full-Band Single VCO Agile Switching Frequency Generator for MB-OFDM UWB. In Proceedings of the IEEE Asian Solid-State Circuits Conference (ASSCC), Jeju, Korea, 12–14 November 2007; pp. 75–78. [Google Scholar]

- Kim, J.; Jung, S.; Jung, J.; Sung, S.-K.; Lee, K.Y.; Nam, C.; Park, B.-H.; Choi, S. A Design of the Frequency Synthesizer for UWB Application in 0.13 μm RF CMOS process. In Proceedings of the IEEE International Workshop on Radio-Frequency Integration Technology (RFIT), Singapore, 9–11 December 2007; pp. 318–321. [Google Scholar]

- Zheng, H.; Luong, H.C. A 1.5 V 3.1 GHz–8 GHz CMOS Synthesizer for 9-Band MB-OFDM UWB Transceivers. IEEE J. Solid-State Circuits 2007, 42, 1250–1260. [Google Scholar] [CrossRef]

- Kuo, Y.F.; Weng, R.M. Regenerative frequency divider for 14 sub-band UWB applications. Electron. Lett. 2008, 44, 111–112. [Google Scholar] [CrossRef]

- Yang, Y.; Weng, S.L. 9.8 mW CMOS frequency synthesizer for mode-I UWB transceivers. Electron. Lett. 2010, 46, 179–180. [Google Scholar] [CrossRef]

- Lo, Y.; Kiang, J. A Single-Sideband Mixer with Band Selection through an Output Switching Quad. In Proceedings of the European Microwave Conference (EuMC), Paris, France, 28–30 September 2010; pp. 1130–1133. [Google Scholar]

- Wang, M.; Saavedra, C.E. Fully Monolithic Single-Sideband Upconverter Mixer with Sideband Selection. In Proceedings of the IEEE MTT-S International Microwave Symposium, Baltimore, MD, USA, 5–10 June 2011; pp. 1–4. [Google Scholar]

| Operating Distance (m) | Transmit Power (dBm) | Data Rate (bps) | Frequency Band (GHz) | |

|---|---|---|---|---|

| ZigBee | 10–100 | 0–3 | 20–250 k | 0.780/0.868 /0.915/2.4 |

| Wireless HART | 10–100 | -- | <250 k | 2.4 |

| ISA100.11a | 10–100 | <26 | 250 k | 2.4 |

| Bluetooth | 1–100 | 0–20 | 1–3 M | 2.4 |

| GSM | <35 k | 30–33 | 13 k | 0.85/0.95 /1.8–1.9 |

| WiBree | 1–10 | −6 | 1 M | 2.4 |

| RFID | <5 | 0 | <0.4 M | 0.01356/ 0.86–0.96/2.4 |

| Load Type | Operating Range/GHz | ISRR/dB | Process | |

|---|---|---|---|---|

| [6] | LC | 5–6 | 42 | 0.13 CMOS |

| [7] | Q-enhanced LC | 3.4/3.9/4.4/5/5.5/6.1/6.6/7.1/7.6/.2/.7/9.2/9.7/10.3 | 33 | 65 nm CMOS |

| [8] | LC | 3.4/3.9/4.4/5/5.5/6.1/6.6/7.1/7.6 | 37 | 0.13 CMOS |

| [15] | Q-enhanced LC | 3.4/4.4 | 30 | 0.18 CMOS |

| [16] | Q-enhanced LC | 3.4/4.4 | 43 | 0.18 CMOS |

| [17] | LC | 3.4/3.9/4.4 | 31 | 0.18 CMOS |

| [18] | LC | 3.4/3.9/4.4/5/5.5/6.1/6.6/7.1/7.6/.2/.7/9.2/9.7/10.3 | 35 | 0.13 CMOS |

| [19] | LC | 3.4/3.9/4.4 | 18–32 | 0.13 CMOS |

| [20] | LC | 3.4/3.9/4.4/5/5.5/6.1/6.6/7.1/7.6 | 22–37 | 0.18 CMOS |

| [21] | LC | 3.4/3.9/4.4/5/5.5/6.1/6.6/7.1/7.6/.2/.7/9.2/9.7/10.3 | 29 | 0.18 CMOS |

| [24] | LC | 5 | 30 | 0.13 CMOS |

| This work | PNR with LC | 2.5–3 | 40–57 | 0.18 CMOS |

| 2.3–3.2 | 30–57 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, D.; Hu, A.; Zhang, K. A Quadrature Single Side-Band Mixer with Passive Negative Resistance in Software-Defined Frequency Synthesizer. Sensors 2018, 18, 3455. https://doi.org/10.3390/s18103455

Liu D, Hu A, Zhang K. A Quadrature Single Side-Band Mixer with Passive Negative Resistance in Software-Defined Frequency Synthesizer. Sensors. 2018; 18(10):3455. https://doi.org/10.3390/s18103455

Chicago/Turabian StyleLiu, Dongsheng, Ang Hu, and Kefeng Zhang. 2018. "A Quadrature Single Side-Band Mixer with Passive Negative Resistance in Software-Defined Frequency Synthesizer" Sensors 18, no. 10: 3455. https://doi.org/10.3390/s18103455

APA StyleLiu, D., Hu, A., & Zhang, K. (2018). A Quadrature Single Side-Band Mixer with Passive Negative Resistance in Software-Defined Frequency Synthesizer. Sensors, 18(10), 3455. https://doi.org/10.3390/s18103455