Abstract

This paper presents an overview of the read noise in CMOS image sensors (CISs) based on four-transistors (4T) pixels, column-level amplification and correlated multiple sampling. Starting from the input-referred noise analytical formula, process level optimizations, device choices and circuit techniques at the pixel and column level of the readout chain are derived and discussed. The noise reduction techniques that can be implemented at the column and pixel level are verified by transient noise simulations, measurement and results from recently-published low noise CIS. We show how recently-reported process refinement, leading to the reduction of the sense node capacitance, can be combined with an optimal in-pixel source follower design to reach a sub- read noise at room temperature. This paper also discusses the impact of technology scaling on the CIS read noise. It shows how designers can take advantage of scaling and how the Metal-Oxide-Semiconductor (MOS) transistor gate leakage tunneling current appears as a challenging limitation. For this purpose, both simulation results of the gate leakage current and noise data reported from different foundries and technology nodes are used.

1. Introduction

The idea of an image sensor with photon counting capability is becoming a subject of interest for new applications and imaging paradigms [1,2,3]. Such a device must have an input-referred read noise negligible compared to a single electron. Among the state-of-the-art imaging devices, single photon detectors may appear to be the best candidate for such an application [4]. Historically, micro-electronics could not provide readout chains with noise levels as low as deep sub-electron. Hence, the solution was to introduce a gain at the level of the photon-electron conversion. In photomultipliers tubes (PMTs) and single photon avalanche photodiodes (SPADs), the electron generated by the incident photon is accelerated and multiplied to a number of electrons from a few hundred in PMTs to millions in SPADs. Such a signal level can be easily detected and quantized into two logic levels, since the number of incident photons during the period of detection is assumed to be much less than one. However, these devices present the following disadvantages [5]. First, they are limited to the case of single photon detection. In other words, the arrival of one photon and multiple photons are not distinguished. Second, these devices suffer from a dead time and after pulse following each photon detection, blinding the device for a certain time. The third limitation is related to the low resolution and fill factors of focal plane arrays using such devices. Additionally, they use high voltages, which are not compliant with standard CMOS image sensor (CIS) processes.

During the last decade, CISs have seen their performance increasing remarkably in terms of dynamic range, speed, resolution and power consumption. With a lower cost and better on-chip integration, CISs replaced progressively the charge coupled devices (CCDs) in many applications and enlarged the market of electronic imaging devices. In terms of sensitivity, the quantum efficiency has been improved to reach levels as high as [3]. The fill factors have been constantly improved. The dark current in the pinned photodiodes (PPDs) has been reduced to levels making the process of electron-hole pair generation noiseless for integration times around tens of ms. The read noise has also been dramatically reduced to reach deep sub-electron levels [6,7,8]. Hence, CIS technologies are advanced enough to envisage the photon counting possibility.

Besides the quantum efficiency, this paper discusses the possibility of performing photon counting, with standard CIS, essentially from the read noise perspective. Starting from the analytical expressions of the input-referred noise, the noise reduction mechanisms at the circuit, device and process level are discussed and verified with simulation, measurements and data reported in recent works. The impact of the combination of different techniques is also analyzed, and the noise levels that can be reached with state-of-the-art technology in standard processes are quantified. This paper also shows how the technology downscaling can be used to reduce the read noise and how the gate leakage current could limit this advantage.

2. CMOS Image Sensors and Photon Counting Requirements

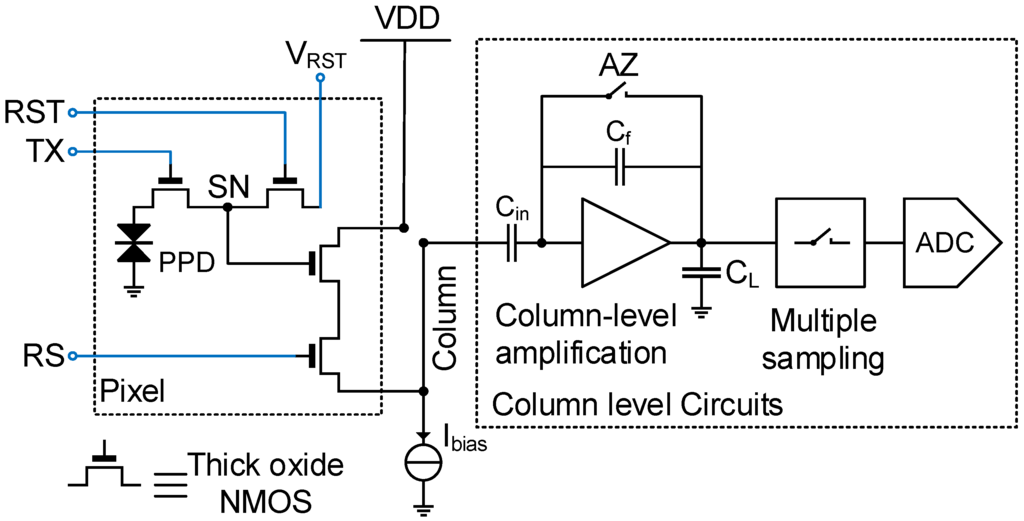

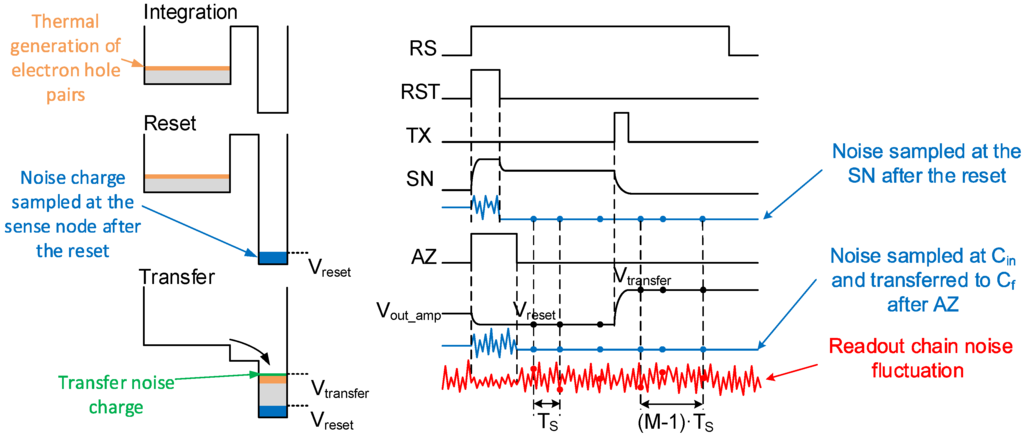

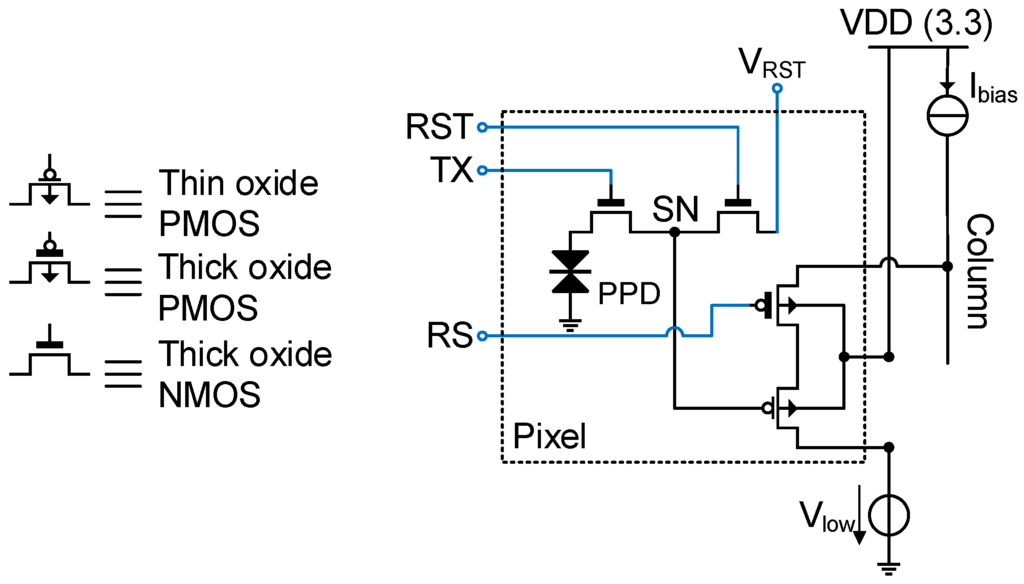

Figure 1 shows the schematic of a conventional low noise CIS readout chain. The corresponding timing diagram is shown in Figure 2. It also shows the potential profile across the PPD, the transfer gate (TX) and the sense node (SN) during the three phases of operation: the integration, the reset and the transfer phases. During the integration time, the PPD accumulates the electrons generated by the incident photons. During the readout, the pixel is connected to the column through the row selection switch (RS), then the reset switch (RST) is closed in order to set the SN voltage higher than the pinning voltage of the PPD. The voltage level at the SN after the reset is read with the in-pixel source follower (SF) and sampled at the end of the readout chain. The potential barrier between the PPD and the SN is controlled by the transfer gate (TX). When the barrier is lowered, the charges accumulated in the PPD are transferred to the SN. The SN voltage level after the transfer is sampled at the output of the readout chain. The reset and transfer samples are then differentiated. This operation is called correlated double sampling (CDS) [9].

Figure 1.

Schematic of a conventional low noise CMOS image sensor (CIS) readout chain. RST, reset switch; TX, transfer gate; RS, row selection switch; SN, sense node; PPD, pinned photodiode; AZ, auto-zero; VDD, supply voltage .

Figure 2.

Timing diagram of the conventional CIS readout chain of Figure 1 with noise mechanisms affecting the signal at the PPD and the readout chain levels.

Figure 2 depicts also the different noise sources affecting the signal in the CIS apart from the photon shot noise. During the integration, the charge originating from the thermal generation of electron-hole pairs in the depleted region of the PPD (the dark current) can corrupt the signal. In state-of-the-art CIS, the dark current in PPDs has been reduced to a few es. Hence, for exposure times below hundreds of ms, the dark current can be neglected.

The reset of the SN leaves a noise charge held at the SN. This noise is as high as several electrons in the case of a SN capacitance of a few fF. However, for 4T pixels, it is canceled thanks to the CDS readout scheme, as depicted in the timing diagram of Figure 2.

The charge transfer from the PPD to the SN can be affected by the noise related to the charge deficit due to incomplete transfer and lag [10,11]. Unlike the sampled reset kTC noise, this noise is not canceled by the CDS. The charge transfer noise has been extensively studied for CCDs [12,13] because an efficient charge transfer is crucial in such devices. In state-of-the-art CIS with 4T pixels, values of the lag as low as have been reported. Thus, the lag can be neglected compared to the read noise in the low light context. The transient noise related to the lag is believed to behave as a shot noise [11], similarly to buried channel CCDs [13]. However, with a lag below , this noise can be neglected in low light conditions. It is also believed that trapping mechanisms in the silicon oxide interface under the transfer gate also contribute to the transfer non-idealities [10,14,15,16], giving rise to a Random Telegraph Signal (RTS)-like noise.

Finally, the readout of the SN reset and transfer voltages is affected by random fluctuations due to the readout chain noise; starting with the in-pixel SF and noise coupling of the TX and RST lines with the SN, the power supply noise and ending with the column-level circuitry and analog-to-digital converters (ADCs). The column-level amplification is introduced in order to minimize the contribution of the next circuit blocks to the input-referred total noise, e.g., buffers, sample-and-holds and ADC. The column-level amplifier also limits the bandwidth in order to minimize the thermal noise [8]. A switched capacitor amplifier is usually used. An auto-zero (AZ) is performed in order to reset its feedback capacitor and to reduce its offset and noise [9]. When the AZ switch is opened, the noise is sampled at the integration capacitor and transferred to the output. This sampled noise is also canceled thanks to the CDS. Low noise CIS readout chains may also include correlated multiple sampling (CMS) that can be implemented with analog circuitry [17,18] or performed after the ADC [19]. CMS consists of averaging M samples after the reset and M other samples after the transfer with a sampling period , then calculating the difference between the two averages.

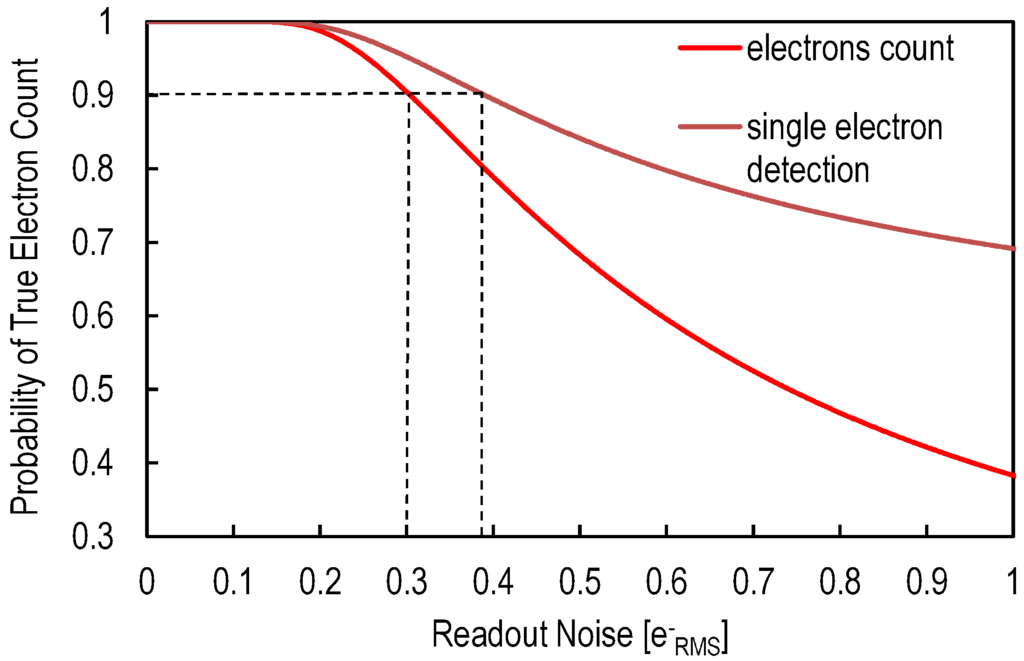

With a careful design, the readout noise originating from the pixel and column-level amplifier is the dominant noise source in CIS. Figure 3 shows the calculated probability of a true photo-electron count and a single photo-electron detection as a function of the input-referred readout chain noise by assuming a Gaussian distribution of noise and using the error function. Based on Figure 3, accuracy requires a read noise below for single photo-electron detection and for photo-electron count. Recently reported works are today closer than ever to these limits [7,8,20]. A detailed noise analysis of the readout noise is therefore necessary in order to determine the key design and process parameters that can be used for further noise reduction.

Figure 3.

Probability of a true photo-electron count and single photo-electron detection as a function of the input-referred readout noise.

3. Read Noise in CIS

In a conventional CIS readout chain, three readout noise sources can be distinguished: thermal noise, noise and leakage current shot noise. For each noise source, the variance at the output of the readout chain is first calculated and then referred to the input as a noise charge. Hence, the pixel conversion gain is a key parameter in the noise analysis. The pixel conversion gain can be calculated using a small-signal analysis of the pixel. It is crucial to take into account the effect of parasitic capacitances. Figure 4 presents a schematic of a 4T pixel section view showing all of the parasitic capacitances connected to the sense node. These include the overlap capacitances of the transfer and reset gates, and , respectively, the sense node junction capacitance, , and the parasitic capacitance related to the metal wires, . These capacitances are independent of the in-pixel SF. Their sum is defined as:

Figure 4.

Cross-section of a conventional 4T pixel showing the different parasitic elements contributing to the sense node capacitance.

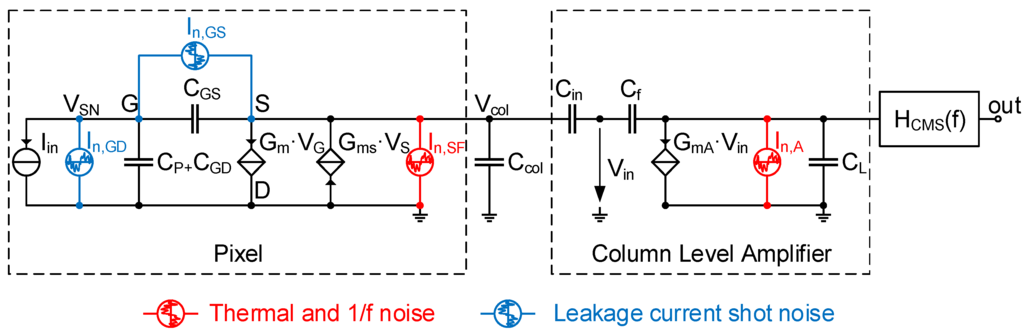

Figure 5 presents a simplified small-signal schematic of the CIS readout chain of Figure 1. This small-signal schematic is used to calculate the conversion gain together with the noise and signal transfer functions. Based on the detailed analytical calculation presented in [8], the conversion gain of a conventional CIS 4T pixel can be expressed as:

Figure 5.

Small-signal analysis of the CIS readout chain depicted in Figure 1 showing the different readout noise sources considered in the analysis.

Here, n is the slope factor of the in-pixel SF [21] defined as , where and are the SF gate and source transconductances, respectively. is the extrinsic capacitance per unit width of the in-pixel source follower transistor. It includes the overlap and fringing capacitances as depicted in Figure 4. is the SF oxide capacitance per unit area.

3.1. 1 Noise

Under the long-channel approximation, the gate-referred noise power spectral density (PSD) of a MOS transistor operating in the saturation region is commonly expressed as:

Here, W and L are the gate width and length; is the oxide capacitance per unit area; and is a noise process and bias-dependent parameter. This empirical model is easy to use for hand calculation and remains valid even for advanced CMOS technologies for adequate gate widths and lengths [22]. The parameter can be expressed as [21,23]:

where k is the Boltzmann constant, T is the absolute temperature, q is the electron charge, λ is the tunneling attenuation distance ( nm) [24], is the oxide trap density and is a bias-dependent parameter. It has been shown in [21] that is close to unity when the transistor is operating in the weak and moderate inversion regime.

Most analog circuit simulators use the Berkeley Short-channel Model (BSIM) to predict the noise behavior of circuits. It is important to establish a relationship between the parameters used by the simulator and the simple equation used for hand calculations in order to best exploit the noise calculation results. The oxide trap density is the key process-dependent parameter. In the BSIM model, it is referred to as the noise parameter A (noiA) [25].

It is well known that the noise PSD is inversely proportional to the gate area. In low noise CIS readout chains, the transistors located outside the pixels array can be designed with gate dimensions much larger than the in-pixel source follower transistor. In this case, the latter becomes the dominant noise source in the readout chain, and the other noise sources can be neglected. Based on the small-signal schematic of Figure 5 and the calculation detailed in [8], the input-referred noise can be expressed as:

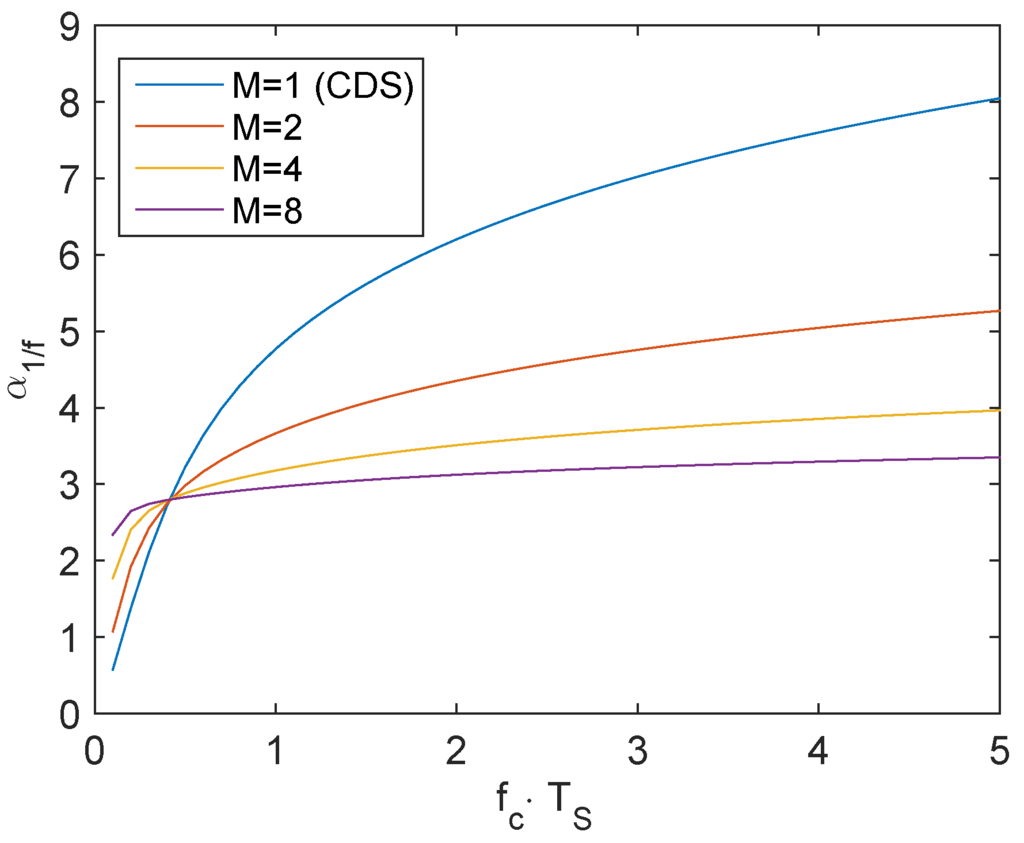

where is a unitless circuit design parameter reflecting the impact of the CMS noise reduction on the noise. Based on the detailed analytical calculation [26], it can be expressed as:

where is the cutoff frequency of the column-level amplifier, which is assumed to be lower than the SF stage bandwidth. is the sampling period of the correlated sampling. is calculated numerically and plotted as a function of in Figure 6. It shows that is weekly dependent on when M is higher than two. In this case, ranges between three and four.

Figure 6.

Numerical calculation of the parameter from Equation (6) as a function of the ratio between the cutoff frequency of the readout chain and the sampling frequency of the correlated sampling T for a simple CDS and CMS with different orders M.

3.2. Thermal Noise

The thermal noise of a MOS transistor operating in saturation is modeled by a drain current source that adds to the signal. The drain current noise PSD is commonly expressed as [21]:

where is the gate transconductance of the transistor and γ is the excess noise factor given by , for a long-channel transistor biased in strong inversion [21].

In a conventional CIS readout chain, besides the power supply and bias voltage noise, there are two dominant thermal noise sources: the in-pixel SF transistor operating in saturation and the column-level amplifier. The latter makes the noise sources from the next stages (ADC, CMS, etc.) negligible when enough gain is provided. The two dominant noise sources are uncorrelated; thus, their noise PSDs add. We assume that the bandwidth of the in-pixel SF stage is limited by the column-level amplifier. We consider that the column-level gain is provided by a closed-loop operational transconductance amplifier (OTA). Using the small-signal analysis of the SF stage and the column-level amplifier [8], the thermal noise voltage variance at the output of the column-level amplifier is calculated. It is then referred to the input using the column-level and conversion gain Equation (2), resulting in:

where . Here, and are the integration and load capacitances of the column-level amplifier. and are the noise excess factors corresponding to the in-pixel source follower transistor and the OTA of the column-level amplifier, respectively. and are the transconductances of the in-pixel SF stage and column-level OTA, respectively. is a unitless circuit design parameter dependent on the circuit or processing techniques used after the column-level amplification stage. In the case of CMS, is given by [26]:

Note that for proper settling of the signal between sampling instants, has to be typically larger than five, and under such conditions, can simply be approximated by .

3.3. Leakage Current Shot Noise

During the readout, the charge transferred to the SN may be corrupted by all of the leakage currents through the junctions and gate oxide due to tunneling. Since these leakage currents are due to barrier control processes, they give rise to shot noise. As shown in the small-signal schematic of Figure 5, the leakage current shot noise can be modeled by two noise current sources: and . represents the shot noise of all of the leakage currents flowing between the SN and the ground, which includes the SN junction leakage and the SF gate oxide tunneling current that sinks into the bulk and the drain. represents the shot noise associated with part of the SF gate oxide tunneling current that flows to the source. The unilateral PSD of the current shot noise can be expressed as [27]:

where is the mean value (DC current) of the total leakage current. It can be shown that both shot noise components and have the same transfer function magnitude, between the noise current source and the output of the column level amplifier. The leakage current shot noise PSD at the output of the column level amplifier can therefore be simplified as:

Note that is the sum of all of the sense node leakage currents. The noise PSD after the CMS, taking into account the impact of aliasing, can be expressed as:

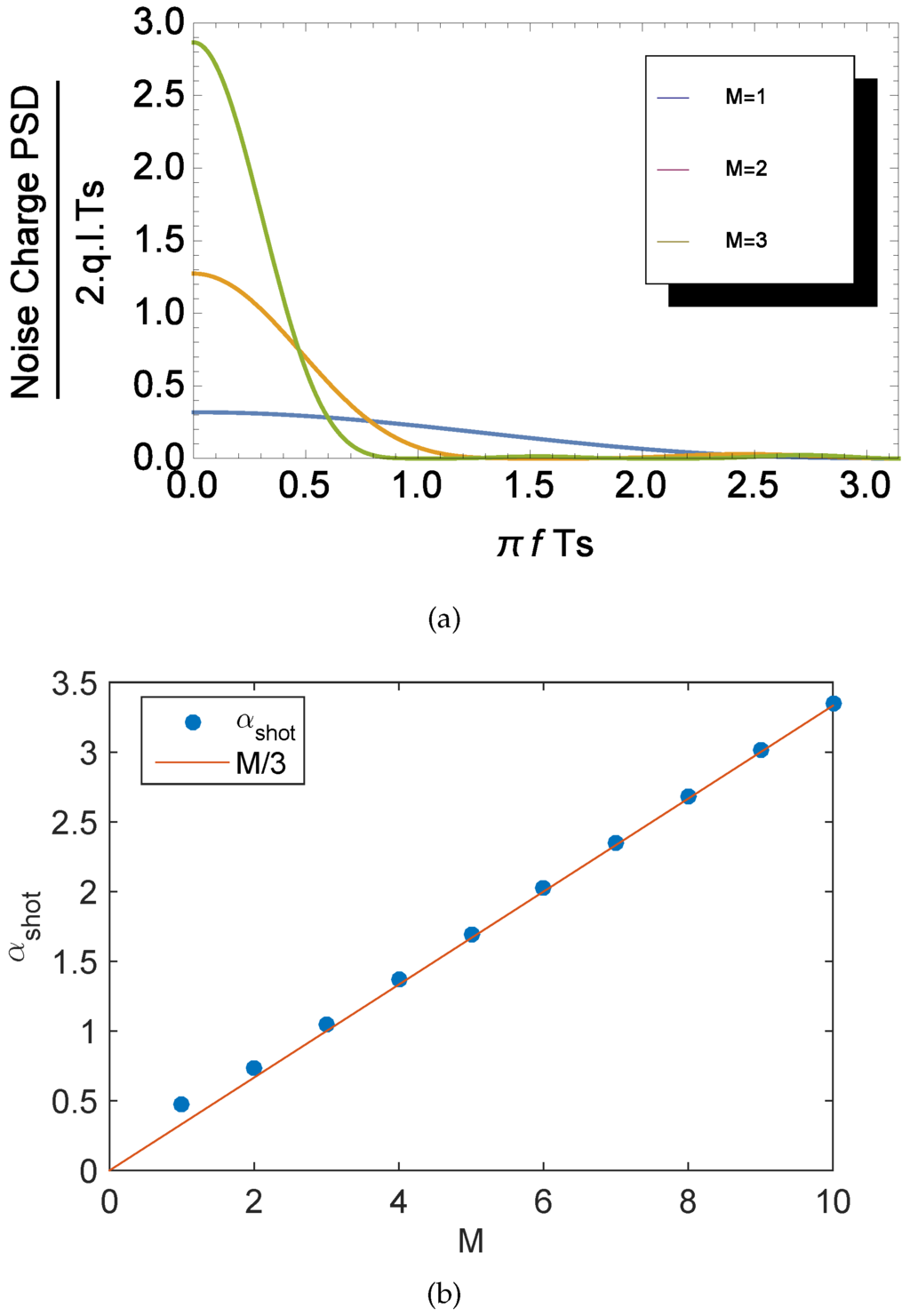

Figure 7a shows a plot of the input-referred shot noise PSD, normalized to . It can be noticed that due to the term in Equation (11), the PSD is independent of , and the area of the PSD increases with M. It can be shown that the input-referred charge variance due to the total leakage current’s shot noise can be expressed as:

with:

Figure 7.

Input-referred shot noise PSD (a) and variance (b), normalized to as a function of the correlated multiple sampling (CMS) order M.

Note that the shot noise current sources feature a white PSD. However, when integrated in the SN capacitance, they give rise to a Wiener process [28]. The variance of this noise is thus expected to rise with the readout time. In order to evaluate the impact of the CMS on the leakage current shot noise, is calculated numerically and plotted in Figure 7b as a function of M. In the case of a simple CDS, is equal to ; hence, the shot noise variance is given by , which corresponds to a typical case of a Wiener process [28]. Figure 7b also shows that, in the general case, the leakage current shot noise increases linearly with .

4. CIS Read Noise Reduction Techniques

4.1. Column-Level Techniques

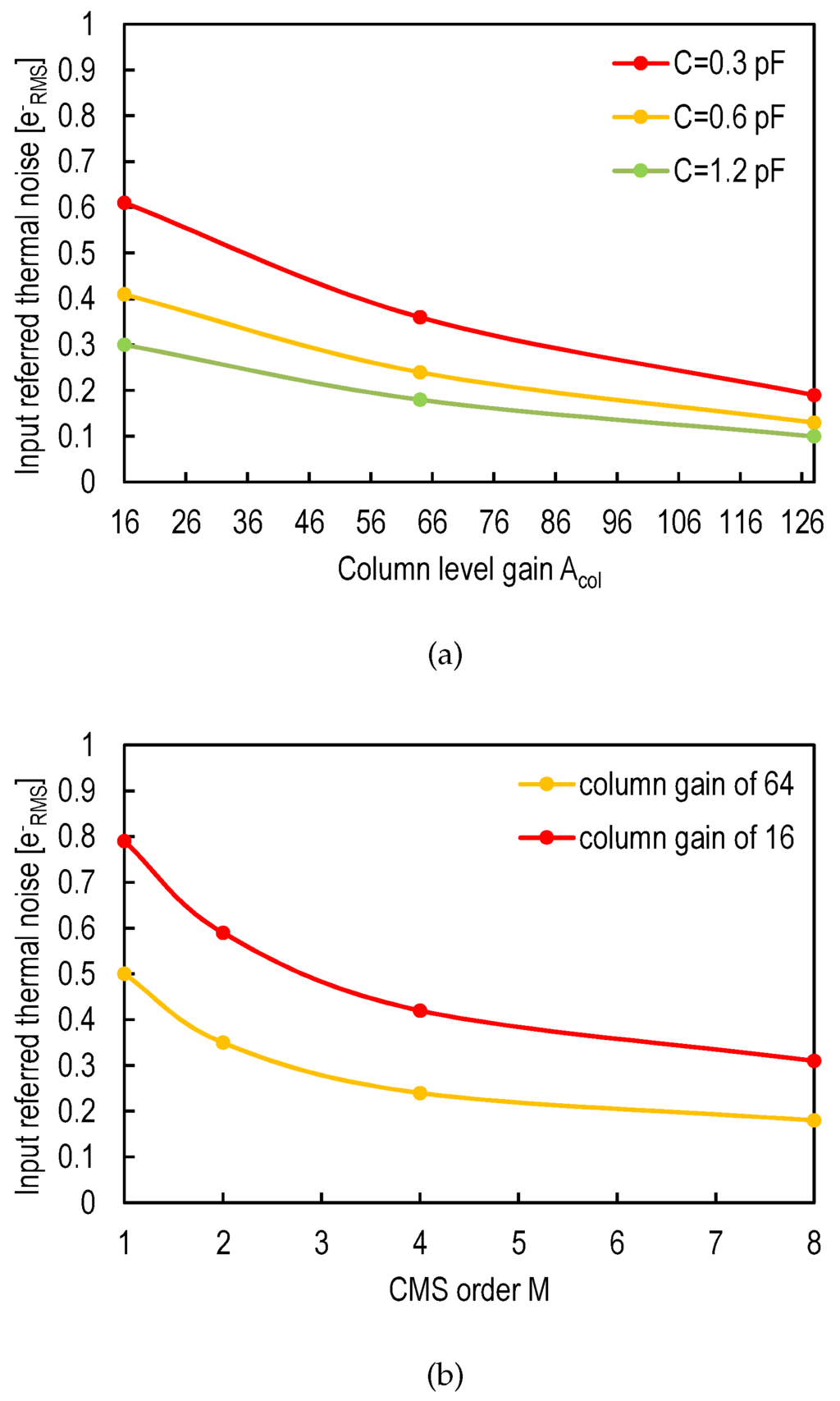

Based on Equation (8), the parameters that can be used to reduce the readout thermal noise independently of the pixel design are the column-level gain , the capacitance C acting on the bandwidth of the column-level amplifier and the CMS order M that determines the value of the parameter . For thermal noise, the column-level gain , the capacitance C and the CMS order M all have the same impact on the input-referred noise. In order to validate this result, transient noise simulations [29] have been performed on a conventional CIS readout chain with a 4T pixel using a standard thick oxide NMOS source follower transistor, a column-level amplifier based on an OTA with a feedback capacitance and the passive CMS circuit presented in [17]. Figure 8a shows the impact of the column-level gain and bandwidth control on the input-referred noise when a simple correlated double sampling is used after the column-level amplifier. Figure 8b shows the impact of the correlated multiple sampling on the input-referred thermal noise for different column-level gains. These simulation results show that the thermal noise can be reduced drastically using only the column-level parameters.

Figure 8.

Input-referred thermal noise, obtained from transient noise simulations, of a CIS readout chain, with a 4T pixel (standard NMOS source follower) with a conversion gain of V, column amplification (closed loop gain with the operational transconductance amplifier (OTA)) and CMS implemented with the analog circuit presented in [17], as a function of: (a) the column-level gain for different values of C and a simple CDS (M = 1); (b) the CMS order M for different values of the column-level gain and pF.

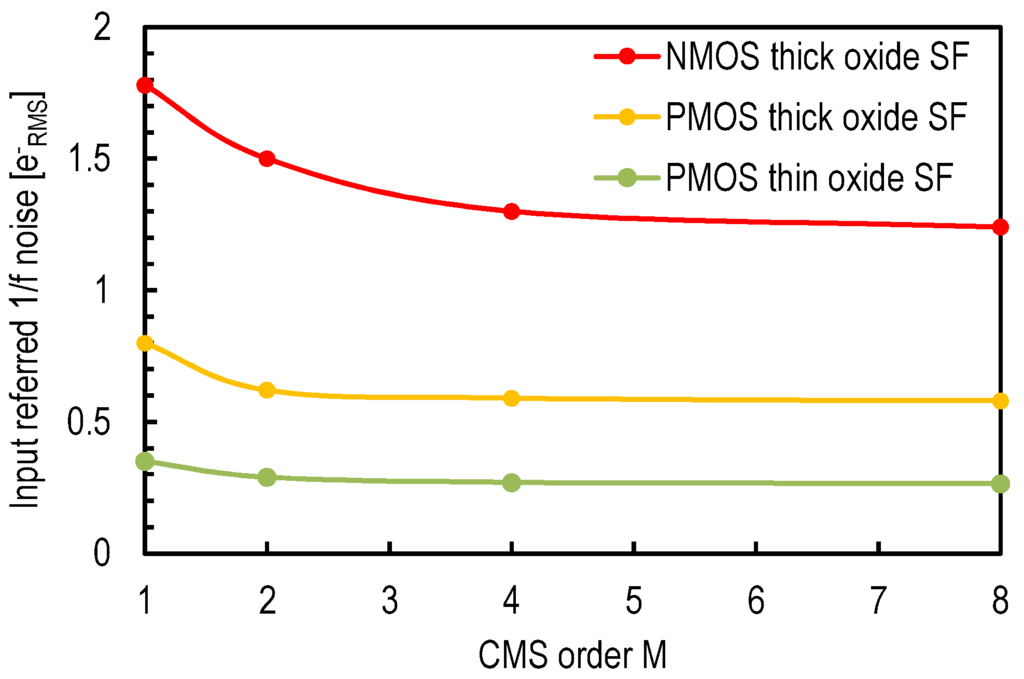

Based on Equation (5), is the only parameter in the input-referred noise expression that is independent of the pixel-level device and process parameters. As shown in Section 3.1, decreases with the CMS order. Figure 9 shows transient noise simulations of the input-referred noise for readout chains with different in-pixel SF types as a function of the CMS order. Figure 9 demonstrates that even if the CMS comes with some noise reduction, the impact of the device parameters (SF type) is much more significant.

Figure 9.

Input-referred noise of a CIS readout chain, with 4T pixel, column amplification and CMS [17], obtained with transient noise simulations, as a function of the CMS order M for different in-pixel source follower transistor types. The pixels with thick oxide NMOS and PMOS SFs feature a conversion gain of about V, while the thin oxide SF based pixel features a conversion gain of V.

4.2. Pixel-Level Techniques

The thermal noise can be reduced to extremely low levels by implementing column-level circuit techniques as shown in Figure 8a,b. Consequently, further reduction of the thermal noise at the pixel level is less efficient, and noise optimization at the pixel level should be mostly focused on reducing the remaining and dominant noise. Equation (5) is the starting point for the noise optimization and suggests different approaches, including proper device selection, design optimizations, as well as process improvements.

4.2.1. Reduce the Capacitance and the Source Follower Transistor Overlap Capacitance

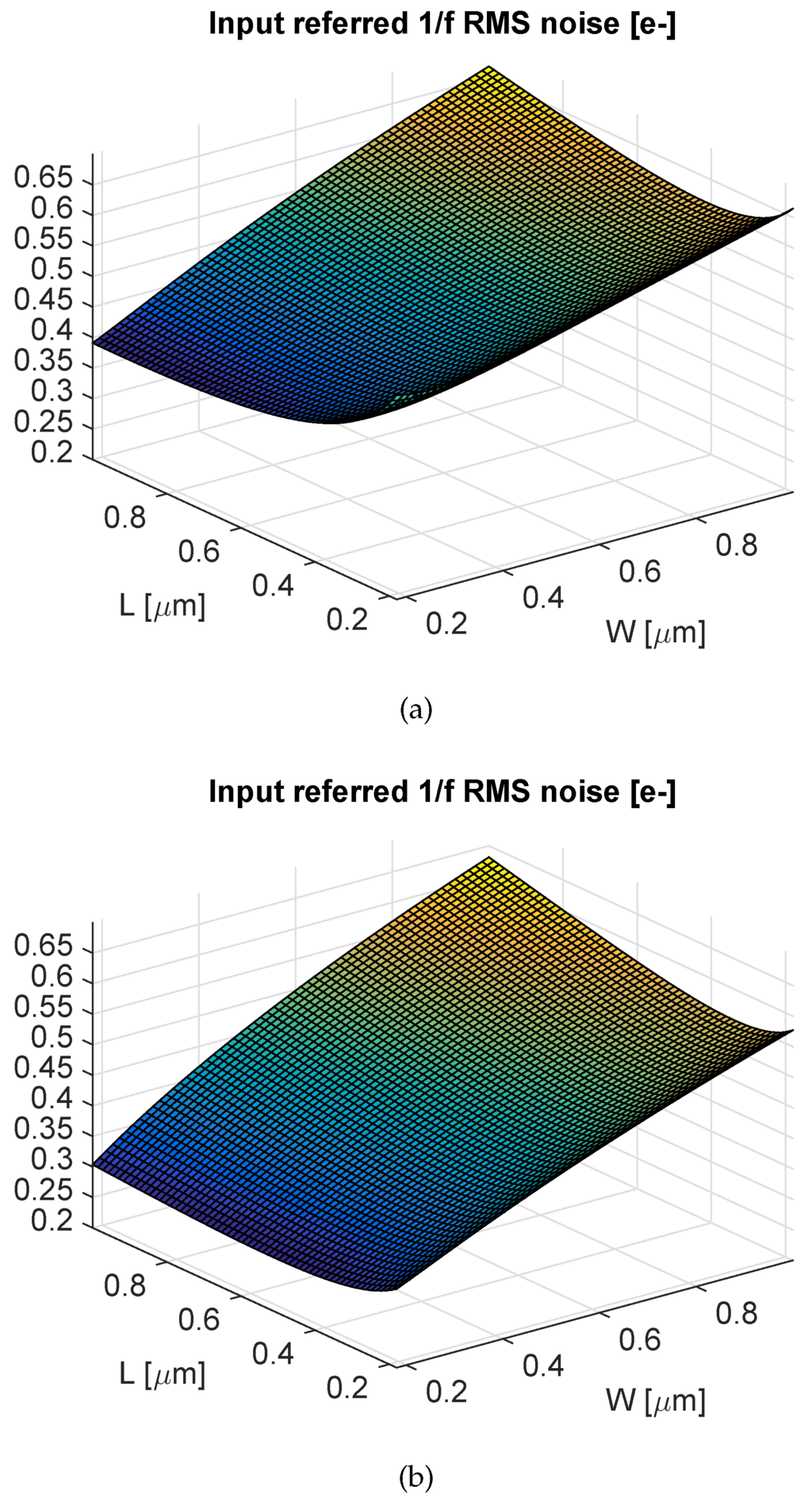

This point remains an active research topic. Careful layout is not enough to significantly decrease the contributions of the wiring parasitic capacitances, the transfer and reset overlap capacitances, as well as the junction capacitance of the floating diffusion. For this purpose, process improvements are necessary. Many recent works presenting sub-electron readout noise CIS actually focused on this point. In [30], different process-level techniques have been presented leading to the reduction of . It has been shown that the omission of the low doped drains (LDDs) used in standard CMOS transistors reduces effectively the gate overlap capacitances. Furthermore, increasing the depletion depth under the floating diffusion by reducing the doping concentration reduces the junction capacitance. The combination of these techniques led to a reduction of about . In [7], the capacitance has been reduced by using an idea called “virtual phase”, well known in CCDs, consisting of creating a potential profile that isolates the floating diffusion from the transfer gate. In this way, the overlap capacitance between the transfer gate and the floating diffusion (denoted in Figure 4) is dramatically reduced. Furthermore, the channel width of the reset transistor is reduced by controlling the doping profile in order to reduce the overlap between the reset gate and the floating diffusion (denoted in Figure 4). However, this was obtained at the cost of a low pixel full-well capacity and a relatively higher lag. In [20], is reduced by introducing a special implant isolating the transfer gate from the SN, and is reduced by omitting the reset transistor. However, this requires the reset to be performed with a high voltage clock of 25 V connected directly to an implant close to the SN. Figure 10 shows the impact of the reduction through a plot of the calculated input-referred noise as a function of the gate width and length, based on Equation (5), for a of fF, corresponding to a standard process, and a of fF, corresponding to the one that could be obtained through advanced process refinements [30]. Figure 10 shows the effectiveness of this reduction, which leads to a reduction of the input-referred noise from to .

Figure 10.

The calculated input-referred noise, based on Equation (5), as a function of the in-pixel source follower width W and length L for a thin oxide transistor in a 180-nm technology where fF/μm, fF/μm, FV/m, , and in (a) fF, it corresponds to the SN capacitance in a standard process, (b) fF corresponds to an SN capacitance reduced with process-level optimization.

4.2.2. Reduce the Noise Process Parameter (the Oxide Trap Density )

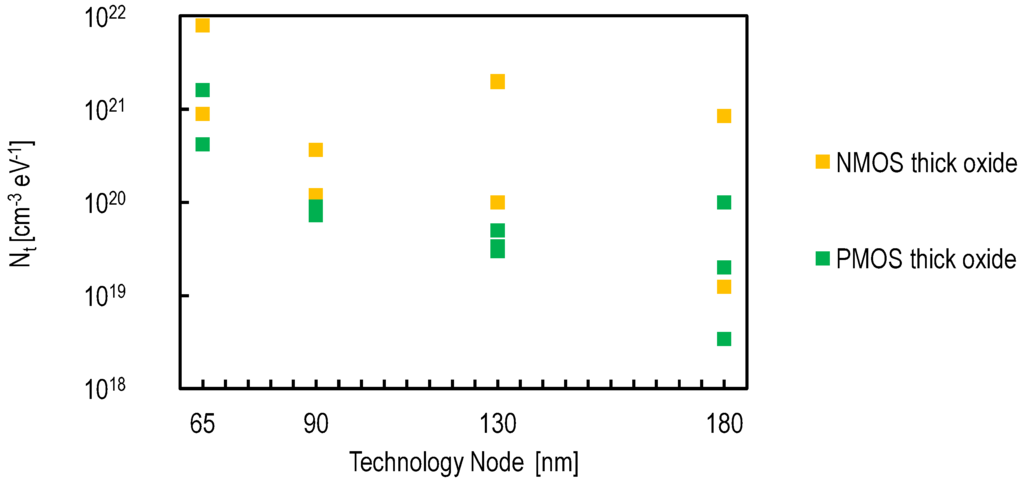

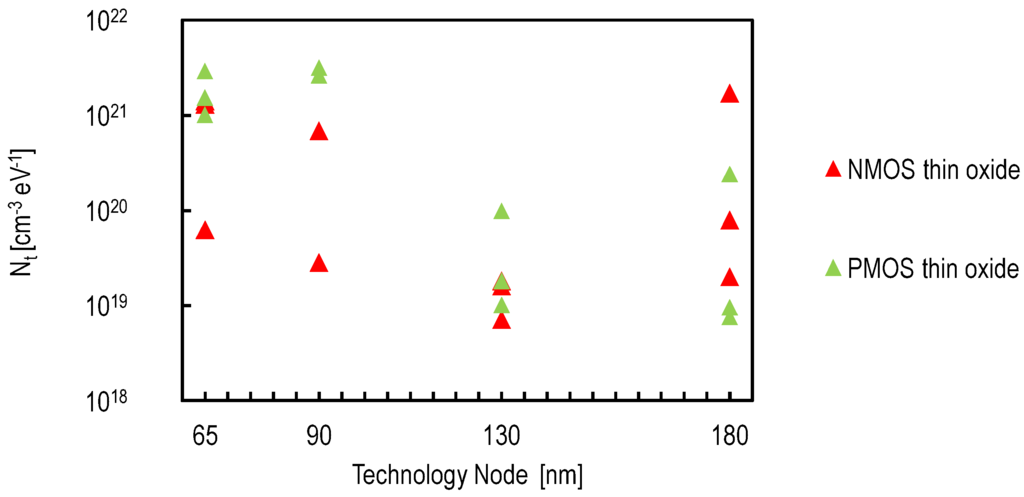

This point can be addressed through design choices and technological improvements. It is known that buried channel devices have a lower noise by featuring a lower parameter. This is likely due to the fact that the charge carriers are kept away from the silicon oxide interface [31]. It has been shown that using buried channel NMOS source followers leads to sub-electron noise performance [19]. From a design aspect, thick-oxide transistors that operate at voltages as high as V are commonly used in CIS pixels. Figure 11 shows the oxide trap density of PMOS and NMOS thick oxide transistors from different foundries and technology nodes. It shows that PMOS transistors feature, generally, a parameter lower than NMOS transistors. Using an in-pixel PMOS source follower transistor also led to a sub-electron noise performance [32]. The drawback of in-pixel PMOS transistor is the reduction of the fill factor due to the spacings imposed by the layout design rules and the possible quantum efficiency reduction if the PMOS n-well is too close to the PPD.

Figure 11.

The oxide trap density , of PMOS and NMOS thick oxide transistors, as a function of the technology node based on measurement results reported in design kits from different foundries.

4.2.3. Increase the Oxide Capacitance per Unit Area

Based on Equation (5), the noise can also be reduced by increasing the oxide capacitance per unit area of the in-pixel SF. From a design perspective, this corresponds to the selection of a thin oxide SF instead of the traditional thick oxide transistor. In most CIS processes, all of the gates included in the pixel feature thick oxides, since the transfer gate and the reset gate are controlled by high voltages (V); the SF is also chosen as a thick oxide transistor to exploit a high dynamic range. In [8], it has been shown how a thin oxide transistor can be implemented in a CIS pixel without degrading the dynamic range or dramatically reducing the fill factor at the benefit of a much reduced input-referred noise.

4.2.4. Use a Minimum Gate Width and an Optimal Length

Based on Equation (5), it can be shown analytically [33,34] or numerically using the a plot of Equation (5) versus the gate width and length that the lowest input-referred noise corresponds to the minimum gate width and an optimal length generally slightly higher [33]. Figure 10 illustrates this principle on a practical example. It shows a plot of the input-referred noise as a function of the gate width and length for a pixel based on a thin oxide PMOS SF of a 180-nm CMOS process for two different values of . It shows how, for both values, the input-referred noise can be reduced by choosing a minimum SF gate width and a slightly larger length. Note that the reduction of the SF gate size might increase the probability of RTS noise occurrence [35]. However, the amplitude of the RTS noise is inversely proportional to the gate area [36]; thus, it would be also reduced by using a minimum SF gate width.

4.2.5. Thin Oxide Source Follower: A Good Match

From the designer’s perspective, the points mentioned in Section 4.2.3 and Section 4.2.4 can both be addressed by using a thin oxide SF. Indeed, A thin oxide SF with a minimum gate width features also lower overlap capacitances. It is important to verify that the choice of a thin oxide transistor does not come at the cost of a negative impact on the noise process parameter . A thinner oxide is expected to come with a better control of the gate over the channel and, therefore, a lower . The oxide trap density of thin oxide PMOS transistors and thick oxide NMOS transistors of different foundries and technology nodes has been compared in [8] based on data reported in design kits. This comparison showed that the thin oxide PMOS transistors generally feature a lower oxide trap density. Thus, using a thin oxide PMOS source follower addresses the points of Section 4.2.2, Section 4.2.3 and Section 4.2.4 at once. Figure 12 shows the schematic of a 4T pixel based on a thin oxide PMOS SF. In order to validate this idea, a transient noise simulation is performed on three readout chains based respectively on a standard thick oxide NMOS, a thick oxide PMOS and a thin oxide PMOS source follower in a 180-nm CIS process. The compared readout chains share the same column level amplification and CMS circuit presented in [17]. Figure 9 shows the impact of the in-pixel source follower transistor type, as well as the CMS order M on the input-referred noise. The PMOS SF-based readout chain features a lower noise than the NMOS-based one thanks to the increase of and the reduction of the parameter . The readout chain based on the thin oxide PMOS SF features the lowest input-referred noise because its SF cumulates a lower , a higher oxide capacitance per unit area and a lower minimum width.

Figure 12.

Schematic of the recently-proposed pixel [8] based on a thin oxide PMOS source follower.

It is important to verify that these techniques are not harmful in terms of the thermal noise. Equation (8) shows that the thermal noise is reduced by increasing the conversion gain. Thus, using a thin oxide SF with smaller gate dimensions is also expected to reduce the input-referred thermal noise.

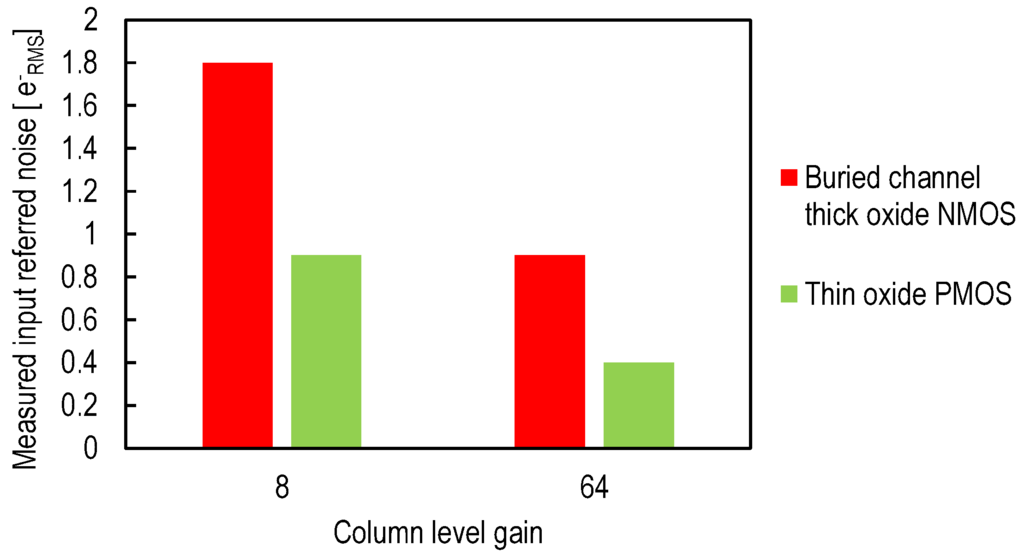

The benefits of using a thin oxide SF transistor have been confirmed with measurement results. A test chip comparing pixels based on thin oxide PMOS source followers with state-of-the-art pixels with thick oxide buried channel NMOS source followers has been presented in [8]. Figure 13 shows the measured average total input-referred noise of the two different pixels for two column-level gain values and with a simple CDS. Figure 13 shows how both thermal (at low column gain) and noise (at high column gain) are dramatically reduced thanks to the implementation of the source follower with a thin oxide PMOS transistor.

Figure 13.

The measured input-referred total noise of a CIS readout chain, with 4T pixel and column amplification, for two column level gains , for an in-pixel buried channel thick oxide NMOS source follower and a thin oxide PMOS source follower from [8].

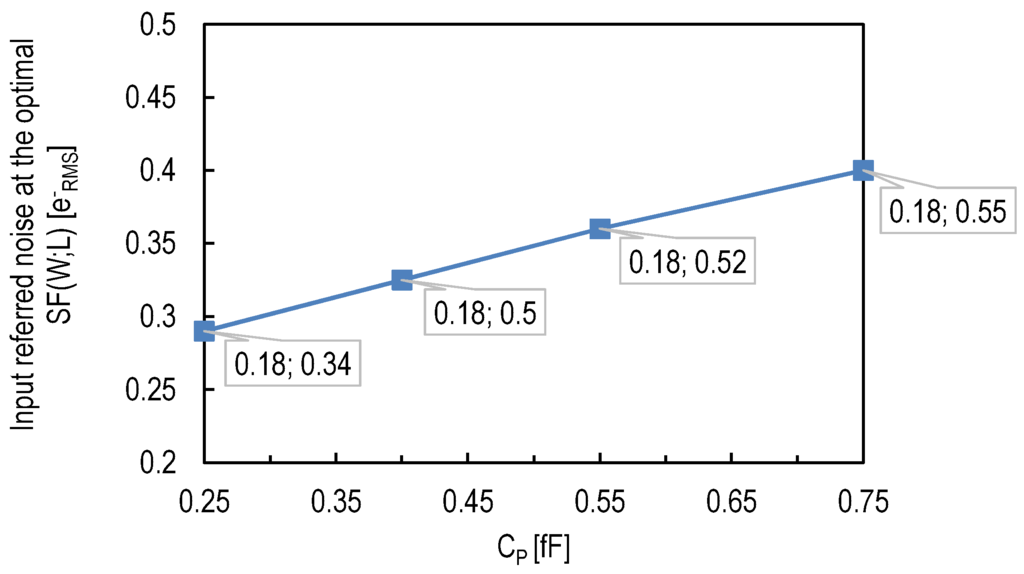

The tested pixel was designed using a standard CIS process and fulfilling the standard design rules. There was therefore no possibility to exploit the impact of the reduction of through process optimization. In order to predict the impact of the combination of thin oxide SF with process optimizations reducing the sense node capacitance, the parameter of Equation (5) is replaced by the measurement results from [30]. The starting point corresponds to the result of obtained in [8] and corresponding to the case of a thin oxide SF-based pixel design with standard rules. Then, the values of based on [30] are used to predict the evolution of the input-referred noise for each additional technique used to reduce the the SN capacitance. The result is plotted in Figure 14. It shows the expected input-referred noise, at the optimal gate width and length, for each value of . Figure 14 shows that the limit can be crossed if the thin oxide PMOS SF is combined with process optimizations reducing in the 180-nm process used in [8].

Figure 14.

The input-referred noise as a function of the capacitance determined by the floating diffusion, wiring and parasitic capacitances independent from the source follower transistor. fF corresponds to the case of a conventional sense node junction, transfer gate and transistors. fF corresponds to the case of transfer and reset gates without low doped drains [30]. fF corresponds to the case of transfer and reset gates without low doped drains and a sense node without channel stop underneath [30]. fF corresponds to the case of more advanced process refinements as [7,30]. The numbers in labels correspond to the minimum width and optimum length as discussed in Section 4.2.4.

5. CIS Read Noise and Technology Downscaling

Since their first development, CIS pixels have always been designed with thick oxide transistors compatible with high voltages (3.3 V). The device parameters of thick oxide transistors do not follow the scaling rules as the thin oxide transistors. The impact of the technology downscaling on these devices is rather limited. Moreover, it appears that the oxide trap density of thick oxide transistors tends to increase with the technology downscaling, as shown in Figure 11.

It has been demonstrated in [8] that a thin oxide SF can be used together with a conventional PPD for a low noise performance. Thin oxide transistors, on the other hand, take full advantage of technology downscaling. Thus, it is interesting to investigate the impact of technology downscaling on the input-referred noise. The starting point for analyzing the impact of the technology downscaling on the input-referred noise of a readout chain based on a thin oxide SF is Equations (5) and (8). The conclusions can be made based on how the technology downscaling affects the different process and device parameters. Table 1 shows the scaling factor corresponding to the relevant device parameters [37]. The technology downscaling allows a higher oxide capacitance per unit area, a lower gate width and lower overlap and parasitic capacitances. Hence, the input-referred noise variance is supposed to decrease with , assuming that the oxide trap density remains constant with the technology downscale. The thermal noise is expected to decrease with and, hence, would remain negligible. The International Technology Roadmap for Semiconductors (ITRS) expects the oxide trap density to decrease with the technology downscaling [22]. Figure 15 shows the values, for thin oxide transistors, reported in design kits of three foundries for different technology nodes. It shows that the oxide trap density follows the ITRS roadmap when downscaling from nm to nm. For more advanced technologies, the data are not conclusive and must be verified by measurements. The noise of NMOS transistors does not increase dramatically. On the contrary, PMOS transistors appear to show a higher for advanced technologies. In bulk CMOS, the buried channel conductance of the PMOS transistors is likely the reason for their lower noise. While deep submicron PMOS transistors are expected to behave as surface channel devices, which explains the fact that their noise becomes comparable to the one of NMOS transistors.

Table 1.

Impact of technology downscaling on the parameters of the input-referred noise in Equation (5).

Figure 15.

The evolution of the oxide trap density , as a function of the technology node based on measurement results reported in design kits from different foundries.

The measurement results presented in [8,38] explore indirectly the impact of the technology downscaling on the noise reduction. A pixel with a thin oxide SF transistor have been compared to a thick oxide SF based one. For the 180-nm process used in [8,38], the thick oxide transistor features an oxide capacitance per unit area of 5 fF/μm compared to fF/μm for the thin oxide transistor. In addition, the minimum width determined by the design rules is m for the thick oxide compared to m for the thin oxide transistor. Consequently, using a thin oxide source follower transistor instead of a thick oxide has the same effect as a technology downscaling with a scaling factor of two. Based on this observation, the input-referred noise is expected to decrease by a factor of two, which matches the measurement results shown in Figure 13.

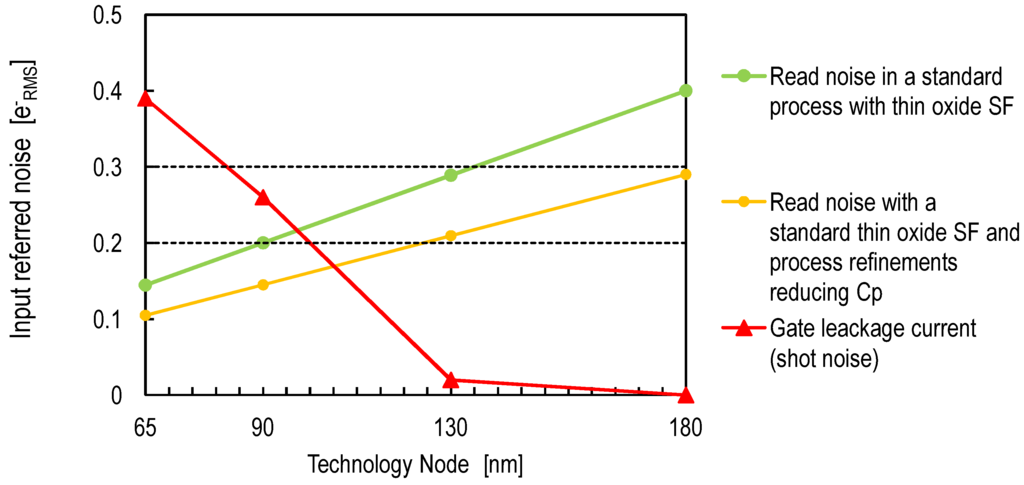

Besides the read noise originating from the and thermal noise, the gate leakage current shot noise has been up to now neglected due to the extremely low levels of the leakage currents achieved in the used technology. It is important to investigate the evolution of this noise when using more advanced technologies. Indeed, the gate leakage current increases by several orders of magnitude when downscaling from 180-nm to 65-nm technologies [37]. Based on Equation (13), the shot noise associated with the gate leakage current is hence expected to increase significantly. In order to evaluate its impact, simulations have been performed with transistors having a minimum gate width and length from technologies between nm and nm. The corresponding leakage current shot noise RMS is given by the square root of the total number of electrons crossing the gate in a time interval of s (enough to read two samples). The results are plotted in Figure 16. Figure 16 also shows how the input-referred noise is expected to decrease by only taking advantage of the technology downscaling based on Equation (5) and the assumption of constant oxide trap density for deep submicron technologies. The starting point corresponds to the input-referred noise obtained using a thin oxide SF in a 180-nm CMOS process [8]. It can be noticed that the limit can be crossed if a CIS process is developed with a technology node under nm and a thin oxide transistor is used as a SF. However, for technologies under nm, the gate leakage current appears to be a severe problem starting to dominate the total noise. Hence, the optimal technology node is between nm and nm, unless process improvements are applied to reduce the gate leakage current. Figure 16 shows also the impact on the technology node when the process refinements reducing the SN capacitance are applied. The noise levels for each technology node are obtained using Equation (5) and the scaling rules. The starting point corresponds to noise expected when combining the thin oxide PMOS SF with a of fF, as shown in Figure 14. The latter shows that an input-referred read noise under could be possible with a technology node between nm and nm, a thin oxide SF and process level reduction.

Figure 16.

The expected evolution, with technology downscale, of the input-referred noise of CIS designed with standard CMOS process with thin oxide in-pixel SF.

RTS noise may also be a concern with the technology downscaling. In sate-of-the-art low noise CMOS image sensors, it may result in a dramatically high input referred-noise value of about several , but it is only present in a minority of pixels (the tail of the noise histogram). Therefore, RTS noise was not accounted for in this work, including in the extrapolation towards downscaled technologies, because we limited the latter to 65 nm, where leakage is much more an issue. A further investigation of input-referred noise for such 4T pixels in deep submicron technology would definitely require one to account for RTS noise. Unfortunately, RTS noise is not modeled in the most common simulators, and the complexity of this phenomena still impedes an analytically- or empirically-precise expression of its occurrence.

6. Conclusions

The capability of performing photo-electron counting, with an accuracy higher than , using conventional CIS readout chains requires a total read noise level below . This read noise is mainly composed of the noise originating from the in-pixel SF, the thermal noise originating from the pixel- and column-level saturated transistors and the shot noise associated with the leakage current at the level of the SN. The latter is negligible in the technology nodes used currently (above nm).

The thermal noise can be drastically reduced, to extremely low levels, by combining column-level gain, bandwidth control and CMS. The noise becomes then the dominant noise source. The reduction of the noise can involve process-, device- and circuit-level optimizations. The process-level refinements include the sense node total capacitance and the SF parameter reduction. At the device level, the input-referred noise can be reduced by using an in-pixel SF with a higher oxide capacitance per unit area, a minimum gate width and an optimal gate length. The implementation of an in-pixel thin oxide PMOS SF-instead of a thick oxide NMOS presents a practical example of how this device level optimization can be performed in a standard process. At the circuit level, the noise can be slightly further reduced using the CMS.

Based on measurement results reported in recent works and the analytical expressions of the input-referred noise, the combination of a standard thin oxide PMOS SF with the process refinement reducing the SN capacitance is expected to decrease the total read noise of a conventional CIS below .

The input-referred thermal and noise are expected to decrease with the technology downscaling to levels below . For technologies below nm, the SF gate oxide leakage current is expected to increase dramatically. Therefore, unless the leakage current is reduced by some other means at the process level, the optimum technology node ranges between nm and nm.

Acknowledgments

Commissariat à l’Énérgie Atomique (CEA) and Délégation générale de l’armement (DGA) are acknowledged for the financial support of this work.

Author Contributions

Assim Boukhayma carried out the data analysis, the theoretical and experimental work. Assim Boukhayma, Arnaud Peizerat and Christian Enz contributed to write this paper. All the authors have read and approved the final manuscript.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Seitz, P.; Theuwissen, A.J.P. Single-Photon Imaging; Springer: Berlin, Germany, 2011. [Google Scholar]

- Fossum, E. The quanta image sensor (QIS): Concepts and challenges. Imaging Appl. Opt. Opt. Soc. Am. 2011. [Google Scholar] [CrossRef]

- Teranishi, N. Required conditions for photon-counting image sensors. IEEE Trans. Electron Devices 2012, 59, 2199–2205. [Google Scholar] [CrossRef]

- Bronzi, D.; Villa, F.; Tisa, S.; Tosi, A.; Zappa, F. SPAD Figures of merit for photon-counting, photon-timing, and imaging applications: A review. IEEE Sens. J. 2016, 16, 3–12. [Google Scholar] [CrossRef]

- Charbon, E. Single-photon imaging in complementary metal oxide semiconductor processes. Philos. Trans. R. Soc. Lond. A Math. Phys. Eng. Sci. 2014, 372. [Google Scholar] [CrossRef] [PubMed]

- Wakashima, S.; Kusuhara, F.; Kuroda, R.; Sugawa, S. A linear response single exposure CMOS image sensor with 0.5 e- readout noise and 76 ke- full well capacity. In Proceedings of the 2015 Symposium on VLSI Circuits, Kyoto, Japan, 17–19 June 2015; pp. C88–C89.

- Ma, J.; Starkey, D.; Rao, A.; Odame, K.; Fossum, E. Characterization of quanta image sensor pump-gate jots with deep sub-electron read noise. IEEE J. Electron Devices Soc. 2015, 3, 472–480. [Google Scholar] [CrossRef]

- Boukhayma, A.; Peizerat, A.; Enz, C. Temporal readout noise analysis and reduction techniques for low-light CMOS image sensors. IEEE Trans. Electron Devices 2016, 63, 72–78. [Google Scholar] [CrossRef]

- Enz, C.; Temes, G. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Bonjour, L.E.; Blanc, N.; Kayal, M. Experimental analysis of lag sources in pinned photodiodes. IEEE Electron Device Lett. 2012, 33, 1735–1737. [Google Scholar] [CrossRef]

- Fossum, E.R. Charge transfer noise and lag in CMOS active pixel sensors. In Proceedings of the 2003 IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors, Elmau, Germany, 15 May 2003; pp. 1–6.

- Thornber, K. Noise suppression in charge transfer devices. Proc. IEEE 1972, 60, 1113–1114. [Google Scholar] [CrossRef]

- Janesick, J.R. Scientific Charge-Coupled Devices; SPIE: Bellingham, WA, USA, 2001. [Google Scholar]

- Wang, X.; Rao, P.R.; Theuwissen, A.J.P. Fixed-pattern noise induced by transmission gate in pinned 4T CMOS image sensor pixels. In Proceedings of the 36th European Solid-State Device Research Conference, Montreux, Switzerland, 19–21 September 2006; pp. 331–334.

- Goiffon, V.; Virmontois, C.; Magnan, P. Investigation of dark current random telegraph signal in pinned photodiode CMOS image sensors. In Proceedings of the 2011 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 8.4.1–8.4.4.

- Fowler, B.; Liu, X.C. Charge Transfer Noise in Image Sensors. In Proceedings of the 2007 International Image Sensor Workshop (IISW), Ogunquit, ME, USA, 7–10 June 2007; pp. 51–54.

- Boukhayma, A.; Peizerat, A.; Enz, C. A correlated multiple sampling passive switched capacitor circuit for low light CMOS image sensors. In Proceedings of the 2015 International Conference on Noise and Fluctuations (ICNF), Xi’an, China, 2–6 June 2015; pp. 1–4.

- Suh, S.; Itoh, S.; Aoyama, S.; Kawahito, S. Column-Parallel correlated multiple sampling circuits for CMOS image sensors and their noise reduction effects. Sensors 2010, 10, 9139–9154. [Google Scholar] [CrossRef] [PubMed]

- Chen, Y.; Xu, Y.; Chae, Y.; Mierop, A.; Wang, X.; Theuwissen, A. A 0.7 temporal-readout-noise CMOS image sensor for low-light-level imaging. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Pap. 2012, 55, 384–386. [Google Scholar]

- Seo, M.; Kawahito, S.; Kagawa, K.; Yasutomi, K. A 0.27 Read Noise 220 μV/e− Conversion Gain Reset-Gate-Less CMOS Image Sensor With 0.11-μm CIS Process. IEEE Electron Device Lett. 2015, 36, 1344–1347. [Google Scholar]

- Enz, C.; Vittoz, E. Charge Based MOS Transistor Modeling: The EkV Model For Low-Power and RF IC Design; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Nemirovsky, Y.; Corcos, D.; Brouk, I.; Nemirovsky, A.; Chaudhry, S. 1/f noise in advanced CMOS transistors. IEEE Instrum. Meas. Mag. 2011, 14, 14–22. [Google Scholar] [CrossRef]

- Hung, K.; Ko, P.; Hu, C.; Cheng, Y. A physics-based MOSFET noise model for circuit simulators. IEEE Trans. Electron Devices 1990, 37, 1323–1333. [Google Scholar] [CrossRef]

- Ghibaudo, G. Low-frequency noise and fluctuations in advanced CMOS devices. Proc. SPIE 2003, 5113, 16–28. [Google Scholar]

- Celik-Butler, Z. Low-frequency noise in deep-submicron metal-oxide-semiconductor field-effect transistors. IEEE Proc. Circuits Devices Syst. 2002, 149, 23–31. [Google Scholar] [CrossRef]

- Enz, C.; Boukhayma, A. Recent trends in low-frequency noise reduction techniques for integrated circuits. In Proceedings of the 2015 International Conference on Noise and Fluctuations (ICNF), Xi’an, China, 2–6 June 2015; pp. 1–6.

- Scholten, A.; Tiemeijer, L.; van Langevelde, R.; Havens, R.; Zegers-van Duijnhoven, A.; Venezia, V. Noise modeling for RF CMOS circuit simulation. IEEE Trans. Electron Devices 2003, 50, 618–632. [Google Scholar] [CrossRef]

- Papoulis, A. Probability, Random Variables, and Stochastic Processes; McGraw-Hill: New York, NY, USA, 1965. [Google Scholar]

- Bolcato, P.; Tawfik, M.; Poujois, R.; Jarron, P. A new efficient transient noise analysis technique for simulation of CCD image sensors or particle detectors. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Diego, CA, USA, 9–12 May 1993; pp. 14.8.1–14.8.4.

- Fumiaki, K.; Shunichi, W.; Satoshi, N.; Rihito, K.; Shigetoshi, S. Analysis and Reduction of Floating Diffusion Capacitance Components of CMOS Image Sensor for Photon-Countable Sensitivity. In Proceedings of the International Image Sensors Workshop (IISW), Vaals, The Netherlands, 8–11 June 2015; pp. 120–123.

- Chen, Y.; Wang, X.; Mierop, A.; Theuwissen, A. A CMOS image sensor with in-pixel buried-channel source follower and optimized row selector. IEEE Trans. Electron Devices 2009, 56, 2390–2397. [Google Scholar] [CrossRef]

- Lotto, C.; Seitz, P.; Baechler, T. A sub-electron readout noise CMOS image sensor with pixel-level open-loop voltage amplification. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 20–24 February 2011. [CrossRef]

- Boukhayma, A.; Peizerat, A.; Dupret, A.; Enz, C. Design optimization for low light CMOS image sensors readout chain. In Proceedings of the IEEE 12th International New Circuits and Systems Conference (NEWCAS), Trois-Rivieres, QC, Canada, 22–25 June 2014; pp. 241–244.

- Boukhayma, A.; Peizerat, A.; Dupret, A.; Enz, C. Comparison of two optimized readout chains for low light CIS. Proc. SPIE 2014, 9022, 90220H–90220H-11. [Google Scholar]

- Martin-Gonthier, P.; Magnan, P. Novel readout circuit architecture for CMOS image sensors minimizing RTS noise. IEEE Electron Device Lett. 2011, 32, 776–778. [Google Scholar] [CrossRef]

- Kwon, H.M.; Han, I.S.; Bok, J.D.; Park, S.U.; Jung, Y.J.; Lee, G.W.; Chung, Y.S.; Lee, J.H.; Kang, C.Y.; Kirsch, P.; et al. Characterization of random telegraph signal noise of high-performance p-MOSFETs with a high-k dielectric/metal gate. IEEE Electron Device Lett. 2011, 32, 686–688. [Google Scholar] [CrossRef]

- Lewyn, L.; Ytterdal, T.; Wulff, C.; Martin, K. Analog circuit design in nanoscale CMOS technologies. Proc. IEEE 2009, 97, 1687–1714. [Google Scholar] [CrossRef]

- Boukhayma, A.; Peizerat, A.; Enz, C. A 0.4 Temporal Readout Noise 7.5 μm Pitch and a 66% Fill Factor Pixel for Low Light CMOS Image Sensors. In Proceedings of the International Image Sensors Workshop (IISW), Vaals, The Netherlands, 8–11 June 2015; pp. 365–367.

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).