A Simple Closed-Loop Active Gate Voltage Driver for Controlling diC/dt and dvCE/dt in IGBTs

Abstract

:1. Introduction

1.1. Junction Temperature (Tj)

1.2. Load Variation

1.3. IGBT’s Nonlinearity

2. Proposed Active Gate Control Method

2.1. Philosophy of the Method

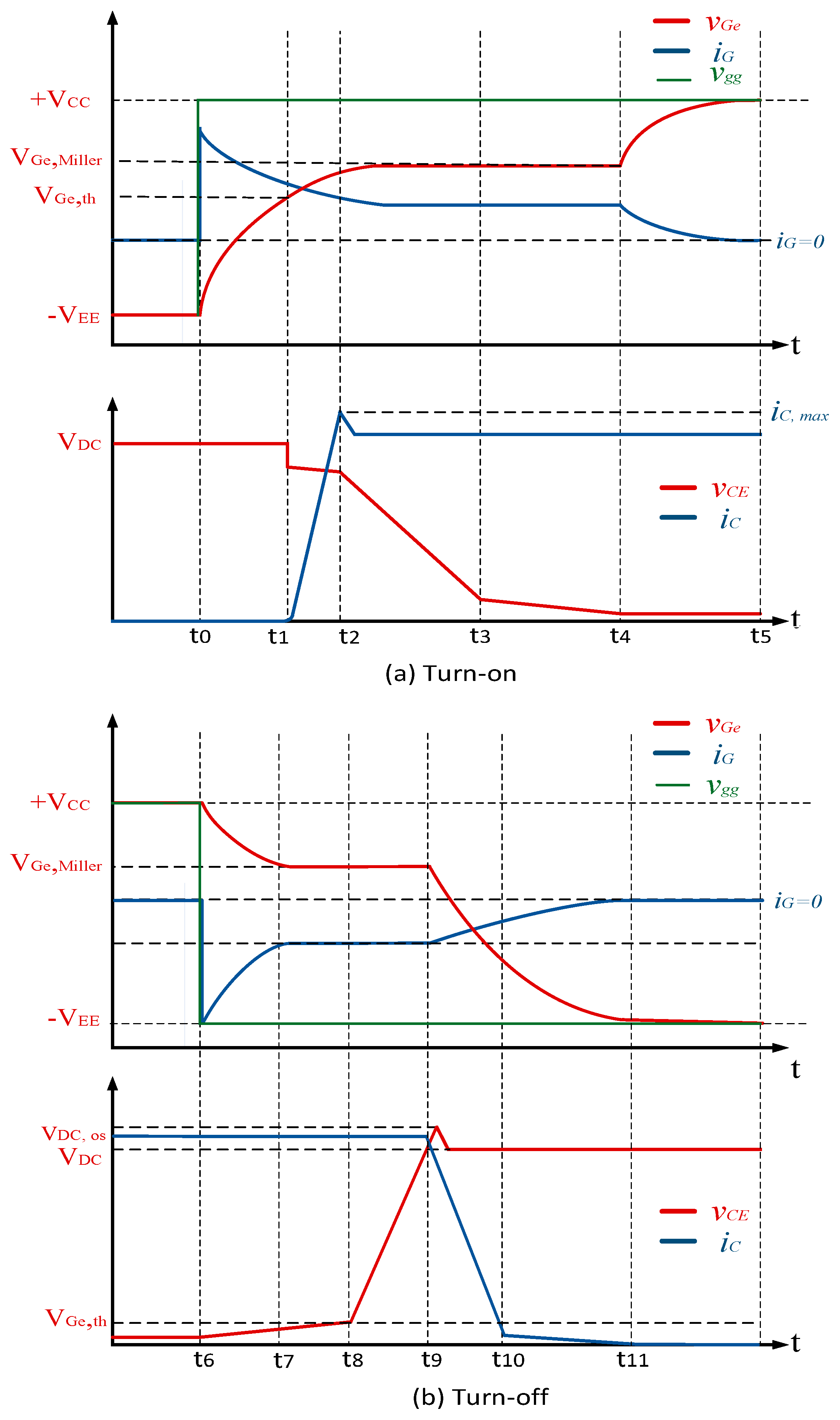

2.2. The Operation Principles

3. The Closed-Loop GD Tuning and Experimental Results

4. The Performance Index of Closed-Loop GD

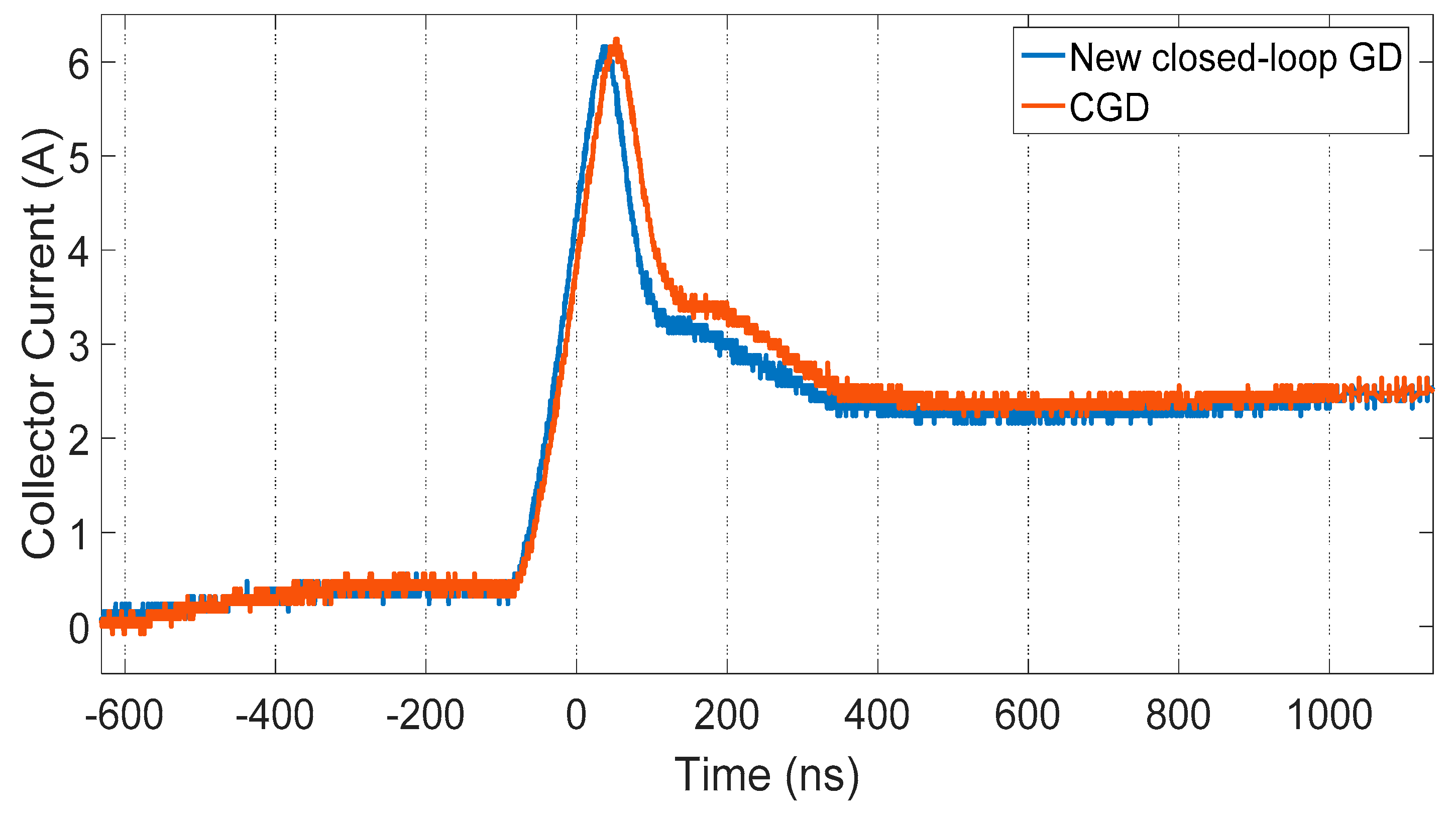

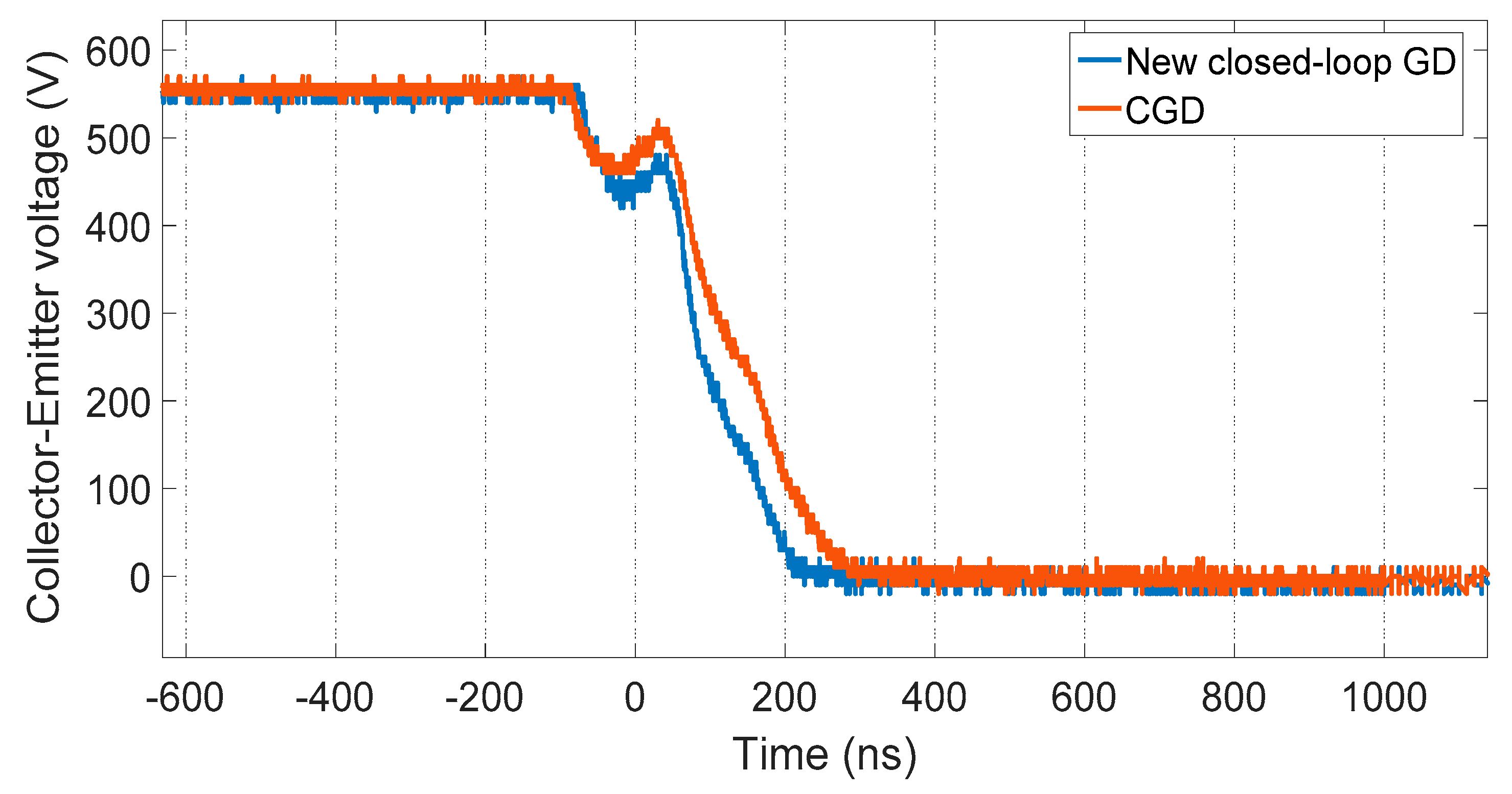

4.1. The Comparison with CGD

4.2. Electromagnetic Interference Analysis

4.3. The Cost Study

5. Conclusions

- The proposed GD has the capability to control diC/dt and dvCE/dt in turn-on and turn-off respectively. Controlling the GD is possible with very simple tuning in both switching states.

- The closed-loop GD has eliminated the overshoot from collector current by more than 20%. Furthermore, the VCE overshoot has been reduced by more than 10%. Therefore, the IGBT lifetime will be extended.

- The performance index showed that the closed-loop GD has lower switching losses compared to CGD in both turn-on and turn-off conditions.

- This novel closed-loop controller keeps its performance versus Tj and load variations without applying an extra circuit in its topology.

- Based on spectrum analysis of the current and voltage transition obtained from experimental tests, the radiated emission of EMI is reduced during switching transient.

- The proposed gate driver is simple enough to allow its use in real industrial applications. In addition, based on the evaluation carried out it is a fairly cost-effective solution.

Author Contributions

Funding

Conflicts of Interest

Appendix A

References

- Paul, C.R. Introduction to Electromagnetic Compatibility, 2nd ed.; Wiley: Hoboken, NJ, USA, 2006. [Google Scholar]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC versus Si—Evaluation of potentials for performance improvement of inverter and DC-DC converter systems by SiC power semiconductors. IEEE Trans. Ind. Electron. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Lobsiger, Y.; Kolar, J.W. Closed-Loop di/dt and dv/dt IGBT Gate Driver. IEEE Trans. Power Electron. 2015, 30, 3402–3417. [Google Scholar] [CrossRef]

- Hefner, A.R. An improved understanding for the transient operation of the power insulated gate bipolar transistor (IGBT). IEEE Trans. Power Electron. 1990, 5, 459–468. [Google Scholar] [CrossRef]

- Hefner, A.R. An investigation of the drive circuit requirements for the power insulated gate bipolar transistor (IGBT). IEEE Trans. Power Electron. 1991, 6, 208–219. [Google Scholar] [CrossRef]

- Chokhawala, R.; Catt, J.; Pelly, B. Gate drive considerations for IGBT modules. Proc. Rec. IEEE Ind. Appl. Soc. Annu. Meet. 1992, 1, 1186–1195. [Google Scholar]

- John, V.; Suh, B.S.; Lipo, T.A. High performance active drive for high power IGBTs. IEEE Trans. Ind. Electron. 1999, 35, 1108–1117. [Google Scholar]

- Park, S.; Jahns, T. Flexible dv/dt and di/dt control method for insulated gate power switches. IEEE Trans. Ind. Appl. 2003, 39, 657–664. [Google Scholar] [CrossRef] [Green Version]

- Palmer, P.; Rajamani, H. Active Voltage control of IGBTs for high power applications. IEEE Trans. Power Electron. 2004, 19, 894–901. [Google Scholar] [CrossRef] [Green Version]

- Dulau, L.; Pontarollo, S.; Boimond, A.; Garnier, J.F.; Giraudo, N.; Terrasse, O. A New Gate Driver Integrated Circuit for IGBT Devices with Advanced Protections. IEEE Trans. Power Electron. 2006, 21, 38–44. [Google Scholar] [CrossRef]

- Idir, N.; Bausiere, R.; Franchaud, J.J. Active gate voltage control of turn-on di/dt and turn-on dv/dt in insulated gate transistors. IEEE Trans. Power Electron. 2006, 21, 849–855. [Google Scholar] [CrossRef]

- Bryant, A.; Wang, Y.; Finney, S.; Lim, T.; Palmer, P. Numerical optimization of an active voltage controller for high-power IGBT converters. IEEE Trans. Power Electron. 2007, 22, 374–383. [Google Scholar] [CrossRef]

- Grbovic, P. An IGBT gate driver for feed-forward control of turn-on losses and reverse recovery current. IEEE Trans. Power Electron. 2008, 23, 643–652. [Google Scholar] [CrossRef]

- Wang, Y.; Palmer, P.; Bryant, A.; Finney, S.; Abu-Khaizaran, M.; Li, G. An analysis of high-power IGBT switching under cascade active voltage control. IEEE Trans. Ind. Appl. 2009, 45, 861–870. [Google Scholar] [CrossRef]

- Grbovi, P.; Gruson, F.; Idir, N.; le Moigne, P. Turn-on performance of reverse blocking IGBT (RB IGBT) and optimization using advanced gate driver. IEEE Trans. Power Electron. 2010, 25, 970–980. [Google Scholar] [CrossRef]

- Chen, L.; Ge, B.; Peng, F.Z. Modeling and analysis of closed-loop gate drive. In Proceedings of the Applied Power Electronics Conference and Exposition, Palm Springs, CA, USA, 21–25 February 2010; pp. 1124–1130. [Google Scholar]

- Lobsiger, Y.; Kolar, J.W. Closed-loop IGBT gate drive featuring highly dynamic di/dt and dv/dt control. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 4754–4761. [Google Scholar]

- Fink, K.; Bernet, S. Advanced gate drive unit with closed-looped di/dt control. IEEE Trans. Power Electron. 2013, 28, 2587–2595. [Google Scholar] [CrossRef]

- Dang, L.; Kuhn, H.; Mertens, A. Digital adaptive driving strategies for high-voltage IGBTs. IEEE Trans. Ind. Appl. 2013, 49, 1628–1636. [Google Scholar] [CrossRef]

- Michel, L.; Boucher, X.; Cheriti, A.; Sicard, P.; Sirois, F. FPGA implementation of an optimal IGBT gate driver based on Posicast control. IEEE Trans. Power Electron. 2013, 28, 2569–2575. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.; Blalock, B.J. A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules. IEEE Trans. Power Electron. 2014, 29, 3720–3732. [Google Scholar] [CrossRef]

- Lu, T.; Zhao, Z.; Ji, S.; Yu, H.; Yuan, L. Active clamping circuit with status feedback for series-connected HV-IGBTs. IEEE Trans. Ind. Appl. 2014, 50, 3579–3590. [Google Scholar] [CrossRef]

- Zhang, F.; Ren, Y.; Tian, M.F.; Yang, X. A novel active gate drive for HV-IGBTs using feed-forward gate charge control strategy. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 7009–7014. [Google Scholar]

- Shu, L.; Zhang, J.; Peng, F.; Chen, Z. Active Current Source IGBT Gate Drive with Closed-Loop di/dt and dv/dt Control. IEEE Trans. Power Electron. 2017, 32, 3787–3796. [Google Scholar] [CrossRef]

- Choi, U.M.; Blaabjerg, F.; Lee, K.B. Study and handling methods of power IGBT module failures in power electronic converter systems. IEEE Trans. Power Electron. 2015, 30, 2517–2533. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, D.; Bryant, A.; Mawby, P.; Ran, L.; Tavner, P. Condition monitoring for device reliability in power electronic converters: A review. IEEE Trans. Power Electron. 2010, 25, 2734–2752. [Google Scholar] [CrossRef]

- Xu, Z.; Li, M.; Wang, F.; Liang, Z. Investigation of Si IGBT operation at 200 °C for traction applications. IEEE Trans. Power Electron. 2013, 28, 2604–2615. [Google Scholar] [CrossRef]

- Rashid, M.H. Power Electronics Handbook: Devices, Circuits and Applications Handbook, 3rd ed.; Elsevier Inc.: New York, NY, USA, 2011. [Google Scholar]

- Bahun, I.; Sunde, V.; Jakopovic, Z. Estimation of Insulated-gate Bipolar Transistor Operating Temperature: Simulation and Experiment. J. Power Electron. 2013, 13, 729–736. [Google Scholar] [CrossRef] [Green Version]

- Sheng, H.; Chen, Z.; Wang, F.; Millner, A. Investigation of 1.2 kV SiC MOSFET for high frequency high power applications. In Proceedings of the 2010 Twenty-Fifth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Palm Springs, CA, USA, 2010; pp. 1572–1577. [Google Scholar]

- Blackburn, D.L. Temperature Measurements of Semiconductor Devices—A Review. Semicond. In Proceedings of the Thermal Measurement & Management Symposium, San Jose, CA, USA, 2004; pp. 70–80. [Google Scholar]

- Oswald, N.; Anthony, P.; McNeill, N.; Stark, B.H. An Experimental Investigation of the Tradeoff between Switching Losses and EMI Generation With Hard-Switched All-Si, Si-SiC, and All-SiC Device Combinations. IEEE Trans. Power Electron. 2014, 29, 2393–2407. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbrert, L.M.; Blalock, B.J. Switching performance improvement of IGBT modules using an active gate driver. In Proceedings of the 28th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, March 2013; pp. 1266–1273. [Google Scholar]

- Licitra, C.; Musumeci, S.; Raciti, A.; Galluzzo, A.U.; Letor, R.; Melito, M. A new driving Circuit for IGBT Devices. IEEE Trans. Power Electron. 1995, 10, 373–378. [Google Scholar] [CrossRef]

- Sachdeva, R.; Nowicki, E.P. A novel gate driver circuit for snubber-less, low-noise operation of high power IGBT. In Proceedings of the IEEE Canadian Conference Electrical and Computer Engineering (CCECE), Winnipeg, MB, Canada, 12–15 May 2002; Volume 1, pp. 212–217. [Google Scholar]

- Igarashi, S.; Takizawa, S.; Tabata, M.; Takei, M.; Kuroki, K. An active control gate drive circuit for IGBTs to realize low-noise and snubber-less system. In Proceedings of the IEEE International Symposium on Power Semicond. Devices IC’s, Weimar, Germany, 26–29 May 1997; pp. 69–72. [Google Scholar]

- Bryant, A.; Lu, L.; Santi, E.; Hudgins, J.; Palmer, P. Modeling of IGBT resistive and inductive turn-on behavior. IEEE Trans. Ind. Appl. 2008, 44, 904–914. [Google Scholar] [CrossRef]

- Trivedi, M.; Shenai, K. Modeling the turn-off of IGBT’s in hard- and soft-switching applications. IEEE Trans. Electron. Devices 1997, 44, 887–893. [Google Scholar] [CrossRef]

- Lobsiger, Y. Closed-Loop IGBT Gate Drive and Current Balancing Concepts. Ph.D. Dissertation, Department of Information Technology and Electrical Engineering, Zürich, Switzerland, 2014. [Google Scholar]

- Yang, X.; Yuan, Y.; Palmer, P.R. Shaping High-Power IGBT Switching Transitions by Active Voltage Control for Reduced EMI Generation. IEEE Trans. Ind. Appl. 2015, 51, 1669–1677. [Google Scholar] [CrossRef]

- Groeger, J.; Schindler, A.; Wicht, B.; Norling, K. Optimized dv/dt, di/dt Sensing for a Digitally Controlled Slope Shaping Gate Driver. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 3564–3569. [Google Scholar]

- Zhou, S.; Zhou, L.; Sun, P. Monitoring potential defects in an IGBT module based on dynamic changes of the gate current. IEEE Trans. Power Electron. 2013, 28, 1479–1487. [Google Scholar] [CrossRef]

- Ghorbani, H.; Sala, V.; Paredes, A.; Romeral, L. A novel EMI reduction design technique in IGBT gate driver for turn-on switching mode. In Proceedings of the 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–7. [Google Scholar]

- Paredes, A.; Sala, V.; Ghorbani, H.; Romeral, L. A Novel Active Gate Driver for Improving SiC MOSFET Switching Trajectory. IEEE Trans. Ind. Electron. 2017, 64, 9032–9042. [Google Scholar] [Green Version]

- Ghorbani, H.; Sala, V.; Paredes, A.; Romeral, L. Embedding a feedforward controller into the IGBT gate driver for turn-on transient improvement. Microelectron. Reliab. 2018, 80, 230–240. [Google Scholar] [CrossRef]

| Ki Coefficient | Intermediate Gate-Voltage Levels | diC/dt (pu.) | Over Current (pu.) |

|---|---|---|---|

| Ki1 | 6.8 | 0.54 | 0.77 |

| Ki2 | 7.6 | 0.58 | 0.8 |

| Ki3 | 8.4 | 0.65 | 0.85 |

| Ki4 | 9 | 0.69 | 0.9 |

| Original GD | - | 1 | 1 |

| Kv Coefficient | Intermediate Gate-Voltage Levels | dvCE/dt (pu.) | V-Overshoot (pu.) |

|---|---|---|---|

| Kv1 | 3.5 | 0.64 | 0.886 |

| Kv2 | 1.5 | 0.72 | 0.911 |

| Kv3 | -1 | 0.79 | 0.93 |

| Kv4 | -4 | 0.93 | 0.95 |

| Original GD | - | 1 | 1 |

| Gate Drivers | Overshoot Value in IC (A) | Overshoot Value in VCE (V) | Eon (µJ) | Eoff (µJ) |

|---|---|---|---|---|

| Original GD | 8 | 790 | 397 | 716 |

| New GD | 6.1 | 700 | 465 | 931 |

| CGD | 6.1 | 700 | 512 | 986 |

| Drivers | Cost (pu) | Efficiency | EMI Reduction | Overshoot Reduction |

|---|---|---|---|---|

| GD+Snubber | 1 | Medium | High | High |

| Proposed AGD | 1.25 | High | High | High |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ghorbani, H.; Sala, V.; Paredes Camacho, A.; Romeral Martinez, J.L. A Simple Closed-Loop Active Gate Voltage Driver for Controlling diC/dt and dvCE/dt in IGBTs. Electronics 2019, 8, 144. https://doi.org/10.3390/electronics8020144

Ghorbani H, Sala V, Paredes Camacho A, Romeral Martinez JL. A Simple Closed-Loop Active Gate Voltage Driver for Controlling diC/dt and dvCE/dt in IGBTs. Electronics. 2019; 8(2):144. https://doi.org/10.3390/electronics8020144

Chicago/Turabian StyleGhorbani, Hamidreza, Vicent Sala, Alejandro Paredes Camacho, and Jose Luis Romeral Martinez. 2019. "A Simple Closed-Loop Active Gate Voltage Driver for Controlling diC/dt and dvCE/dt in IGBTs" Electronics 8, no. 2: 144. https://doi.org/10.3390/electronics8020144