1. Introduction

The conventional distributed amplifier (DA) has been broadly used for wide-band small-signal applications due to its ability to combine multiple amplifying devices without compromising the gain bandwidth product [

1]. However, its success in power applications has been limited for several major reasons, such as the unequal distribution of output power between active devices, which results in the underutilization of some of the active devices [

2,

3,

4] and the wasted power at the inactive output port that reduces efficiency [

5,

6,

7].

Several alternative topologies have been proposed in the literature to overcome these drawbacks, such as output line tapering [

7] and improved circuit optimisation [

2,

3,

4]. A variation of the DA topology, the dual-fed distributed amplifier, has been proposed in order to harness the power in the backward waves [

5,

6]. The schematic of this topology is shown in

Figure 1b. The working principle of this topology is to use both input ends to inject the input signal using a hybrid and all the available output power from both output ports is withdrawn using another hybrid. The addition of the forward and reverse gains for the splitted input signals results in a 6 dB increase in the overall gain, while the combination of both output ports increases the output power 3 dB. Nonetheless, forward and reverse gains have a different frequency behaviour. While the forward gain of a conventional DA is broadband, the reverse gain is narrowband and, as a consequence, the dual-fed DA frequency response is also narrowband. Some authors have proposed using composite right/left-handed (CRLH) transmission lines to operate at high frequencies [

8]. In this case, the frequency response changes from low-pass to pass-band, but the bandwidth is still limited by the narrowband response of the reverse path. In both scenarios, the frequency limitation of the small-signal response in the reverse path results in a large-signal response also limited in frequency. This opens up the possibilities of improving one of the main drawbacks of distributed amplifiers, which is their large area consumption. This paper proposes effective area reduction techniques using stacked inductors for a dual-fed CMOS distributed power amplifier that does not affect its large signal performance. To our knowledge, the combination of these techniques has not been implemented in previous works.

2. Single-Fed and Dual-Fed DAs

The circuit diagram of a conventional low-pass DA is shown in

Figure 1a. In this topology, as the input signal flows through the gate transmission line, the output currents from each gain stage are added in the drain line. If the losses are not considered, the gain of a DA rises linearly as the number of stages is increased while the bandwidth stays constant. This is due to the fact that the parasitic capacitances of the transistors are assimilated into the gate and drain lines, forming lumped-element T-section constant-k filters, whose cut-off frequency limits the bandwidth of the circuit [

1]. The characteristic impedance (

Z0) and cut-off frequency (

fc) of both transmission lines (TL) are given by:

Since

Z0 and

fc of both lines are identical, their capacitances and inductances should also be equal. As the drain-to-bulk capacitance (

Cdb) of a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is typically lower than its gate-to-source capacitance (

Cgs), a capacitor (

Cd) is included at the drain so both capacitances are equivalent:

When losses are taken into account, the signal at each stage of the DA is attenuated. The main contributors to these losses are finite

Q inductors and the drain-to-source resistance (

rds) in the drain line. Under these conditions, the gain of the DA is typically described as follows:

in which

Ad and

Ag are the attenuation of the drain and gate lines,

gm is the MOSFET transconductance and

N is the total number of stages. In this equation, the following assumptions are considered:

Unilateral MOSFET model (ignores Cgd),

Image impedance matched terminations,

Equal gate and drain phase velocities.

The optimum number of stages that maximises the gain is a function of gate and drain line attenuation. These attenuations are complex functions and depend on the specific MOSFET parameters, as well as on the operating and cut-off frequencies. As the signal travels along the gate line towards the termination, less signal is available for each MOSFET due to the attenuation and, as a consequence, the overall gain decreases resulting in an increased number of stages. The number of stages for this work is chosen as 4.

The required

gm can be found from the low frequency gain of Equation (

5) when the gain, number of stages and drain-line inductance and capacitance are known, as shown in Equation (

6):

Hence, the transistor width-length ratio can be derived from:

where:

W, transistor gate width,

L, transistor gate length,

n, electron mobility,

Cox, gate oxide capacitance per unit area,

VT, threshold voltage,

Vgs, gate-source voltage.

Finally, the device length and width can be found by combining Equation (

7) with the following expression:

Conventional DA designs feature gate and drain transmission lines with low-pass characteristics and equal electrical lengths (

g(

) =

d(

)). As a consequence, the forward gain adopts a wideband nature, in which the corner frequencies of the unit cells are the limiting factor. On the contrary, the reverse gain follows a low-pass behaviour, as seen in

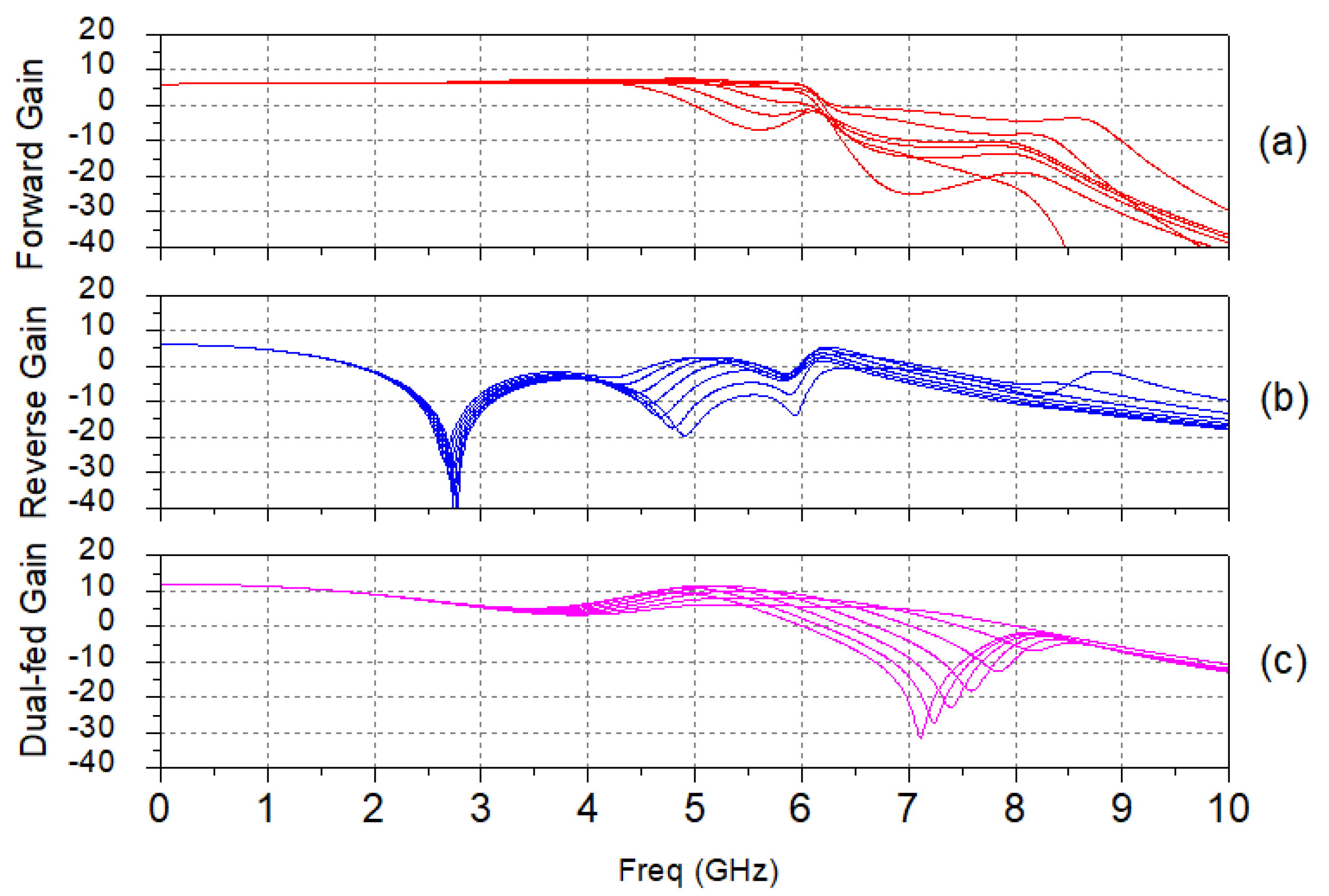

Figure 1c.

The dual-fed configuration shown in

Figure 1b benefits from the forward and reverse gains of the DA, improving both power and gain when its performance is compared to the single-fed topology. This increase will only occur at low frequencies, since the reverse gain has low pass frequency response despite the fact that the forward gain has a broadband response. This can be seen in

Figure 1c, where the small-signal gain of a dual-fed DA is plotted.

3. Area Reduction Techniques

One of the main drawbacks of distributed amplifiers is that they are formed by a noticeable amount of inductors that occupy most of the layout. Hence, it is paramount to analyse the influence of the coils and their placement on the circuit.

The most obvious method is to place the inductors closer together, which results in a more compact layout. However, this causes positive mutual coupling between the inductors when they are coiled in the same direction. Otherwise, the coupling would be negative [

9]. To summarise, in DAs with inductors placed close together, it is crucial to properly orientate the inductors in order to reduce the chip area by minimising the effect of mutual coupling [

10].

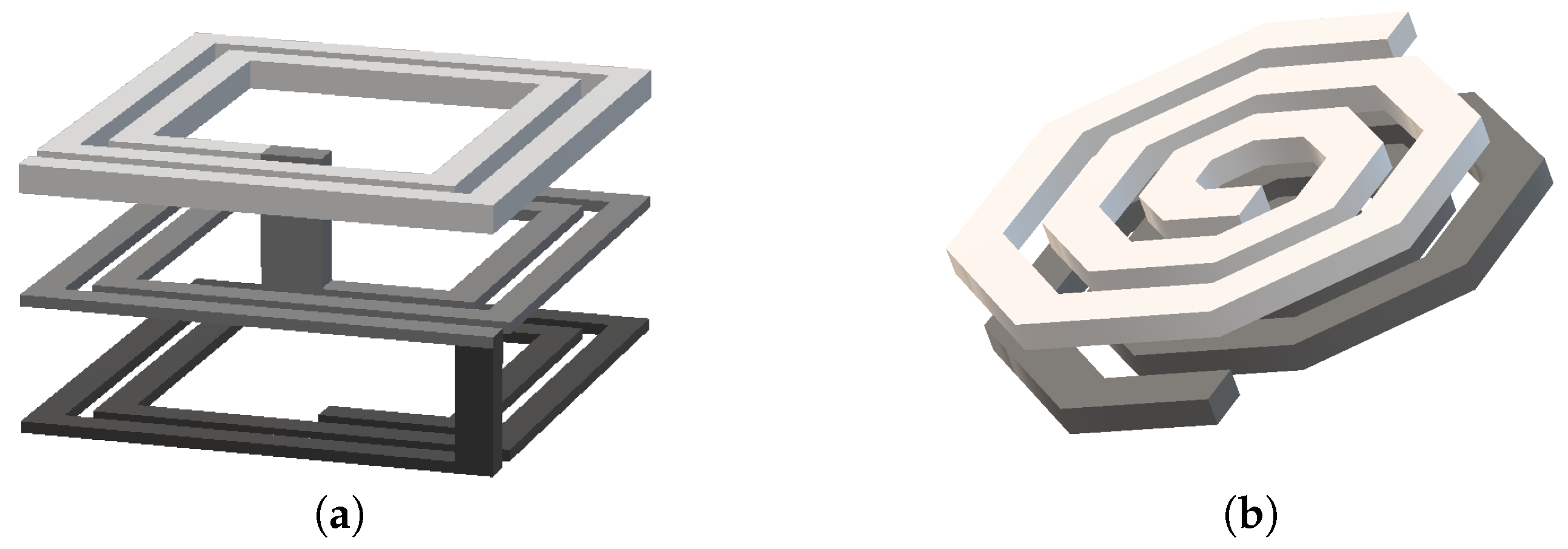

By using multilevel inductors instead of the conventional single-level or planar inductors, area minimization can also be accomplished [

11,

12,

13,

14,

15] (see

Figure 2a). In the multilevel structure, the coil is expanded vertically, while in the single level structure, the inductor is implemented using a single metal layer. Typically, the top layer is used to enhance the quality factor of the coil, since the lower metal layers are thinner. This means that, for a given inductance, the single-level structure shows a much larger area compared to a multilevel one. Using the thinner lower metal layers causes an increase of both the substrate capacitance and metal resistance. However, this disadvantage is compensated by the lower substrate losses due to their reduced area. This way, only a slight degradation of the performance of the stacked inductor is achieved compared to that of the planar spiral inductors.

Both methods show that it is possible to reduce the area without significantly modifying the small-signal circuit response [

9]. However, a further reduction in area can be achieved if some inductors could be placed on top of others, as seen in

Figure 2b, where they should be winded in the opposite direction in order to reduce the mutual inductance and capacitance that appears between them. Even though this method could minimise the area considerably, the increased capacitance between the inductors would lower the cut-off frequency of the artificial transmission lines, reducing the small-signal behaviour of the DA. This can be exploited to make a dual-fed distributed power amplifier due to its low-pass frequency response. The increased capacitance when two of the coils of the gate line (L

G1 and L

G2) are placed one on top of the other is shown highlighted in

Figure 1a.

Figure 3 shows a simulation of the forward and reverse gains when the coupling capacitance between both inductors is varied. As it can be seen, the frequency response of the forward gain is reduced, but the reverse gain remains the same. Therefore, if a dual-fed DA is made based on this topology, its gain will not be affected due to its low-pass frequency response.

4. Experimental Results

In this section, the suggested area reduction techniques will be corroborated. To do so, two four-stage DAs have been designed in a standard 0.35-μm CMOS technology using the component values shown in

Table 1, which were obtained following the procedure explained in

Section 2.

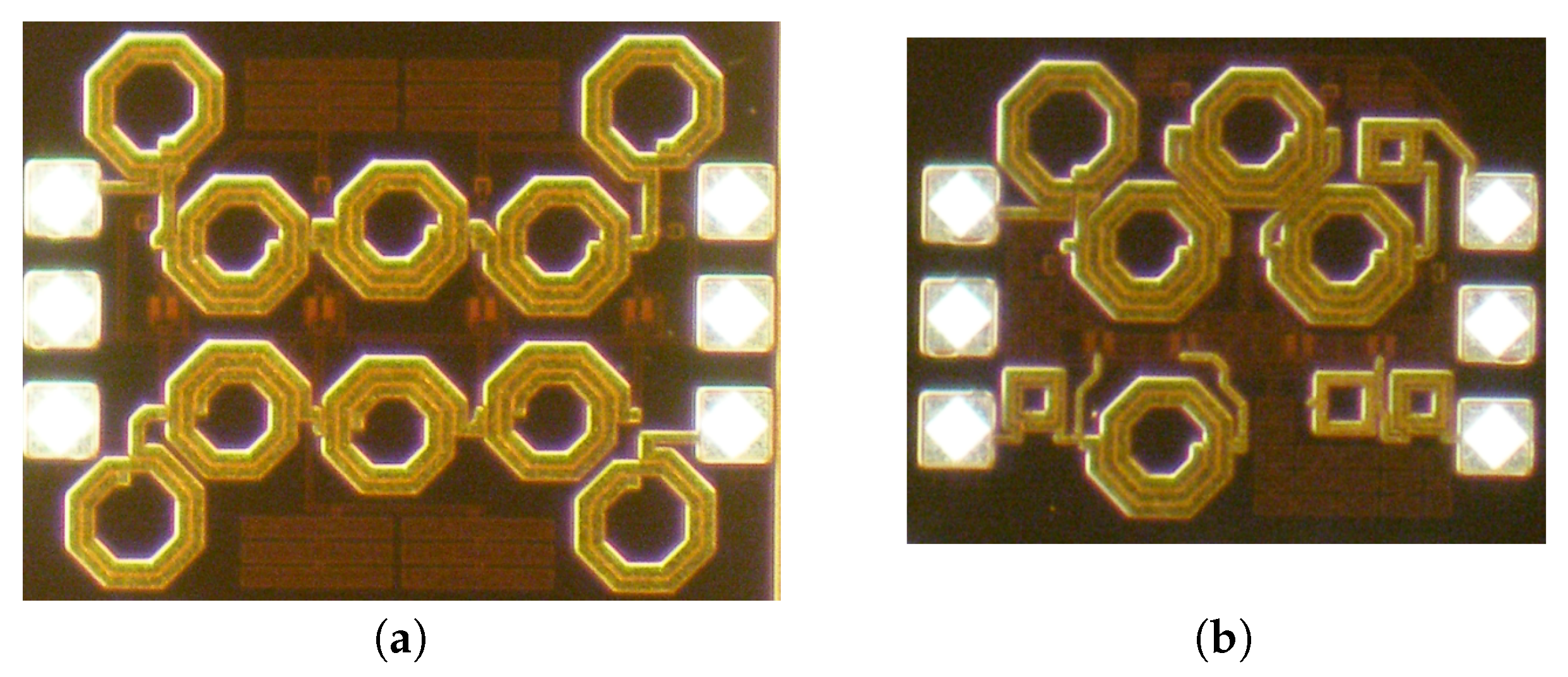

The fabricated circuits are shown in

Figure 4, where DA1 and DA2 correspond to a conventional and a compact design, respectively. DA1 uses conventional spiral inductors without implementing any area reduction technique. The total area of this circuit is 0.742 mm

2 including the pads. On the contrary, DA2 uses the area reduction techniques discussed in the previous section. First, a more compact layout has been obtained by placing the coils close to each other. To avoid the effect of the mutual coupling between the inductors, the coils have been oriented in the opposite direction. Additionally, multilevel inductors have been used on the gate line (L

G3, (L

G/2)

R and (L

G/2)

L). Finally, two of the spiral inductors of the gate line (L

G1 and L

G2) have been placed one on top of the other (stacked) to share the same area. This circuit still uses conventional inductors in the drain line since the multilevel inductors cannot withstand the current going through this path. However, (L

D/2)

R has been implemented using a multilevel coil given that the current flowing through this inductor is lower since the circuit is biased using Port 3. By applying these modifications, the compact design occupies an area of 0.503 mm

2, which results in a 32% area reduction.

Measurements were performed with on-wafer probing with two bias tees connected at the input and output ports. To implement the dual-fed versions, a power divider and combiner were included externally to the single-fed prototypes.

The measured forward and reverse small-signal gains are presented in

Figure 5a. The experimental results were obtained using the same DC bias conditions: 3 V on the drains and 0.8 V on the gates. As expected, the forward gain of DA2 is reduced compared to that of DA1 due to the coupling capacitance between the inductors placed one above the other. However, the reverse gains are very similar.

The relation between the measured output power and the input power for both configurations at 1 GHz is shown in

Figure 5b. Note that, to compare the performance, the input power level between the dual and the single-fed prototypes must be shifted 3 dB. As explained in

Section 1, in the dual-fed configuration a 3 dB output power increment and a 6 dB gain boost is achieved when compared to the single-fed DA.

Figure 5c depicts the measured results of power-added efficiency (PAE) as a function of the input power at 1 GHz. The obtained values are close to the theoretical limit of 40%, which meet those obtained in previous works [

8,

16]. The PAE for the dual-fed configuration for a 14 dBm input power is shown in

Figure 5d as a function of frequency. As expected, the low-pass frequency response of conventional DAs results in a PAE decrease as the frequency increases. Note that the bandwidth for both DAs is similar, provided that the frequency response of the dual-fed DA is limited by the reverse gain, which is similar for both circuits.

5. Conclusions

In this paper, several area reduction approaches have been implemented in a dual-fed DA. The first of them consists of placing the inductors closer together, considering that it is essential to properly orientate the coils in order to minimise the mutual coupling issue. The other techniques deal with the area occupied by the inductors, by using multilevel inductors and placing inductors one on top of the other.

The application of these techniques achieves a 32% area reduction, where the variation of the circuit performance is negligible. The large signal parameters, output power and PAE, remain practically the same. Even though there is a discrepancy between the small signal parameters of both versions, they are almost identical at the operating frequency, which is 1 GHz. It should be noted that the area of the circuit could be further minimised as the number of stages increases.