A 0.49–4.34 μW LC-SAR Hybrid ADC with a 10.85-Bit ENOB and 20 KS/s Bandwidth

Abstract

:1. Introduction

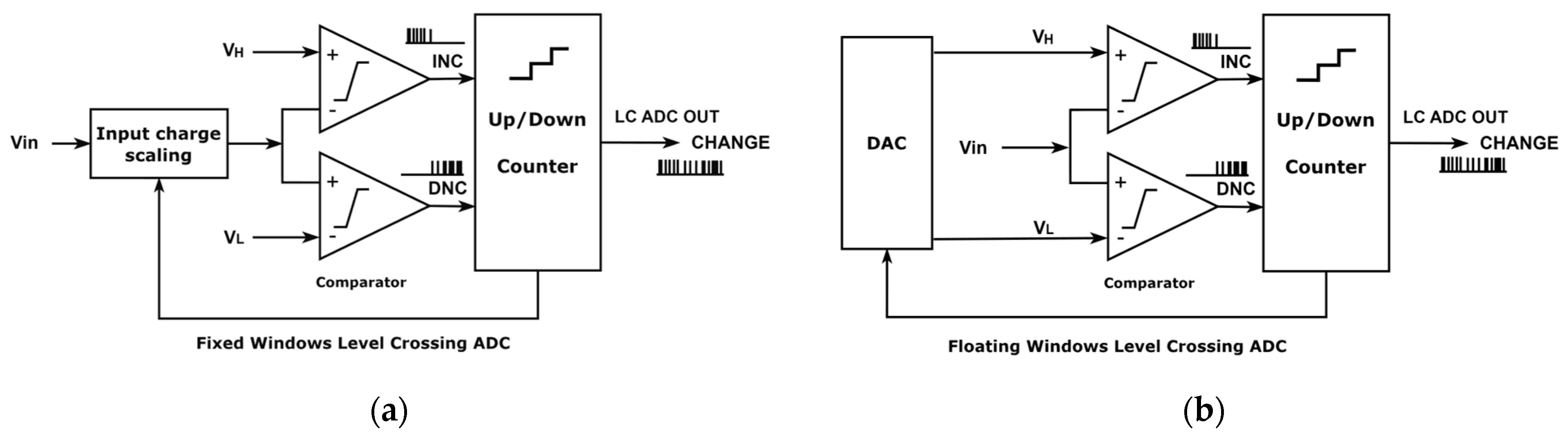

2. Proposed LC-SAR Hybrid ADC Architecture

2.1. Motivation

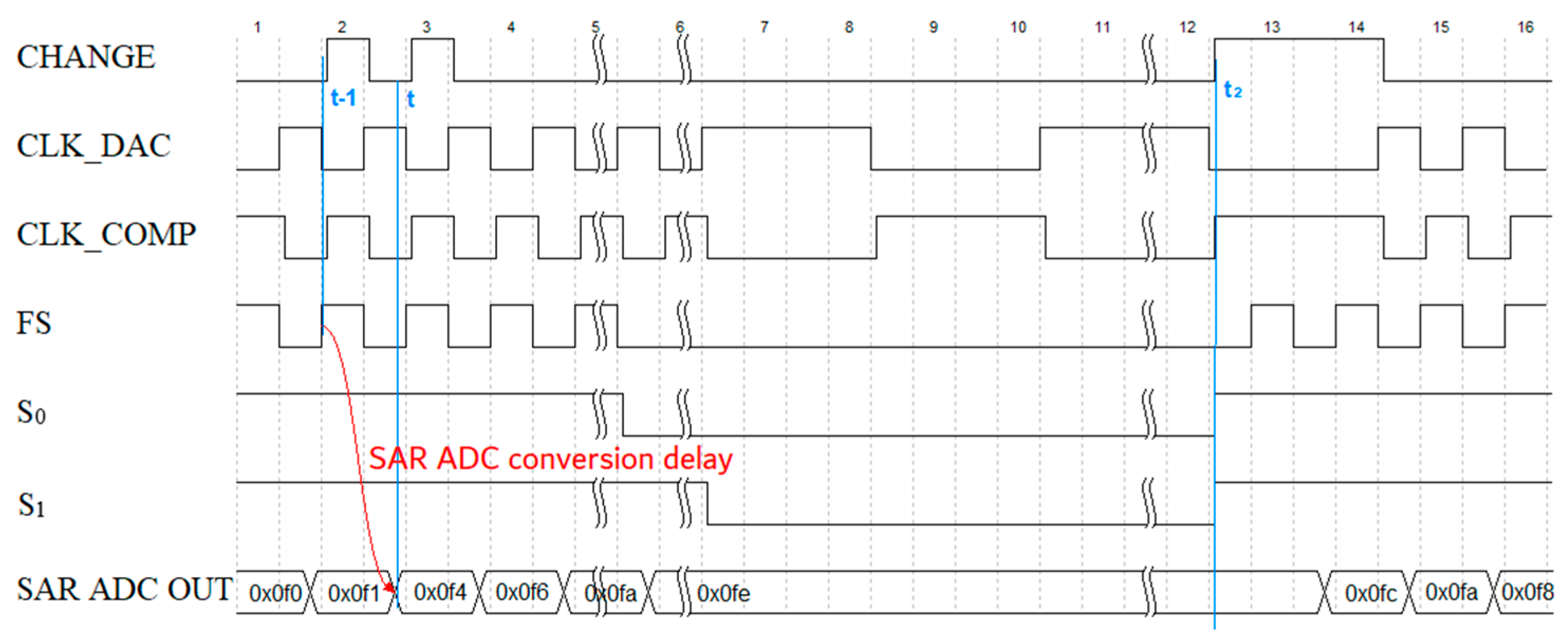

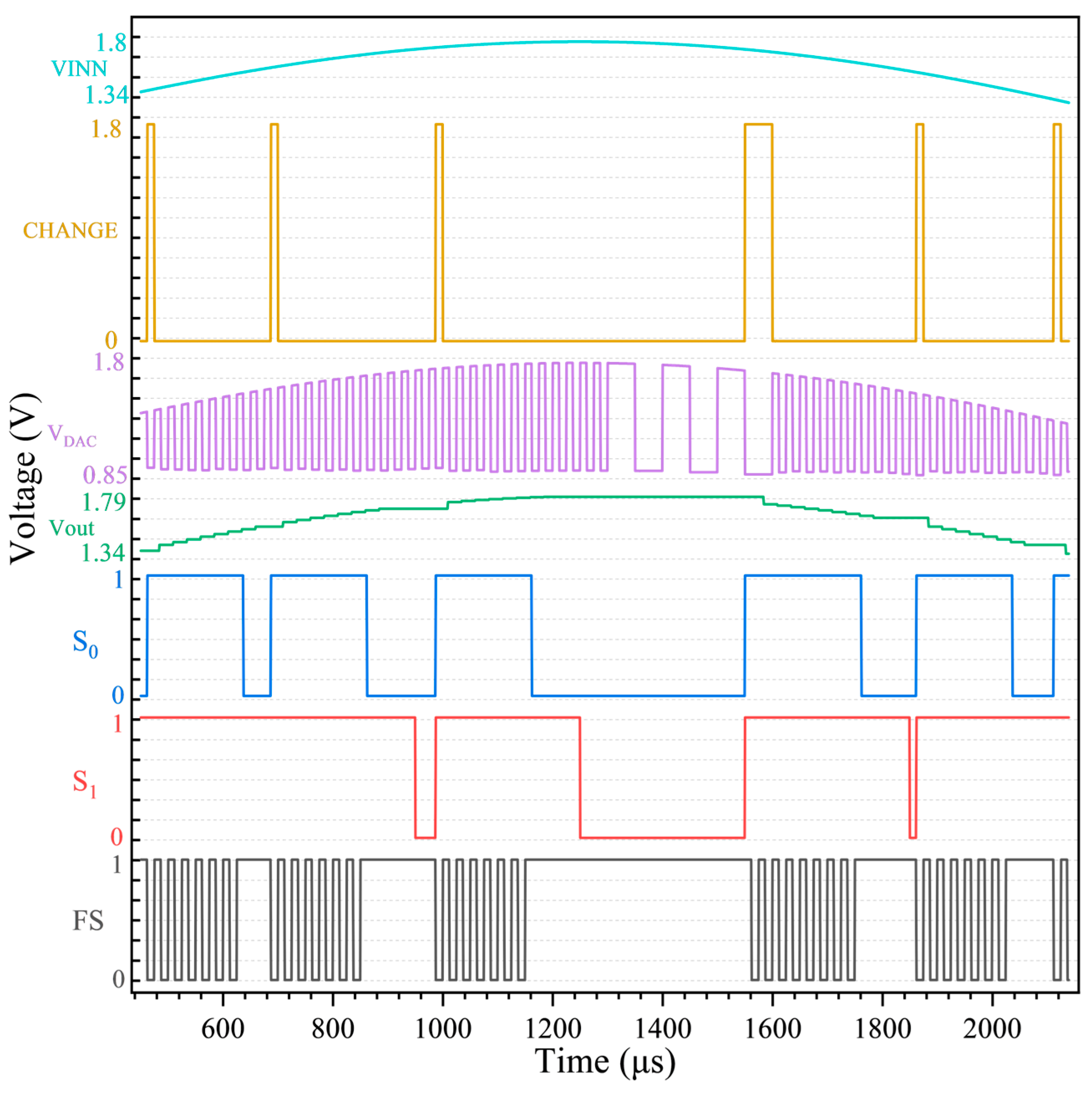

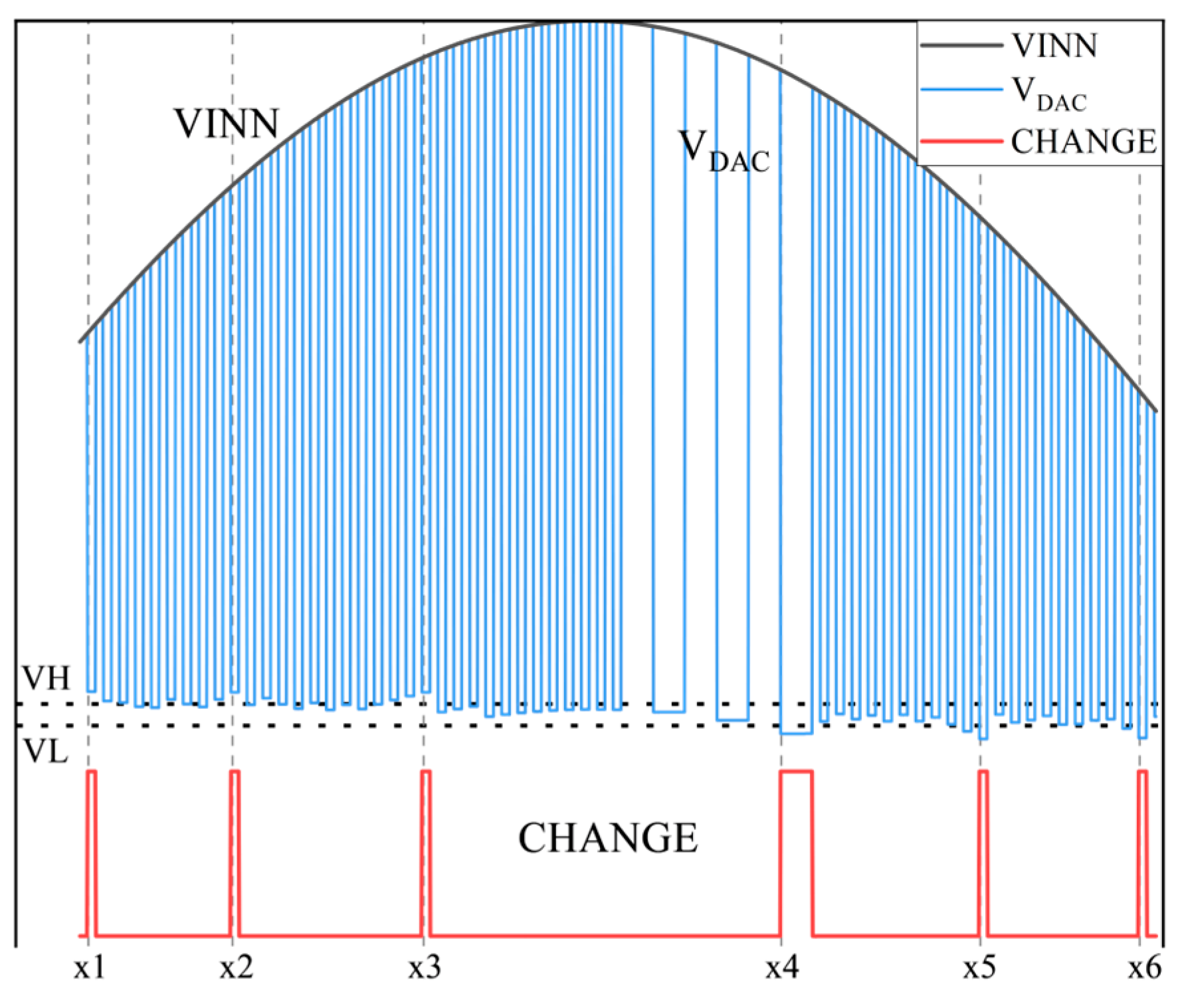

2.2. System Architecture and Operation

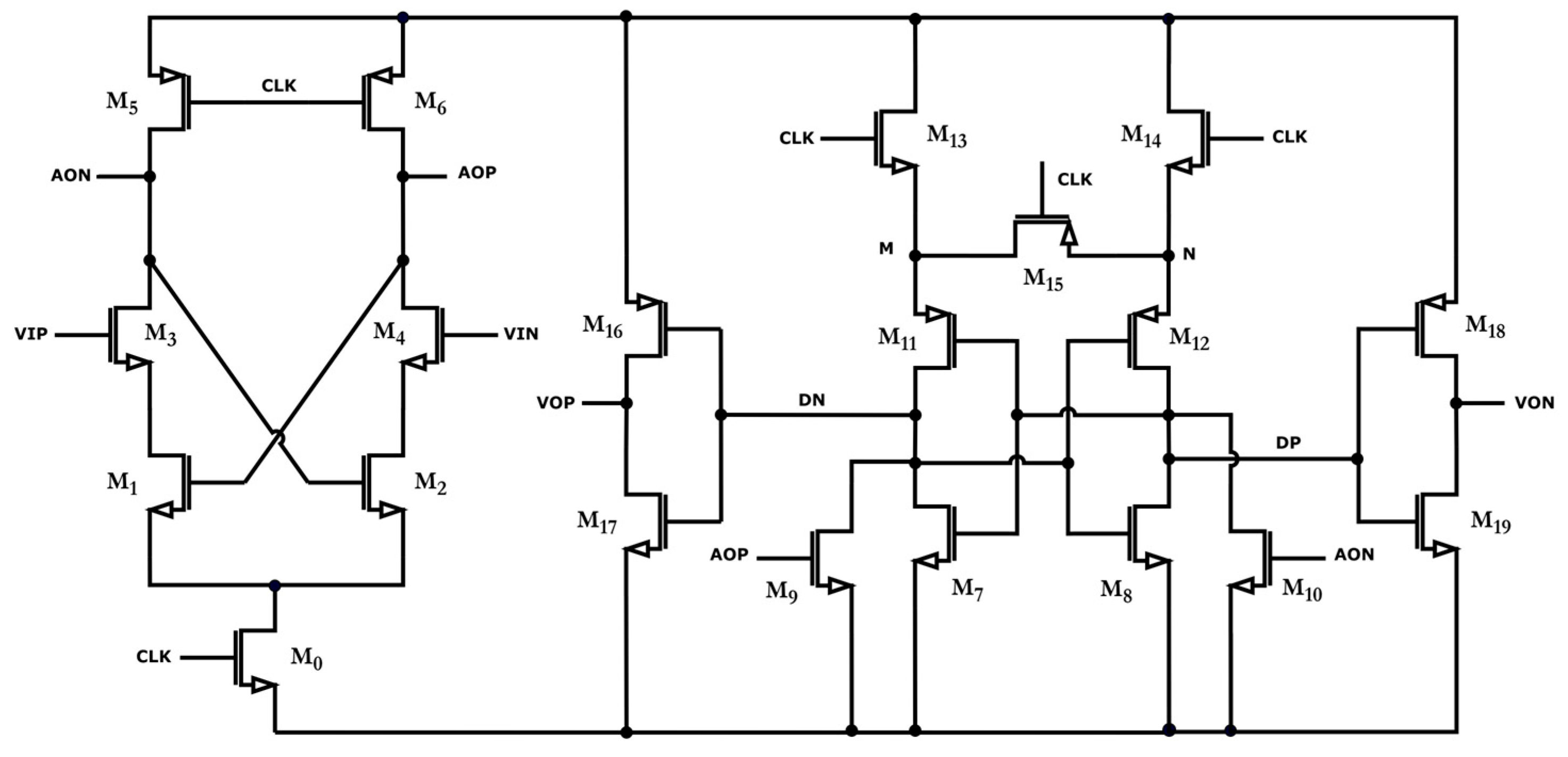

3. LC-SAR Hybrid ADC Circuit Implementation

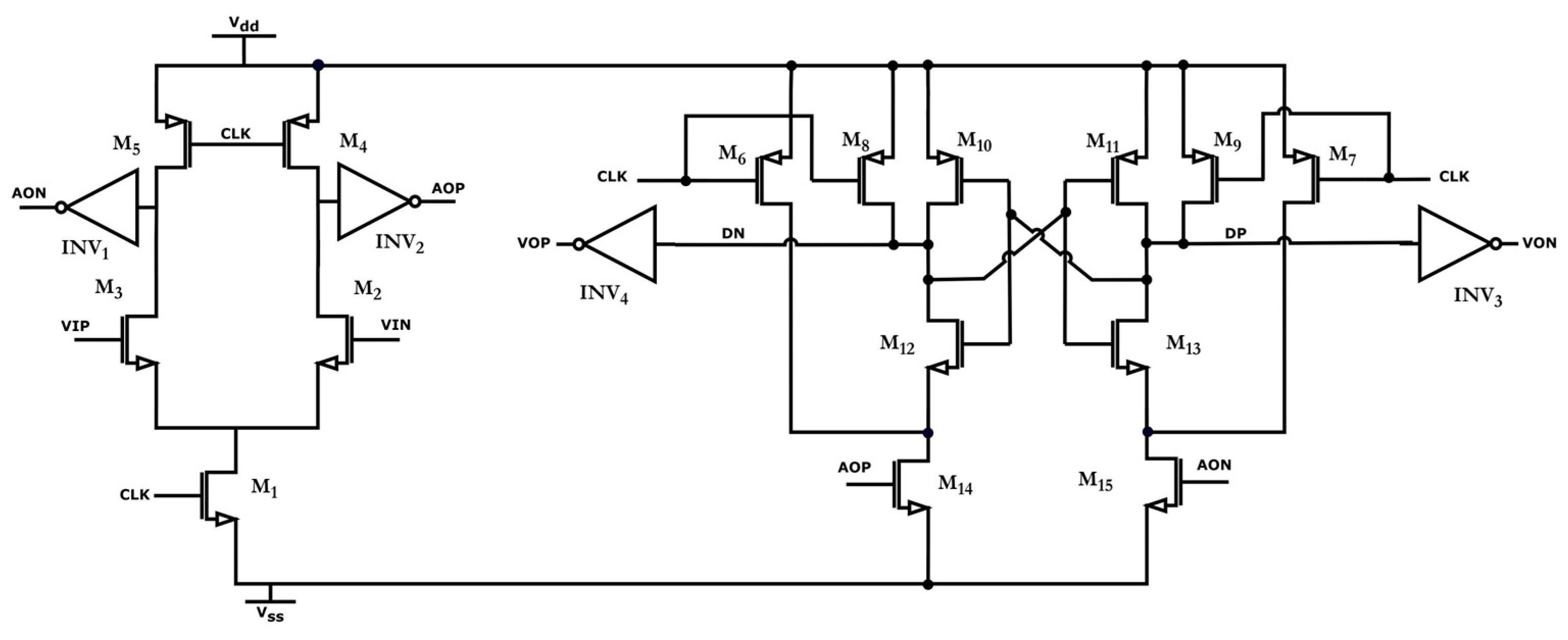

3.1. LC ADC

3.2. CLK_GEN

- A maximum operating frequency of 40 kHz;

- When S0 = 1 and S1 = 0, the LC ADC operates at one-fourth of the original normal operating frequency (10 kHz).

- A sampling frequency of 40 kHz;

- Stops working when S0 = 0 and S1 = 1, i.e., FS no longer outputs pulses;

- The SAR ADC requires 13 clock cycles to complete a conversion.

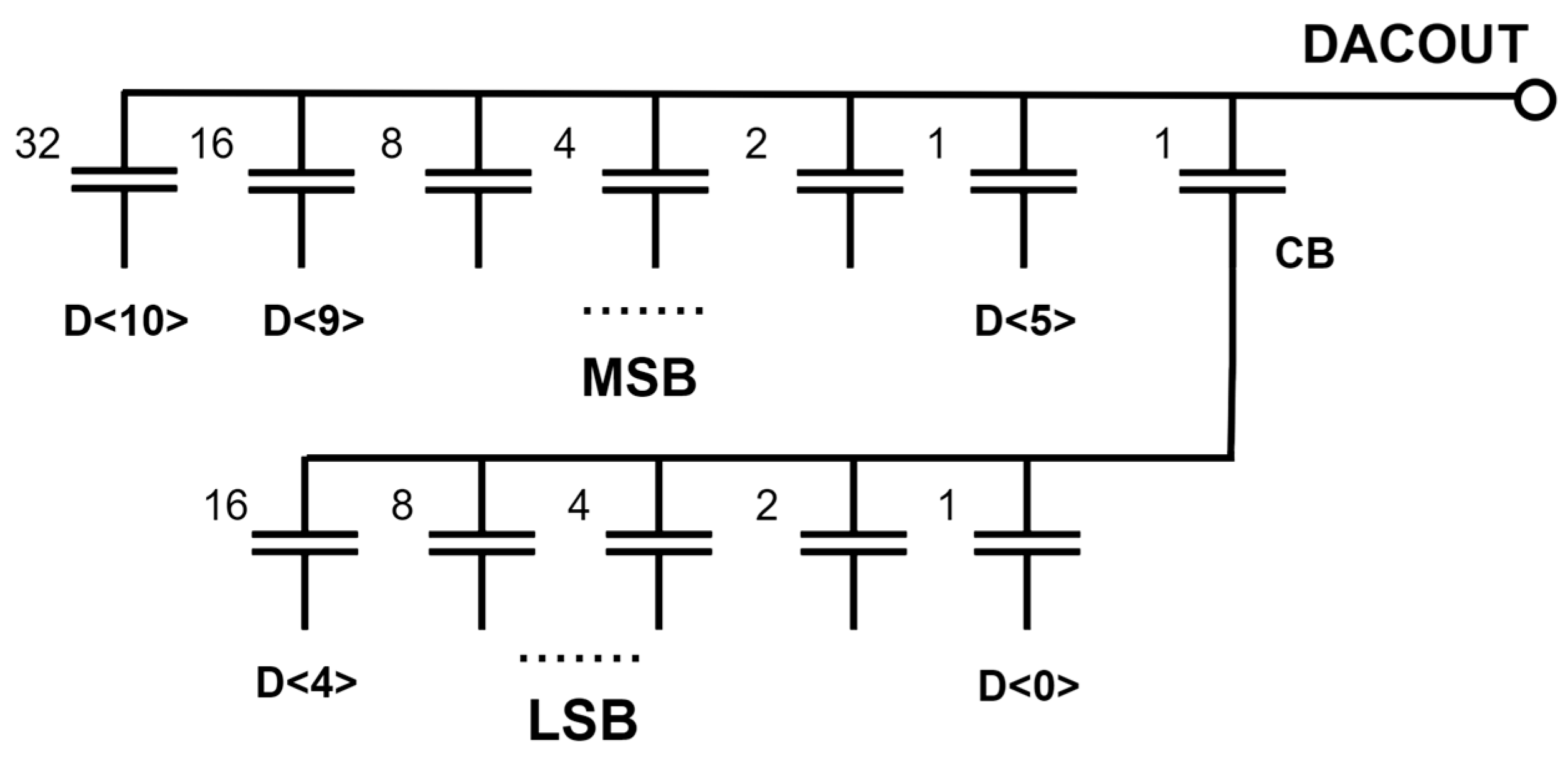

3.3. SAR ADC

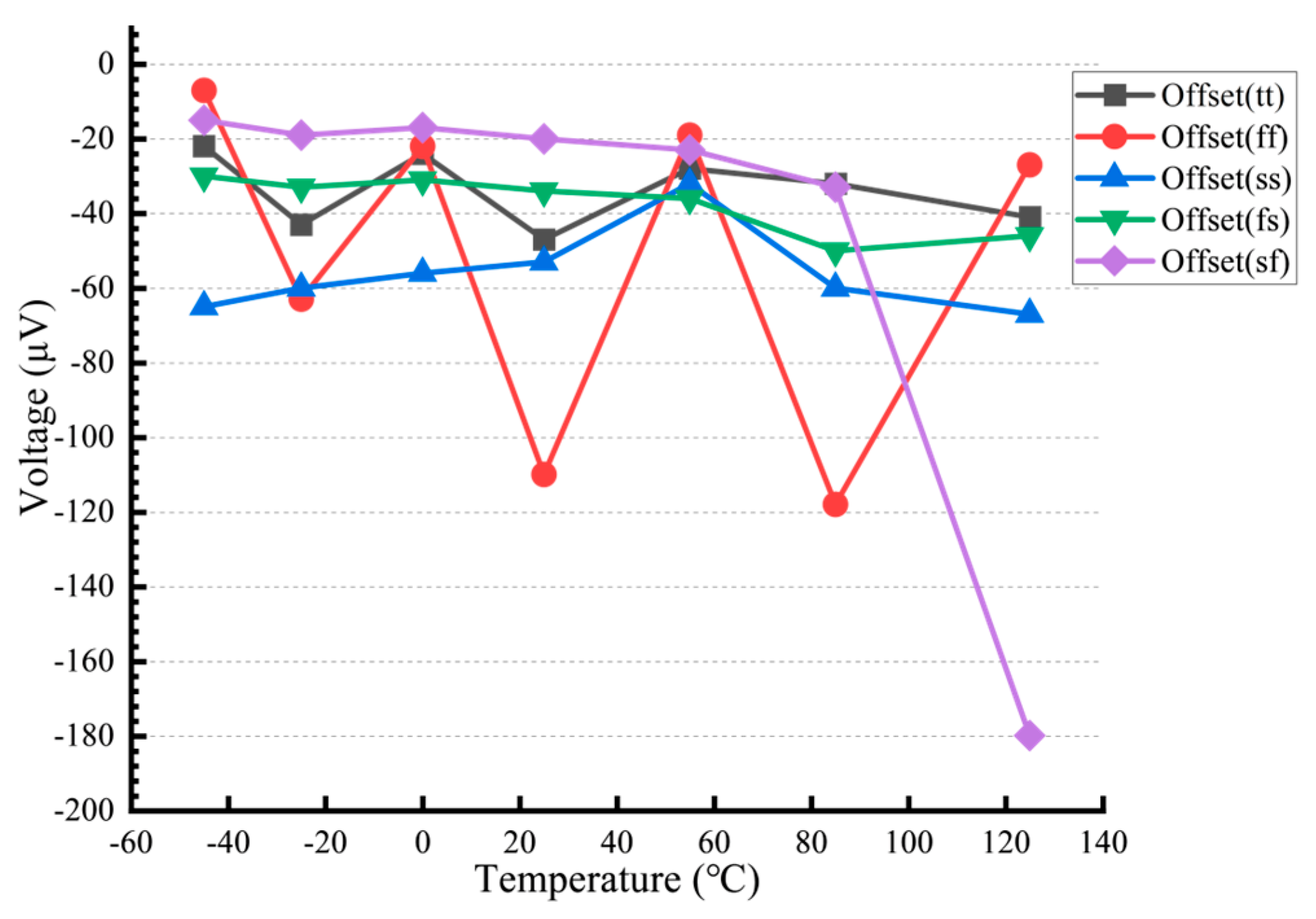

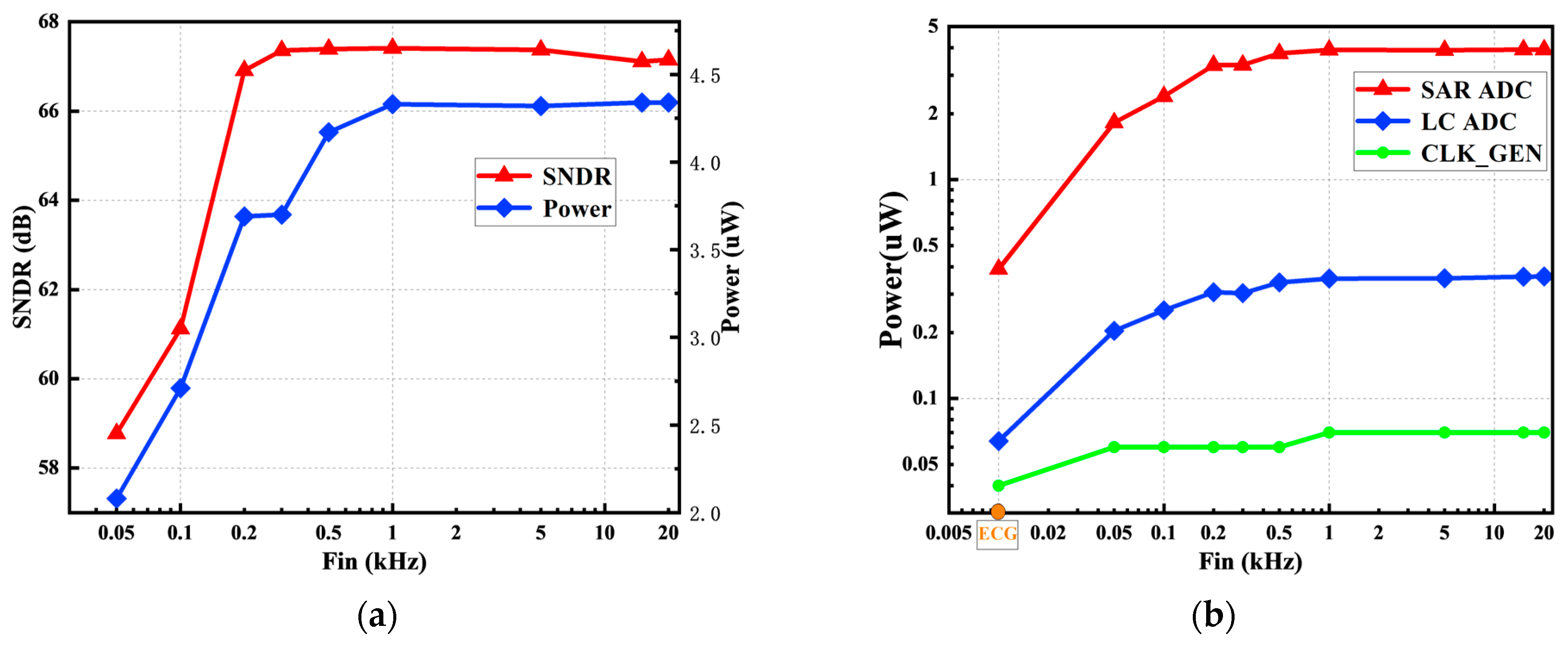

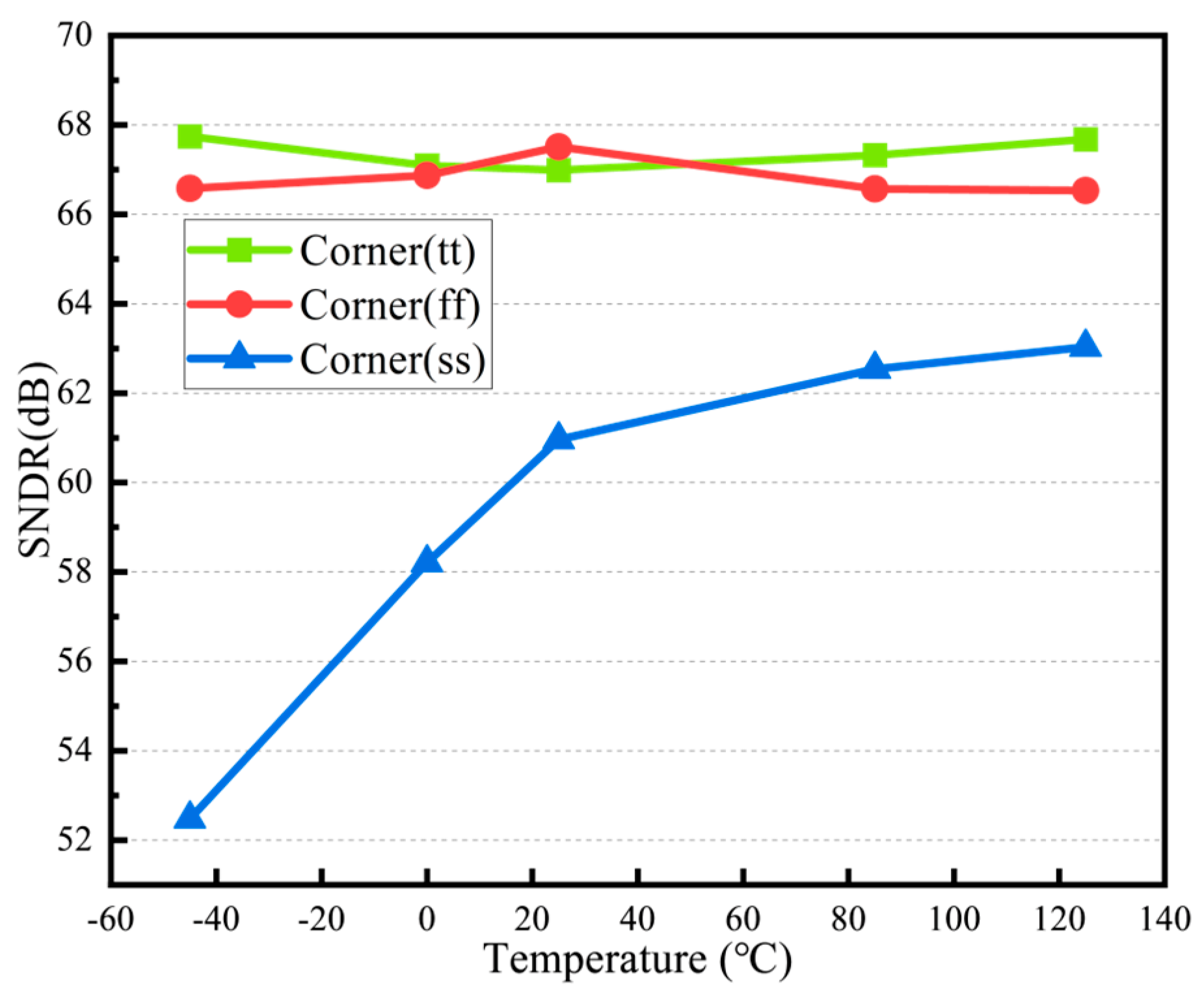

4. Simulation Results and Analysis

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- World Health Organization. Available online: https://www.who.int/health-topics/cardiovascular-diseases/ (accessed on 11 March 2024).

- Zhang, Y.; Xu, X.; Yu, Z. A Low-Power SAR ADC with Multi-mode Switching Scheme. In Proceedings of the 2022 10th International Symposium on Next-Generation Electronics (ISNE), Wuxi, China, 12–14 May 2023; pp. 1–3. [Google Scholar] [CrossRef]

- Van Assche, J.; Gielen, G. Power Efficiency Comparison of Event-Driven and Fixed-Rate Signal Conversion and Compression for Biomedical Applications. IEEE Trans. Biomed. Circuits Syst. 2020, 14, 746–756. [Google Scholar] [CrossRef] [PubMed]

- Hou, Y.; Yousef, K.; Atef, M.; Wang, G.; Lian, Y. A 1-to-1-kHz, 4.2-to-544-nW, Multi-Level Comparator Based Level-Crossing ADC for IoT Applications. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1390–1394. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, H.; Zhang, Y.; Shen, L.; Ru, J.; Fan, H.; Tan, Z.; Wang, Y.; Ye, L.; Huang, R. A Software-Defined Always-On System With 57–75-nW Wake-Up Function Using Asynchronous Clock-Free Pipelined Event-Driven Architecture and Time-Shielding Level-Crossing ADC. IEEE J. Solid-State Circuits 2021, 56, 2804–2816. [Google Scholar] [CrossRef]

- Zhang, X.; Lian, Y. A 300-mV 220-nW Event-Driven ADC With Real-Time QRS Detection for Wearable ECG Sensors. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 834–843. [Google Scholar] [CrossRef]

- Polineni, S.; Gupta, A.K. 8-bit Nano watt level crossing ADC for bio-medical application. In Proceedings of the 2015 International Conference on Computer, Communication and Control (IC4), Indore, India, 10–12 September 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Weltin-Wu, C.; Tsividis, Y. An Event-driven Clockless Level-Crossing ADC With Signal-Dependent Adaptive Resolution. IEEE J. Solid-State Circuits 2013, 48, 2180–2190. [Google Scholar] [CrossRef]

- Van Assche, J.; Gielen, G. A 10.4-ENOB 0.92–5.38 μW Event-Driven Level-Crossing ADC with Adaptive Clocking for Time-Sparse Edge Applications. In Proceedings of the ESSCIRC 2022—IEEE 48th European Solid State Circuits Conference (ESSCIRC), Milan, Italy, 19–22 September 2022; pp. 261–264. [Google Scholar] [CrossRef]

- Li, M.; Song, S.; Qu, W.; Ye, L.; Zhao, M.; Tan, Z. A 1.2V 62.2dB SNDR SAR-Assisted Event-Driven Clockless Level-Crossing ADC for Time-Sparse Signal Acquisition. In Proceedings of the ESSCIRC 2023—IEEE 49th European Solid State Circuits Conference (ESSCIRC), Lisbon, Portugal, 11–14 September 2023; pp. 289–292. [Google Scholar] [CrossRef]

- Zhang, Z.; Yu, Q.; Li, J.; Wang, X.-Z.; Ning, N. A 12-Bit Dynamic Tracking Algorithm-Based SAR ADC With Real-Time QRS Detection. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 2923–2933. [Google Scholar] [CrossRef]

- Wang, H.; Schembari, F.; Staszewski, R.B. An Event-Driven Quasi-Level-Crossing Delta Modulator Based on Residue Quantization. IEEE J. Solid-State Circuits 2020, 55, 298–311. [Google Scholar] [CrossRef]

- Wang, Z.; Ye, L.; Zhang, H.; Ru, J.; Fan, H.; Wang, Y.; Huang, R. 20.2 A 57nW Software-Defined Always-On Wake-Up Chip for IoT Devices with Asynchronous Pipelined Event-Driven Architecture and Time-Shielding Level-Crossing ADC. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 314–316. [Google Scholar] [CrossRef]

- Rovere, G.; Fateh, S.; Benini, L. A 2.2-μW Cognitive Always-On Wake-Up Circuit for Event-Driven Duty-Cycling of IoT Sensor Nodes. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 543–554. [Google Scholar] [CrossRef]

- Rovere, G.; Fateh, S.; Benini, L. A 2.1 μW event-driven wake-up circuit based on a level-crossing ADC for pattern recognition in healthcare. In Proceedings of the 2017 IEEE Biomedical Circuits and Systems Conference (BioCAS), Turin, Italy, 19–21 October 2017; pp. 1–4. [Google Scholar] [CrossRef]

- Kubendran, R.; Park, J.; Sharma, R.; Kim, C.; Joshi, S.; Cauwenberghs, G.; Ha, S. A 4.2-pJ/Conv 10-b Asynchronous ADC with Hybrid Two-Tier Level-Crossing Event Coding. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Ogweno, A.; Degenaar, P.; Khomenko, V.; Yakovlev, A. A fixed window Level Crossing ADC with activity dependent power dissipation. In Proceedings of the 2016 14th IEEE International New Circuits and Systems Conference (NEWCAS), Vancouver, BC, Canada, 26–29 June 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Ravanshad, N.; Rezaee-Dehsorkh, H.; Lotfi, R.; Lian, Y. A Level-Crossing Based QRS-Detection Algorithm for Wearable ECG Sensors. IEEE J. Biomed. Health Inform. 2014, 18, 183–192. [Google Scholar] [CrossRef] [PubMed]

- Sirimasakul, S.; Thanachayanont, A. A Logarithmic Level-Crossing ADC with Fixed Comparison Window. In Proceedings of the 2022 19th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), Prachuap Khiri Khan, Thailand, 24–27 May 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Sirimasakul, S.; Thanachayanont, A. A logarithmic level-crossing ADC. In Proceedings of the 2017 14th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), Phuket, Thailand, 27–30 June 2017; pp. 576–579. [Google Scholar] [CrossRef]

- Siddharth, R.K.; Kumar, Y.B.N.; Vasantha, M.H.; Bonizzoni, E. A Low-Power Auxiliary Circuit for Level-Crossing ADCs in IoT-Sensor Applications. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Zhuang, H.; Guo, W.; Liu, J.; Tang, H.; Zhu, Z.; Chen, L.; Sun, N. A Second-Order Noise-Shaping SAR ADC With Passive Integrator and Tri-Level Voting. IEEE J. Solid-State Circuits 2019, 54, 1636–1647. [Google Scholar] [CrossRef]

- Empirical Rule: Understanding the Three Sigma Rule in Statistics. Available online: https://decodingdatascience.com/empirical-rule-understanding-the-three-sigma-rule-in-statistics/ (accessed on 11 March 2024).

- Allen, P.E.; Holberg, D.R. CMOS Analog Circuit Design; Oxford Press: New York, NY, USA, 2002; pp. 635–641. [Google Scholar]

- Tong, X.; Yang, Y.; Zhu, Z.; Liu, L. Mismatch analysisi and high-level modeling of passive components in successive approximation A/D converters. J. Xidian Univ. 2011, 38, 123–129. [Google Scholar] [CrossRef]

- Saeed, M.; Wang, Q.; Märtens, O.; Larras, B.; Frappé, A.; Cardiff, B.; John, D. Evaluation of Level-Crossing ADCs for Event-Driven ECG Classification. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 1129–1139. [Google Scholar] [CrossRef] [PubMed]

| Mean(F) | 20.2825 f | 112.201 f | 429.389 f | 1.28815 p | 1.71752 p |

| Std Dev(F) | 91.3447 a | 202.147 a | 386.818 a | 669.989 a | 773.647 a |

| ε | 0.45036% | 0.180165% | 0.0900856% | 0.052011% | 0.045044% |

| Parameter | [7] | [9] * | [11] * | [10] * | [17] | This Work |

|---|---|---|---|---|---|---|

| Topology | LC | LC | SAR | LC-SAR | LC | LC-SAR |

| Technology (nm) | 180 | 40 | 130 | 55 | 350 | 180 |

| Active Area (mm2) | - | 0.012 | 0.03 | 0.063 | - | 1.167 |

| Need External CLK | NO | YES | YES | NO | YES | YES |

| Supply Voltage (V) | 0.8 | 0.5/1 | 0.6 | 1.2 | 1/2.5 | 1/1.8 |

| Quantizer Resolution (bit) | 8 | 8 | 12 | 4 + 4 | - | 6 + 11 |

| Bandwidth (Hz) | 5~3.3k | 15k | 5k | 25k | 20k | 20k |

| Power (μW) | 0.062~0.106 | 0.92~5.38 | 1.88 | 0.44~5.7 | 30 | 0.49~4.34 |

| ENOB (bit) | 6.39 | 10.4 | 10.72 | 10.04 | 8.29 | 10.85 |

| SNDR (dB) | 40.2 | 64.4 | 66.3 | 62.2 | 39.5 | 67.41 |

| FoMw (fJ/conv.-step) | 132.5~191.7 | 132.7 | 111.4 | 29.7~108.3 | 2396 | 58.8 |

| FoMs (dB) | 119.2~145.1 | 158.8 | 160.5 | 158.6 | 127.7 | 164 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tang, H.; Xu, W.; Li, H.; Wei, B.; Wei, X. A 0.49–4.34 μW LC-SAR Hybrid ADC with a 10.85-Bit ENOB and 20 KS/s Bandwidth. Electronics 2024, 13, 1078. https://doi.org/10.3390/electronics13061078

Tang H, Xu W, Li H, Wei B, Wei X. A 0.49–4.34 μW LC-SAR Hybrid ADC with a 10.85-Bit ENOB and 20 KS/s Bandwidth. Electronics. 2024; 13(6):1078. https://doi.org/10.3390/electronics13061078

Chicago/Turabian StyleTang, Hai, Weilin Xu, Haiou Li, Baolin Wei, and Xueming Wei. 2024. "A 0.49–4.34 μW LC-SAR Hybrid ADC with a 10.85-Bit ENOB and 20 KS/s Bandwidth" Electronics 13, no. 6: 1078. https://doi.org/10.3390/electronics13061078