Design and Implementation of Single-Phase Grid-Connected Low-Voltage Battery Inverter for Residential Applications

Abstract

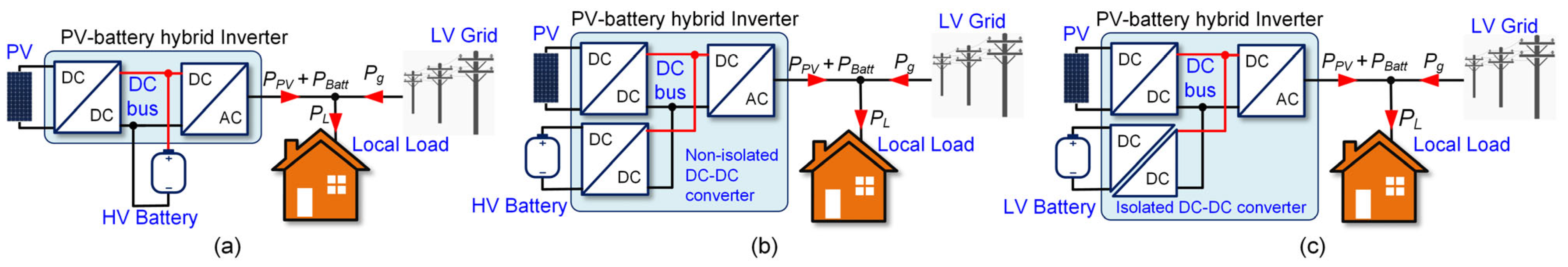

:1. Introduction

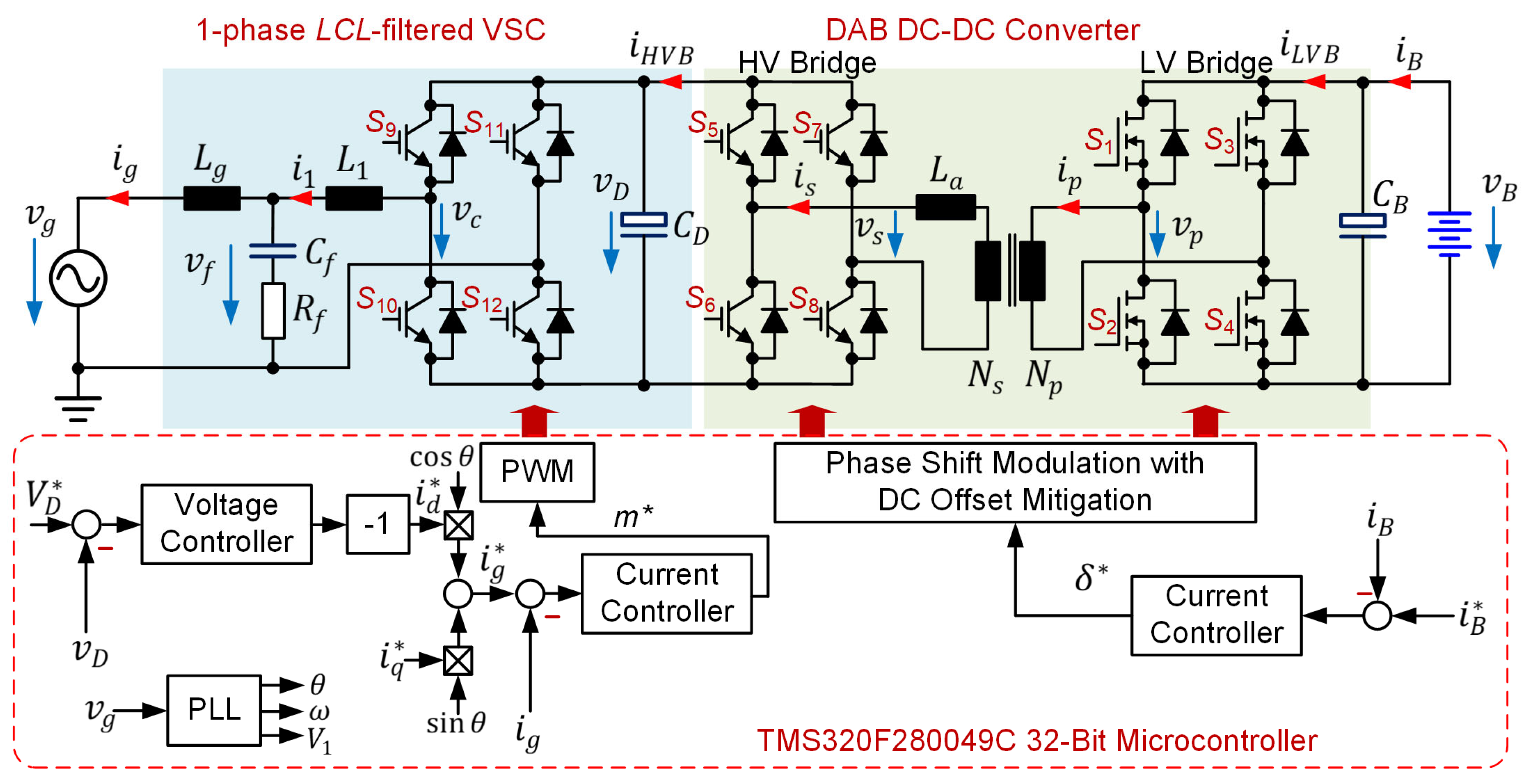

2. System Description

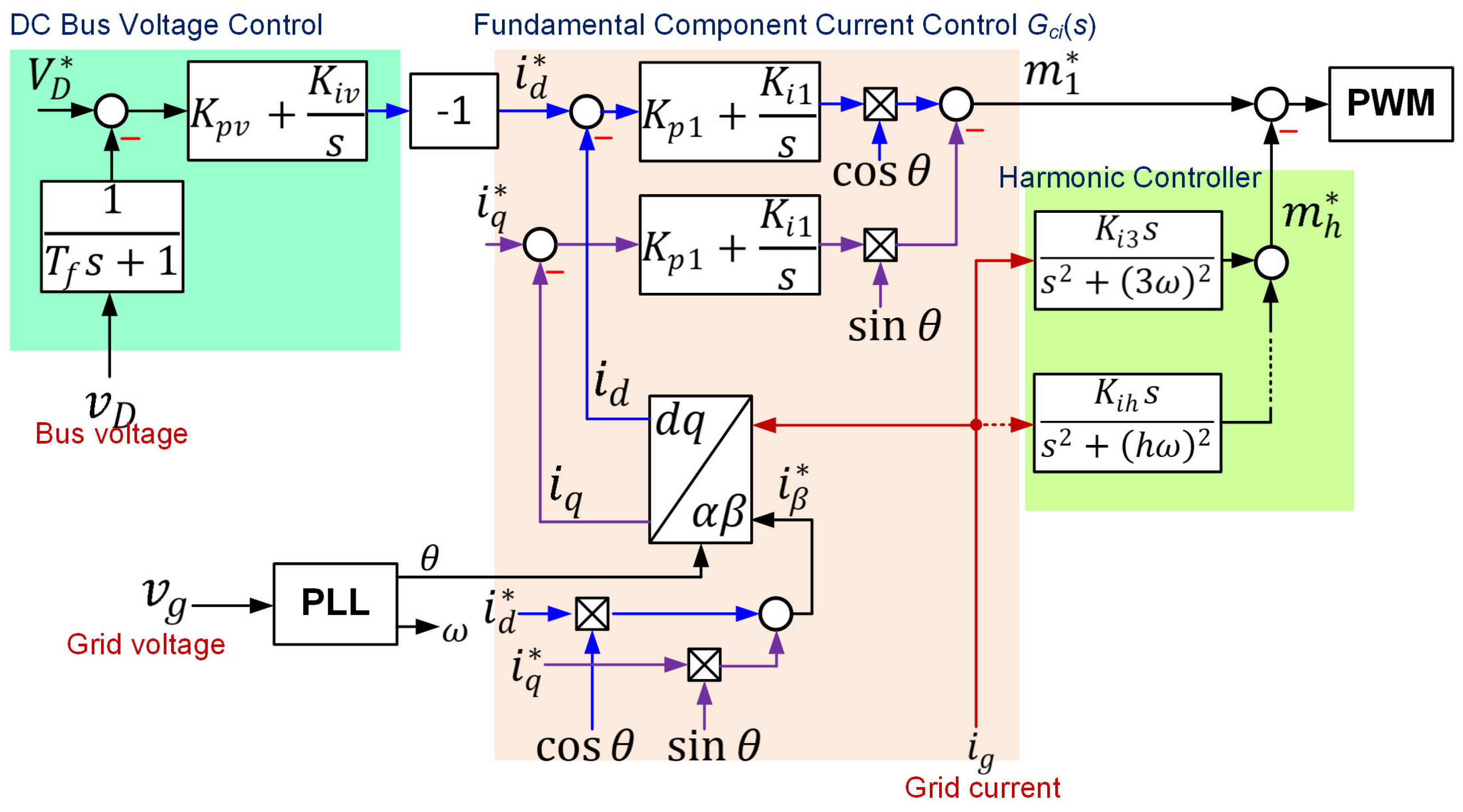

3. Implementation of the Grid-Connected VSC

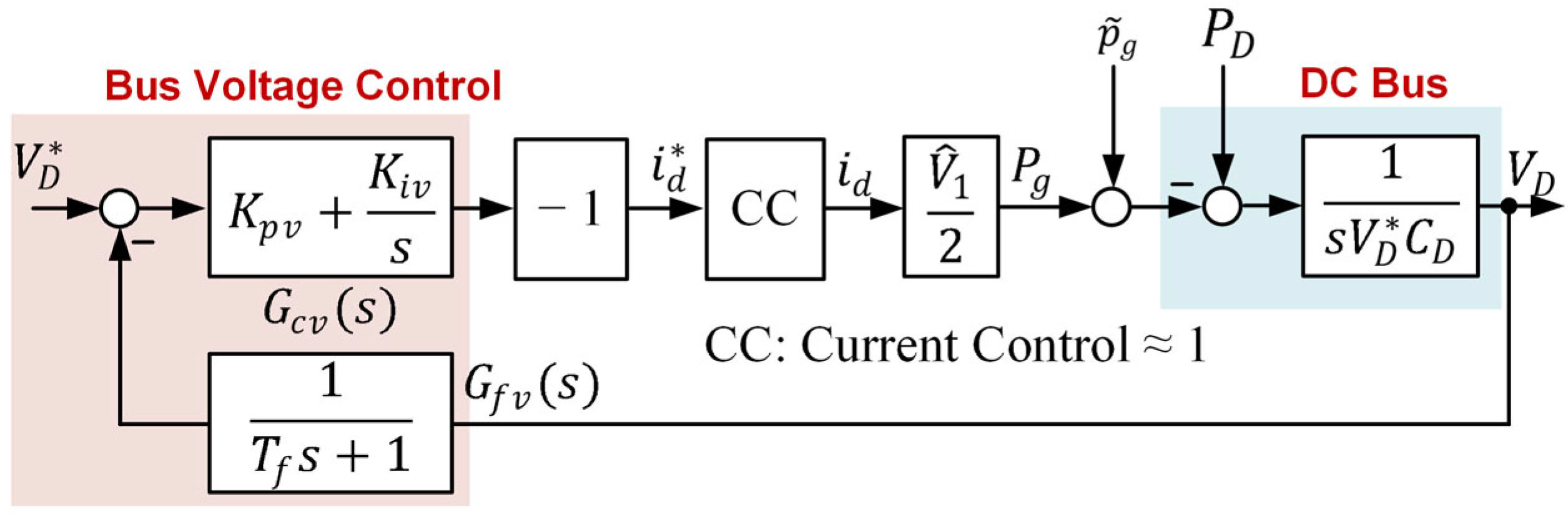

3.1. VSC Modeling

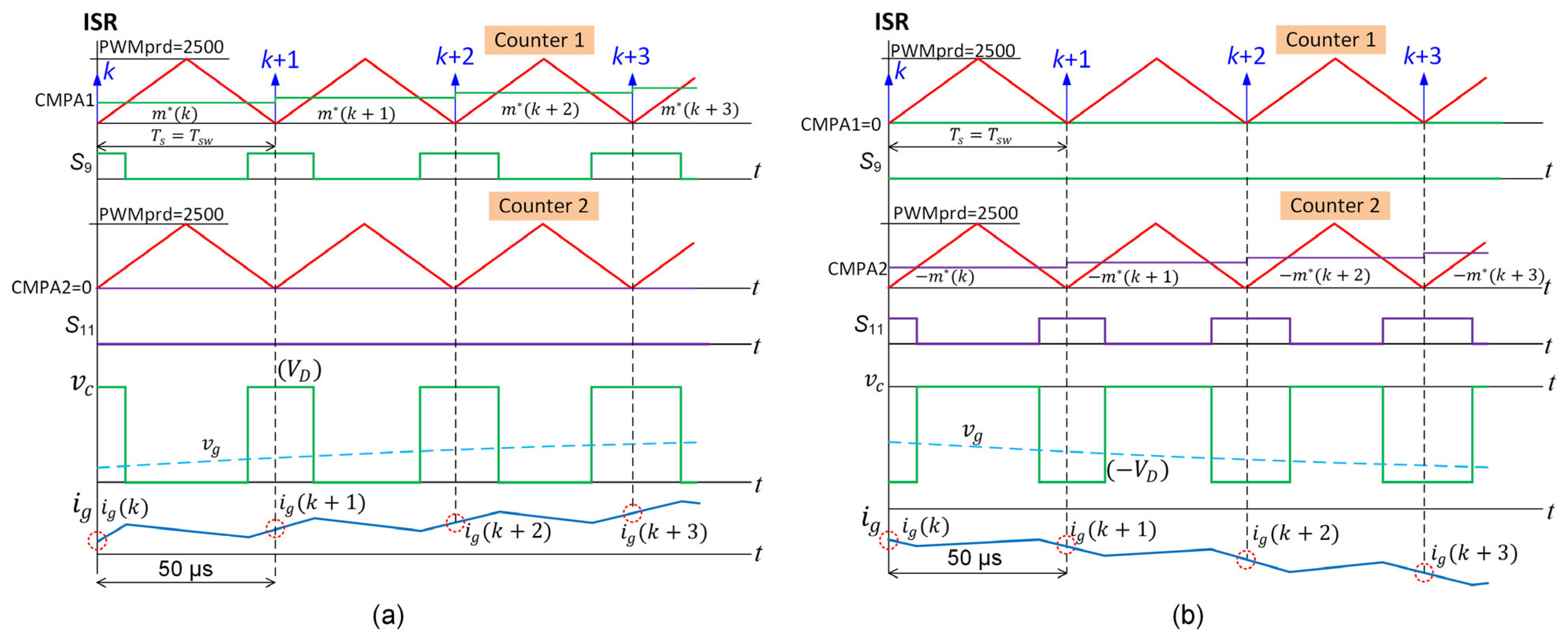

3.2. VSC Control System Implementation

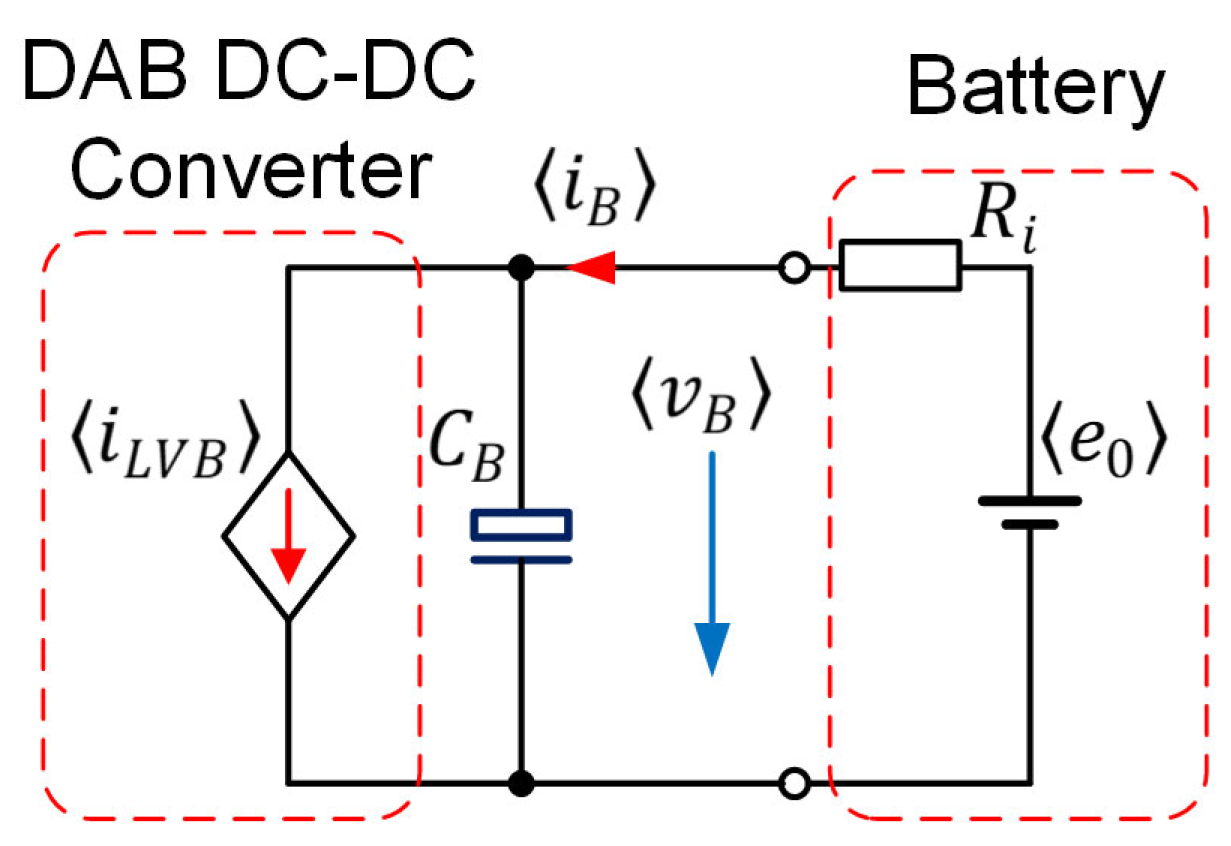

4. Implementation of the Battery-Side DAB DC-DC Converter

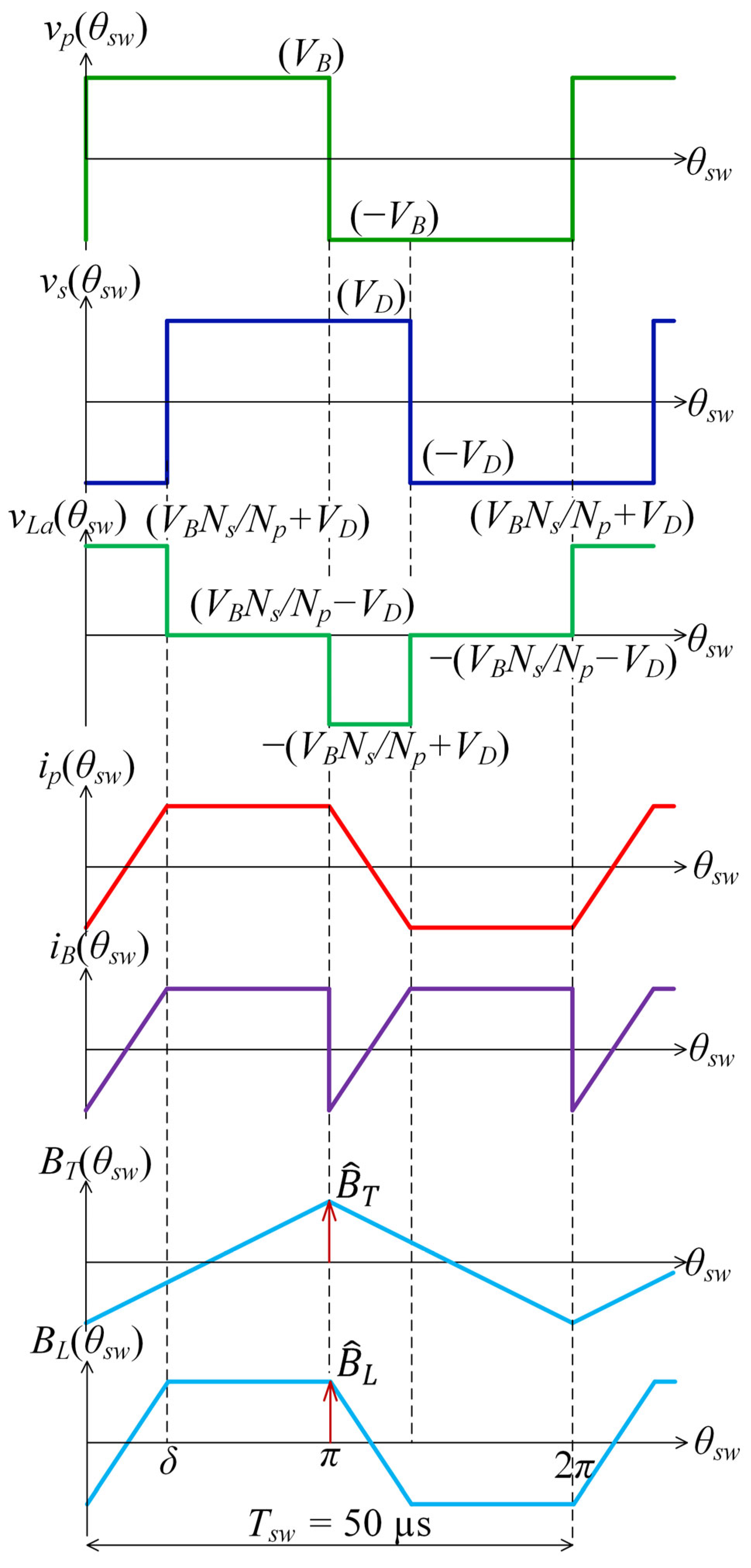

4.1. Basic Operation of the DAB DC-DC Converter

4.2. Design of the Transformer and Series Inductor

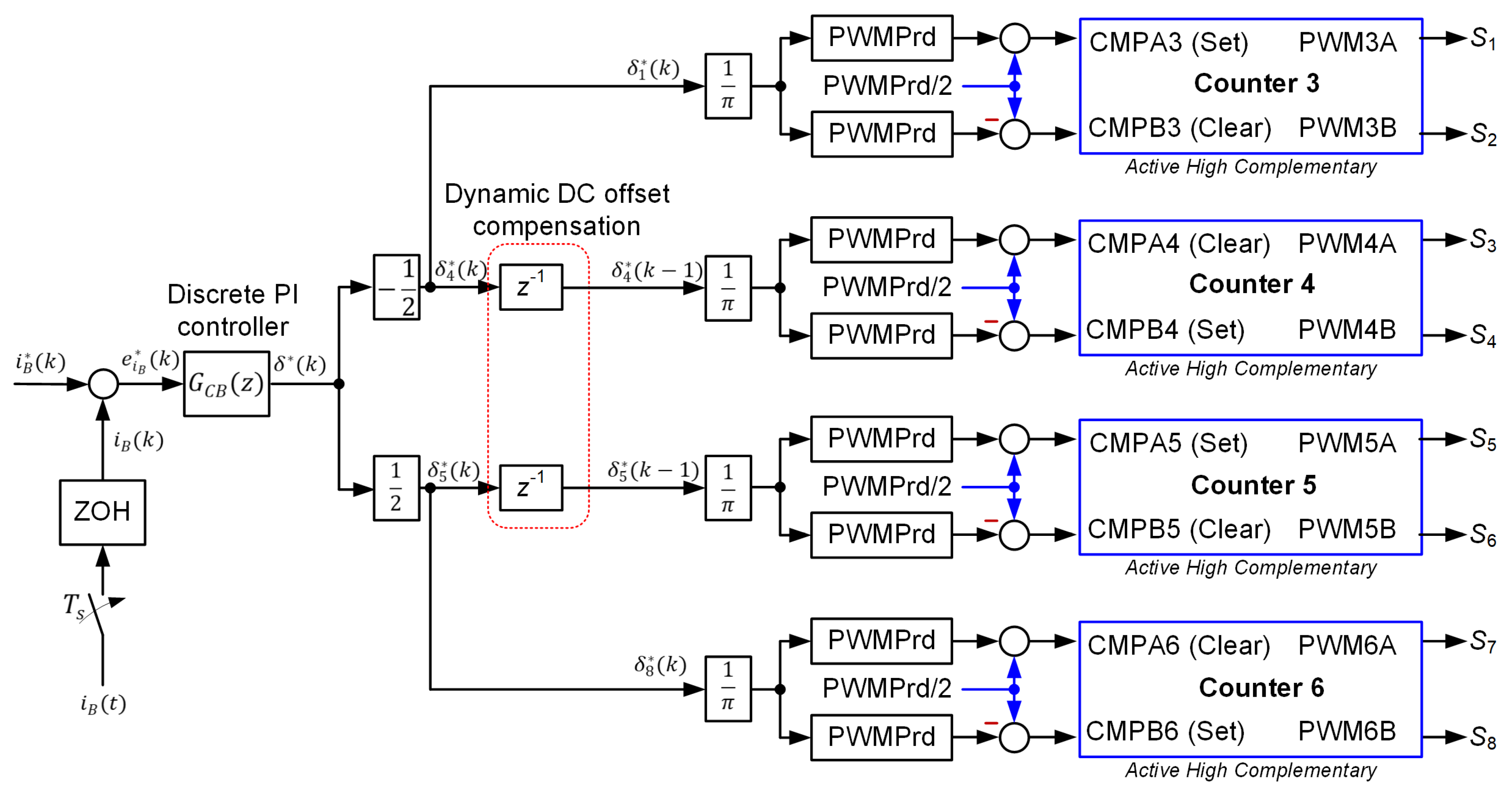

4.3. Control System Implementation of the DAB DC-DC Converter

4.4. Tuning of the Battery Current Control Loop

5. Experimental Validation

5.1. Experimental Setup

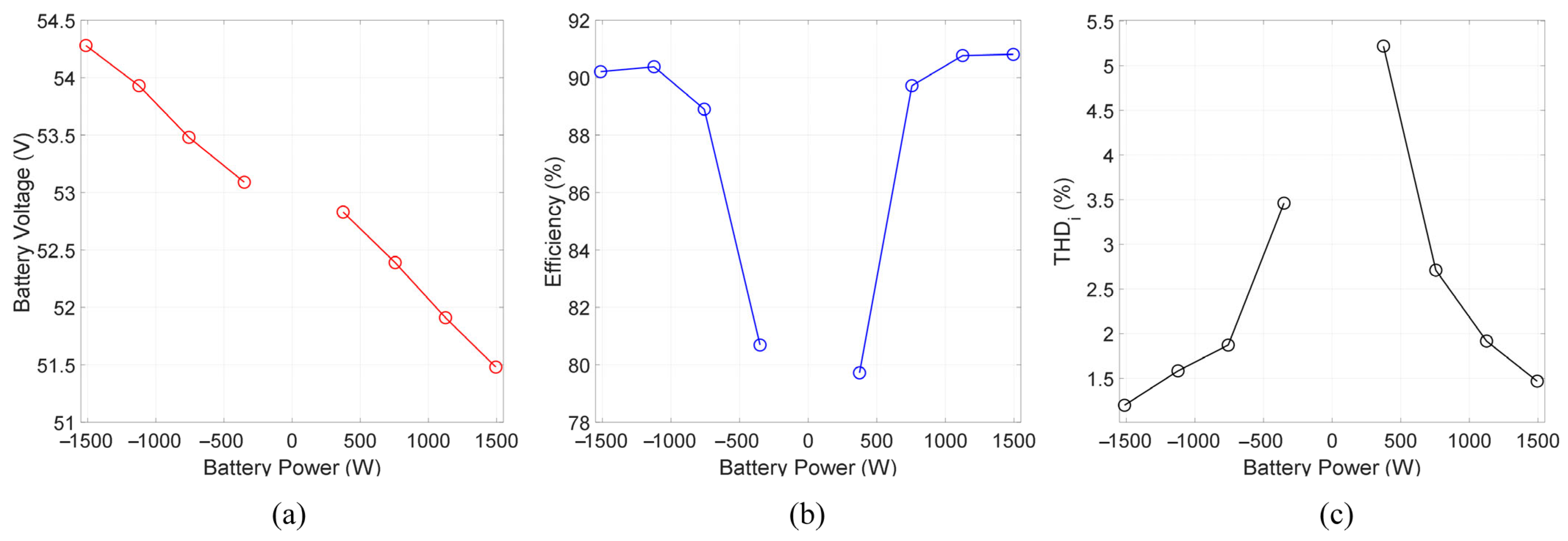

5.2. Experimental Results

5.2.1. Validation of the Dynamic DC Offset Compensation Scheme

5.2.2. Validation of the Closed-Loop Control of the Battery Current

6. Conclusions and Future Outlook

- (1)

- Adoption of advanced battery current control schemes regardless of the battery’s internal impedance parameters.

- (2)

- Increasing the switching frequency and improving the modulation strategies of the DAB DC-DC converter to enhance efficiency and power density.

- (3)

- Optimizing the design of the ripple filter on the battery side.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Renewables 2023-Analysis and Forecast to 2028. Available online: https://iea.blob.core.windows.net/assets/96d66a8b-d502-476b-ba94-54ffda84cf72/Renewables_2023.pdf (accessed on 4 February 2024).

- Hu, J.; Li, Z.; Zhu, J.; Guerrero, J.M. Voltage Stabilization: A Critical Step Toward High Photovoltaic Penetration. IEEE Ind. Electron. Mag. 2019, 13, 17–30. [Google Scholar] [CrossRef]

- IRENA. Innovation Landscape Brief: Utility-Scale Batteries. Available online: https://www.irena.org/-/media/Files/IRENA/Agency/Publication/2019/Sep/IRENA_Utility-scale-batteries_2019.pdf (accessed on 4 February 2024).

- Riyaz, A.; Sadhu, P.K.; Iqbal, A.; Alamri, B. Comprehensive Survey of Various Energy Storage Technology Used in Hybrid Energy. Electronics 2021, 10, 2037. [Google Scholar] [CrossRef]

- Ko, J.-S.; Huh, J.-H.; Kim, J.-C. Overview of Maximum Power Point Tracking Methods for PV System in Micro Grid. Electronics 2020, 9, 816. [Google Scholar] [CrossRef]

- Ahmed, M.; Harbi, I.; Kennel, R.; Heldwein, M.L.; Rodríguez, J.; Abdelrahem, M. Performance Evaluation of PV Model-Based Maximum Power Point Tracking Techniques. Electronics 2022, 11, 2563. [Google Scholar] [CrossRef]

- Galkin, I.A.; Blinov, A.; Vorobyov, M.; Bubovich, A.; Saltanovs, R.; Peftitsis, D. Interface Converters for Residential Battery Energy Storage Systems: Practices, Difficulties and Prospects. Energies 2021, 14, 3365. [Google Scholar] [CrossRef]

- Cao, J.; Emadi, A. Batteries Need Electronics. IEEE Ind. Electron. Mag. 2011, 5, 27–35. [Google Scholar] [CrossRef]

- Biao, Z.; Qiang, S.; Wenhua, L.; Yandong, S. Overview of Dual-Active-Bridge Isolated Bidirectional DC-DC Converter for High-Frequency-Link Power-Conversion System. IEEE Trans. Power Electron. 2014, 29, 4091–4106. [Google Scholar] [CrossRef]

- Somkun, S.; Sato, T.; Chunkag, V.; Pannawan, A.; Nunocha, P.; Suriwong, T. Performance Comparison of Ferrite and Nanocrystalline Cores for Medium-Frequency Transformer of Dual Active Bridge DC-DC Converter. Energies 2021, 14, 2407. [Google Scholar] [CrossRef]

- Lo Franco, F.; Morandi, A.; Raboni, P.; Grandi, G. Efficiency Comparison of DC and AC Coupling Solutions for Large-Scale PV+BESS Power Plants. Energies 2021, 14, 4823. [Google Scholar] [CrossRef]

- Duracell Energy Bank. Available online: https://www.duracellenergybank.com/ (accessed on 4 February 2024).

- What to Expect for Powerwall 3. Available online: https://www.tesla.com/support/energy/powerwall/learn/what-expect-powerwall-3 (accessed on 4 February 2024).

- Kheraluwala, M.N.; Gascoigne, R.W.; Divan, D.M.; Baumann, E.D. Performance characterization of a high-power dual active bridge DC-to-DC converter. IEEE Trans. Ind. Appl. 1992, 28, 1294–1301. [Google Scholar] [CrossRef]

- Jin, N.-Z.; Feng, Y.; Chen, Z.-Y.; Wu, X.-G. Bidirectional CLLLC Resonant Converter Based on Frequency-Conversion and Phase-Shift Hybrid Control. Electronics 2023, 12, 1605. [Google Scholar] [CrossRef]

- Zhou, K.; Sun, Y. Research on Bidirectional Isolated Charging System Based on Resonant Converter. Electronics 2022, 11, 3625. [Google Scholar] [CrossRef]

- Shu, L.; Chen, W.; Song, Z. Prediction method of DC bias in DC-DC dual-active-bridge converter. CPSS Trans. Power Electron. Appl. 2019, 4, 152–162. [Google Scholar] [CrossRef]

- Wang, Z.; Chai, J.; Sun, X. Method to control flux balancing of high-frequency transformers in dual active bridge dc–dc converters. J. Eng. 2018, 2018, 1835–1843. [Google Scholar] [CrossRef]

- Guzmán, P.; Vázquez, N.; Liserre, M.; Orosco, R.; Pinto Castillo, S.E.; Hernández, C. Two-Stage Modulation Study for DAB Converter. Electronics 2021, 10, 2561. [Google Scholar] [CrossRef]

- Takagi, K.; Fujita, H. Dynamic Control and Performance of a Dual-Active-Bridge DC–DC Converter. IEEE Trans. Power Electron. 2018, 33, 7858–7866. [Google Scholar] [CrossRef]

- Karimi-Ghartemani, M.; Khajehoddin, S.A.; Jain, P.; Bakhshai, A. A systematic approach to DC-bus control design in single-phase grid-connected renewable converters. IEEE Trans. Power Electron. 2013, 28, 3158–3166. [Google Scholar] [CrossRef]

- Somkun, S.; Srita, S.; Kaewchum, T.; Pannawan, A.; Saeseiw, C.; Pachanapan, P. Adaptive Notch Filters for Bus Voltage Control and Capacitance Degradation Prognostic of Single-Phase Grid-Connected Inverter. IEEE Trans. Ind. Electron. 2023, 70, 12190–12200. [Google Scholar] [CrossRef]

- Taghizadeh, S.; Karimi-Ghartemani, M.; Hossain, M.J.; Lu, J. A Fast and Robust DC-Bus Voltage Control Method for Single-Phase Voltage-Source DC/AC Converters. IEEE Trans. Power Electron. 2019, 34, 9202–9212. [Google Scholar] [CrossRef]

- Pannawan, A.; Kaewchum, T.; Somkun, S.; Hinkkanen, M. Fast Bus Voltage Control of Single-Phase Grid-Connected Converter with Unified Harmonic Mitigation. IEEE Access 2023, 11, 6452–6466. [Google Scholar] [CrossRef]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Dynamics assessment of advanced single-phase PLL structures. IEEE Trans. Ind. Electron. 2013, 60, 2167–2177. [Google Scholar] [CrossRef]

- TMS320F28004x Real-Time Microcontrollers-Technical Reference Manual; Texas Instruments Incorporated: Dallas, TX, USA, 2022.

- Kot, R.; Stynski, S.; Stepien, K.; Zaleski, J.; Malinowski, M. Simple technique reducing leakage current for H-bridge converter in transformerless photovoltaic generation. J. Power Electron. 2016, 16, 153–162. [Google Scholar] [CrossRef]

- De Doncker, R.W.A.A.; Divan, D.M.; Kheraluwala, M.H. A three-phase soft-switched high-power-density DC/DC converter for high-power applications. IEEE Trans. Ind. Appl. 1991, 27, 63–73. [Google Scholar] [CrossRef]

- Ferrites and Accessories SIFERRIT Material N87; EPCOS AG: Heidenheim, Germany, 2006.

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Kluwer Academic: New York, NY, USA, 2001. [Google Scholar]

- Gierczynski, M.; Grzesiak, L.M.; Kaszewski, A. A Dual Rising Edge Shift Algorithm for Eliminating the Transient DC-Bias Current in Transformer for a Dual Active Bridge Converter. Energies 2021, 14, 4264. [Google Scholar] [CrossRef]

- Tomasov, M.; Kajanova, M.; Bracinik, P.; Motyka, D. Overview of Battery Models for Sustainable Power and Transport Applications. Transp. Res. Procedia 2019, 40, 548–555. [Google Scholar] [CrossRef]

- Sadhukhan, C.; Mitra, S.K.; Bhattacharyya, S.; Almatrafi, E.; Saleh, B.; Naskar, M.K. Modeling and simulation of high energy density lithium-ion battery for multiple fault detection. Sci. Rep. 2022, 12, 9800. [Google Scholar] [CrossRef] [PubMed]

- Åström, K.J.; Hägglund, T. PID Controllers: Theory, Design, and Tuning, 2nd ed.; ISA: Durham, NC, USA, 1995. [Google Scholar]

| Parameters | Value |

|---|---|

| Maximum grid power | 3 kW |

| Nominal grid voltage | 220 Vrms |

| DC bus voltage | 400 V |

| Nominal grid frequency | 50 Hz |

| Battery nominal voltage, | 51.2 V |

| Battery voltage range | 40–60 V |

| Maximum battery current | 60 A |

| Parameters | Value |

|---|---|

| Inductor | 0.8 mH |

| Winding resistance of | 0.07 Ω |

| Inductor | 0.4 mH |

| Winding resistance of | 0.06 Ω |

| Filter capacitor | 2 μF |

| Damping resistor | 1.1 Ω |

| DC bus capacitor | 800 μF |

| Series inductor | 230 μH |

| MF transformer’s turn ratio | 7.81 |

| Battery-side capacitor | 9.9 mF |

| Switching frequency | 20 kHz |

| Control sampling frequency | 20 kHz |

| Parameters | Transformer | Inductor |

|---|---|---|

| Material | EPCOS N87 ferrite | EPCOS N87 ferrite |

| Core structure | 2 sets of E65/32/27 | 1 set of ETD49 with 2 mm gap |

| Total core area, | 10.58 cm2 | 2.11 cm2 |

| Magnetic length, | 14.7 cm | 11.4 cm |

| Primary winding | 4 turns 4 Litz wires (500 × WG40) | 55 turns 2 Litz wires (128 × AWG40) |

| Secondary winding | 31 turns 2 Litz wires (128 × AWG40) | - |

| at 51.2 V/60 V | 0.20 T/0.24 T | 0.28 T/0.36 T |

| Est. at 51.2 V V | 9.1 W | 4.0 W |

| Est. at 51.2 V V | 8.7 W | 2.2 W |

| Est. at 51.2 V V | 17.8 W | 6.2 W |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pannawan, A.; Kaewchum, T.; Saeseiw, C.; Pachanapan, P.; Hinkkanen, M.; Somkun, S. Design and Implementation of Single-Phase Grid-Connected Low-Voltage Battery Inverter for Residential Applications. Electronics 2024, 13, 1014. https://doi.org/10.3390/electronics13061014

Pannawan A, Kaewchum T, Saeseiw C, Pachanapan P, Hinkkanen M, Somkun S. Design and Implementation of Single-Phase Grid-Connected Low-Voltage Battery Inverter for Residential Applications. Electronics. 2024; 13(6):1014. https://doi.org/10.3390/electronics13061014

Chicago/Turabian StylePannawan, Akekachai, Tanakorn Kaewchum, Chayakarn Saeseiw, Piyadanai Pachanapan, Marko Hinkkanen, and Sakda Somkun. 2024. "Design and Implementation of Single-Phase Grid-Connected Low-Voltage Battery Inverter for Residential Applications" Electronics 13, no. 6: 1014. https://doi.org/10.3390/electronics13061014