Design of a 12-Bit SAR ADC with Calibration Technology

Abstract

:1. Introduction

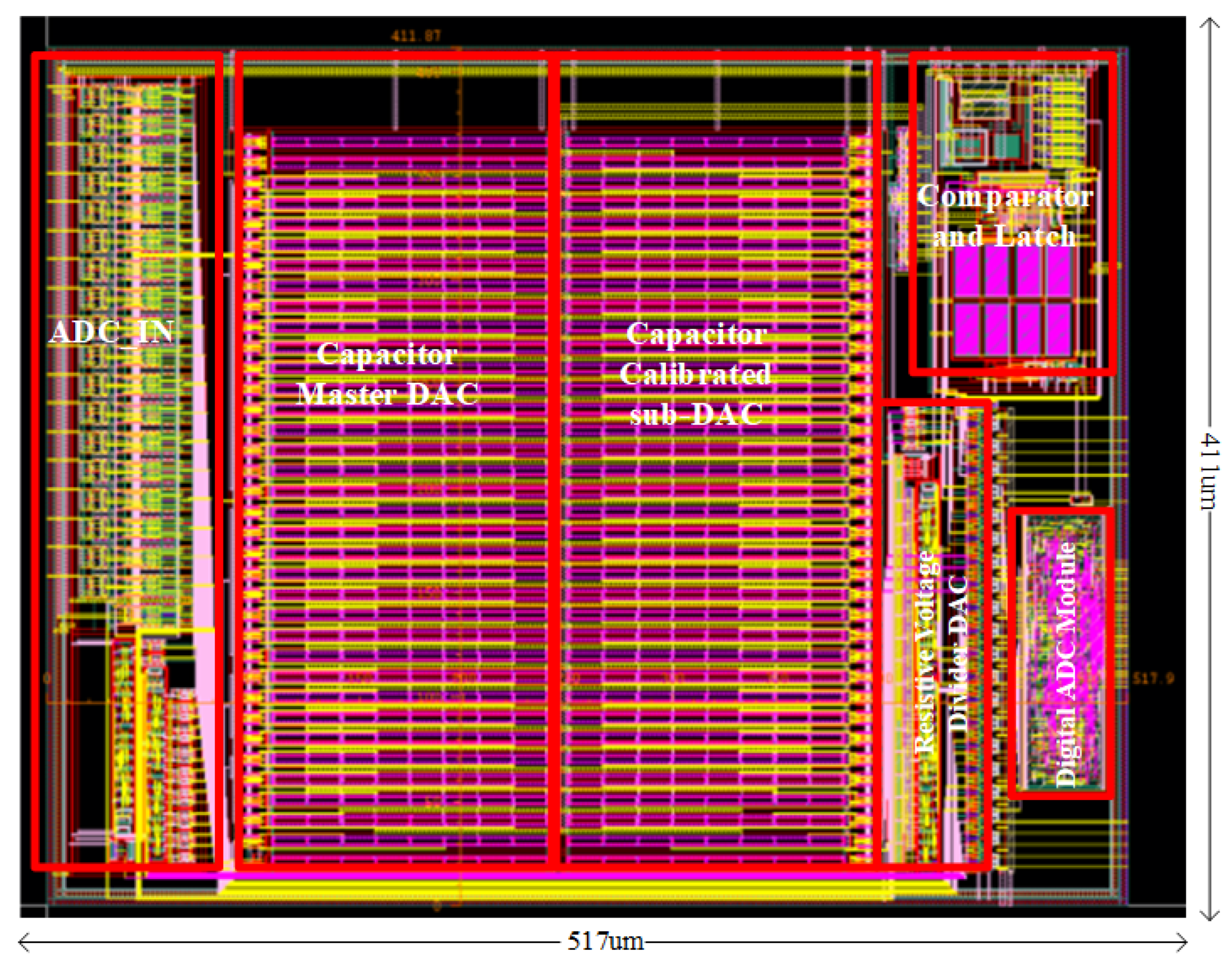

2. SAR ADC Overall Circuit Design

2.1. Overall Circuit Structure

2.2. DAC Circuit Design

2.3. Comparator and Latch Design

3. Calibration Principles and Processes

3.1. Calibration Principle

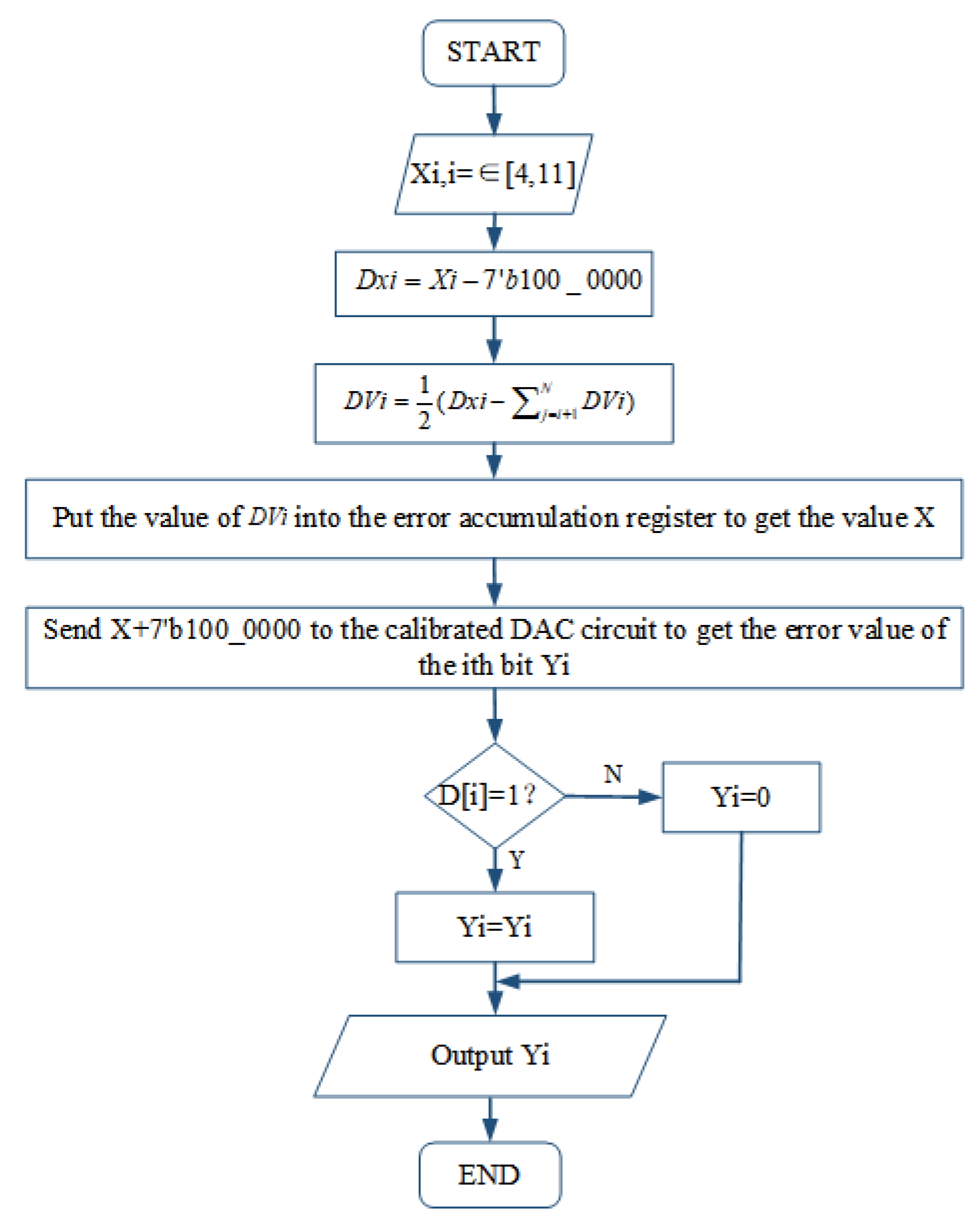

3.2. Calibration Process

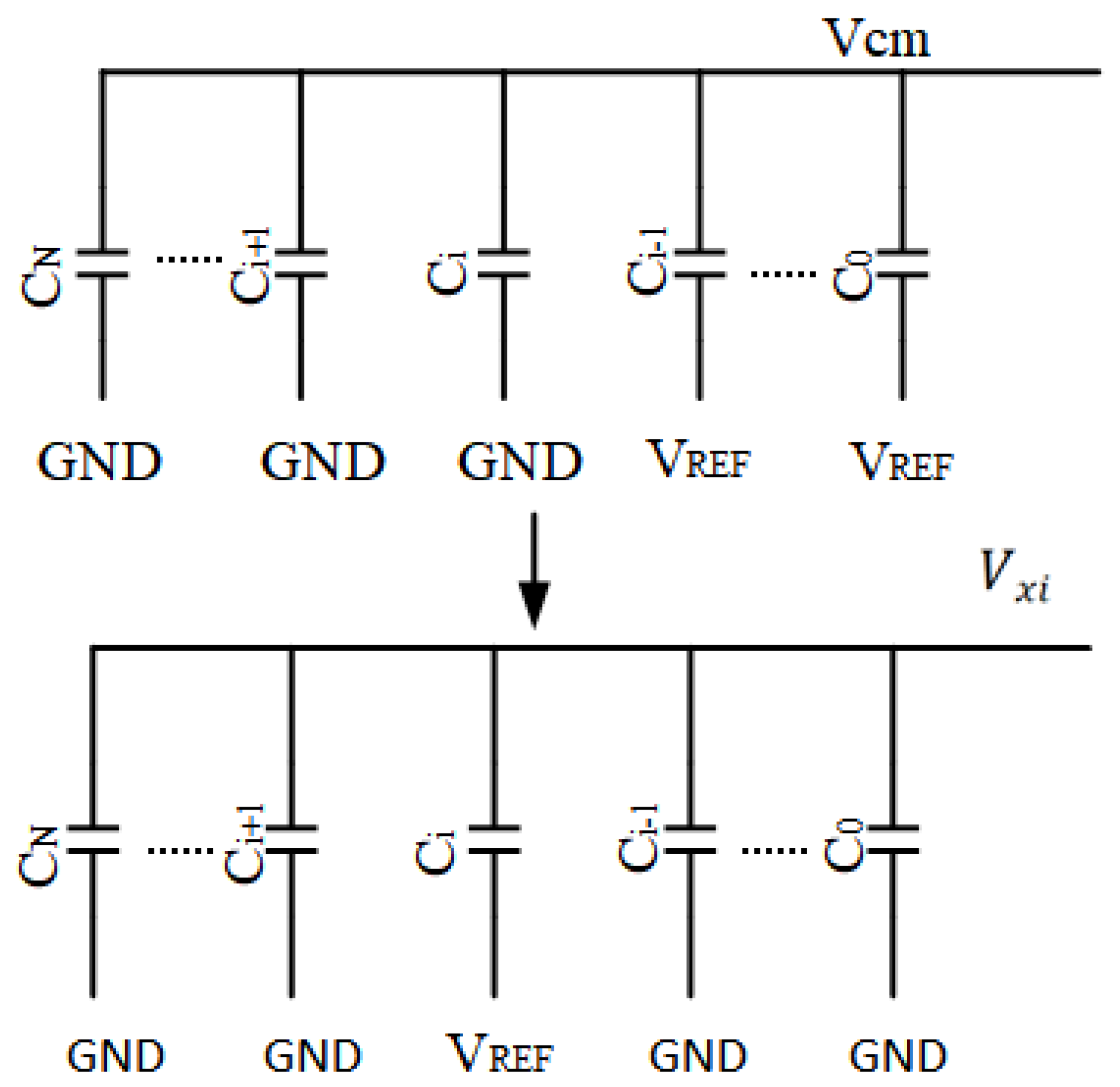

3.2.1. Calibration Sampling Stage

3.2.2. Calibration Conversion Stage

3.3. Analog-to-Digital Conversion

4. Simulation Results

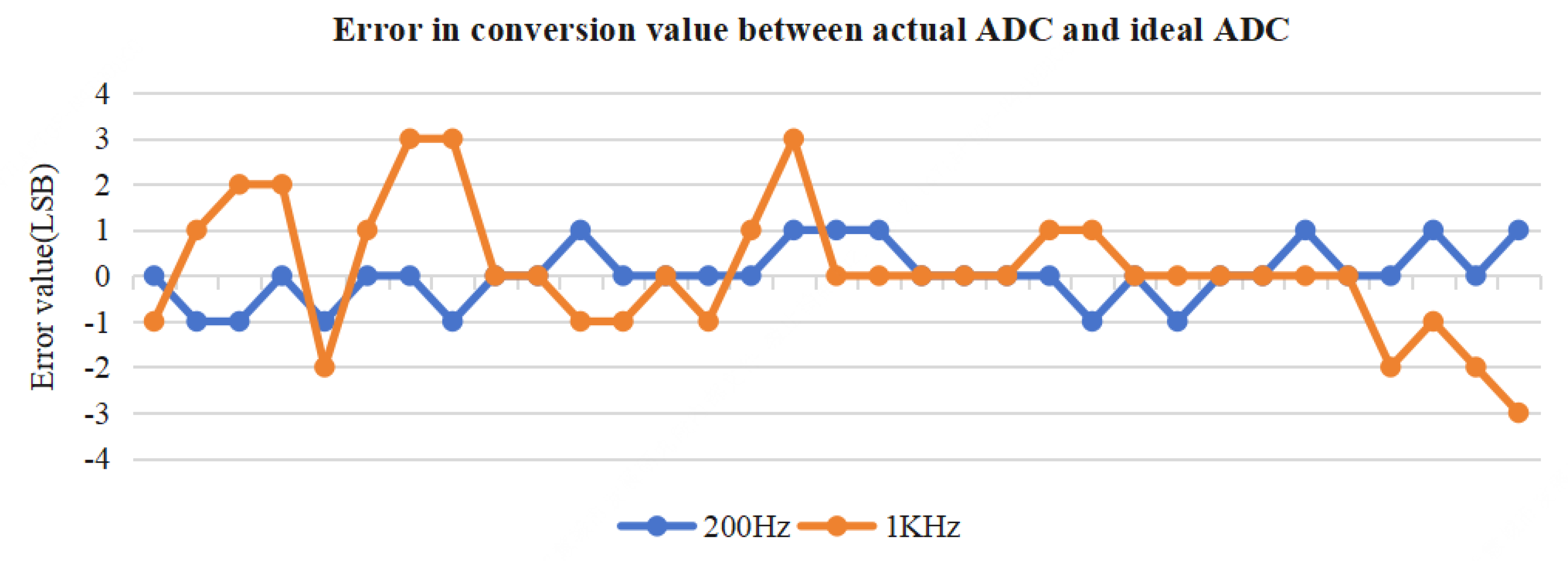

4.1. Error Analysis

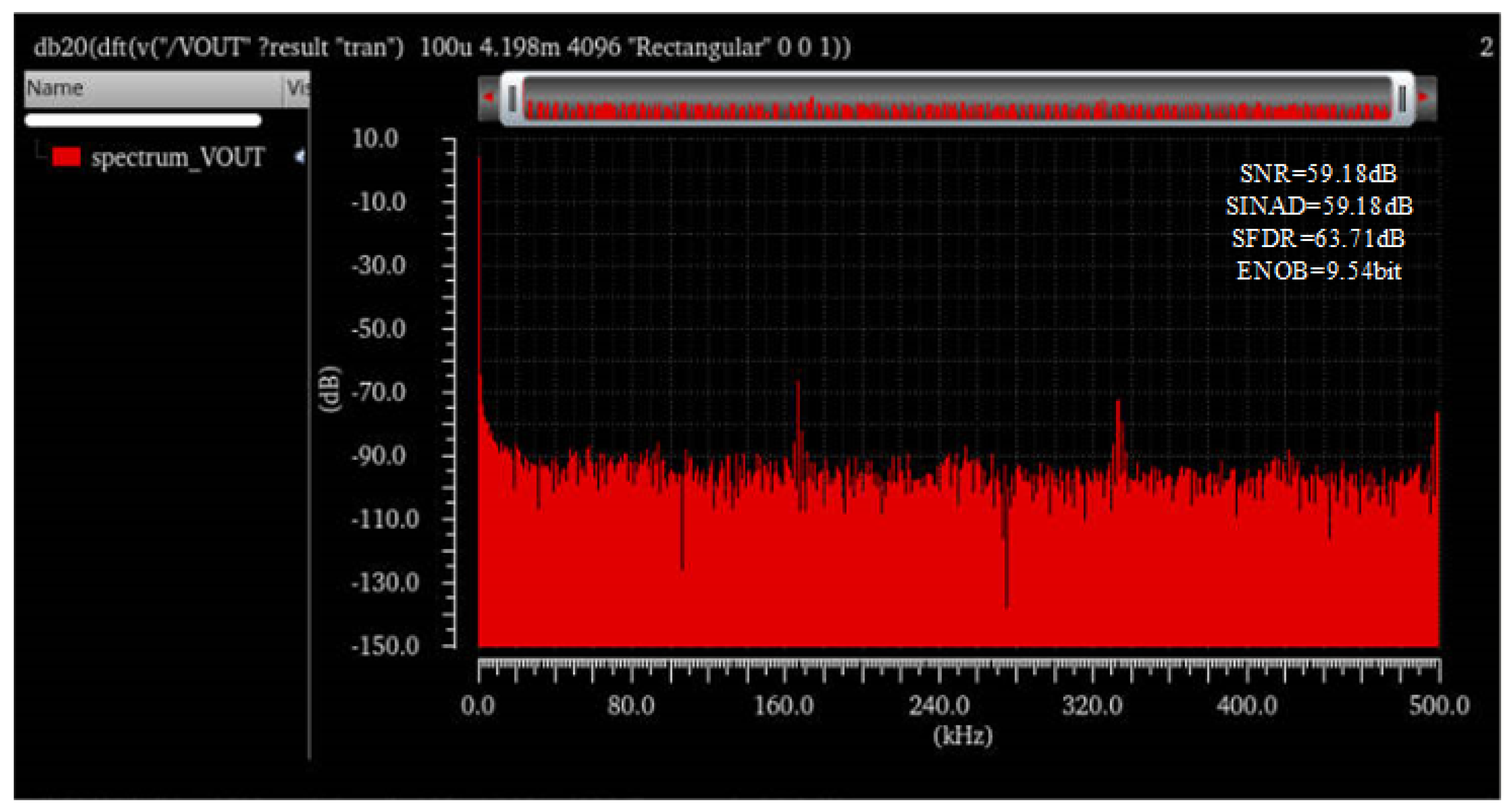

4.2. Spectral Analysis

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Jing, W. Research and Design of a 12-Bit Low Power SAR ADC. Master’s Thesis, Nanjing University of Posts, Nanjing, China, 2021. [Google Scholar] [CrossRef]

- Jinghui, L.; Rensheng, S.; Ruitong, X. Design of 14-bit SAR ADC based on digital self-calibration. China Integr. Circuit 2023, 32, 30–36. [Google Scholar]

- Shuirong, J.; Tianyao, W.; Zhangming, Z. The Key Design Techniques of 12-Bits SAR ADC. Chin. J. Electron Devices 2015, 38, 1022–1030. [Google Scholar]

- Chen, L.; Ma, J.; Sun, N. Capacitor mismatch calibration for SAR ADCs based on comparator metastability detection. In Proceedings of the 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourn, VIC, Canada, 1–5 June 2014; pp. 2357–2360. [Google Scholar]

- Xu, L.; Dai, Z.; Xie, L.; Jin, X. A 12 bit 1 MS/s SAR ADC with Digital self-calibration. Microelectronics 2019, 49, 320–325. [Google Scholar] [CrossRef]

- Wei, L.; Shangshang, G.; Xiao, W.; Shiguang, S. A digital foreground calibration algorithm for SAR ADC. J. Xian Univ. Post Telecommun. 2021, 26, 34–41. [Google Scholar] [CrossRef]

- Yutong, Z.; Xian, G.; Zhe, M. Research and Application of Calibration Technique for Successive Approximation ADC. China Integr. Circ. 2019, 28, 70–75. [Google Scholar]

- Pengzhan, J.; Sheng, D.; Wei, H.; Zhangming, Z.; Shuirong, J. Design and calibration algorithm of high-precision SAR ADC Capacitor Array. Semicond. Technol. 2023, 48, 1020–1029. [Google Scholar] [CrossRef]

- Yenuchenko, M.S.; Kvashina, N.V. Influence Analysis of Mismatch on Nonlinearity in Hybrid RC-DACs. In Proceedings of the 2023 IEEE 24th International Conference of Young Professionals in Electron Devices and Materials (EDM), Novosibirsk, Russia, 29 June–3 July 2023; pp. 400–403. [Google Scholar] [CrossRef]

- Lee, H.S.; Hodges, D. Self-calibration technique for A/D converters. IEEE Trans. Circuits Syst. 1983, 30, 188–190. [Google Scholar]

- Xujun, L.; Rui, L.; Chaofeng, Z.; Huan, D. A digital calibration algorithm for differential structure SAR ADC. China Integr. Circuit 2022, 31, 25–31+65. [Google Scholar]

- Weiming, X.; Jinping, Z.; Li, L. A design of self-calibration 12-bit SAR-ADC. Electron. Packag. 2019, 19, 20–23. [Google Scholar] [CrossRef]

- Li, Z.; Xi, J.; He, L.; Sun, K. A front-end circuit with 16-channel 12-bit 100-kSps RC-hybrid SAR ADC for industrial monitoring application. In Proceedings of the 2016 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Republic of Korea, 25–28 October 2016; pp. 340–343. [Google Scholar] [CrossRef]

- Lee, J.H.; Lee, K.Y. A Design of Low-Power Bootstrapped CMOS Switch for 20MS/s 12-bit Charge Sharing SAR ADCs. In Proceedings of the 2021 18th International SoC Design Conference (ISOCC), Jeju, Republic of Korea, 6–9 October 2021; pp. 5–6. [Google Scholar] [CrossRef]

- Zhang, J.; Guo, Z.; Li, L.; Xu, R. A Low-Power High-Precision 12Bit SAR ADC. In Proceedings of the 2022 7th International Conference on Integrated Circuits and Microsystems (ICICM), Xi’an, China, 28–31 October 2022; pp. 516–520. [Google Scholar] [CrossRef]

- Qi-zhang, L.; Zhe-ying, L. A Design of a 12-bit 1MSPs SAR ADC. J. Beijing Union Univ. Nat. Sci. 2011, 25, 6–9. [Google Scholar] [CrossRef]

- Kim, M.R.; Kim, Y.O.; Kwak, Y.S.; Ahn, G.C. A 12-bit 200-kS/s SAR ADC with hybrid RC DAC. In Proceedings of the 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Ishigaki Island, Japan, 17–20 November 2014; pp. 185–188. [Google Scholar] [CrossRef]

| Not Mismatched | Mismatched but Not Calibrated | Apply Calibration | Error When Not Calibrated (LSB) | Error after Calibration (LSB) |

|---|---|---|---|---|

| 2483 | 2479 | 2481 | 4 | 2 |

| 2803 | 2799 | 2803 | 4 | 0 |

| 3447 | 3449 | 3445 | 2 | 2 |

| 3896 | 3896 | 3896 | 0 | 0 |

| 4091 | 4091 | 4089 | 0 | 2 |

| 4003 | 4003 | 4002 | 0 | 1 |

| 3544 | 3545 | 3544 | 1 | 0 |

| 3067 | 3060 | 3065 | 7 | 2 |

| 2303 | 2300 | 2301 | 3 | 1 |

| 3537 | 3539 | 3535 | 2 | 2 |

| Parameters | This Work | [1] | [13] | [14] | [15] |

|---|---|---|---|---|---|

| Technology (nm) | 55 | 180 | 180 | 130 | 130 |

| Resolution(bit) | 12 | 12 | 12 | 12 | 12 |

| Supply voltage (V) | 3.3 | 1.2 | 3.3 | / | 5 |

| Sampling rate | 1 M | 100 K | 100 K | 20 M | K |

| Channel | 18 | / | 16 | 8 | / |

| Power consumption (mW) | 1.78 | 0.078 | 2.04 | 1.5 | 0.04 |

| SNDR (dB) | 59.18 | 62.37 | 62.13 | 65.82 | 68.15 |

| ENOB (bit) | 9.54 | 10.07 | 10.05 | / | 11.02 |

| Area mm2 | 0.21 | 0.18 | 2.55 | 0.81 | / |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, D.; Hu, J.; Huang, X.; Zhong, Q. Design of a 12-Bit SAR ADC with Calibration Technology. Electronics 2024, 13, 548. https://doi.org/10.3390/electronics13030548

Wang D, Hu J, Huang X, Zhong Q. Design of a 12-Bit SAR ADC with Calibration Technology. Electronics. 2024; 13(3):548. https://doi.org/10.3390/electronics13030548

Chicago/Turabian StyleWang, Deming, Jing Hu, Xin Huang, and Qinghua Zhong. 2024. "Design of a 12-Bit SAR ADC with Calibration Technology" Electronics 13, no. 3: 548. https://doi.org/10.3390/electronics13030548