Active Thermal Control in Neutral-Point-Clamped Multilevel Converters Based on Switching-Cell Arrays

Abstract

:1. Introduction

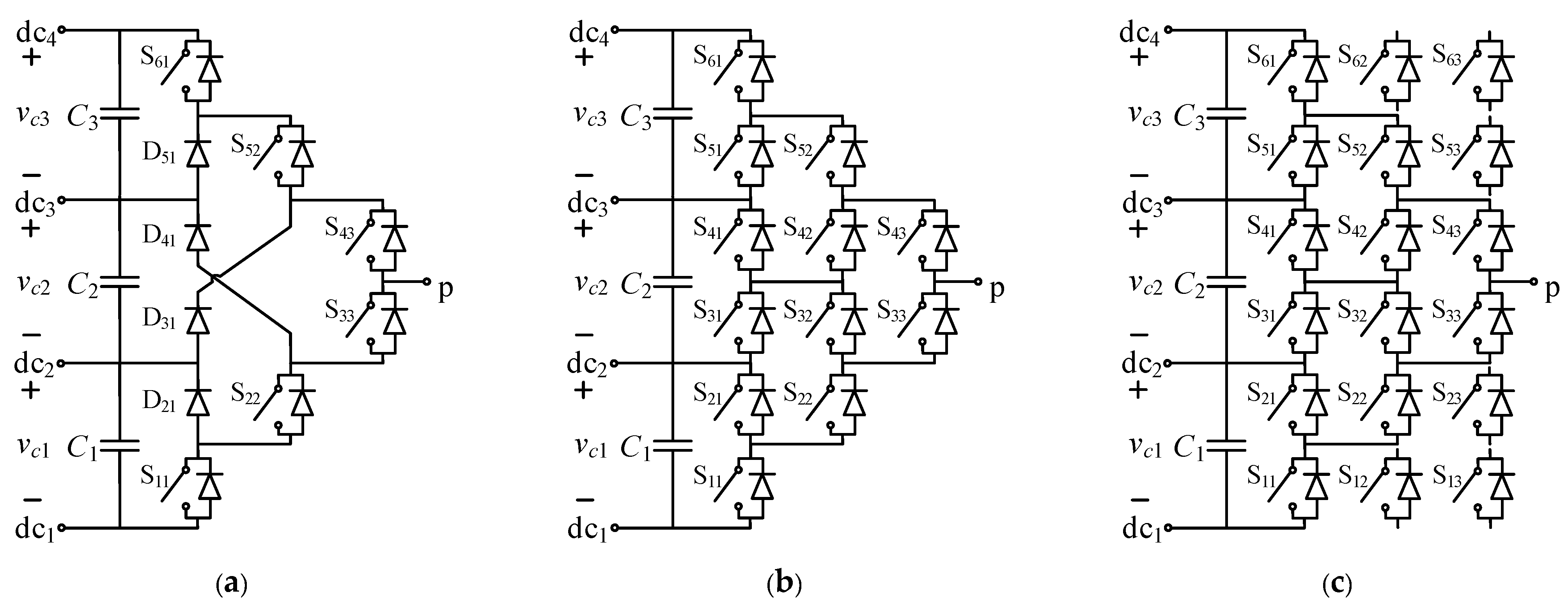

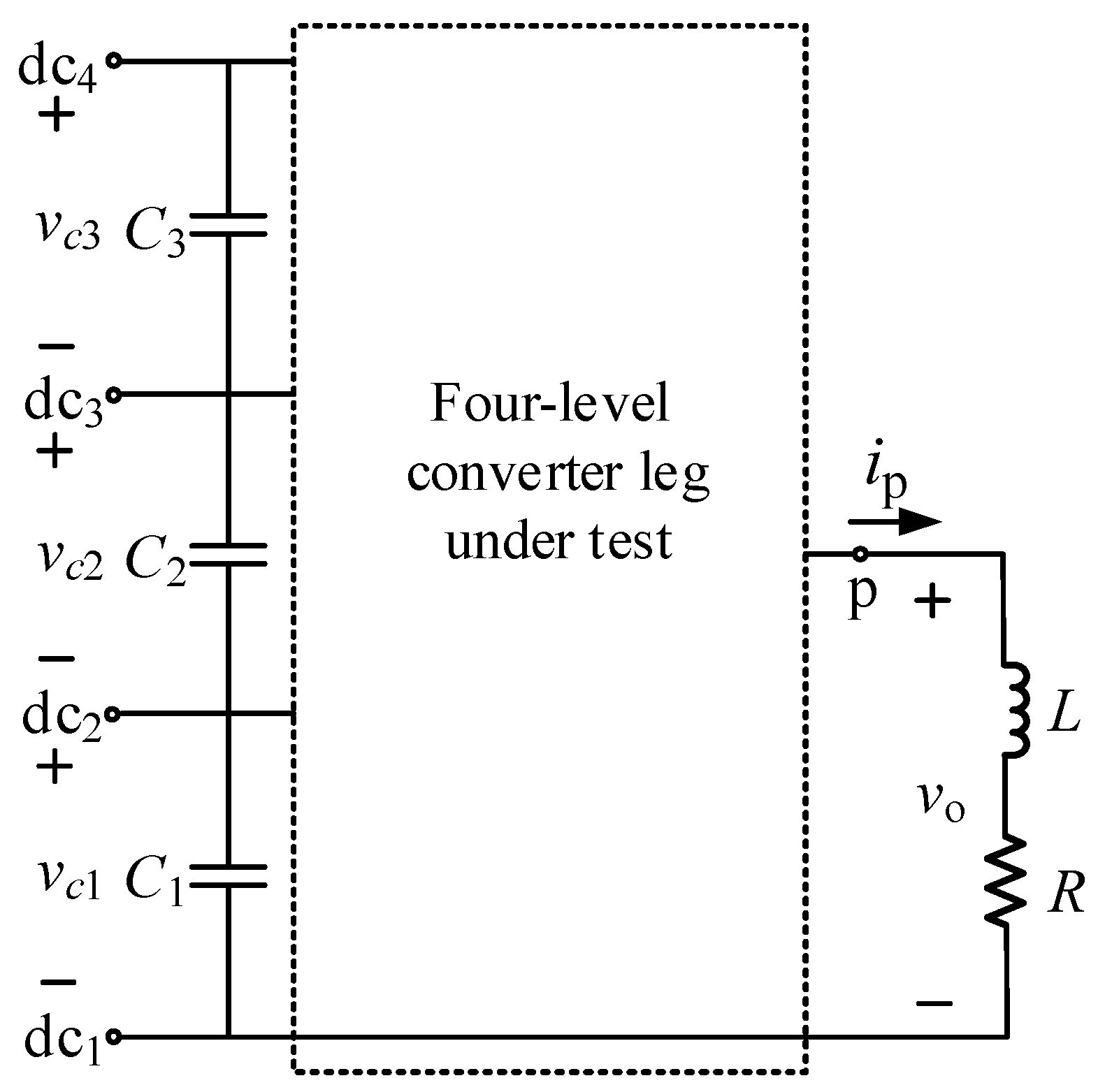

2. Description of the NPC Multilevel Converter Based on SCA

2.1. Topology and Configuration Description

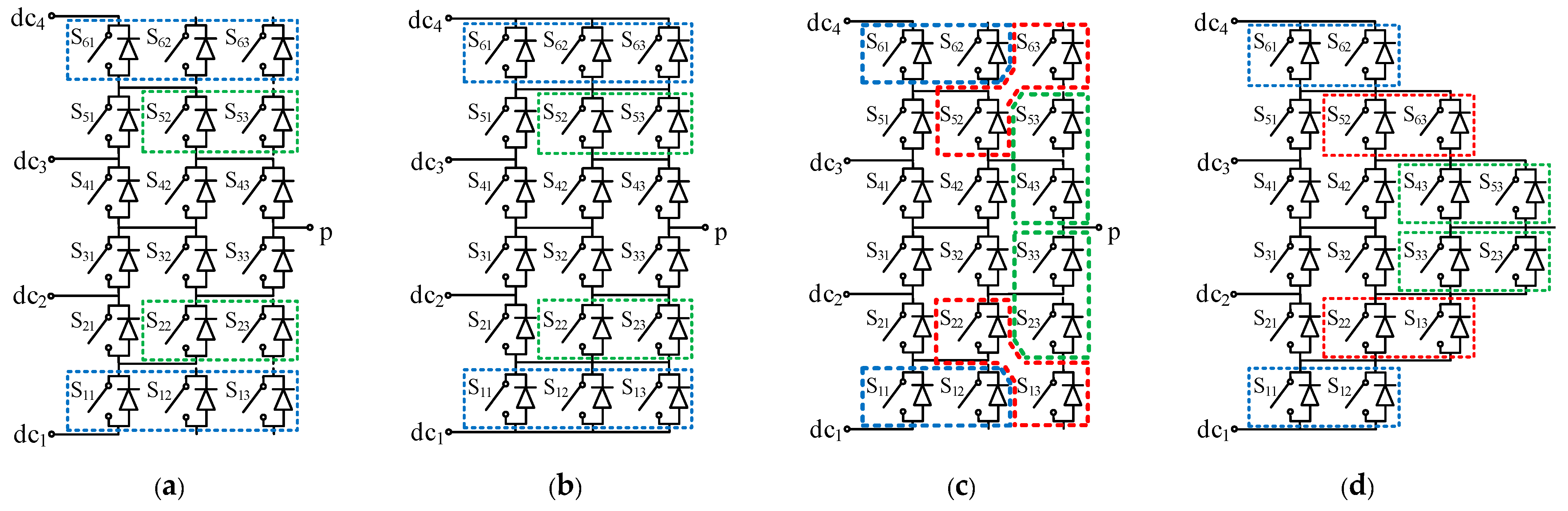

2.2. Selection of Redundant SCA Configurations

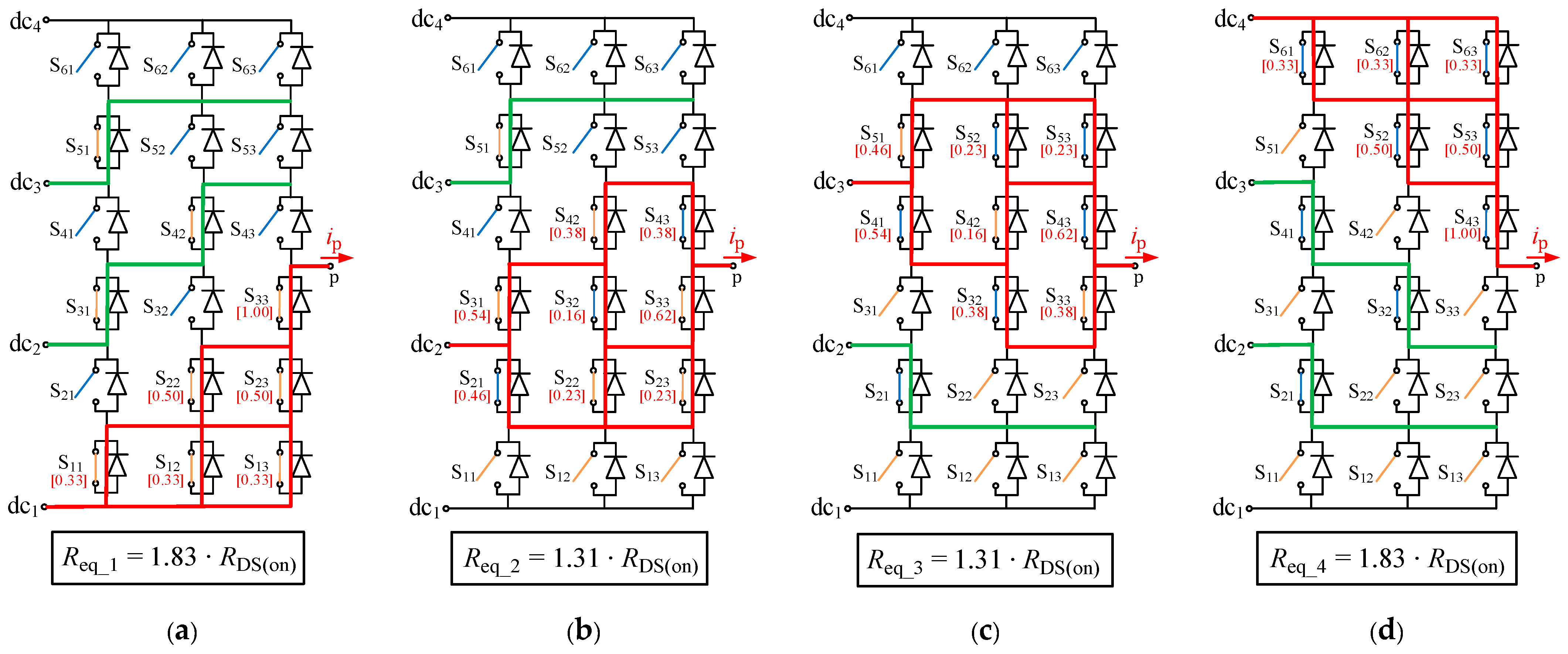

2.3. Switching States: Conduction Losses

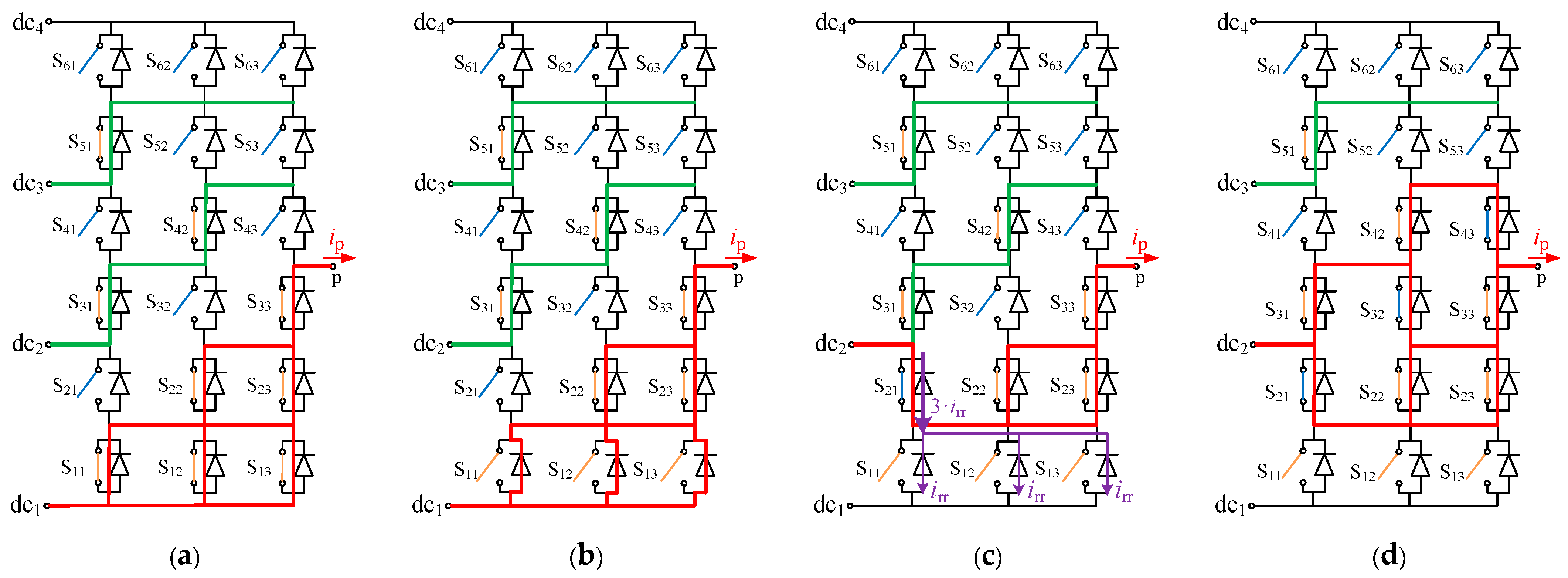

2.4. Switching Transitions: Switching Losses

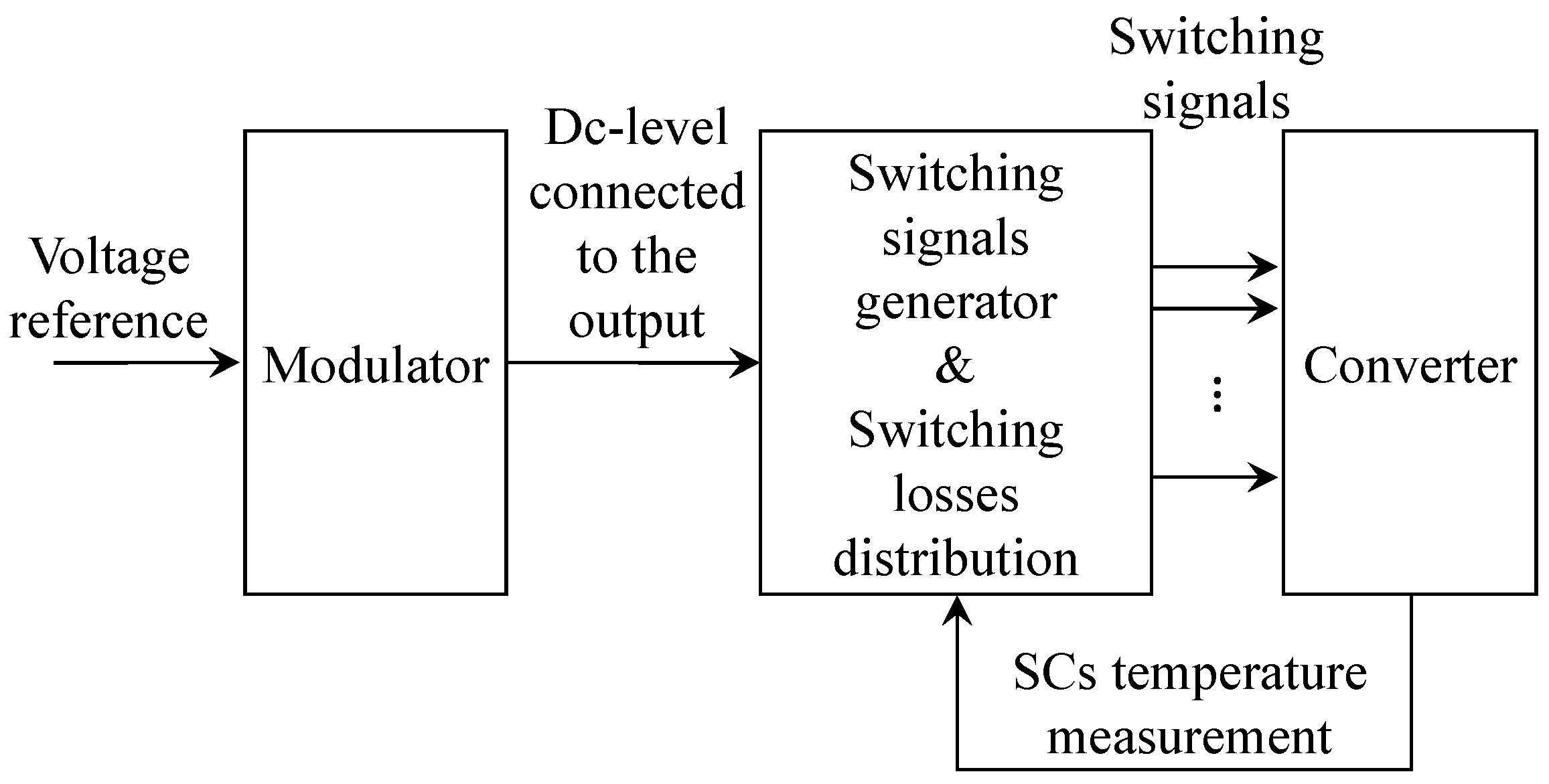

3. Active Thermal Control Method

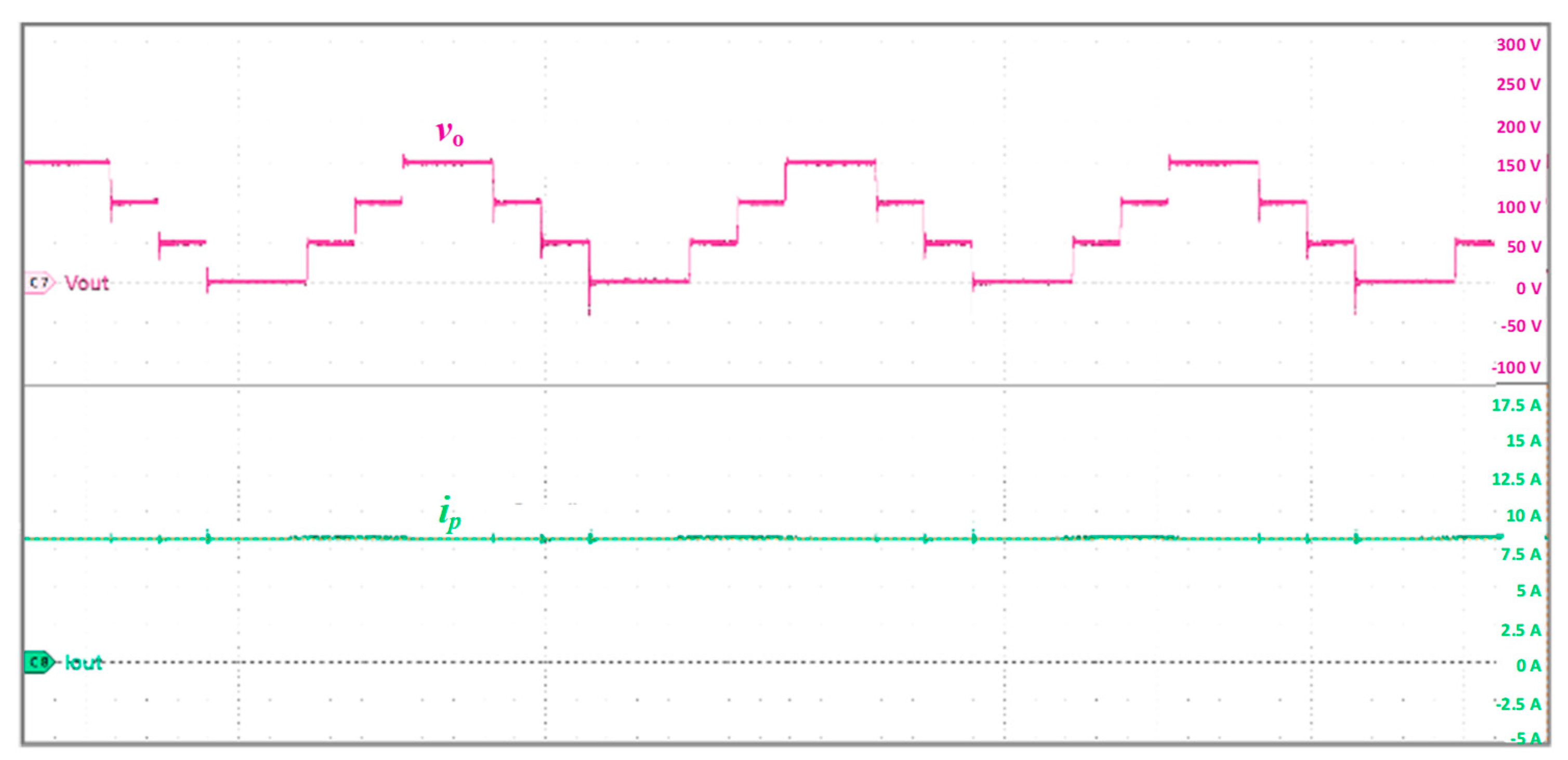

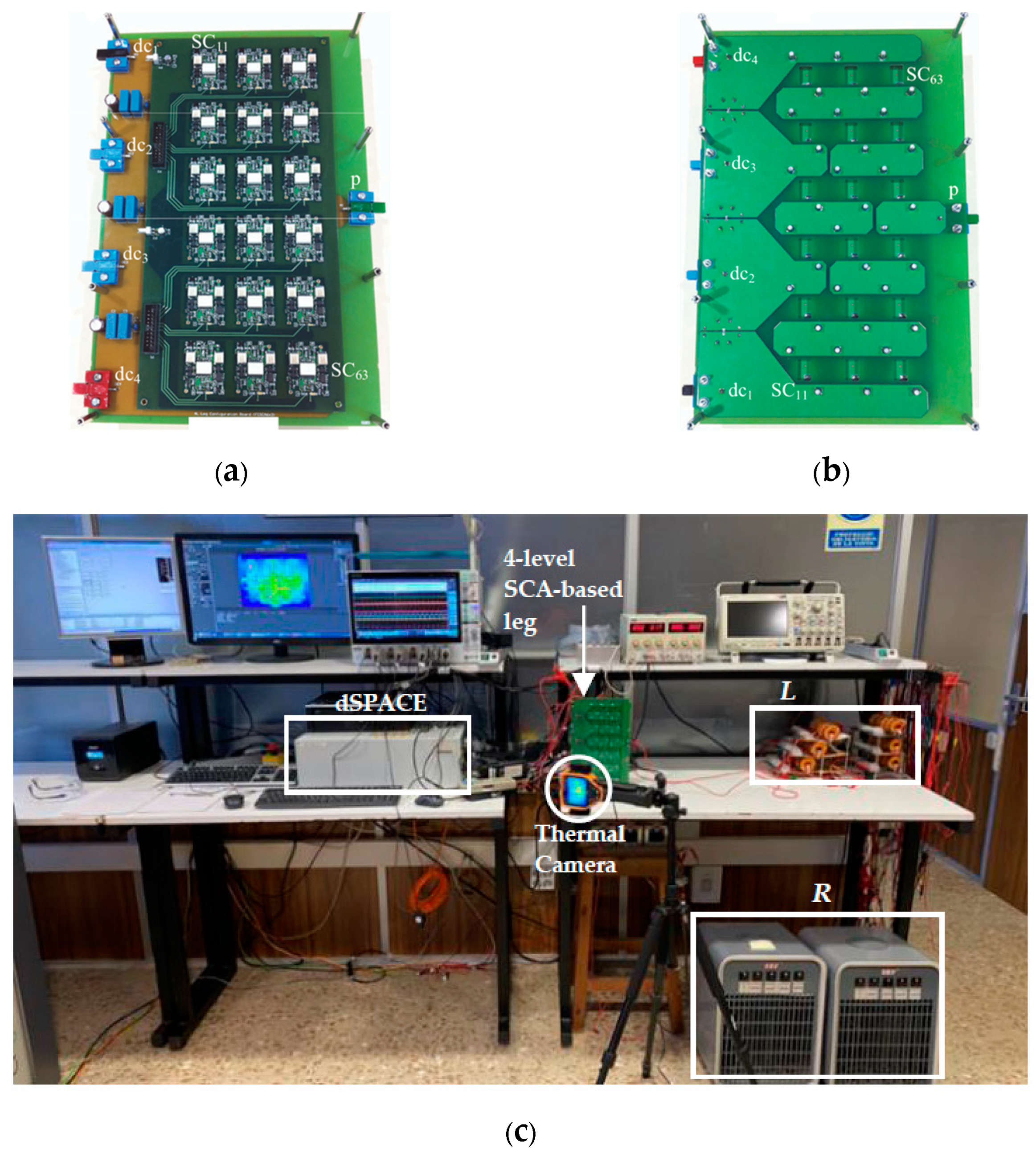

4. Experimental Results

5. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Hasegawa, K.; Akagi, H. Low-Modulation-Index Operation of a Five-Level Diode-Clamped Pwm Inverter with a DC-Voltage-Balancing Circuit for a Motor Drive. IEEE Trans. Power Electron. 2012, 27, 3495–3504. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B.; Rivera, M.; Rodriguez, J. A New Power Conversion System for Megawatt PMSG Wind Turbines Using Four-Level Converters and a Simple Control Scheme Based on Two-Step Model Predictive Strategy-Part II: Simulation and Experimental Analysis. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 14–25. [Google Scholar] [CrossRef]

- Lee, J.S.; Lee, K.B. New Modulation Techniques for a Leakage Current Reduction and a Neutral-Point Voltage Balance in Transformerless Photovoltaic Systems Using a Three-Level Inverter. IEEE Trans. Power Electron. 2014, 29, 1720–1732. [Google Scholar] [CrossRef]

- Shu, Z.; Ding, N.; Chen, J.; Zhu, H.; He, X. Multilevel SVPWM with Dc-Link Capacitor Voltage Balancing Control for Diode-Clamped Multilevel Converter Based STATCOM. IEEE Trans. Ind. Electron. 2013, 60, 1884–1896. [Google Scholar] [CrossRef]

- Bezerra, P.A.M.; Krismer, F.; Kolar, J.W.; Aljameh, R.K.; Paredes, S.; Heller, R.; Brunschwiler, T.; Francese, P.A.; Morf, T.; Kossel, M.A.; et al. Electrical and Thermal Characterization of an Inductor-Based ANPC-Type Buck Converter in 14 nm CMOS Technology for Microprocessor Applications. IEEE Open J. Power Electron. 2020, 1, 456–468. [Google Scholar] [CrossRef]

- Leon, J.I.; Vazquez, S.; Franquelo, L.G. Multilevel Converters: Control and Modulation Techniques for Their Operation and Industrial Applications. Proc. IEEE 2017, 105, 2066–2081. [Google Scholar] [CrossRef]

- Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Alepuz, S.; Busquets-Monge, S.; Nicolás-Apruzzese, J.; Filbà-Martínez, À.; Bordonau, J.; Yuan, X.; Kouro, S. A Survey on Capacitor Voltage Control in Neutral-Point-Clamped Multilevel Converters. Electronics 2022, 11, 527. [Google Scholar] [CrossRef]

- Teymour, H.R.; Sutanto, D.; Muttaqi, K.; Ciufo, P. Solar PV and Battery Storage Integration using a New Configuration of a Three-Level NPC Inverter With Advanced Control Strategy. IEEE Trans. Energy Convers. 2014, 29, 354–365. [Google Scholar]

- Busquets-Monge, S.; Filba-Martinez, A.; Alepuz, S.; Nicolas-Apruzzese, J.; Luque, A.; Conesa-Roca, A.; Bordonau, J. Multibattery-Fed Neutral-Point-Clamped DC-AC Converter with SoC Balancing Control to Maximize Capacity Utilization. IEEE Trans. Ind. Electron. 2020, 67, 16–27. [Google Scholar] [CrossRef]

- Peyghami, S.; Blaabjerg, F.; Palensky, P. Incorporating Power Electronic Converters Reliability into Modern Power System Reliability Analysis. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 1668–1681. [Google Scholar] [CrossRef]

- Falck, J.; Felgemacher, C.; Rojko, A.; Liserre, M.; Zacharias, P. Reliability of Power Electronic Systems: An Industry Perspective. IEEE Ind. Electr Mag. 2018, 12, 24–35. [Google Scholar] [CrossRef]

- Wang, H.; Liserre, M.; Blaabjerg, F.; de Place Rimmen, P.; Jacobsen, J.B.; Kvisgaard, T.; Landkildehus, J. Transitioning to physics-of-failure as a reliability driver in power electronics. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 97–114. [Google Scholar] [CrossRef]

- Blasko, V.; Lukaszewski, R.; Sladky, R. On line thermal model and thermal management strategy of a three phase voltage source inverter. In Proceedings of the IEEE Industry Applications Conference, Phoenix, AZ, USA, 3–7 October 1999. [Google Scholar]

- Andresen, M.; Liserre, M.; Buticchi, G. Review of active thermal and lifetime control techniques for power electronic modules. In Proceedings of the European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014. [Google Scholar]

- Brückner, T.; Bernet, S.; Güldner, H. The Active NPC Converter and Its Loss-Balancing Control. IEEE Trans. Ind. Electron. 2005, 52, 855–868. [Google Scholar] [CrossRef]

- Brückner, T.; Bernet, S.; Steimer, P.K. Feedforward Loss Control of Three-Level Active NPC Converters. IEEE Trans. Ind. Appl. 2007, 43, 1588–1596. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Caballero Diaz, L. Switching-Cell Arrays—An Alternative Design Approach in Power Conversion. IEEE Trans. Ind. Electron. 2019, 66, 25–36. [Google Scholar] [CrossRef]

- Bruckner, T.; Bemet, S. Loss Balancing in Three-Level Voltage Source Inverters Applying Active NPC Switches. In Proceedings of the IEEE Power Electronics Specialists Conference, Vancouver, BC, Canada, 17–21 June 2001. [Google Scholar]

- Busquets-Monge, S.; Nicolas-Apruzzese, J. A Multilevel Active-Clamped Converter Topology—Operating Principle. IEEE Trans. Ind. Electron. 2011, 58, 3868–3878. [Google Scholar] [CrossRef]

| DC Level Connected | ANPC | Configuration #1 | Configuration #2 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 61 | 61 | 62 | 63 | 61 | 62 | 63 | ||||||

| dc4 | 1 | 0.33 | 0.33 | 0.33 | 0.50 | 0.50 | 0.50 | |||||

| dc3 | - | - | - | - | - | - | 0.23 | |||||

| dc2 | - | - | - | - | - | - | - | |||||

| dc1 | - | - | - | - | - | - | - | |||||

| 51 | 52 | 51 | 52 | 53 | 51 | 52 | 53 | |||||

| dc4 | - | 1 | - | 0.50 | 0.50 | - | 0.50 | 0.50 | ||||

| dc3 | 0.40 | 0.40 | 0.46 | 0.23 | 0.23 | 0.48 | 0.24 | 0.33 | ||||

| dc2 | - | - | - | - | - | - | - | 0.17 | ||||

| dc1 | - | - | - | - | - | - | - | - | ||||

| 41 | 42 | 43 | 41 | 42 | 43 | 41 | 42 | 43 | ||||

| dc4 | - | - | 1 | - | - | 1 | - | - | 0.50 | |||

| dc3 | 0.60 | 0.20 | 0.60 | 0.54 | 0.16 | 0.62 | 0.52 | 0.18 | 0.33 | |||

| dc2 | - | 0.40 | 0.40 | - | 0.38 | 0.38 | - | 0.34 | 0.17 | |||

| dc1 | - | - | - | - | - | - | - | - | - | |||

| 31 | 32 | 33 | 31 | 32 | 33 | 31 | 32 | 33 | ||||

| dc4 | - | - | - | - | - | - | - | - | - | |||

| dc3 | - | 0.40 | 0.40 | - | 0.38 | 0.38 | - | 0.34 | 0.17 | |||

| dc2 | 0.60 | 0.20 | 0.60 | 0.54 | 0.16 | 0.62 | 0.52 | 0.18 | 0.33 | |||

| dc1 | - | - | 1 | - | - | 1 | - | - | 0.50 | |||

| 21 | 22 | 21 | 22 | 23 | 21 | 22 | 23 | |||||

| dc4 | - | - | - | - | - | - | - | - | ||||

| dc3 | - | - | - | - | - | - | - | 0.17 | ||||

| dc2 | 0.40 | 0.40 | 0.46 | 0.23 | 0.23 | 0.48 | 0.24 | 0.33 | ||||

| dc1 | - | 1 | - | 0.50 | 0.50 | - | 0.50 | 0.50 | ||||

| 11 | 11 | 12 | 13 | 11 | 12 | 13 | ||||||

| dc4 | - | - | - | - | - | - | - | |||||

| dc3 | - | - | - | - | - | - | - | |||||

| dc2 | - | - | - | - | - | - | 0.24 | |||||

| dc1 | 1 | 0.33 | 0.33 | 0.33 | 0.50 | 0.50 | 0.50 | |||||

| Dc Level Connected | ANPC | Configuration #1 | Configuration #2 |

|---|---|---|---|

| dc4 | 3.00 | 1.83 | 1.50 |

| dc3 | 1.40 | 1.31 | 1.03 |

| dc2 | 1.40 | 1.31 | 1.03 |

| dc1 | 3.00 | 1.83 | 1.50 |

| ANPC | Configuration #1 | Configuration #2 | ||||

|---|---|---|---|---|---|---|

| Dc-Level Switching Transition | SCs That Can Concentrate the Losses (Turn on/Turn off) | Diodes Presenting Reverse Recovery | SCs That Can Concentrate the Losses (Turn on/Turn off) | Diodes Presenting Reverse Recovery | SCs That Can Concentrate the Losses (Turn on/Turn off) | Diodes Presenting Reverse Recovery |

| Positive pole terminal current (ip > 0) | ||||||

| 1→2 | 21 or 32 or 43 (on) | 11 | 21 or 32 or 43 (on) | 11-12-13 | 21 or 32 or 43 or 53 (on) | 11-12 |

| 2→3 | 41 or 52 (on) | 31-22 | 41 or 52 or 53 (on) | 31-22-23 | 41 or 52 or 63 (on) | 31-22-13 |

| 3→4 | 61 (on) | 51-42-33 | 61 or 62 or 63 (on) | 51-42-33 | 61 or 62 (on) | 51-42-33-23 |

| 4→3 | 61 (off) | - | 61 or 62 or 63 (off) | - | 61 or 62 (off) | - |

| 3→2 | 41 or 52 (off) | - | 41 or 52 or 53 (off) | - | 41 or 52 or 63 (off) | - |

| 2→1 | 21 or 32 or 43 (off) | - | 21 or 32 or 43 (off) | - | 21 or 32 or 43 or 53 (off) | - |

| Negative pole terminal current (ip < 0) | ||||||

| 1→2 | 11 (off) | - | 11 or 12 or 13 (off) | - | 11 or 12 (off) | - |

| 2→3 | 31 or 22 (off) | - | 31 or 22 or 23 (off) | - | 31 or 22 or 13 (off) | - |

| 3→4 | 51 or 42 or 33 (off) | - | 51 or 42 or 33 (off) | - | 51 or 42 or 33 or 23 (off) | - |

| 4→3 | 51 or 42 or 33 (on) | 61 | 51 or 42 or 33 (on) | 61-62-63 | 51 or 42 or 33 or 23 (on) | 61-62 |

| 3→2 | 31 or 22 (on) | 41-52 | 31 or 22 or 23 (on) | 41-52-53 | 31 or 22 or 13 (on) | 41-52-63 |

| 2→1 | 11 (on) | 21-32-43 | 11 or 12 or 13 (on) | 21-32-43 | 11 or 12 (on) | 21-32-43-53 |

| Parameter | ANPC | Configuration #1 | Configuration #2 |

|---|---|---|---|

| fs = 10 kHz | |||

| Tmax | 45.5 | 45.6 | 39.1 |

| Tmean | 43.0 | 40.7 | 38.0 |

| Tmax − Tmin | 4.7 | 8.6 | 3.1 |

| (SD) | 1.5 | 2.1 | 1.0 |

| fs = 20 kHz | |||

| Tmax | 47.8 | 49.9 | 42.2 |

| Tmean | 44.3 | 43.9 | 40.2 |

| Tmax − Tmin | 6.6 | 10.7 | 4.7 |

| (SD) | 2.0 | 2.6 | 1.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Alepuz, S.; Nicolás-Apruzzese, J.; Rafiezadeh, R.; Busquets-Monge, S.; Raya, M.; Filbà-Martínez, À. Active Thermal Control in Neutral-Point-Clamped Multilevel Converters Based on Switching-Cell Arrays. Electronics 2023, 12, 4055. https://doi.org/10.3390/electronics12194055

Alepuz S, Nicolás-Apruzzese J, Rafiezadeh R, Busquets-Monge S, Raya M, Filbà-Martínez À. Active Thermal Control in Neutral-Point-Clamped Multilevel Converters Based on Switching-Cell Arrays. Electronics. 2023; 12(19):4055. https://doi.org/10.3390/electronics12194055

Chicago/Turabian StyleAlepuz, Salvador, Joan Nicolás-Apruzzese, Roya Rafiezadeh, Sergio Busquets-Monge, Mariana Raya, and Àlber Filbà-Martínez. 2023. "Active Thermal Control in Neutral-Point-Clamped Multilevel Converters Based on Switching-Cell Arrays" Electronics 12, no. 19: 4055. https://doi.org/10.3390/electronics12194055