Bidirectional Interleaved DC–DC Converter for Supercapacitor Energy Storage Integration with Reduced Capacitance

Abstract

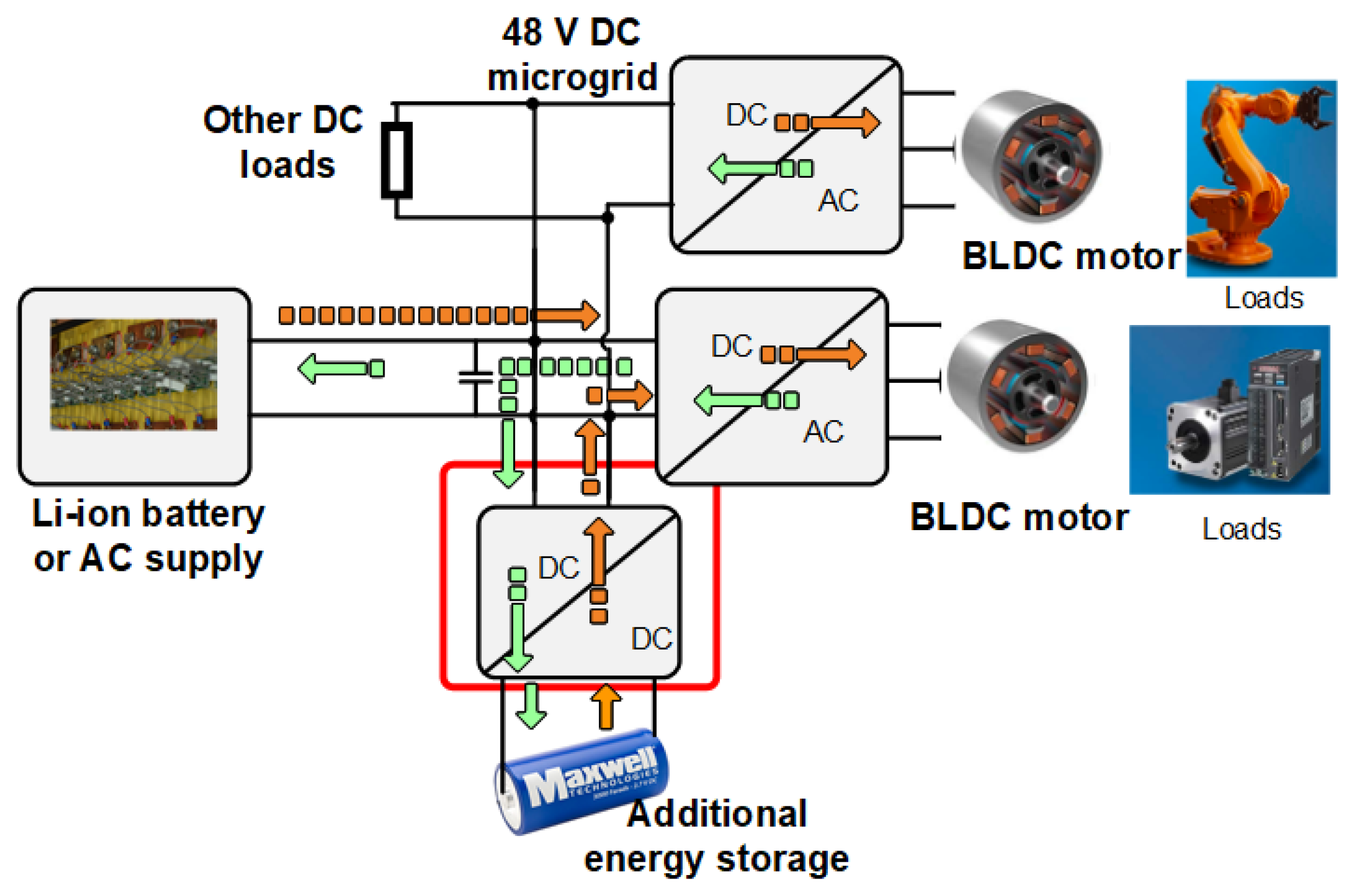

:1. Introduction

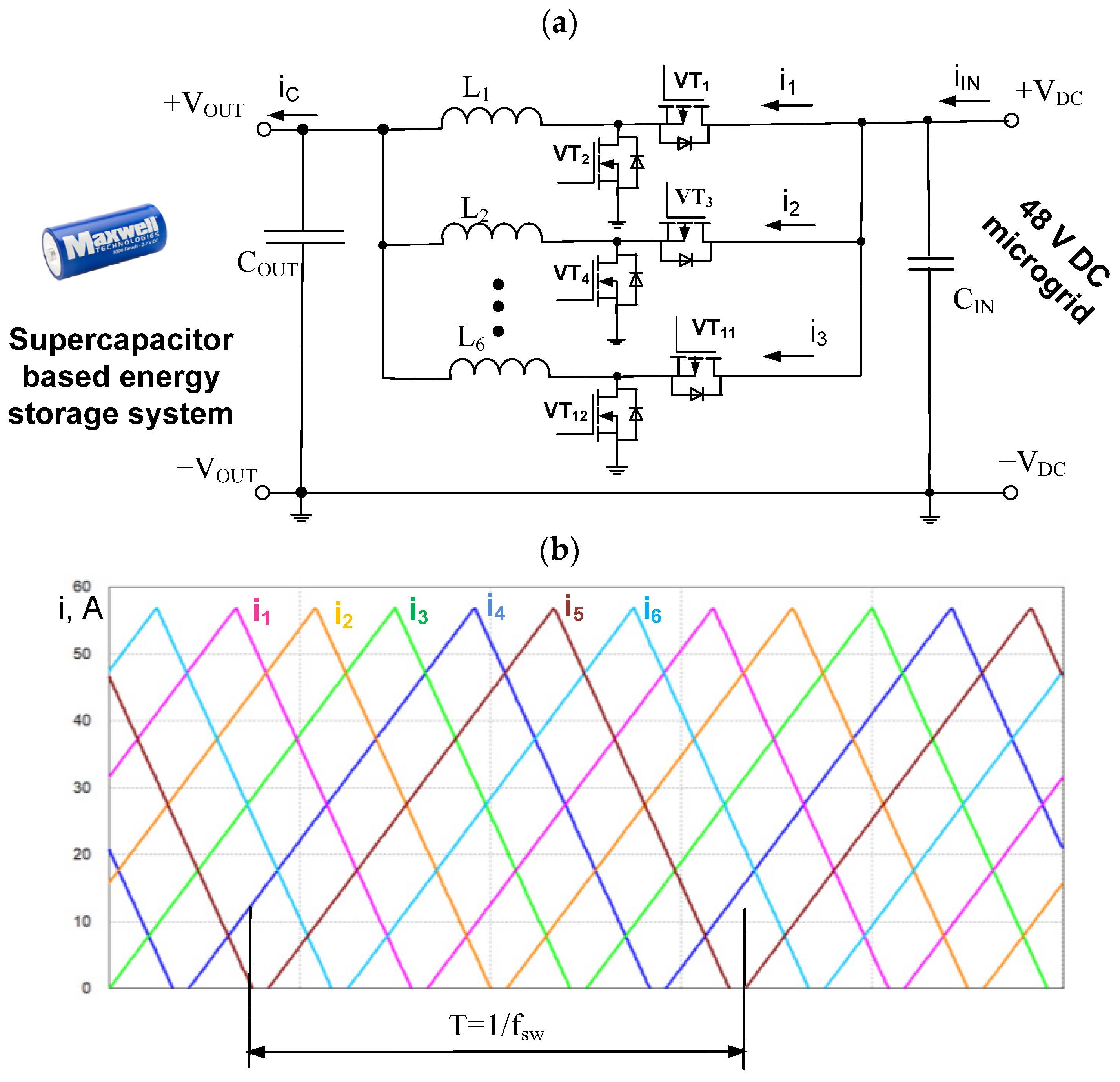

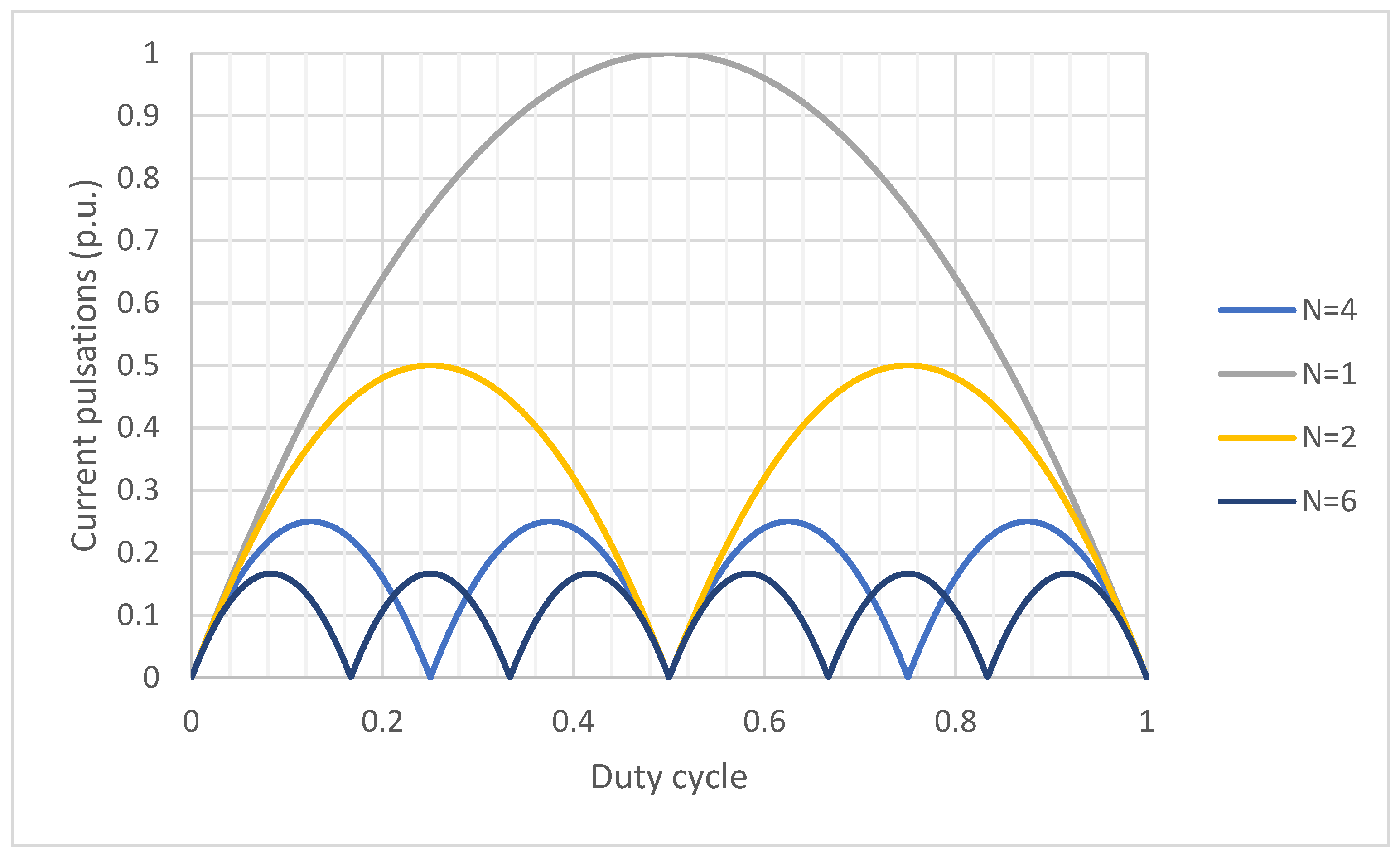

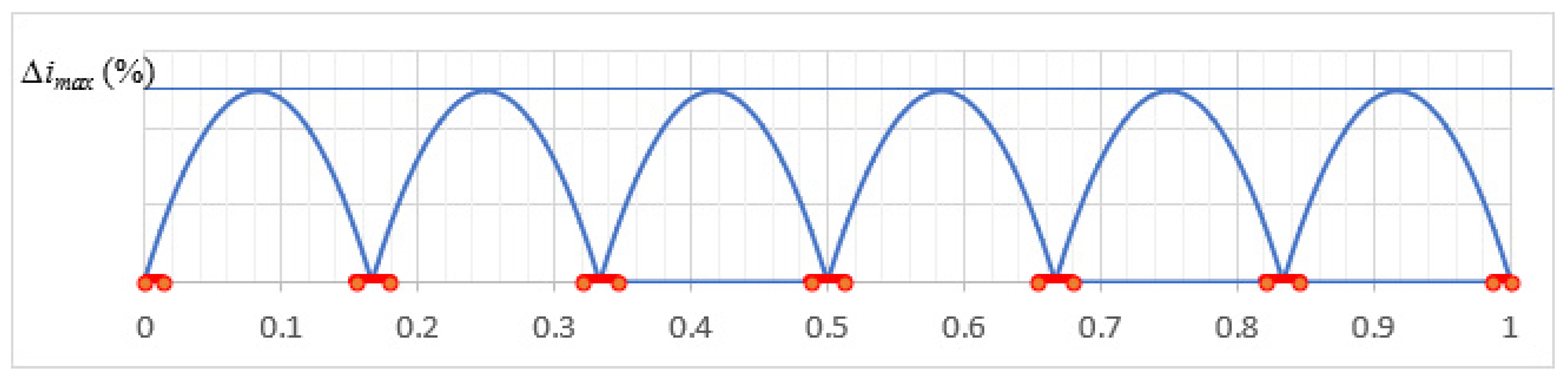

2. Current Ripple of Interleaved Converter and Output Filter Minimization

3. Supercapacitor Charging and Discharging with Constant Voltage

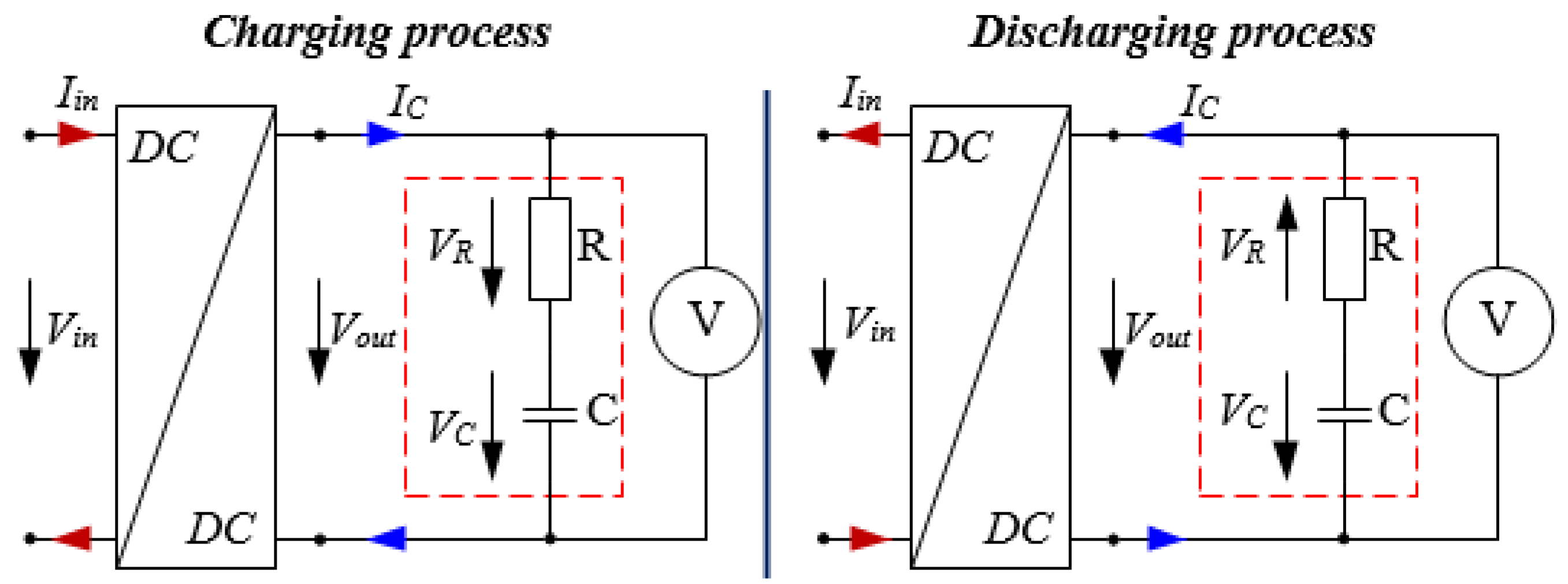

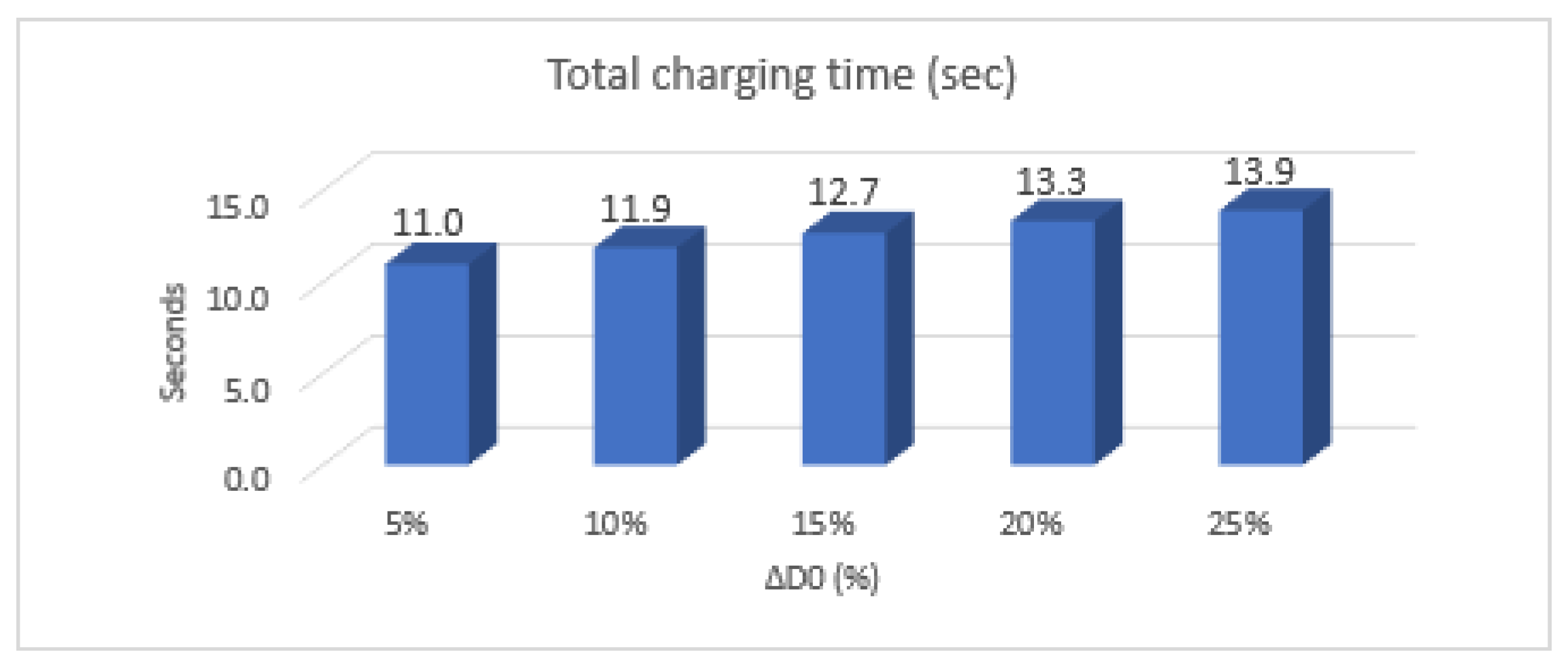

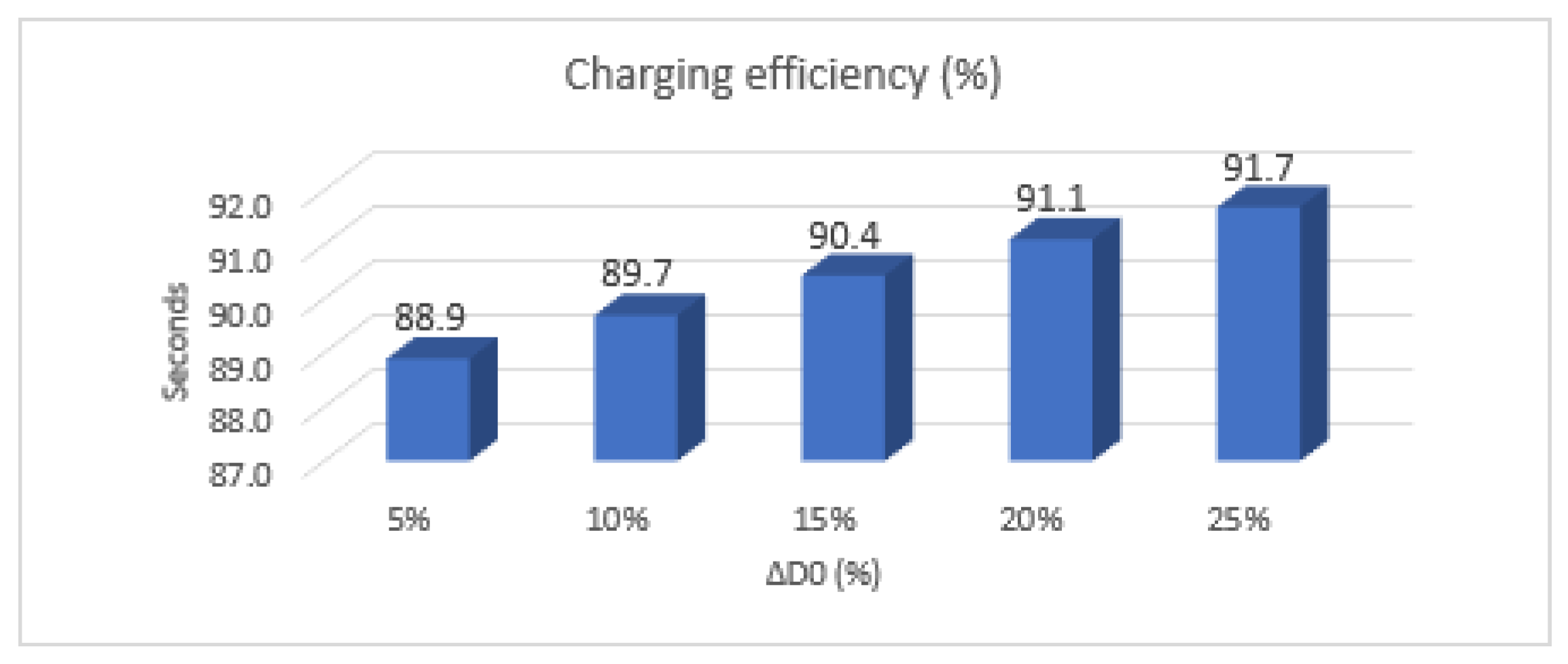

3.1. Description of Theoretical Model of Supercapacitor Circuit

3.2. Mathematical Calculations of Supercapacitor Charging and Discharging with Constant Voltage

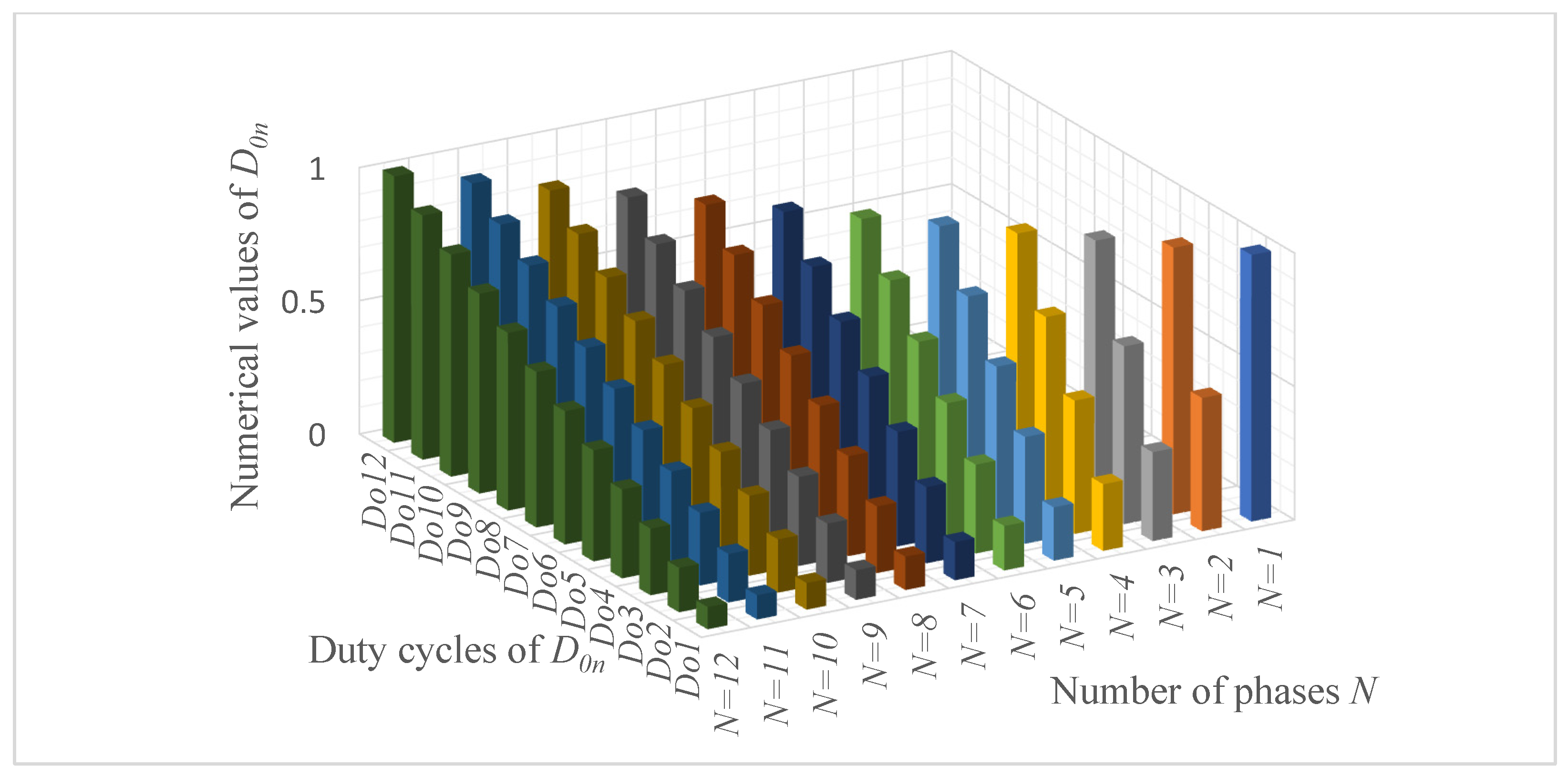

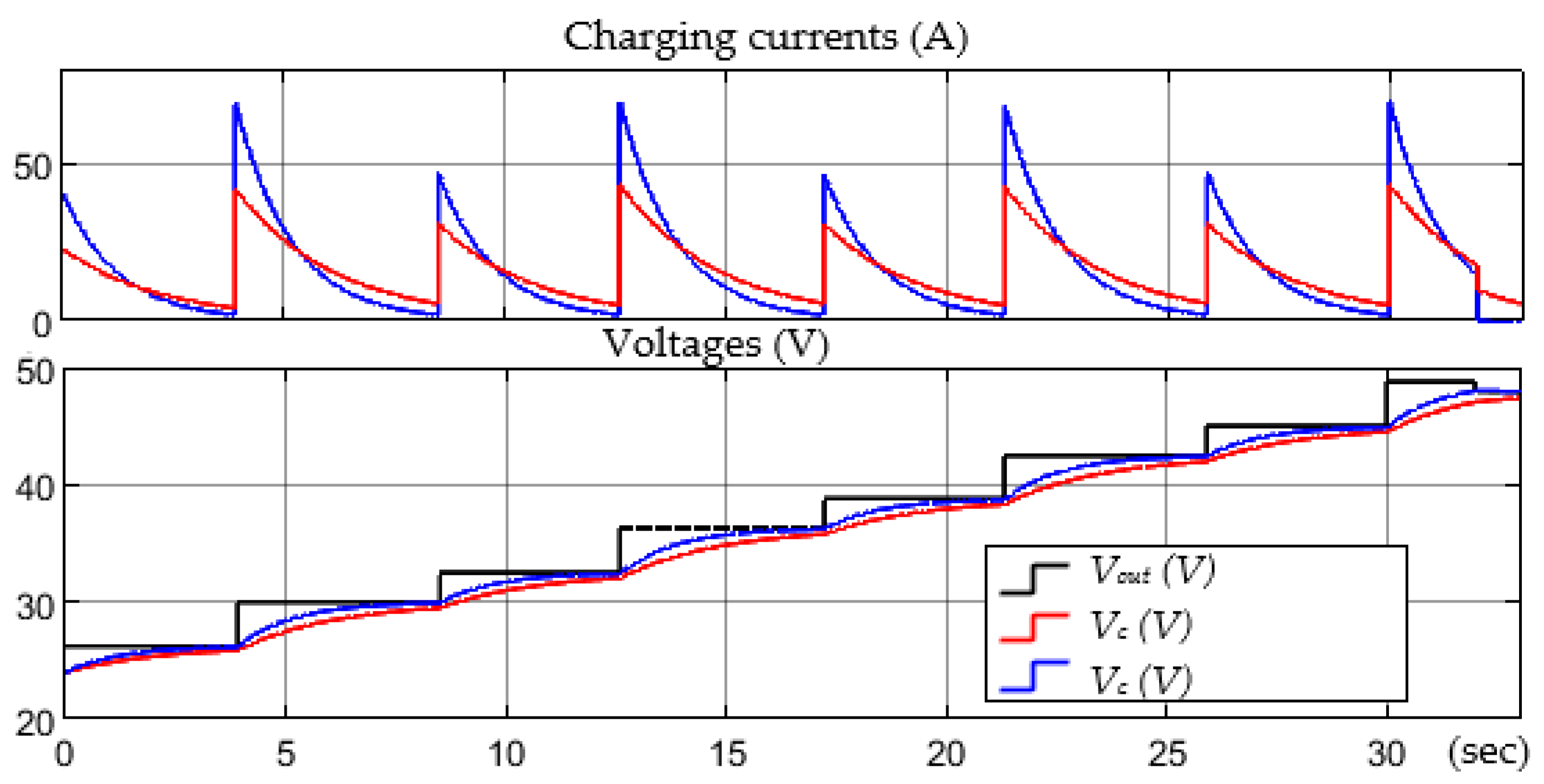

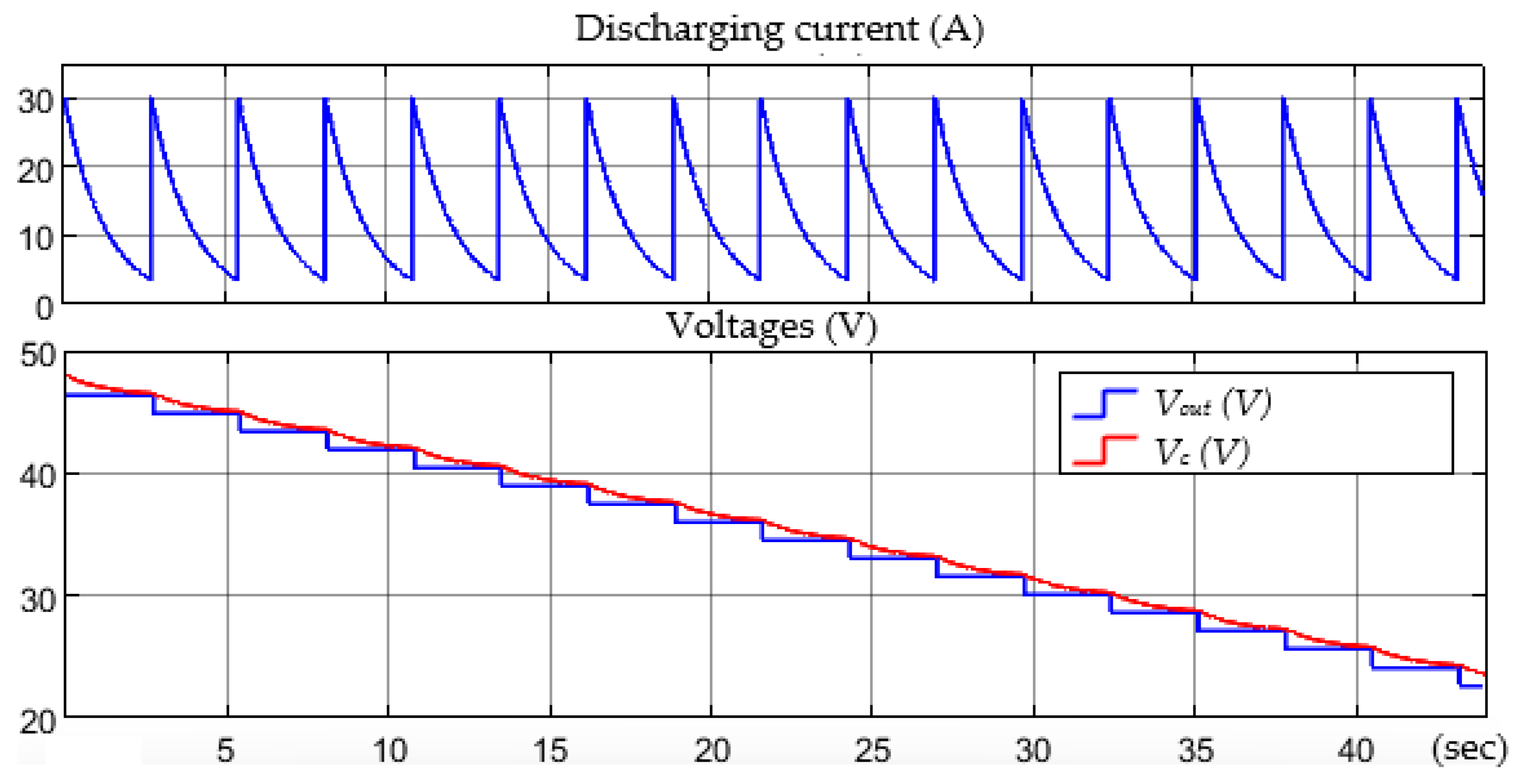

3.3. Regulation of Switching the Duty Cycles D0n Depending on the Difference between Vout and VC

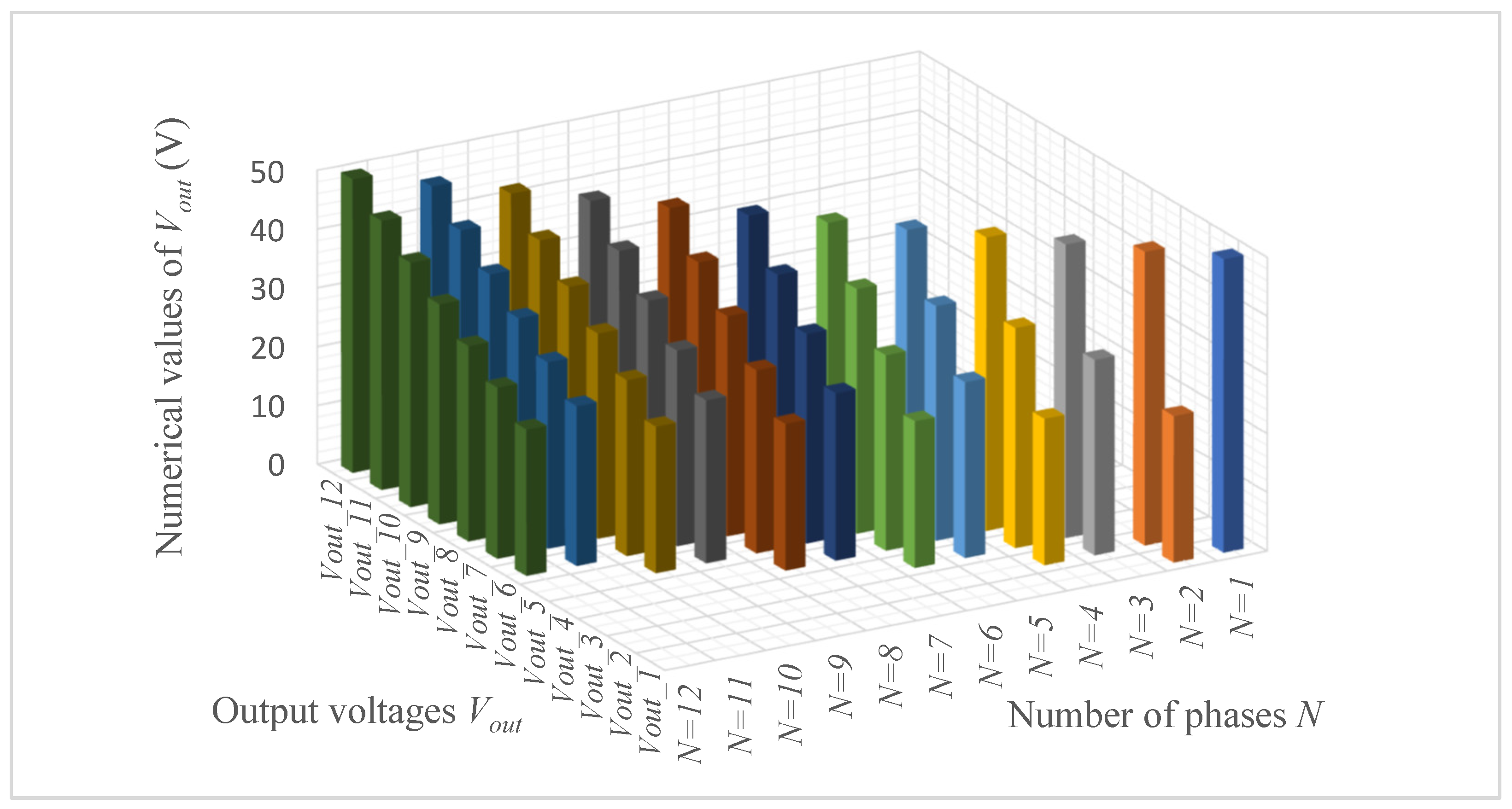

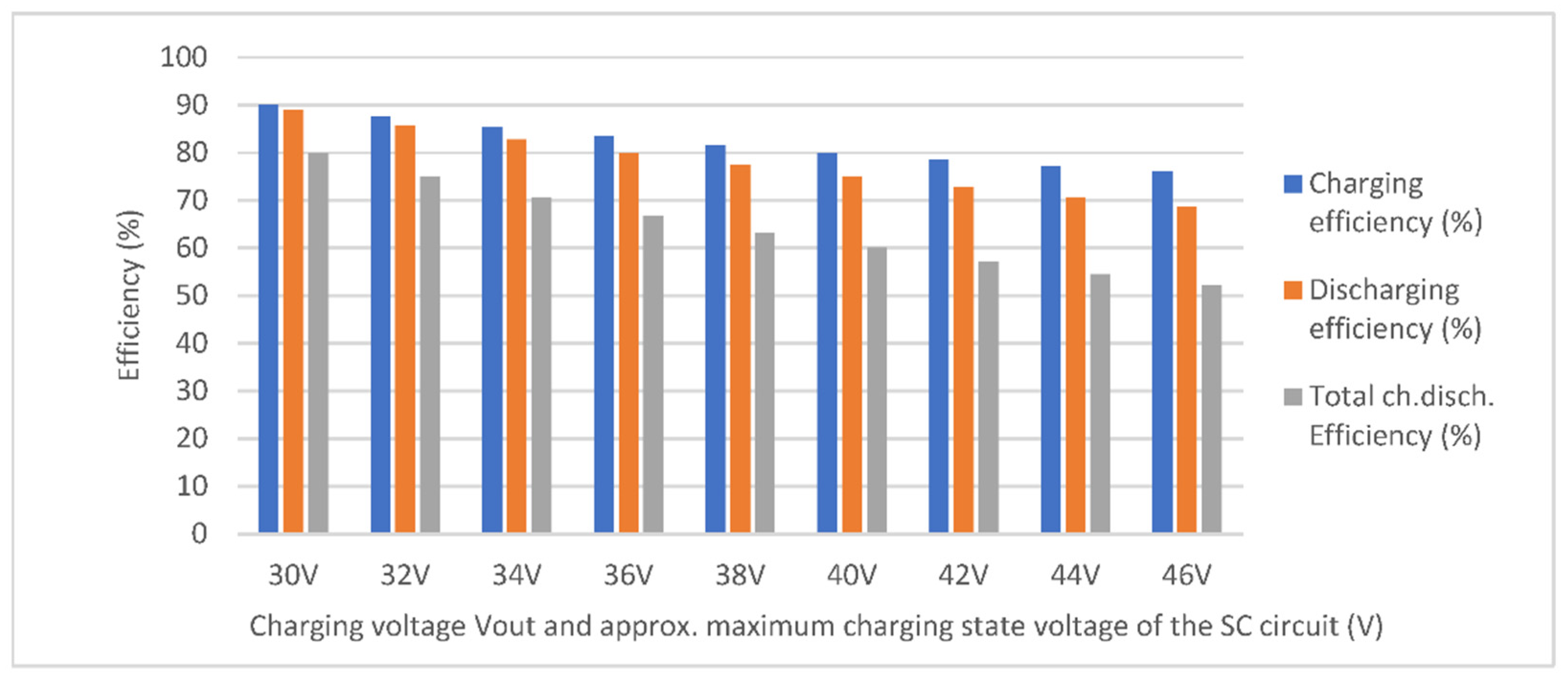

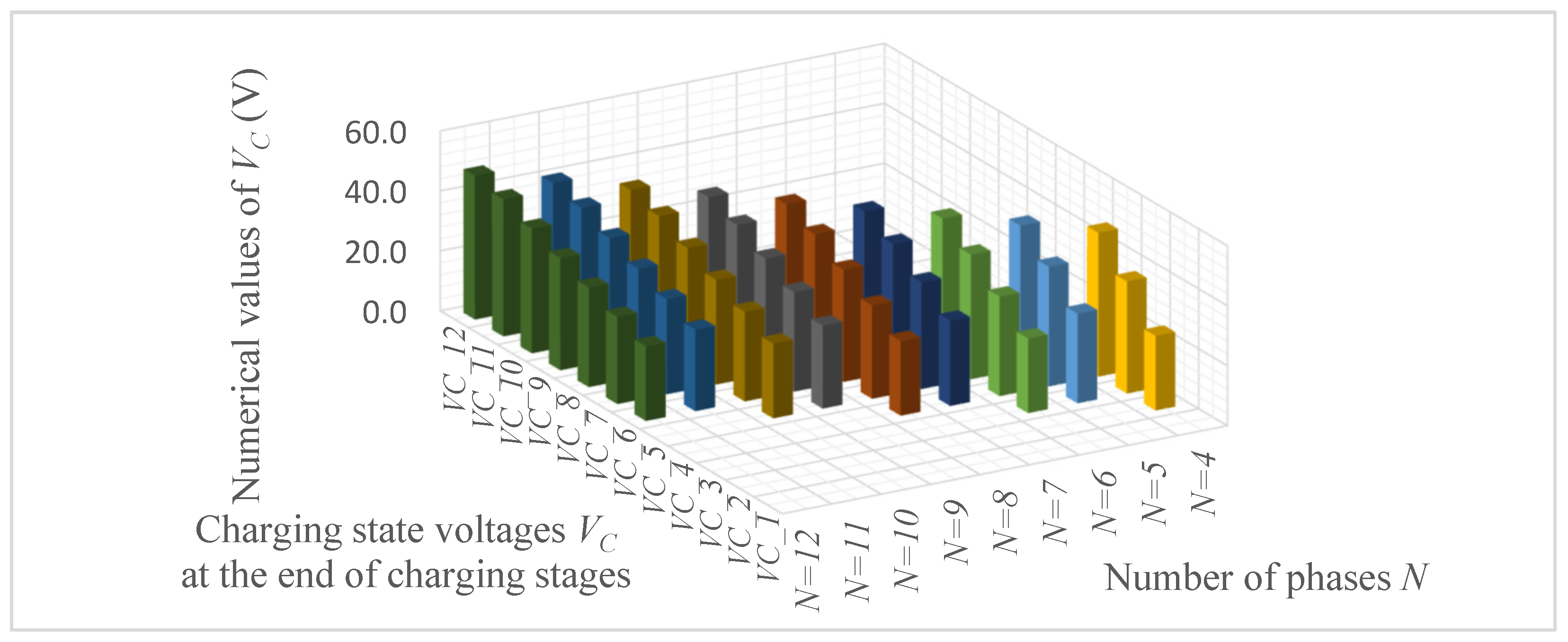

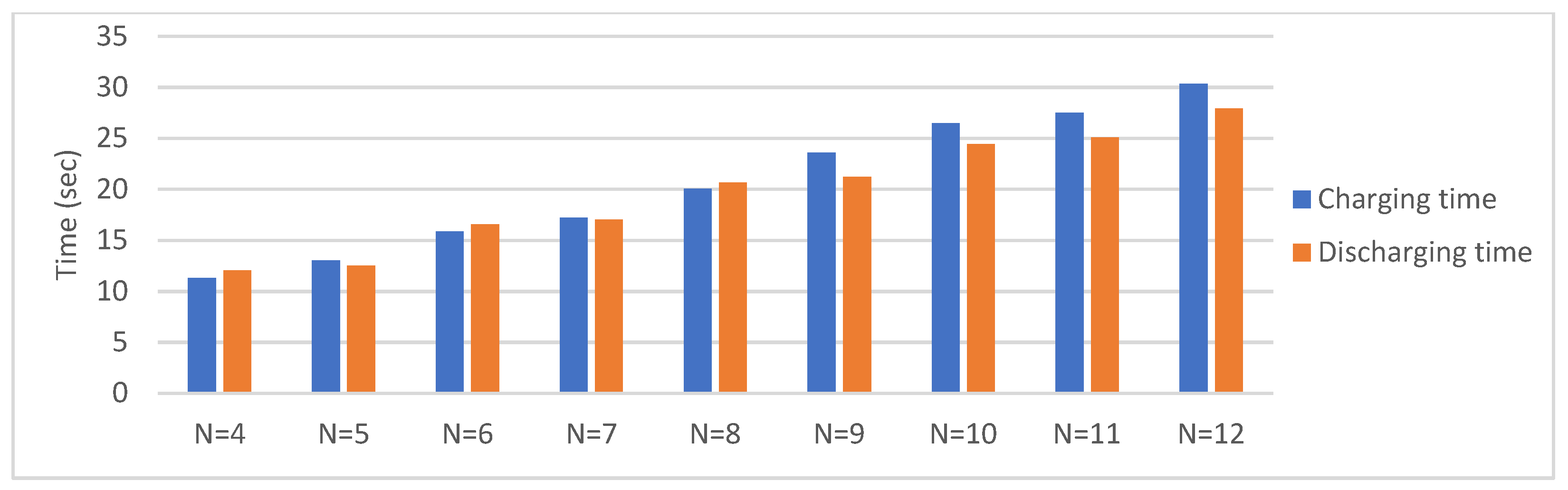

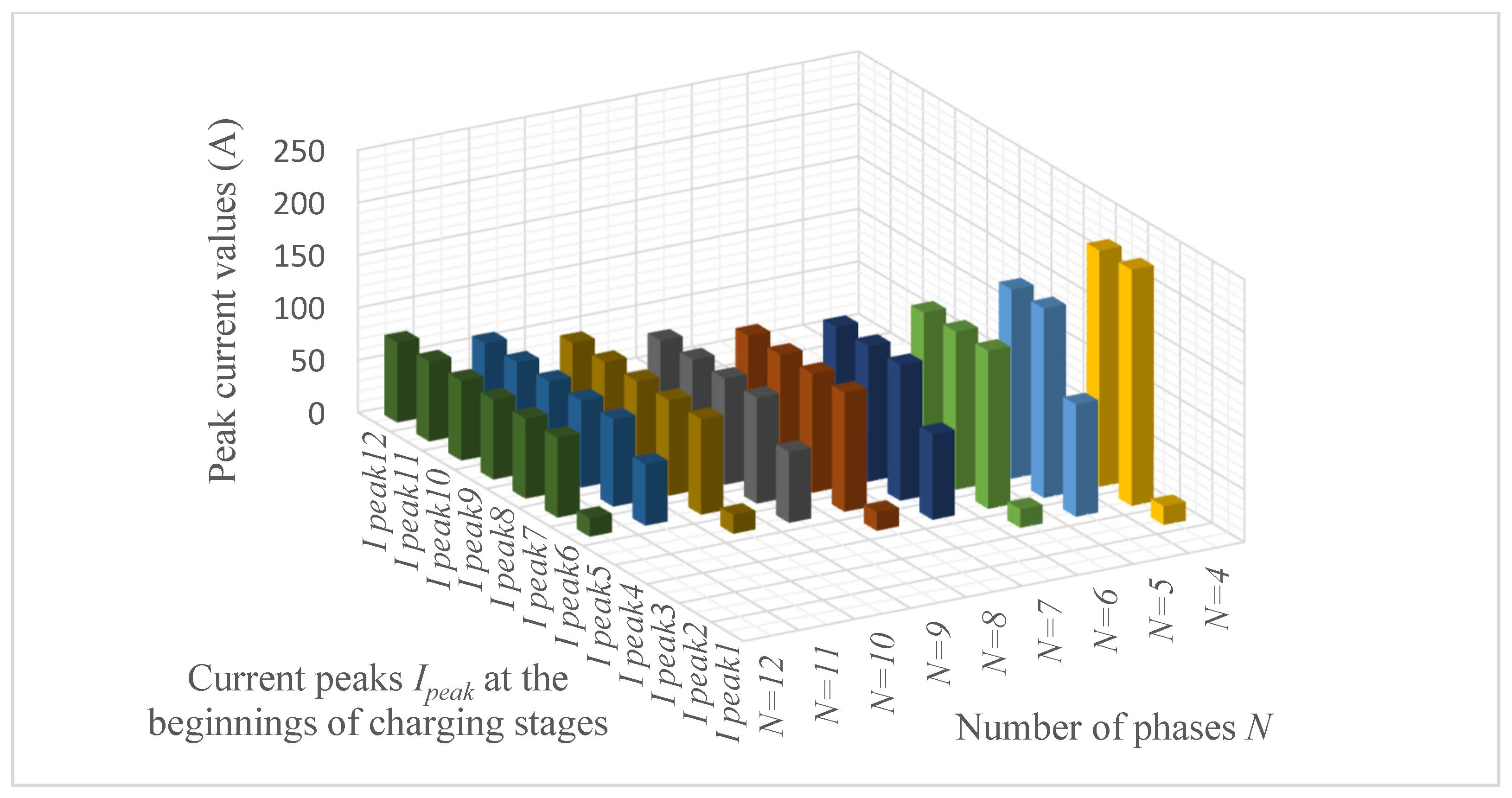

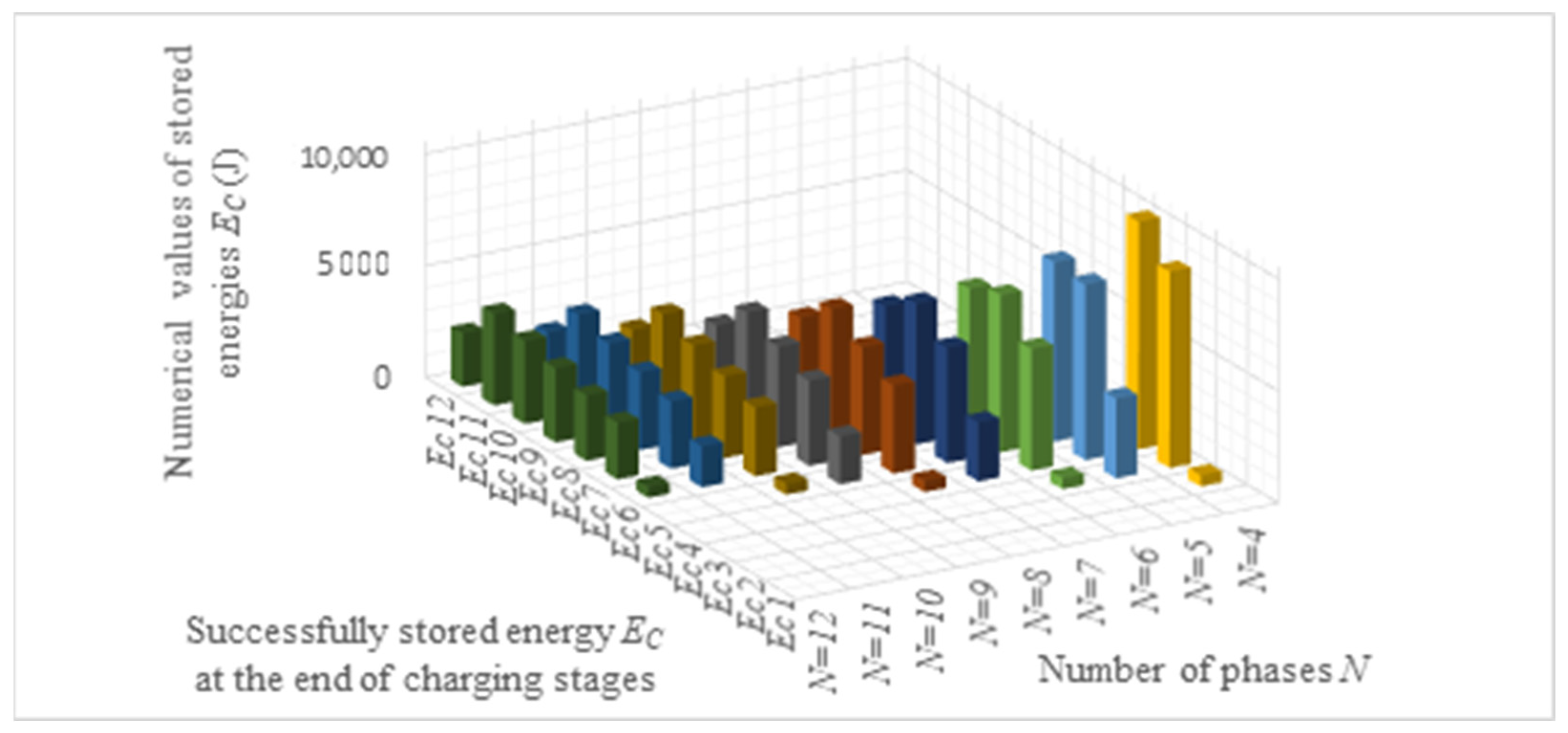

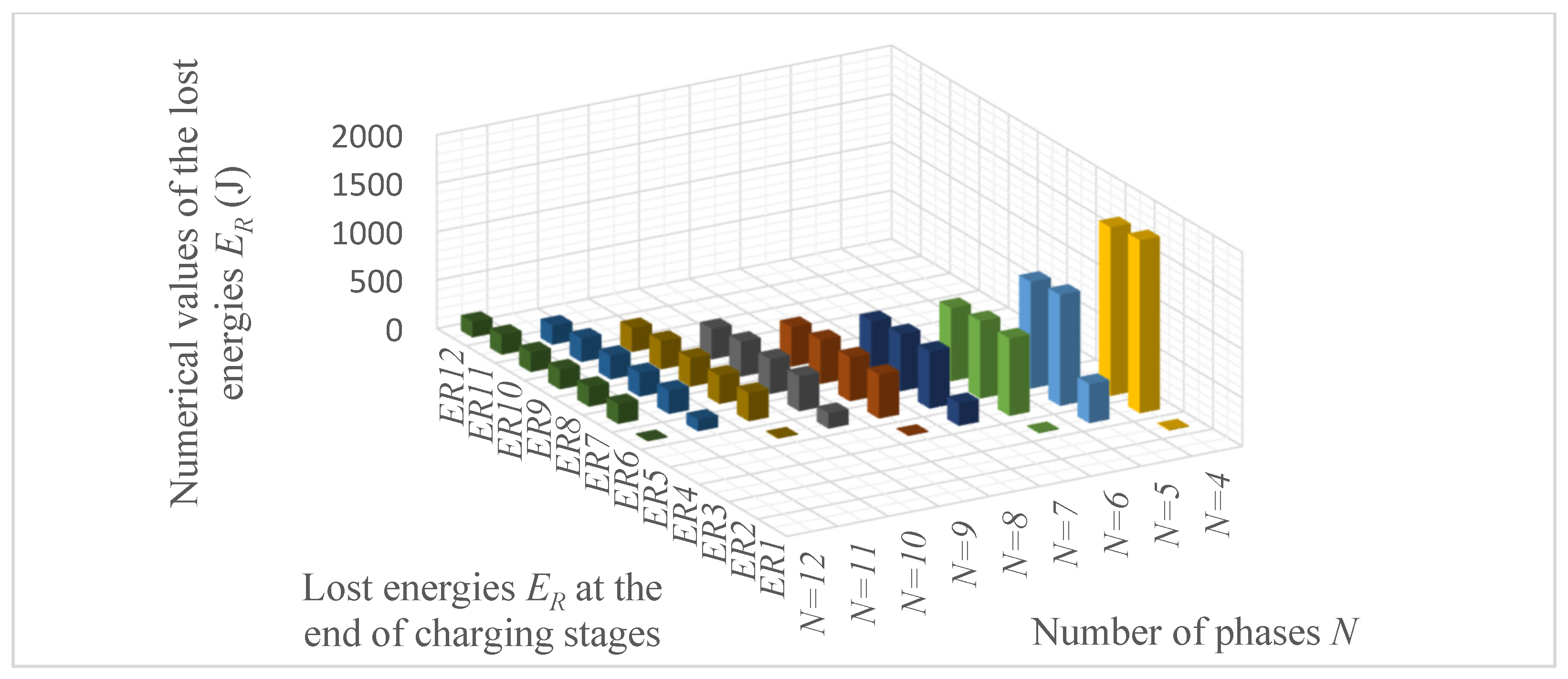

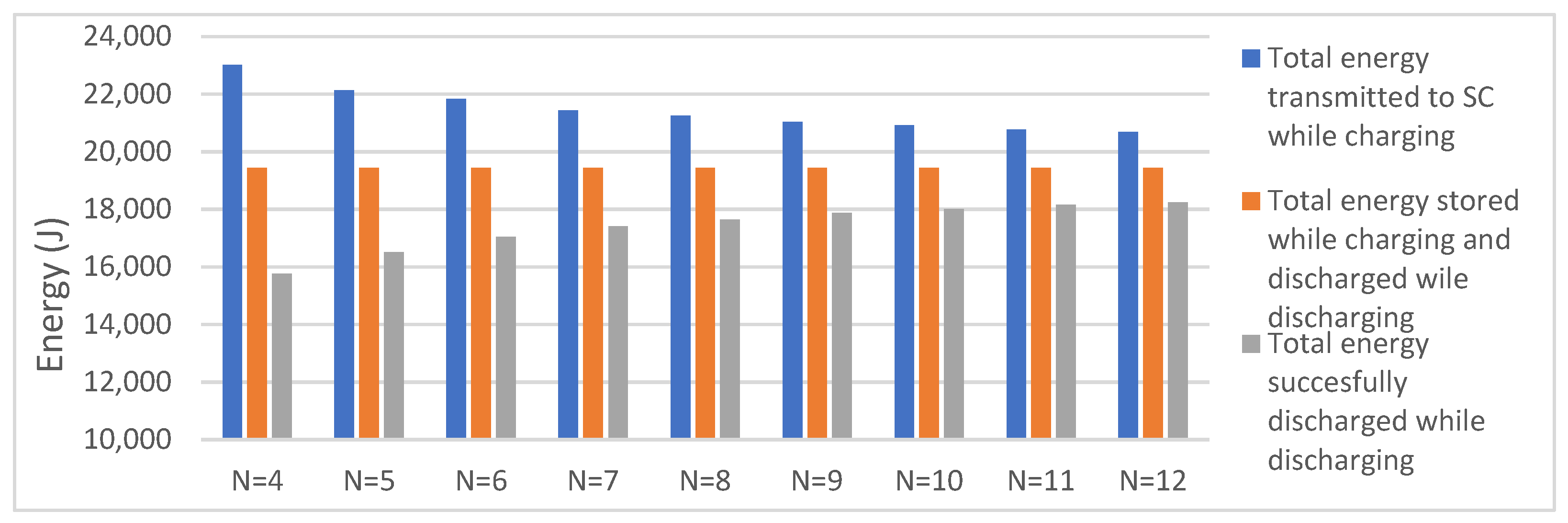

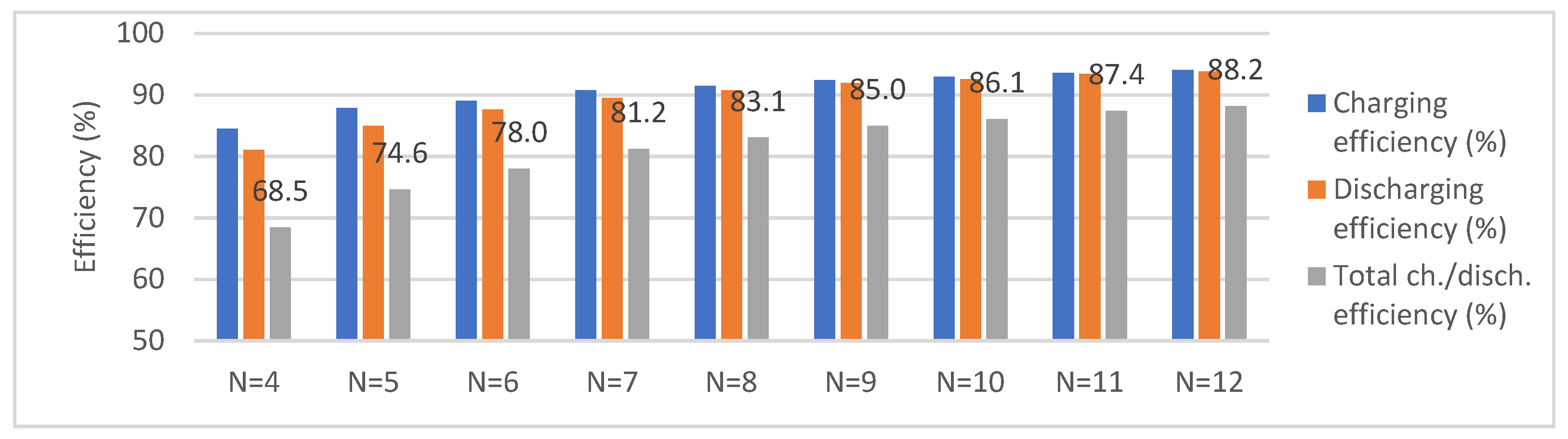

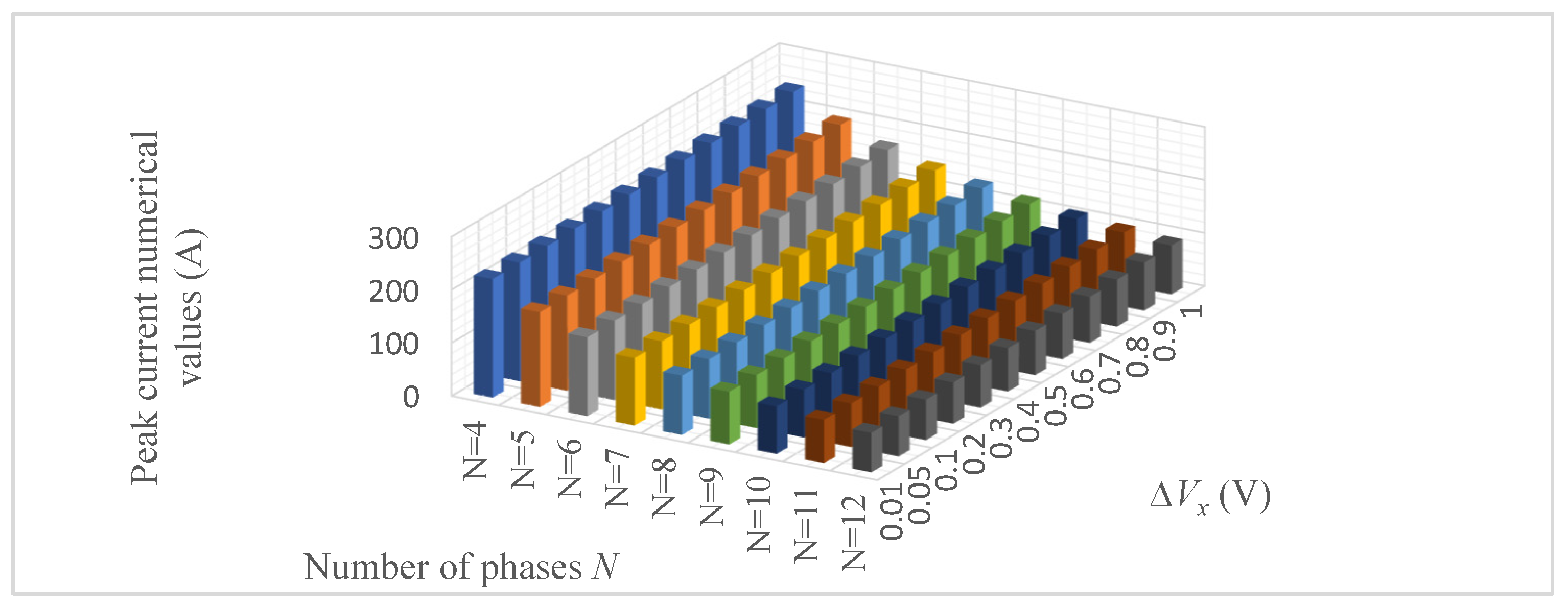

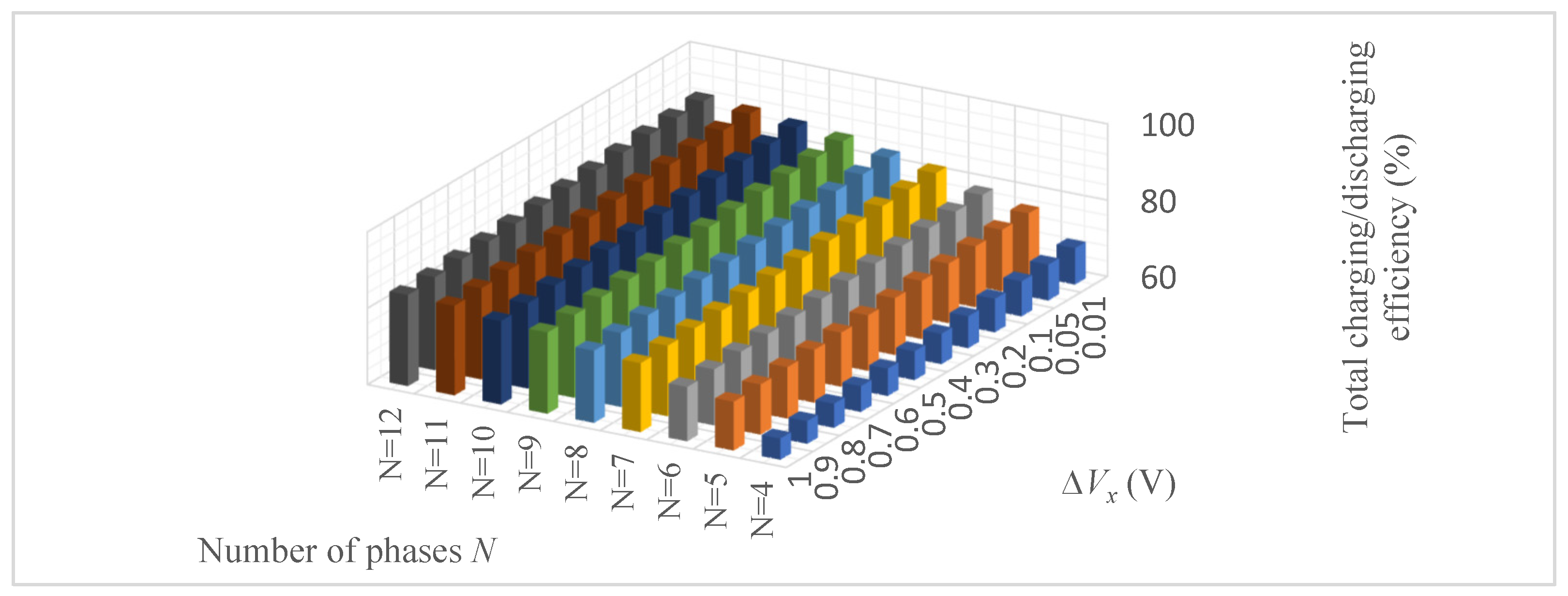

4. Analysis of Supercapacitor Charging and Discharging Efficiency Depending on the Number of Phases

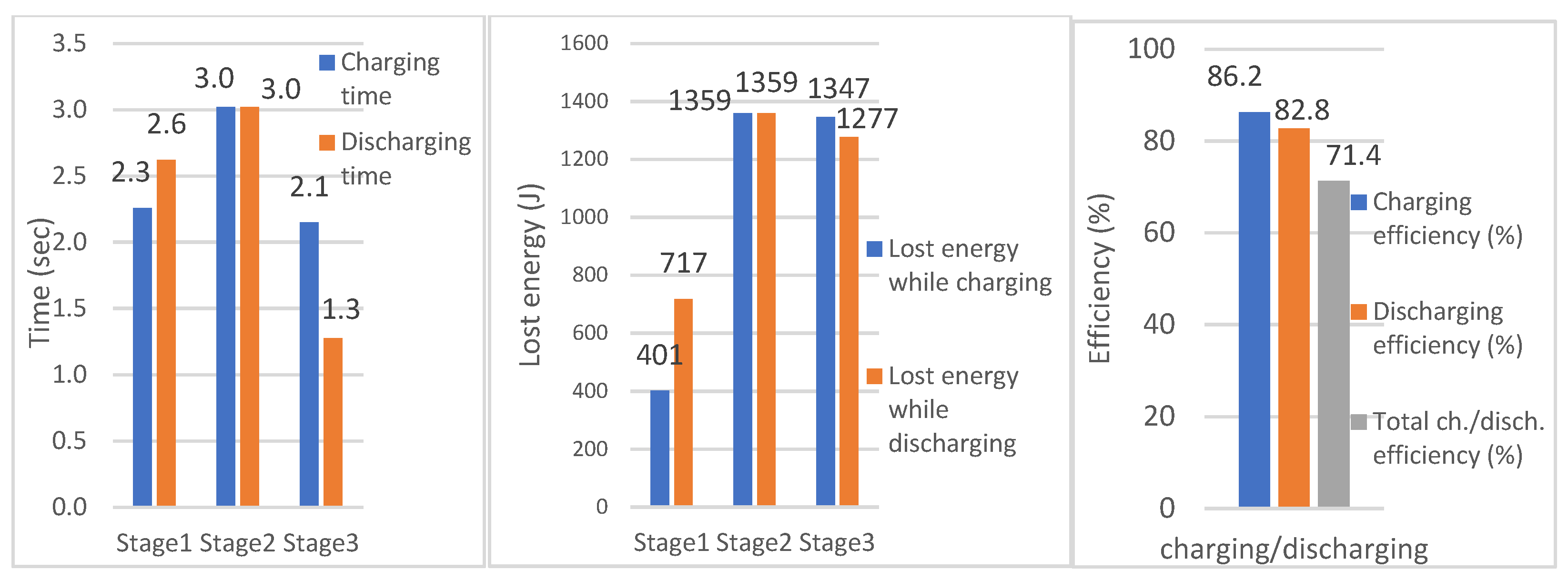

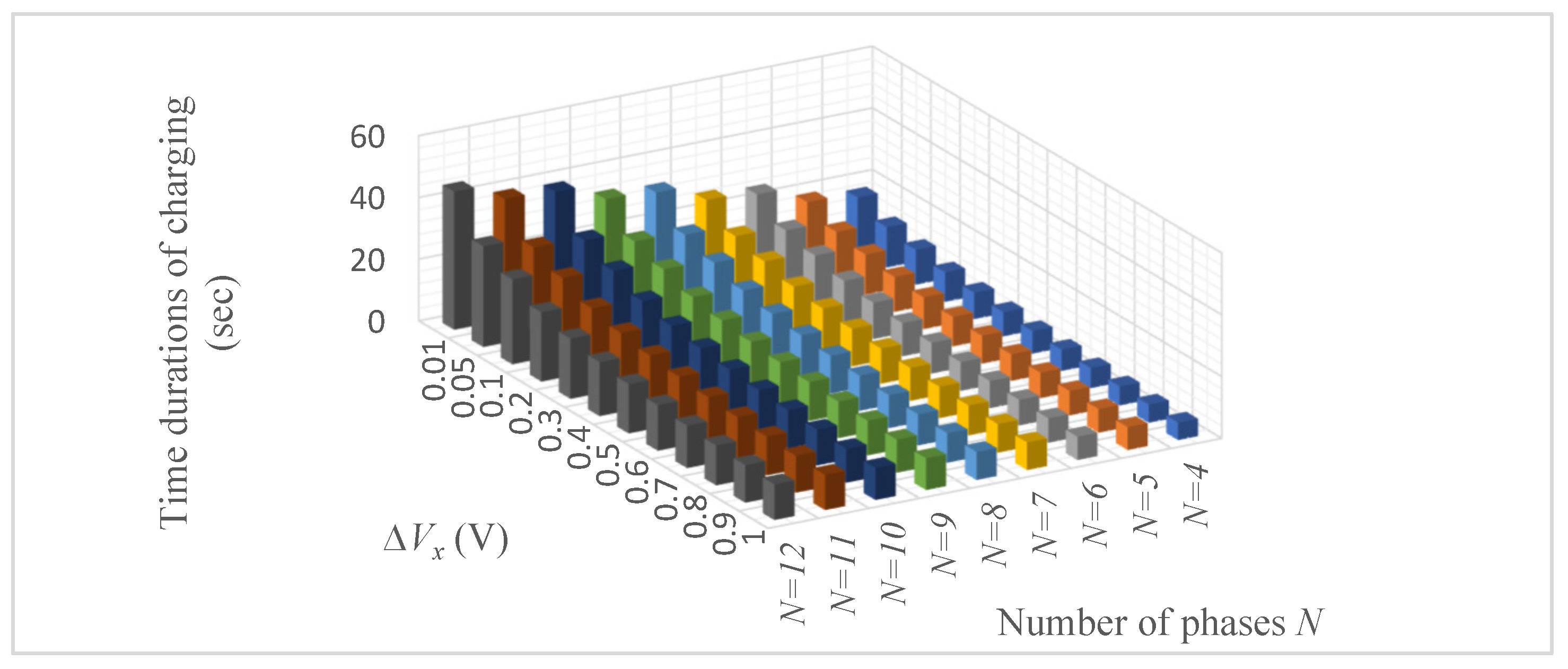

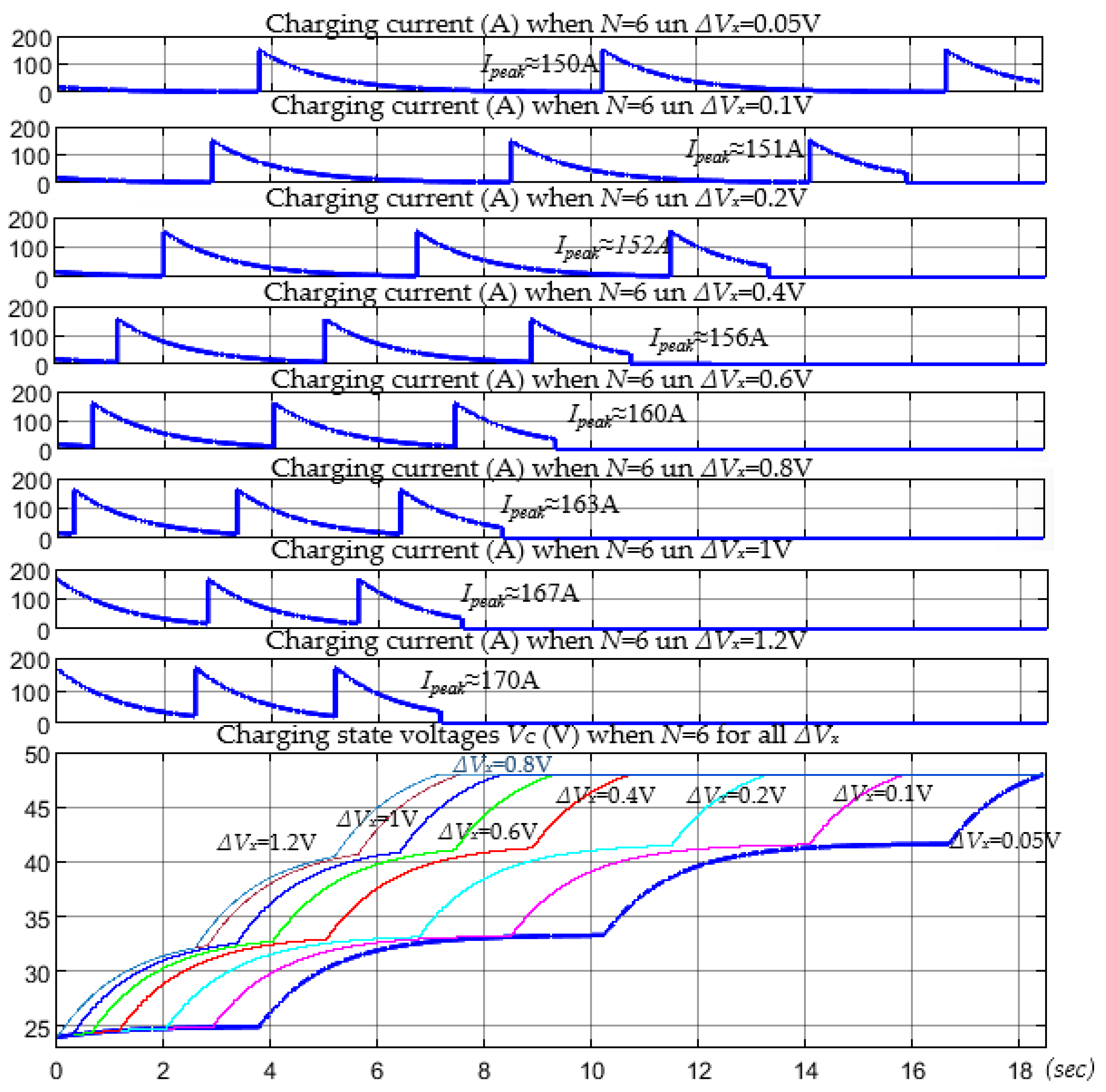

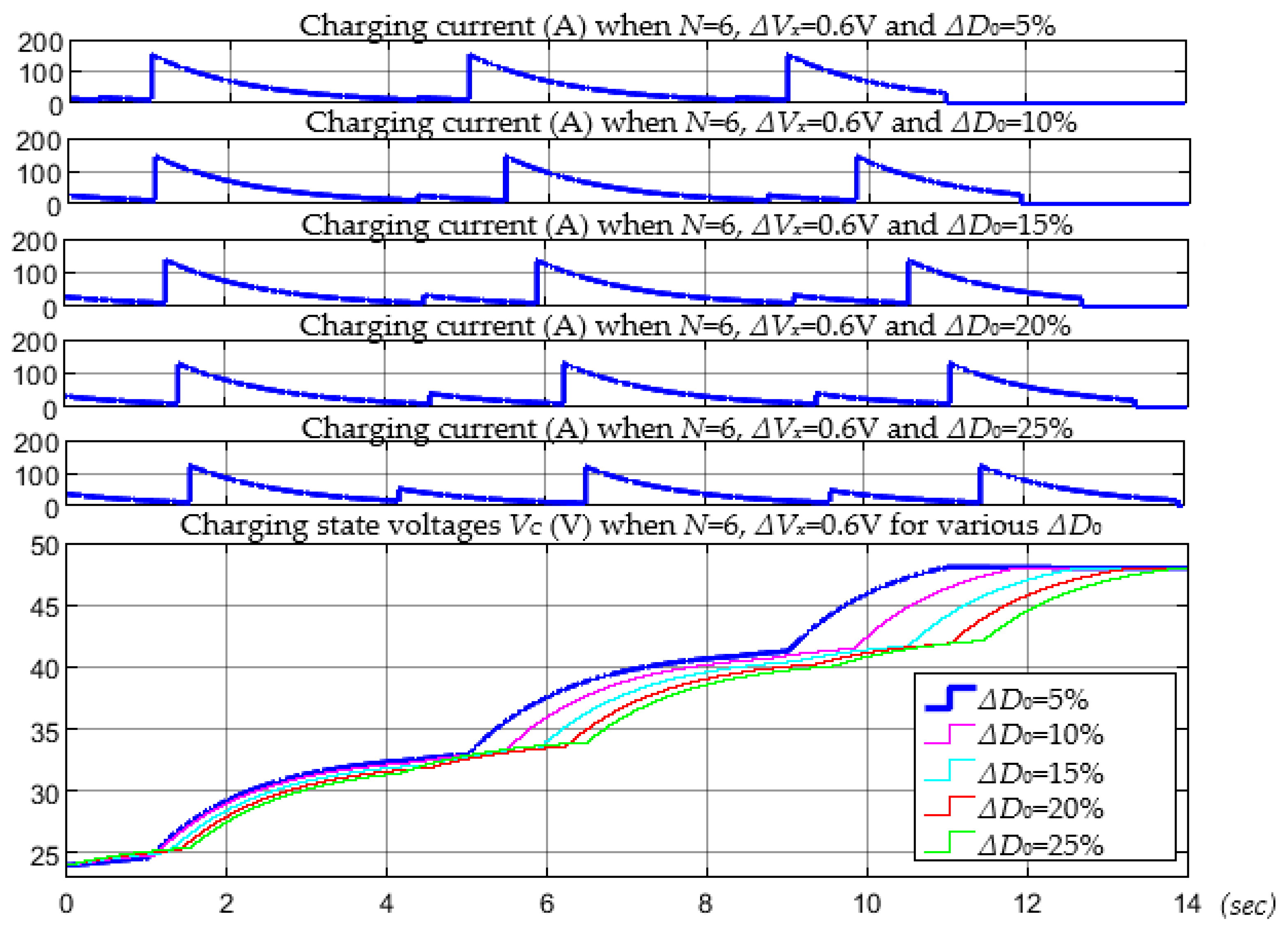

5. Analysis of Supercapacitor Charging Efficiency Depending on Faster Duty Cycle Changes

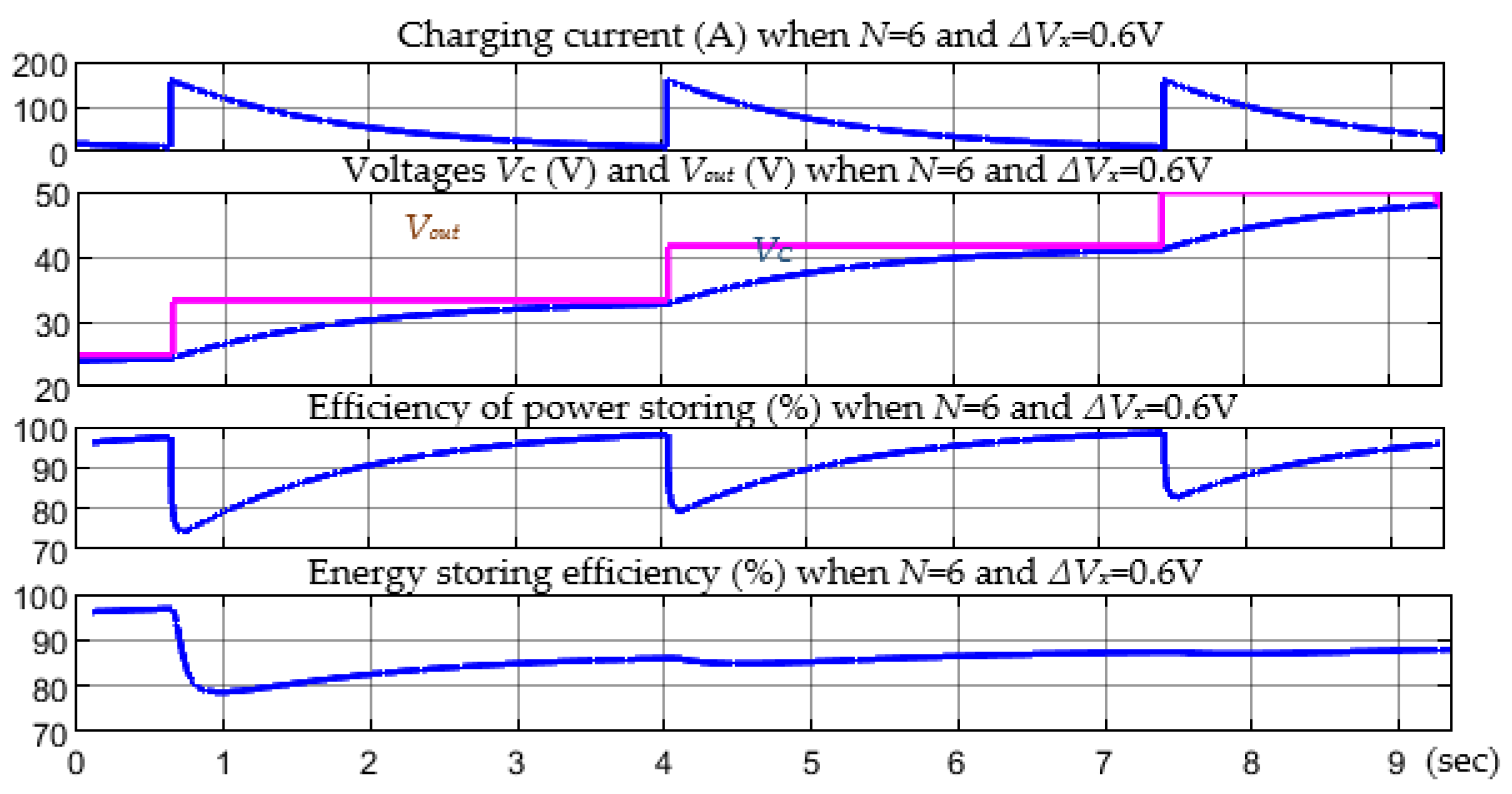

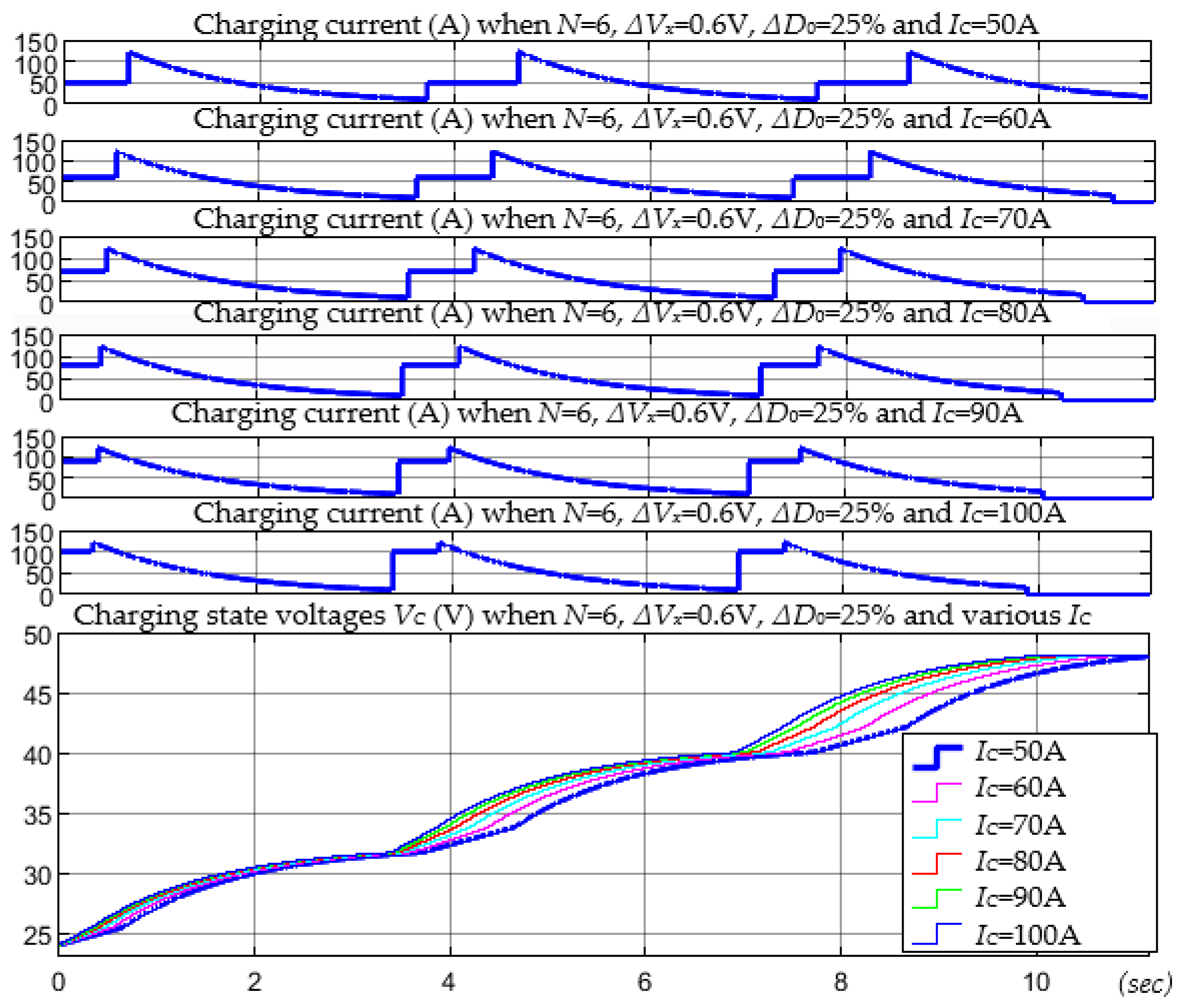

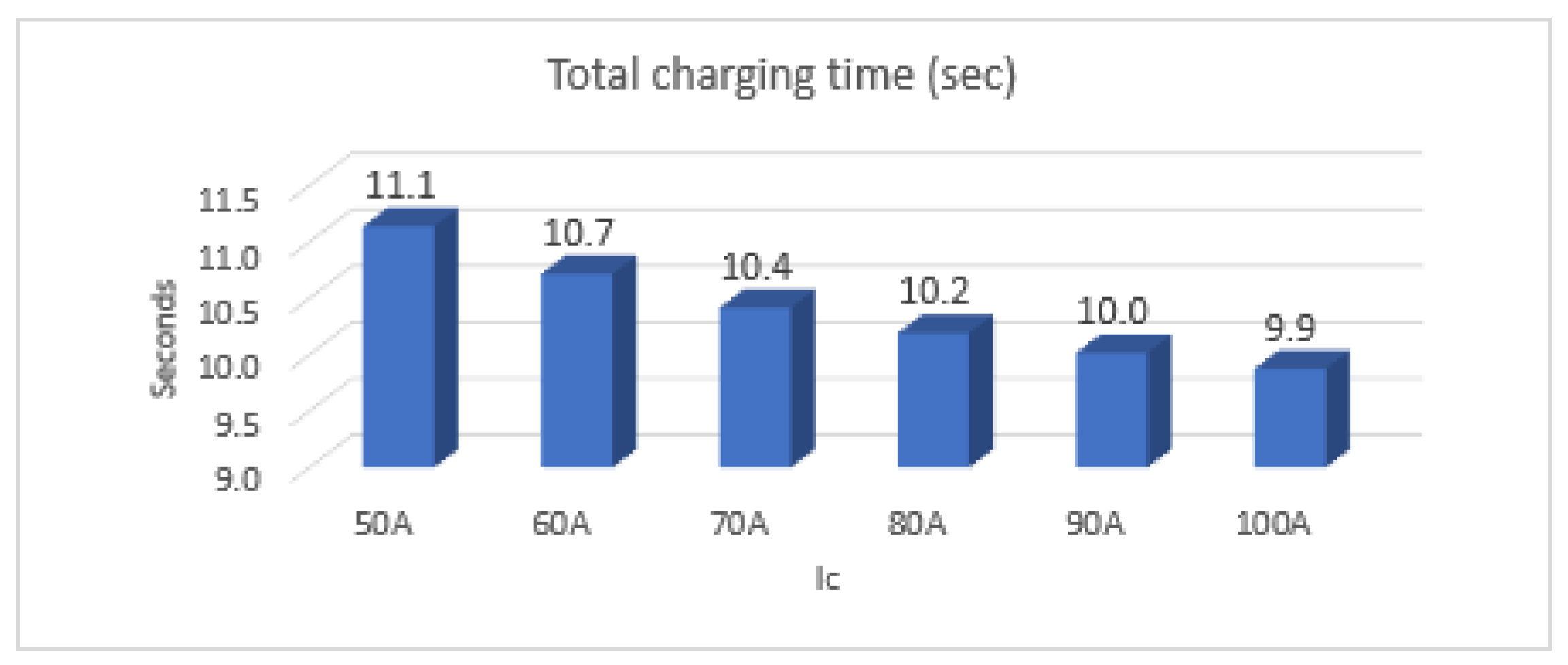

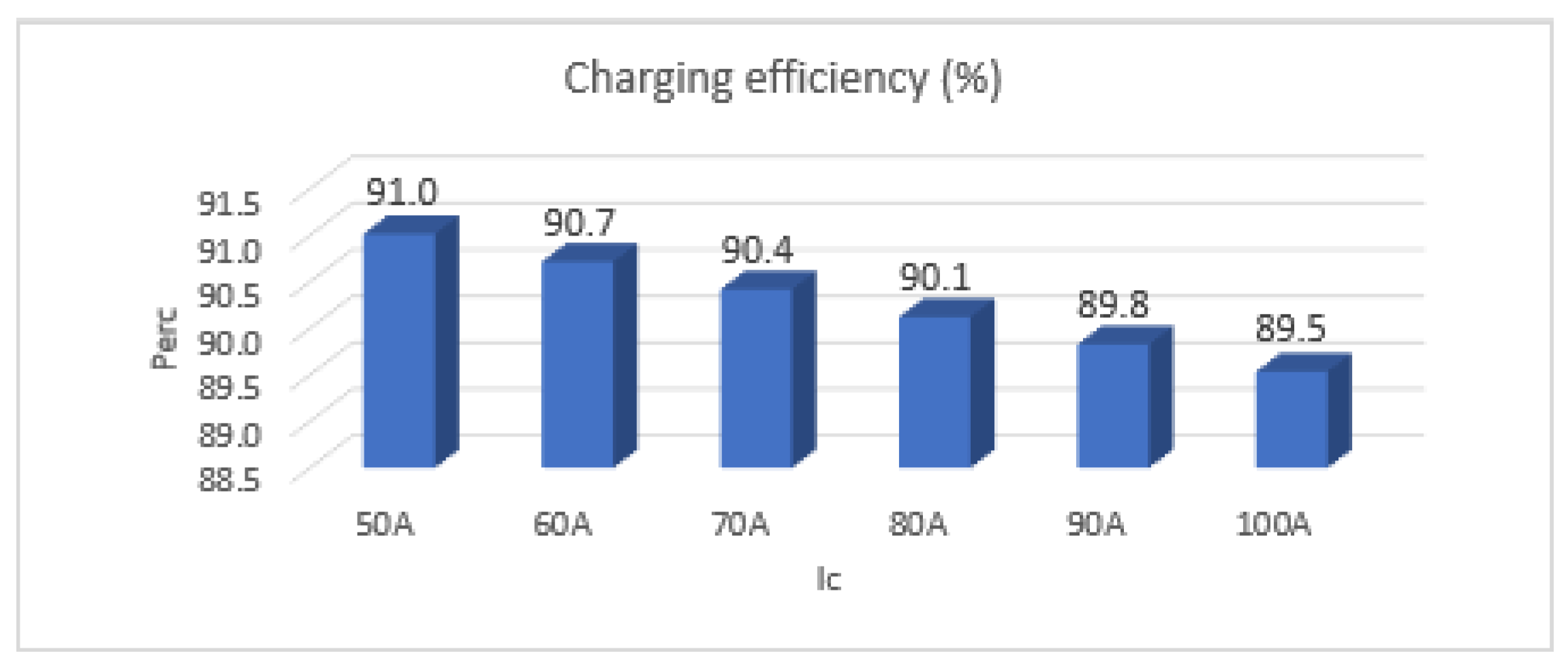

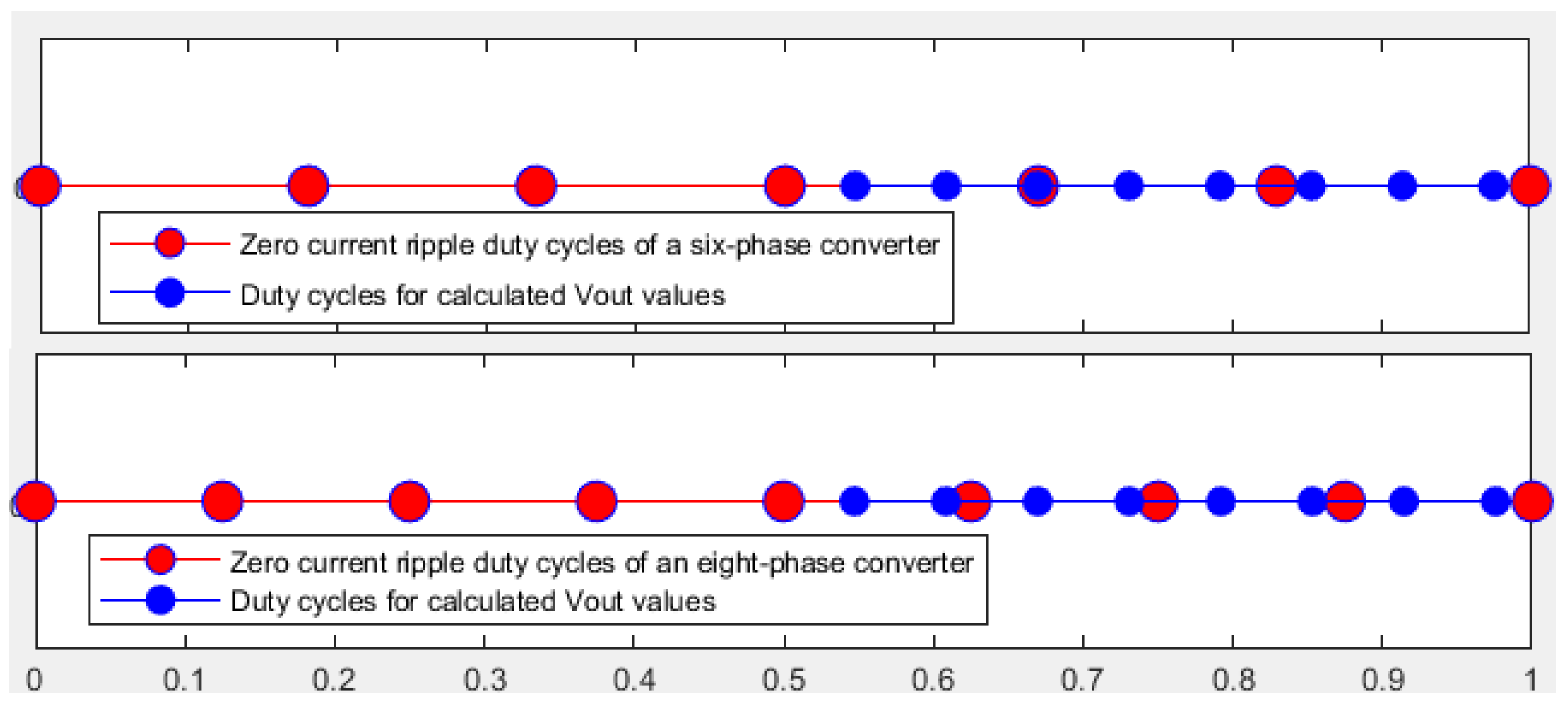

6. Charging and Discharging Utilizing Duty Cycle Regions with Small Current Ripples

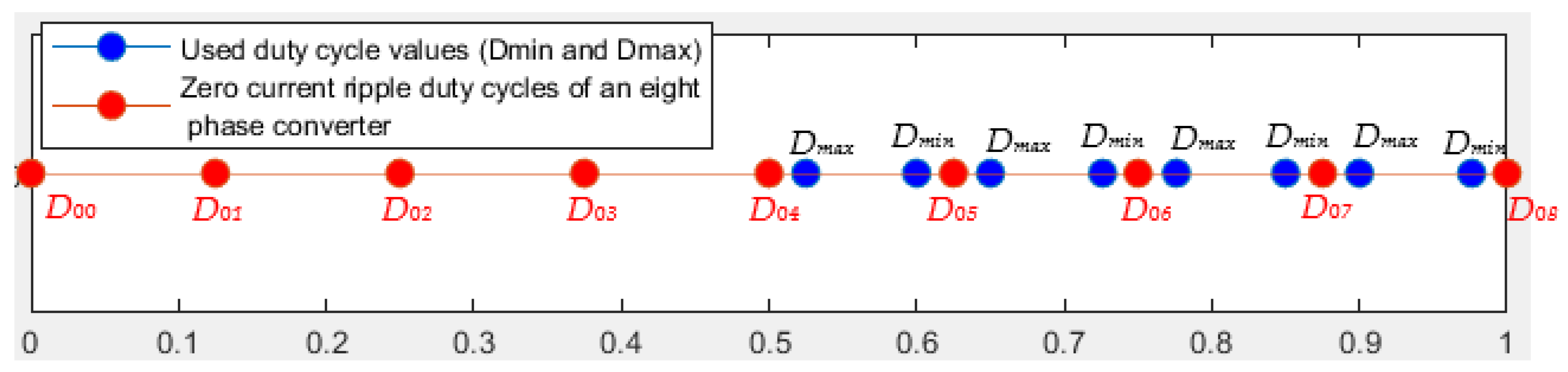

6.1. Strategy with Utilization of Minimum and Maximum Duty Cycles from Regions with Lowest Current Ripple

6.2. Strategy of Combining Constant Voltage Charging and Constant Current Charging

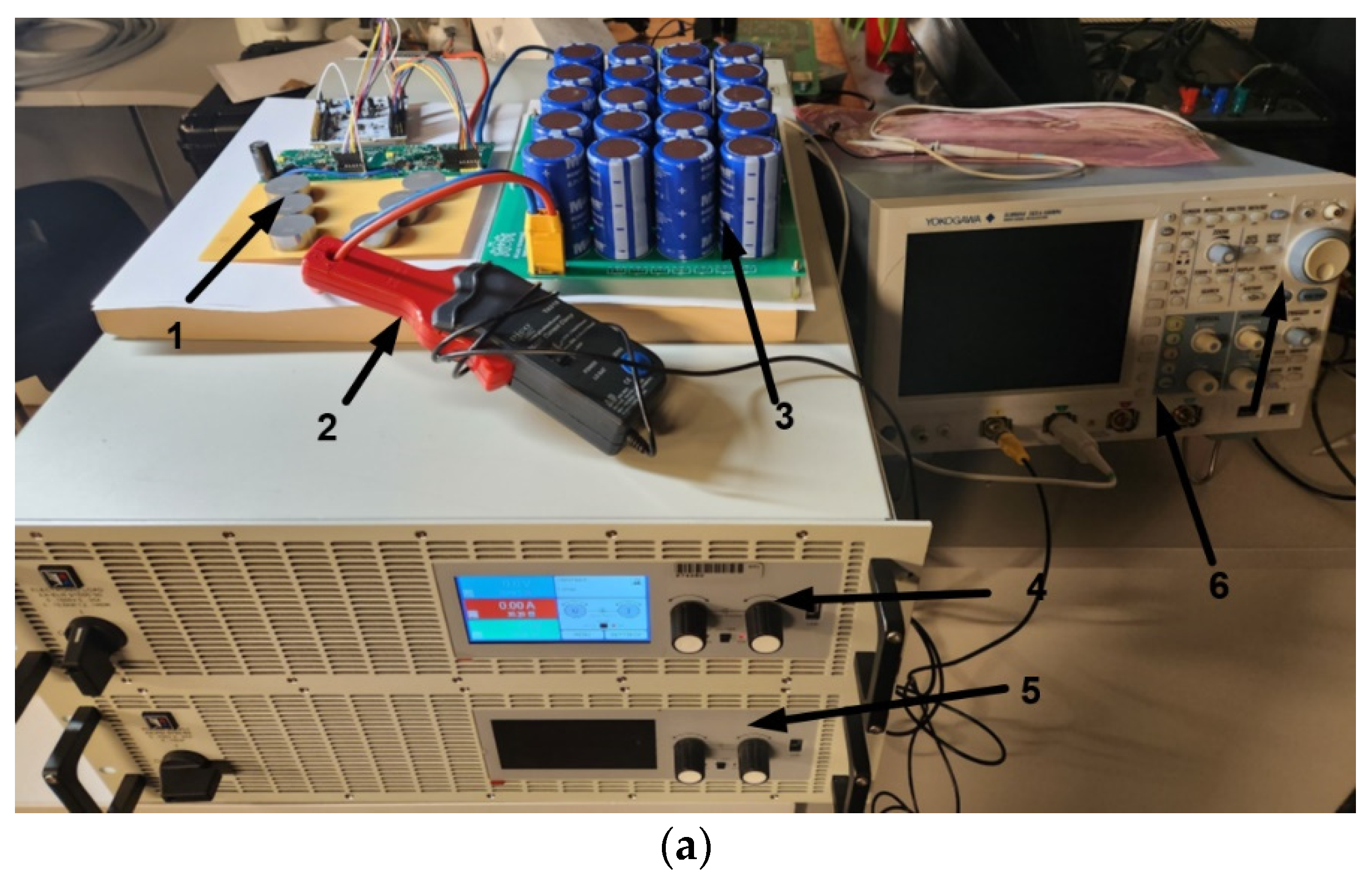

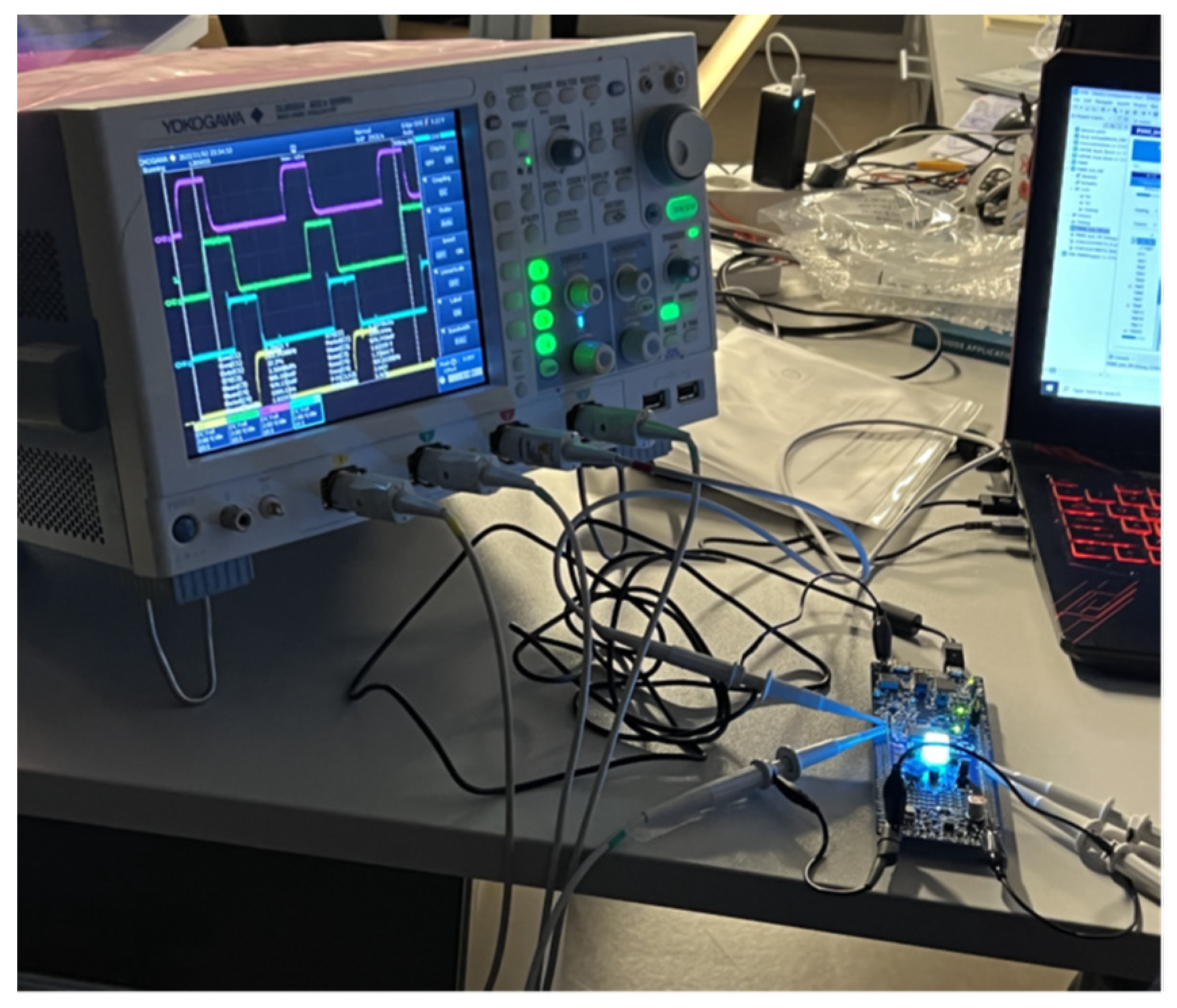

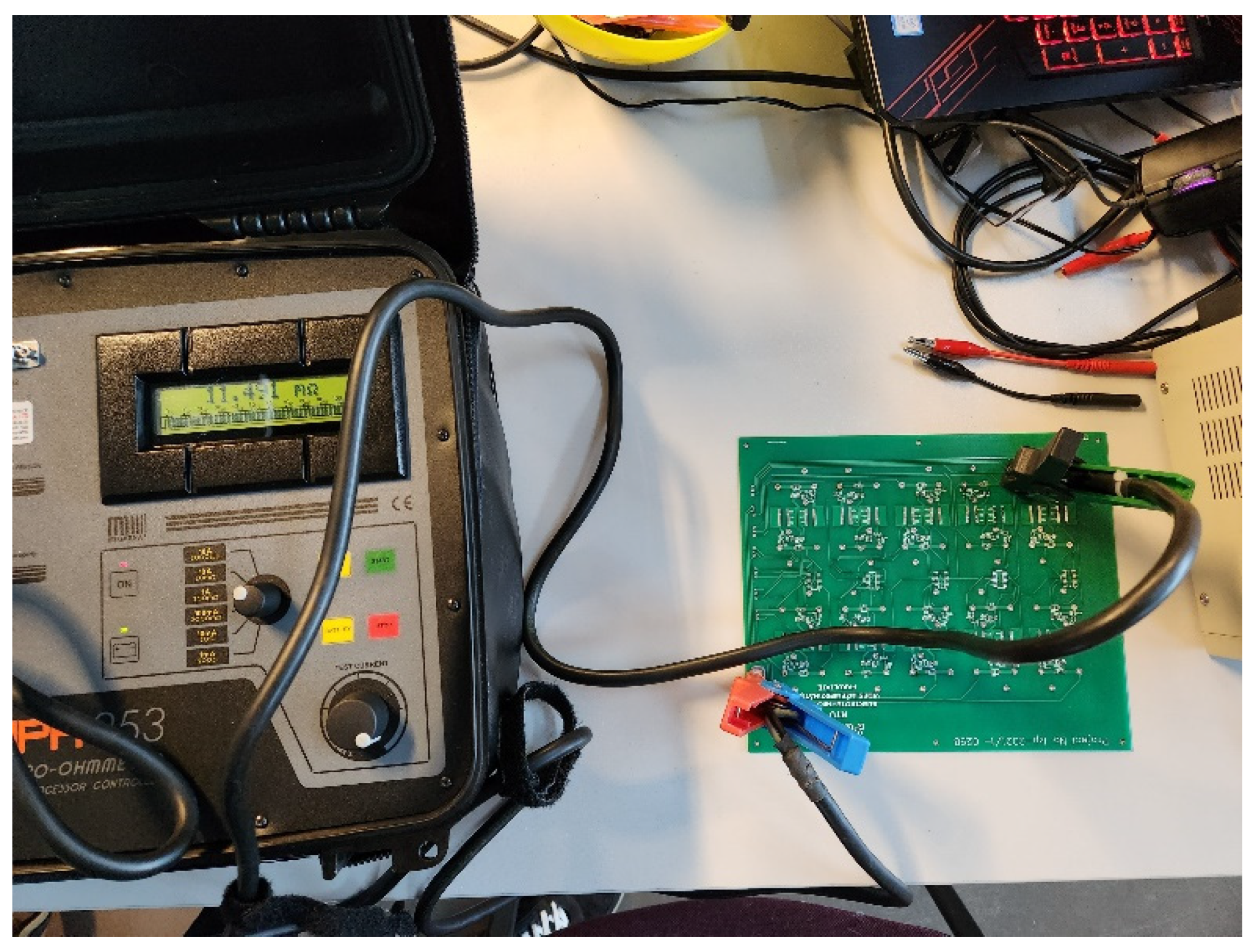

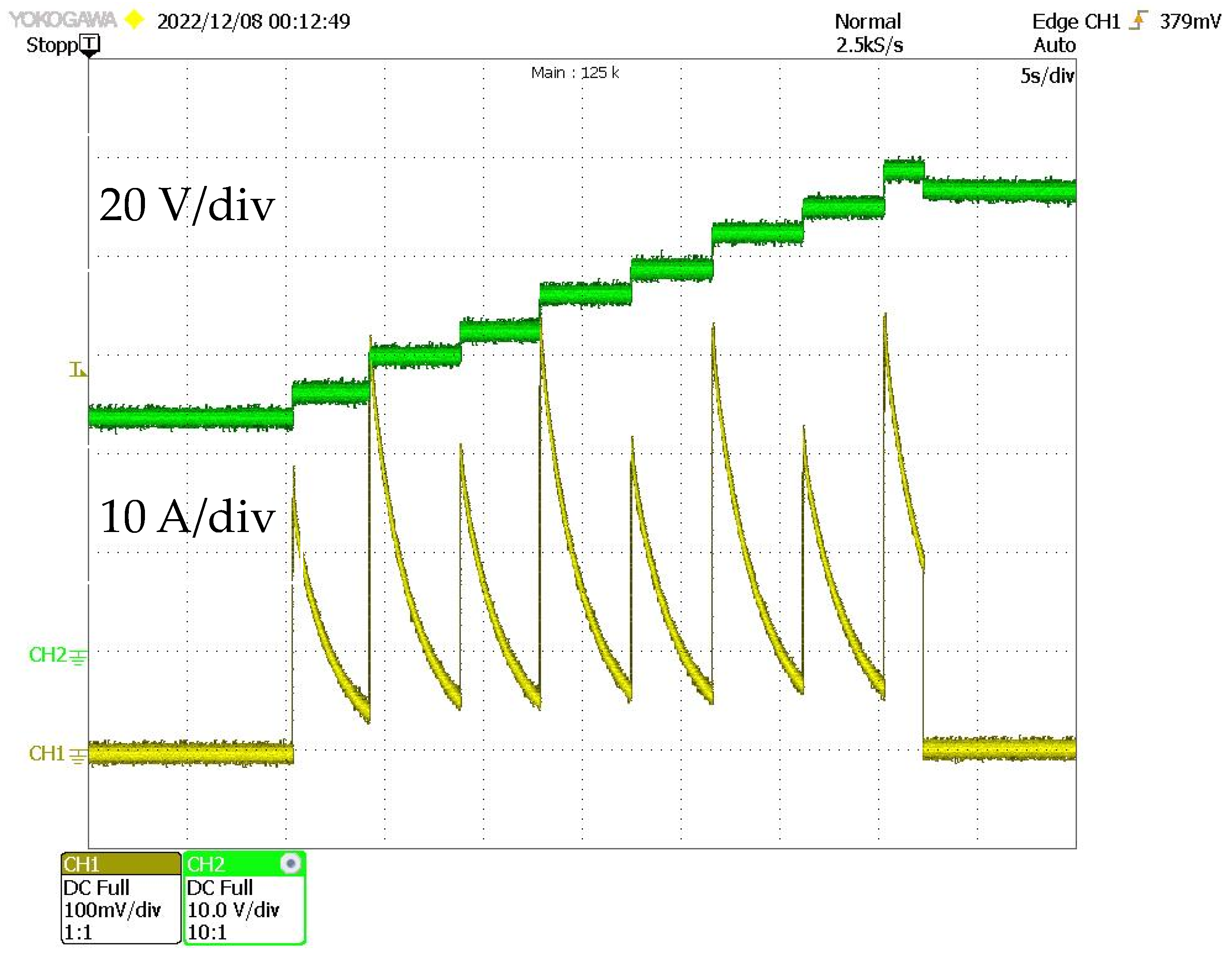

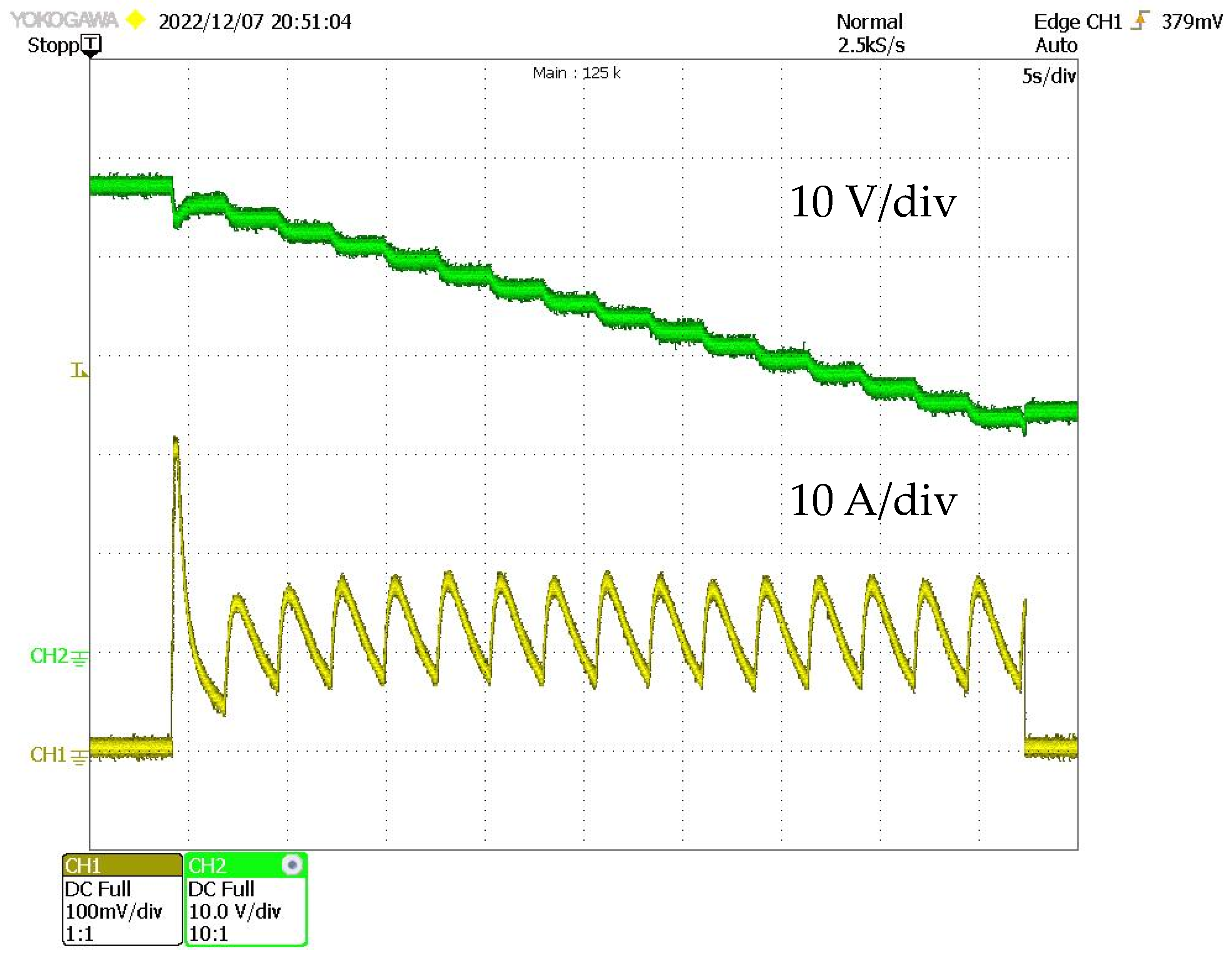

7. Practical Verification of Theoretical Results

8. Discussion

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Elsayed, A.T.; Mohamed, A.A.; Mohammed, O.A. DC microgrids and distribution systems: An overview. Electr. Power Syst. Res. 2015, 119, 407–417. [Google Scholar] [CrossRef]

- Meike, D.; Pellicciari, M.; Berselli, G. Energy Efficient Use of Multirobot Production Lines in the Automotive Industry: Detailed System Modeling and Optimization. IEEE Trans. Autom. Sci. Eng. 2014, 11, 798–809. [Google Scholar] [CrossRef]

- Khan, M.A.; Zeb, K.; Sathishkumar, P.; Ali, M.U.; Uddin, W.; Hussain, S.; Ishfaq, M.; Khan, I.; Cho, H.-G.; Kim, H.-J. A Novel Supercapacitor/Lithium-Ion Hybrid Energy System with a Fuzzy Logic-Controlled Fast Charging and Intelligent Energy Management System. Electronics 2018, 7, 63. [Google Scholar] [CrossRef] [Green Version]

- Zhou, H.; Duong, T.; Sing, S.T.; Khambadkone, A.M. Interleaved bi-directional Dual Active Bridge DC-DC converter for interfacing ultracapacitor in micro-grid application. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010; pp. 2229–2234. [Google Scholar] [CrossRef]

- Barati, F.; Ahmadi, B. Current sharing in non-coupled interleaved bi-directional boost converters for supercapacitor applications. In Proceedings of the 2015 IEEE 6th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aachen, Germany, 22–25 June 2015; pp. 1–5. [Google Scholar] [CrossRef]

- Rimondi, M.; Mandrioli, R.; Cirimele, V.; Pittala, L.K.; Ricco, M.; Grandi, G. Design of an Integrated, Six-Phase, Interleaved, Synchronous DC/DC Boost Converter on a Fuel-Cell-Powered Sport Catamaran. Designs 2022, 6, 113. [Google Scholar] [CrossRef]

- Waffler, S.; Biela, J.; Kolar, J.W. Output ripple reduction of an automotive multi-phase bi-directional dc-dc converter. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 2184–2190. [Google Scholar] [CrossRef]

- Schumacher, D.; Magne, P.; Preindl, M.; Bilgin, B.; Emadi, A. Closed loop control of a six phase interleaved bidirectional dc-dc boost converter for an EV/HEV application. In Proceedings of the 2016 IEEE Transportation Electrification Conference and Expo (ITEC), Dearborn, MI, USA, 27–29 June 2016; pp. 1–7. [Google Scholar] [CrossRef]

- Tran, D.; Chakraborty, S.; Lan, Y.; van Mierlo, J.; Hegazy, O. Optimized Multiport DC/DC Converter for Vehicle Drivetrains: Topology and Design Optimization. Appl. Sci. 2018, 8, 1351. [Google Scholar] [CrossRef] [Green Version]

- Gorji, S.A.; Sahebi, H.G.; Ektesabi, M.; Rad, A.B. Topologies and Control Schemes of Bidirectional DC–DC Power Converters: An Overview. IEEE Access 2019, 7, 117997–118019. [Google Scholar] [CrossRef]

- Xu, Q.; Vafamand, N.; Chen, L.; Dragičević, T.; Xie, L.; Blaabjerg, F. Review on Advanced Control Technologies for Bidirectional DC/DC Converters in DC Microgrids. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 1205–1221. [Google Scholar] [CrossRef]

- Chen, C.-J.; Zeng, Z.-Y.; Cheng, C.-H.; Lin, F.-T. Comprehensive Analysis and Design of Current-Balance Loop in Constant On-Time Controlled Multi-Phase Buck Converter. IEEE Access 2020, 8, 184752–184764. [Google Scholar] [CrossRef]

- Abu-Qahouq, J.A. Analysis and Design of N-Phase Current-Sharing Autotuning Controller. IEEE Trans. Power Electron. 2010, 25, 1641–1651. [Google Scholar] [CrossRef]

- Yao, Z.; Lu, S. A Simple Approach to Enhance the Effectiveness of Passive Currents Balancing in an Interleaved Multiphase Bidirectional DC–DC Converter. IEEE Trans. Power Electron. 2019, 34, 7242–7255. [Google Scholar] [CrossRef]

- Konjedic, T.; Korošec, L.; Truntič, M.; Restrepo, C.; Rodič, M.; Milanovič, M. DCM-Based Zero-Voltage Switching Control of a Bidirectional DC–DC Converter With Variable Switching Frequency. IEEE Trans. Power Electron. 2016, 31, 3273–3288. [Google Scholar] [CrossRef]

- Li, J.; Sullivan, C.R.; Schultz, A. Coupled-inductor design optimization for fast-response low-voltage DC-DC converters. In Proceedings of the APEC. Seventeenth Annual IEEE Applied Power Electronics Conference and Exposition, Dallas, TX, USA, 10–14 March 2002; Volume 2, pp. 817–823. [Google Scholar] [CrossRef] [Green Version]

- Forest, F.; Meynard, T.A.; Laboure, E.; Costan, V.; Sarraute, E.; Cuniere, A.; Martire, T. Optimization of the Supply Voltage System in Interleaved Converters Using Intercell Transformers. IEEE Trans. Power Electron. 2007, 22, 934–942. [Google Scholar] [CrossRef]

- Nagaraja, H.N.; Kastha, D.; Petra, A. Design Principles of a Symmetrically Coupled Inductor Structure for Multiphase Synchronous Buck Converters. IEEE Trans. Ind. Electron. 2011, 58, 988–997. [Google Scholar] [CrossRef]

- He, L.; Lin, Z.; Tan, Q.; Lu, F.; Zeng, T. Interleaved High Step-Up Current Sharing Converter with Coupled Inductors. Electronics 2021, 10, 436. [Google Scholar] [CrossRef]

- Zhang, S. Analysis and minimization of the input current ripple of Interleaved Boost Converter. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 852–856. [Google Scholar] [CrossRef]

- Grbović, P.J. Closed form analysis of N-cell interleaved two-level DC-DC converters: The DC bus capacitor current stress. In Proceedings of the 2013 IEEE ECCE Asia Downunder, Melbourne, VIC, Australia, 3–6 June 2013; pp. 122–129. [Google Scholar] [CrossRef]

- Shi, L.; Crow, M.L. Comparison of ultracapacitor electric circuit models. In Proceedings of the 2008 IEEE Power and Energy Society General Meeting—Conversion and Delivery of Electrical Energy in the 21st Century, Pittsburgh, PA, USA, 20–24 July 2008; pp. 1–6. [Google Scholar] [CrossRef]

- Şahİn, M.E.; Blaabjerg, F.; Sangwongwanİch, A. Modelling of supercapacitors based on simplified equivalent circuit. CPSS Trans. Power Electron. Appl. 2021, 6, 31–39. [Google Scholar] [CrossRef]

- Cabrane, Z.; Lee, S.H. Electrical and Mathematical Modeling of Supercapacitors: Comparison. Energies 2022, 15, 693. [Google Scholar] [CrossRef]

- Berrueta, A.; Ursúa, A.; Martín, I.S.; Eftekhari, A.; Sanchis, P. Supercapacitors: Electrical Characteristics, Modeling, Applications, and Future Trends. IEEE Access 2019, 7, 50869–50896. [Google Scholar] [CrossRef]

| Name | Unit | Value |

|---|---|---|

| Inductance L | µH | 1 |

| Output voltage | V | 50 |

| Input voltage | V | 20–48 |

| Power | kW | 3 |

| Switching frequency | kHz | 500 |

| Output capacitor | µF | 100 |

| Input capacitor | µF | 0–25 |

| Transistor on-state resistance | mΩ | 15 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kroičs, K.; Staņa, Ģ. Bidirectional Interleaved DC–DC Converter for Supercapacitor Energy Storage Integration with Reduced Capacitance. Electronics 2023, 12, 126. https://doi.org/10.3390/electronics12010126

Kroičs K, Staņa Ģ. Bidirectional Interleaved DC–DC Converter for Supercapacitor Energy Storage Integration with Reduced Capacitance. Electronics. 2023; 12(1):126. https://doi.org/10.3390/electronics12010126

Chicago/Turabian StyleKroičs, Kaspars, and Ģirts Staņa. 2023. "Bidirectional Interleaved DC–DC Converter for Supercapacitor Energy Storage Integration with Reduced Capacitance" Electronics 12, no. 1: 126. https://doi.org/10.3390/electronics12010126