New Resistor-Less Electronically Controllable ±C Simulator Employing VCII, DVCC, and a Grounded Capacitor

Abstract

:1. Introduction

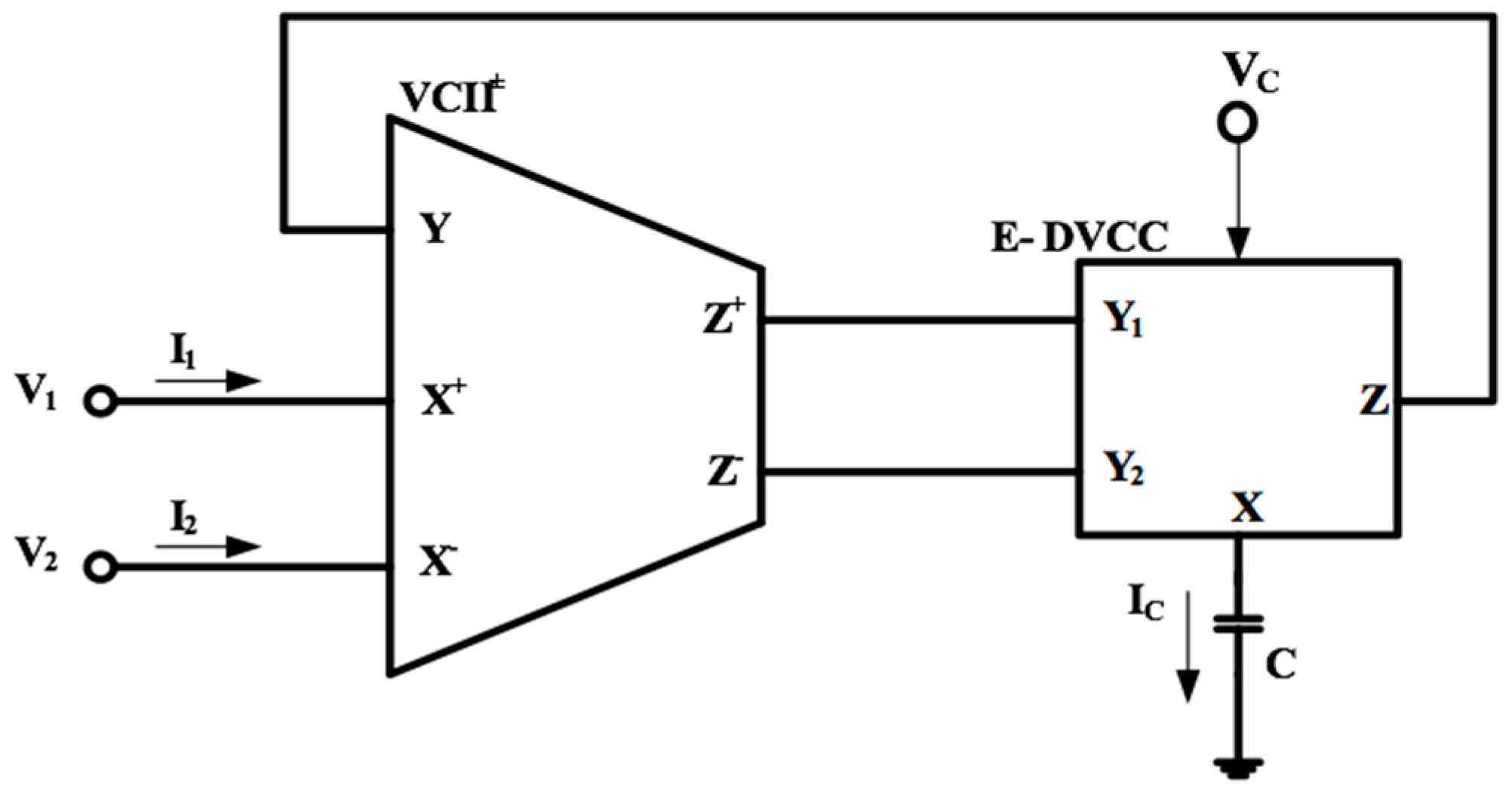

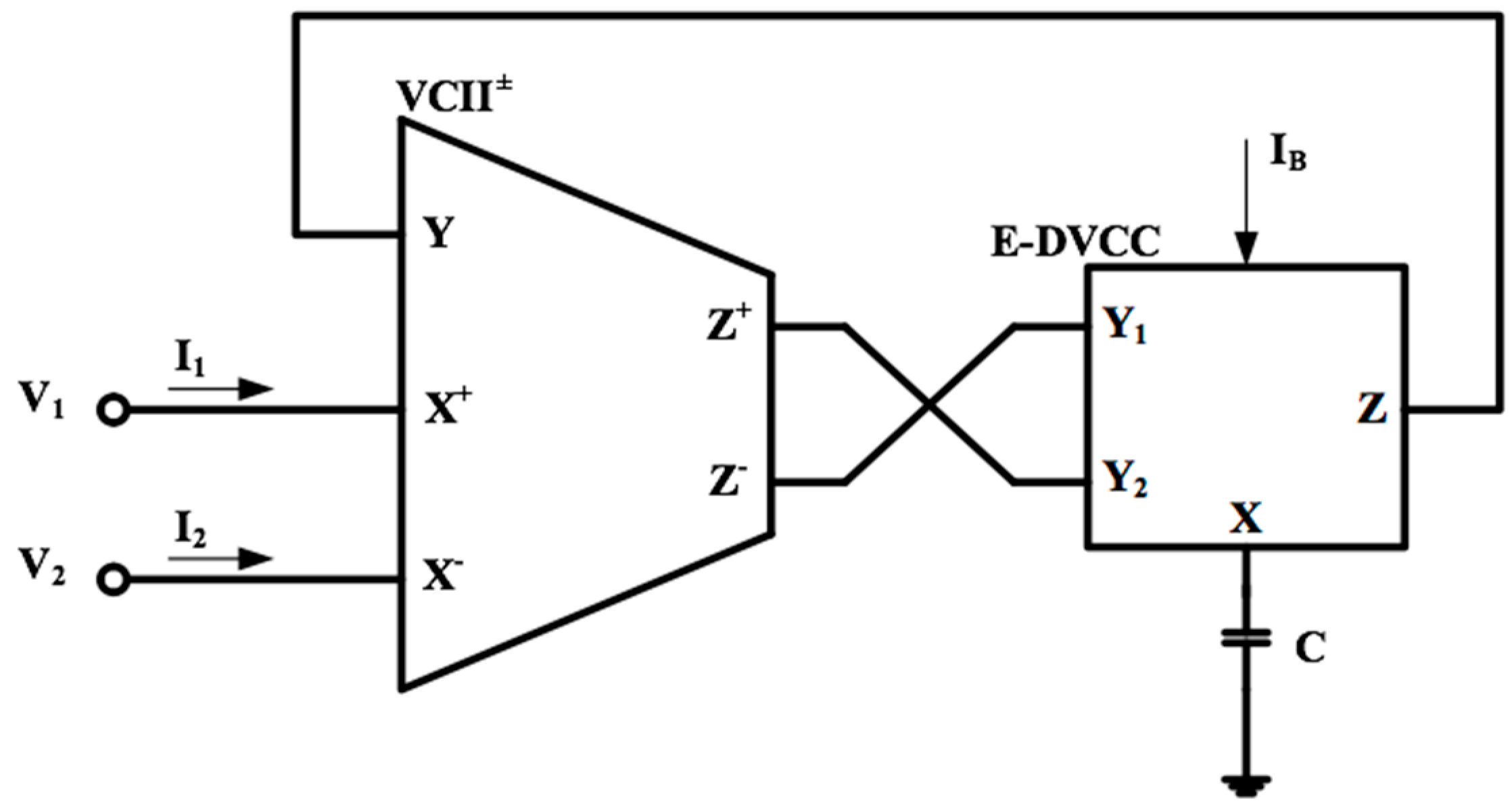

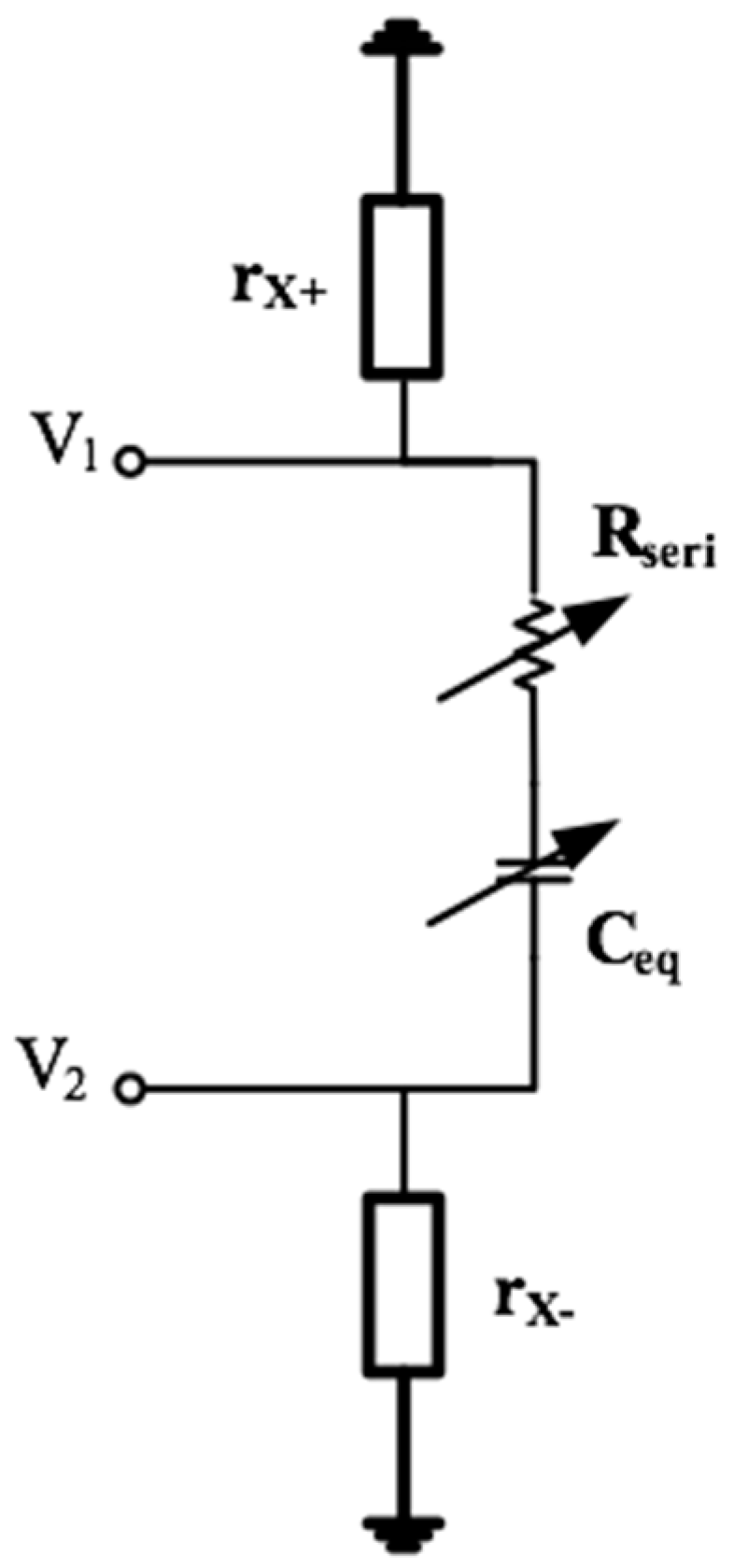

2. The Proposed VCII-Based Floating ±C Multiplier

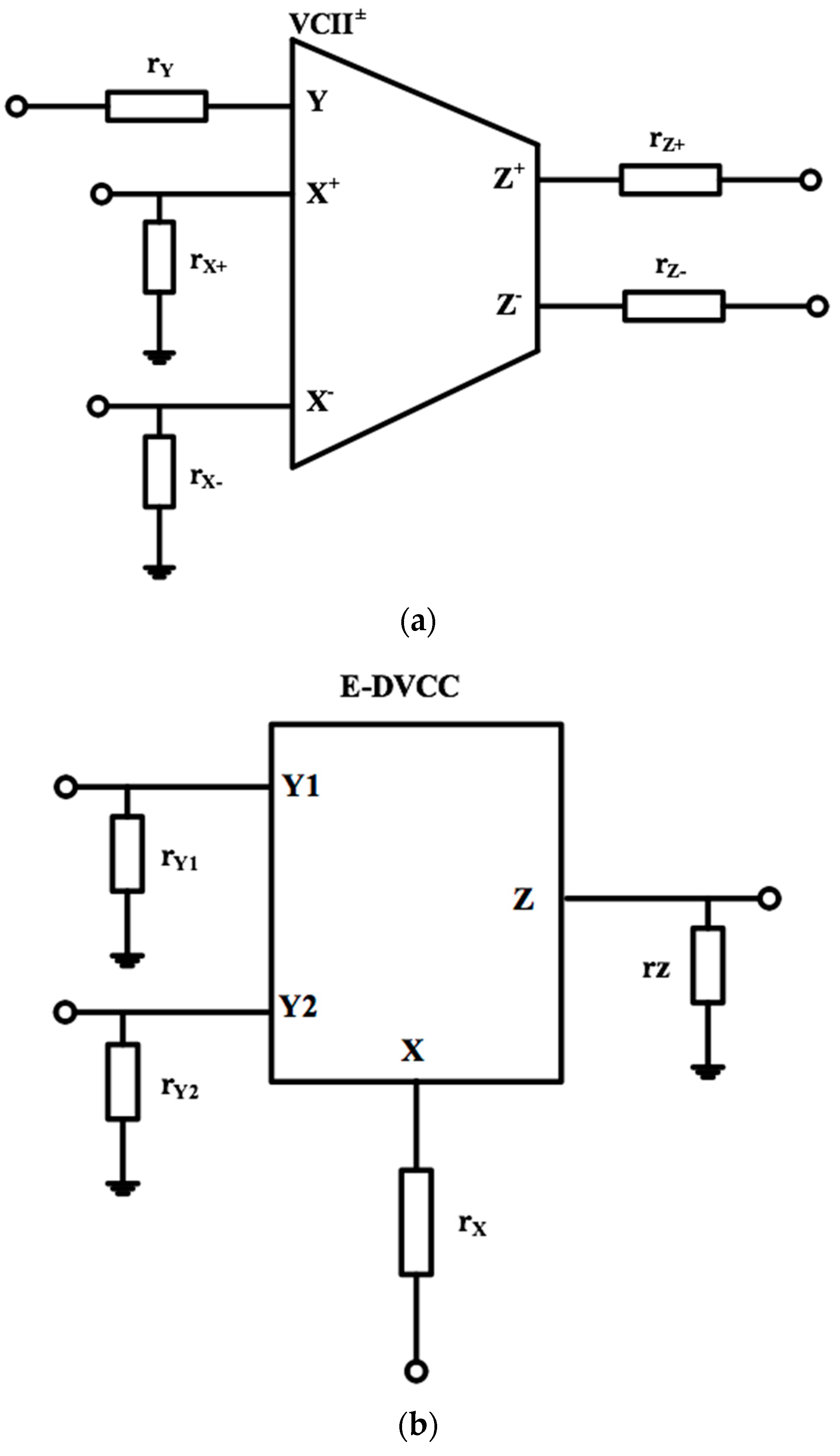

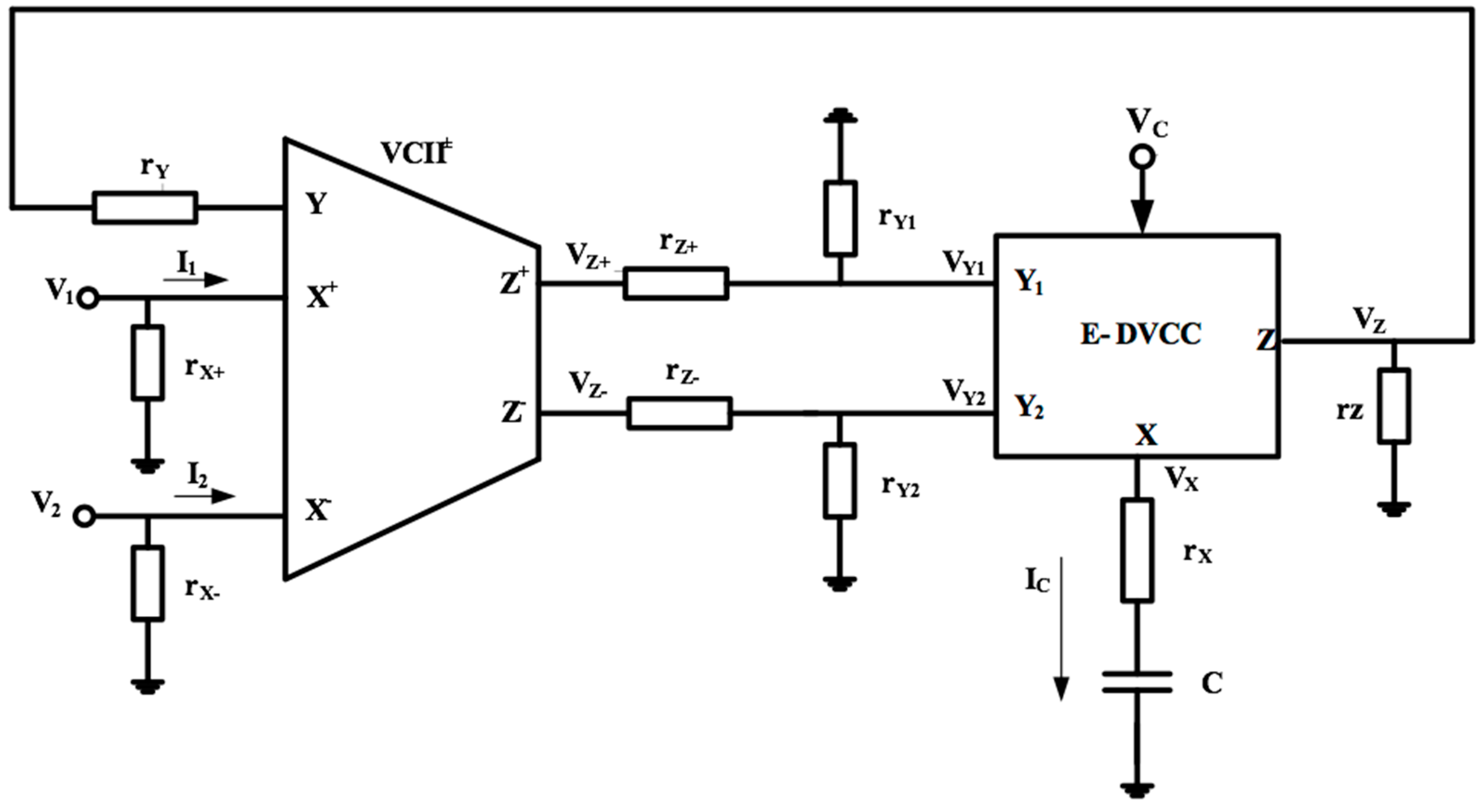

3. Non-Ideal Analysis

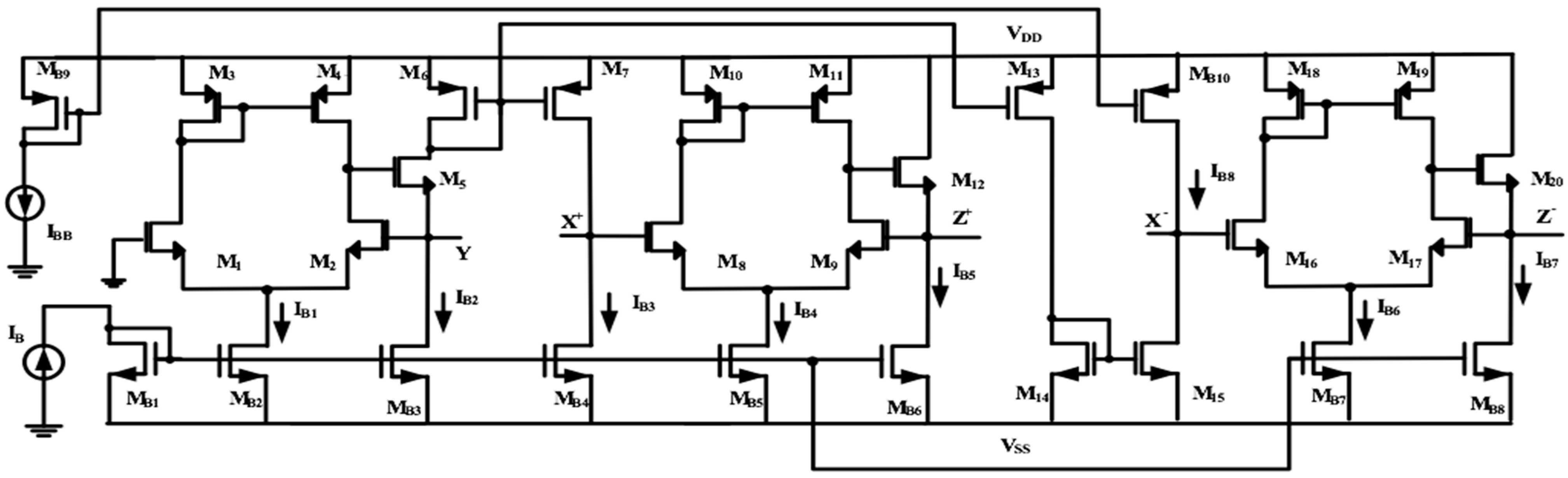

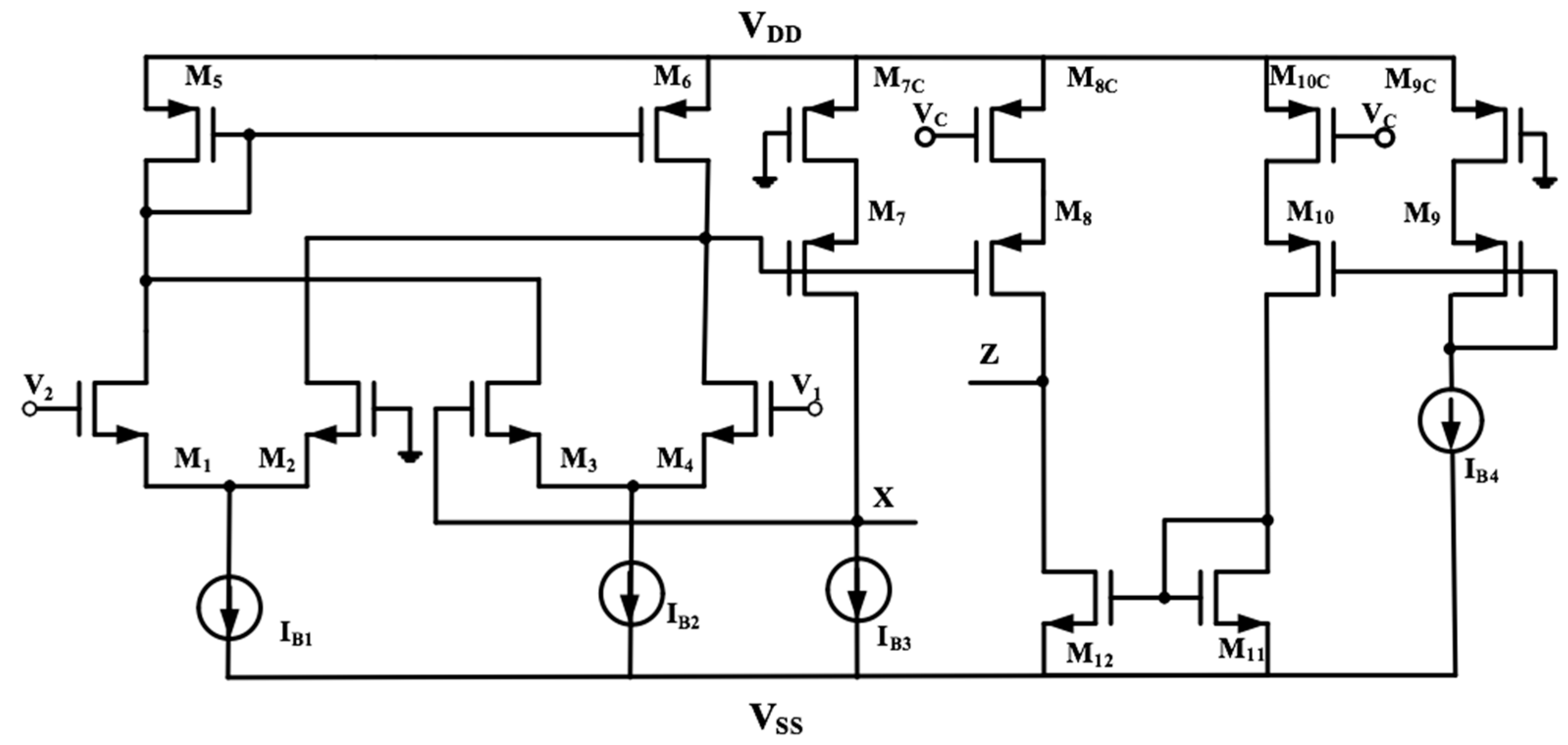

4. The CMOS Implementation of VCII± and E-DVCC

5. Simulation Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Al-Absi, M.A.; Al-Suhaibani, E.S.; Abuelma’atti, M.T. A New Compact CMOS C-Multiplier. Analog Integr. Circuits Signal Process. 2017, 90, 653–658. [Google Scholar] [CrossRef]

- Stornelli, V.; Safari, L.; Barile, G.; Ferri, G. A New Extremely Low Power Temperature Insensitive Electronically Tunable VCII-Based Grounded Capacitance Multiplier. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 72–76. [Google Scholar] [CrossRef]

- Pennisi, S. High Accuracy CMOS Capacitance Multiplier. In Proceedings of the 9th International Conference on Electronics, Circuits and Systems, Dubrovnik, Croatia, 15–18 September 2002; Volume 1, pp. 389–392. [Google Scholar]

- Abuelma’atti, M.T.; Tasadduq, N.A. Electronically Tunable Capacitance Multiplier and Frequency-Dependent Negative-Resistance Simulator Using the Current-Controlled Current Conveyor. Microelectron. J. 1999, 30, 869–873. [Google Scholar] [CrossRef]

- Myderrizi, I.; Zeki, A. Electronically Tunable DXCCII-Based Grounded Capacitance Multiplier. AEU Int. J. Electron. Commun. 2014, 68, 899–906. [Google Scholar] [CrossRef]

- Shu, K.; Sanchez-Sinencio, E.; Silva-Martinez, J.; Embabi, S.H.K. A 2.4-GHz Monolithic Fractional-N Frequency Synthesizer with Robust Phase-Switching Prescaler and Loop Capacitance Multiplier. IEEE J. Solid-State Circuits 2003, 38, 866–874. [Google Scholar] [CrossRef] [Green Version]

- Al-Absi, M.A.; Abulema’atti, M.T. A Tunable Floating Impedance Multiplier. Arab. J. Sci. Eng. 2019, 44, 7085–7089. [Google Scholar] [CrossRef]

- Prommee, P.; Somdunyakanok, M. CMOS-Based Current-Controlled DDCC and Its Applications to Capacitance Multiplier and Universal Filter. AEU Int. J. Electron. Commun. 2011, 65, 1–8. [Google Scholar] [CrossRef]

- Li, Y. A Series of New Circuits Based on CFTAs. AEU Int. J. Electron. Commun. 2012, 66, 587–592. [Google Scholar] [CrossRef]

- De Marcellis, A.; Ferri, G.; Guerrini, N.C.; Scotti, G.; Stornelli, V.; Trifiletti, A. A Novel Low-Voltage Low-Power Fully Differential Voltage and Current Gained CCII for Floating Impedance Simulations. Microelectron. J. 2009, 40, 20–25. [Google Scholar] [CrossRef]

- Yuce, E.; Minaei, S.; Cicekoglu, O. Resistorless Floating Immittance Function Simulators Employing Current Controlled Conveyors and a Grounded Capacitor. Electr. Eng. 2006, 88, 519–525. [Google Scholar] [CrossRef]

- Yuce, E. A Novel Floating Simulation Topology Composed of Only Grounded Passive Components. Int. J. Electron. 2010, 97, 249–262. [Google Scholar] [CrossRef]

- Alpaslan, H. DVCC-Based Floating Capacitance Multiplier Design. Turk. J. Electr. Eng. Comput. Sci. 2017, 25, 1334–1345. [Google Scholar] [CrossRef]

- Al-Absi, M.A.; Al-Khulaifi, A.A. A New Floating and Tunable Capacitance Multiplier with Large Multiplication Factor. IEEE Access 2019, 7, 120076–120081. [Google Scholar] [CrossRef]

- Ananda Mohan, P.V. Floating Capacitance Simulation Using Current Conveyors. J. Circuits Syst. Comput. 2005, 14, 123–128. [Google Scholar] [CrossRef]

- Padilla-Cantoya, I.; Furth, P.M. Enhanced Grounded Capacitor Multiplier and Its Floating Implementation for Analog Filters. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 962–966. [Google Scholar] [CrossRef]

- Tangsrirat, W. Floating Simulator with a Single DVCCTA. Indian J. Eng. Mater. Sci. 2013, 20, 79–86. [Google Scholar]

- Padilla-Cantoya, I. Low-Power High Parallel Load Resistance Current-Mode Grounded and Floating Capacitor Multiplier. IEEE Trans. Circuits Syst. II Express Briefs 2013, 60, 16–20. [Google Scholar] [CrossRef]

- Jaikla, W.; Siripruchyanan, M. An Electronically Controllable Capacitance Multiplier with Temperature Compensation. In Proceedings of the 2006 International Symposium on Communications and Information Technologies, Bangkok, Thailand, 18–20 October 2006; pp. 356–359. [Google Scholar]

- Kartci, A.; Ayten, U.E.; Herencsar, N.; Sotner, R.; Jerabek, J.; Vrba, K. Application Possibilities of VDCC in General Floating Element Simulator Circuit. In Proceedings of the 2015 European Conference on Circuit Theory and Design (ECCTD), Trondheim, Norway, 24–26 August 2015; pp. 1–4. [Google Scholar]

- Matsumoto, F.; Nishioka, S.; Ohbuchi, T.; Fujii, T. Design of a Symmetry-Type Floating Impedance Scaling Circuits for a Fully Differential Filter. Analog Integr. Circuits Signal Process. 2015, 85, 253–261. [Google Scholar] [CrossRef] [Green Version]

- Sedra, A.; Smith, K. A Second-Generation Current Conveyor and Its Applications. IEEE Trans. Circuit Theory 1970, 17, 132–134. [Google Scholar] [CrossRef]

- Alzaher, H.A.; Elwan, H.; Ismail, M. A CMOS Fully Balanced Second-Generation Current Conveyor. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 2003, 50, 278–287. [Google Scholar] [CrossRef]

- Prommee, P.; Somdunyakanok, M.; Toomsawasdi, S. CMOS-Based Current-Controlled DDCC and Its Applications. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 1045–1048. [Google Scholar]

- Torteanchai, U.; Kumngern, M.; Dejhan, K. Current-Controlled CCDDCC with Controlled Current Gain. In Proceedings of the 2011 IEEE International Conference on Computer Science and Automation Engineering, Shanghai, China, 10–12 June 2011; Volume 4, pp. 568–571. [Google Scholar]

- Herencsar, N.; Koton, J.; Vrba, K.; Lattenberg, I. Current Follower Transconductance Amplifier (CFTA)—A Useful Building Block for Analog Signal Processing. J. Act. Passiv. Electron. Devices 2011, 6, 217–229. [Google Scholar]

- Yuce, E. DO-CCII/DO-DVCC Based Electronically Fine Tunable Quadrature Oscillators. J. Circuits Syst. Comput. 2017, 26, 1750025. [Google Scholar] [CrossRef]

- Carvajal, R.G.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Torralba, A.; Galan, J.A.G.; Carlosena, A.; Chavero, F.M. The Flipped Voltage Follower: A Useful Cell for Low-Voltage Low-Power Circuit Design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Čajka, J.; Vrba, K. The Voltage Conveyor May Have in Fact Found Its Way into Circuit Theory. AEU Int. J. Electron. Commun. 2004, 58, 244–248. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. An Overview on the Second Generation Voltage Conveyor: Features, Design and Applications. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 547–551. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High Performance Voltage Output Filter Realizations Using Second Generation Voltage Conveyor. Int. J. RF Microw. Comput. Aided Eng. 2018, 28, e21534. [Google Scholar] [CrossRef]

- Safari, L.; Yuce, E.; Minaei, S.; Ferri, G.; Stornelli, V. A Second-Generation Voltage Conveyor (VCII)–Based Simulated Grounded Inductor. Int. J. Circuit Theory Appl. 2020, 48, 1180–1193. [Google Scholar] [CrossRef]

- Stornelli, V.; Safari, L.; Barile, G.; Ferri, G. A New VCII Based Grounded Positive/Negative Capacitance Multiplier. AEU Int. J. Electron. Commun. 2021, 137, 153793. [Google Scholar] [CrossRef]

- Yuce, E.; Safari, L.; Minaei, S.; Ferri, G.; Barile, G.; Stornelli, V. A New Simulated Inductor with Reduced Series Resistor Using a Single VCII±. Electronics 2021, 10, 1693. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S. A Novel Resistor-Free Electronically Adjustable Current-Mode Instrumentation Amplifier. Circuits Syst. Signal Process. 2013, 32, 1025–1038. [Google Scholar] [CrossRef]

| E-DVCC | Transistor | M1–M4 | M5–M6, M7, M8C, M10C, M9 | M7C, M9C | M11, M12 | M8, M10 |

| Aspect Ratio (W/L) | 9 µm/0.18 µm | 72 µm/0.9 µm | 7.2 µm/0.9 µm | 9 µm/0.9 µm | 720 µm/0.9 µm | |

| VCII | Transistor | M1–M2, M8–M9, M17–M18, M6–M7, M13 | M3–M4, M10–M11, M18–M19 | M5, M12, M20 | ||

| Aspect Ratio (W/L) | 9 µm/0.72 µm | 36 µm/0.72 µm | 8 µm/0.72 µm | |||

| VCII± | E-DVCC | |||

|---|---|---|---|---|

| rY | 38.6 Ω | αc1 | 0.998 | |

| rX+ | 147.5 kΩ | αc2 | 0.997 | |

| rX− | 133.7 kΩ | rx | 574 Ω | |

| rZ+ | 37 Ω | rY1, rY2 | >2 GΩ | |

| rZ | VC = 0 V | 120 kΩ | ||

| VC = −0.45 V | 80 kΩ | |||

| VC = −0.9 V | 50 kΩ | |||

| rZ− | 37 Ω | K | VC = 0 V | 10 |

| β1 (DC) | 1.023 | VC = −0.45 V | 19.5 | |

| β2 (DC) | 1.01 | VC = −0.9 V | 25.4 | |

| αv1 (DC) | 0.983 | Pd | VC = 0 V | 1.43 mW |

| αv2 (DC) | 0.983 | VC = 0 V | 2.03 mW | |

| Pd | 0.804 mW | VC = −0.9 V | 2.38 mW | |

| VC | Multiplication Factor | Expected Value of Ceq | Simulated Value of Ceq | % Error | |

|---|---|---|---|---|---|

| Positive simulator | VC = 0 V | 10 | 100 pF | 99.4 pF | −0.6 |

| VC = −0.45 V | 19.5 | 195 pF | 196.1 pF | 0.56 | |

| VC = −0.9 V | 25.4 | 254 pF | 255.4 pF | 0.55 | |

| Negative simulator | VC = 0 V | 10 | −100 pF | −99.47 pF | −0.53 |

| VC = −0.45 V | 19.5 | −195 pF | −196 pF | 0.51 | |

| VC = −0.9 V | 25.4 | −254 pF | −255.3 pF | 0.51 |

| Electronic Tuning | Max Error | Vdd–Vss | Power Consumption | Number of Transistors | Passive Elements | ABB | Ref | |

|---|---|---|---|---|---|---|---|---|

| R | Floating C | |||||||

| Yes | 20% 1 | NA | NA | NA | 1 | No | 2OTA + CCII | [7] |

| Yes | NA | ±1.25 V | 4.05 Mw 2 | 99 | 0 | No | 3CCDDC | [8] |

| Yes | NA | ±1.5 V | NA | 104 | 0 | No | 4CFTA | [9] |

| Yes | NA | 2 V | 0.7 mW | 47 | 0 | Yes | VGC-CCII | [10] |

| Yes | NA | ±2.5 V | 4.98 mW | 70 | 0 | No | Do-CCII + 3CCCII | [11] |

| No | NA | ±1.5 V | 9.52 mW | 36 | 2 | No | 2DVCC | [12] |

| No | NA | ±0.75 V | 1.29 mW | 98 | 2 | No | 2MODVCC | [13] |

| Yes | 8.60% | ±0.75 V | 2.3 µW–6.34 µW | 76 | 0 | Yes | CCII + 4OTA | [14] |

| No | NA | NA | NA | NA | 2 | No | 2CCII | [15] |

| Yes | 10%1 | ±2 V | NA | 24 | 1 | No | DVCCTA | [16] |

| No | 7.60% | 1.3 V | 1.32 mW | 72 | 0 | yes | 2OTA | [17] |

| No | NA | 1.5 V | 240 μW | 34 | 0 | Yes | FVF | [18] |

| Yes | 8% | ±2.5 V | 0.565 mW | 104 | 0 | No | 4Gm | [19] |

| No | NA | ±0.45 V | 0.556 mW | 56 | 2 | No | 2DVCC | [20] |

| No | NA | 1.8 V | 5.72 µW | 11 | 0 | Yes | MOS | [21] |

| Yes | 0.56% | ±0.9 V | 2.234 mW–3.184 mW | 51 | 0 | No | VCII± + E-DVCC | Proposed |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ferri, G.; Safari, L.; Barile, G.; Scarsella, M.; Stornelli, V. New Resistor-Less Electronically Controllable ±C Simulator Employing VCII, DVCC, and a Grounded Capacitor. Electronics 2022, 11, 286. https://doi.org/10.3390/electronics11020286

Ferri G, Safari L, Barile G, Scarsella M, Stornelli V. New Resistor-Less Electronically Controllable ±C Simulator Employing VCII, DVCC, and a Grounded Capacitor. Electronics. 2022; 11(2):286. https://doi.org/10.3390/electronics11020286

Chicago/Turabian StyleFerri, Giuseppe, Leila Safari, Gianluca Barile, Massimo Scarsella, and Vincenzo Stornelli. 2022. "New Resistor-Less Electronically Controllable ±C Simulator Employing VCII, DVCC, and a Grounded Capacitor" Electronics 11, no. 2: 286. https://doi.org/10.3390/electronics11020286