Circuit Techniques in GaN Technology for High-Temperature Environments

Abstract

:1. Introduction

2. High Temperature Characterization and Modeling of Passive Elements

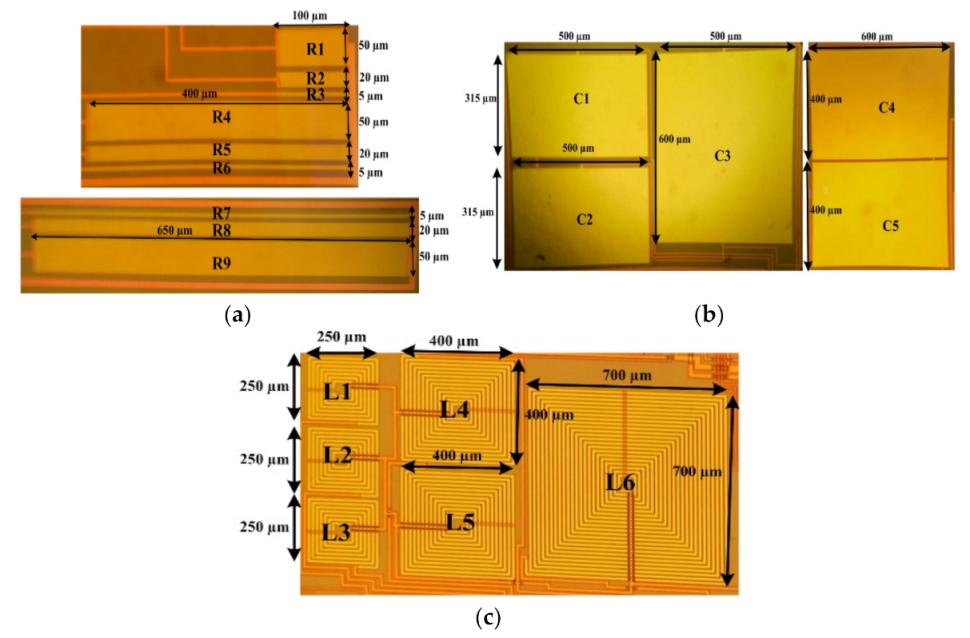

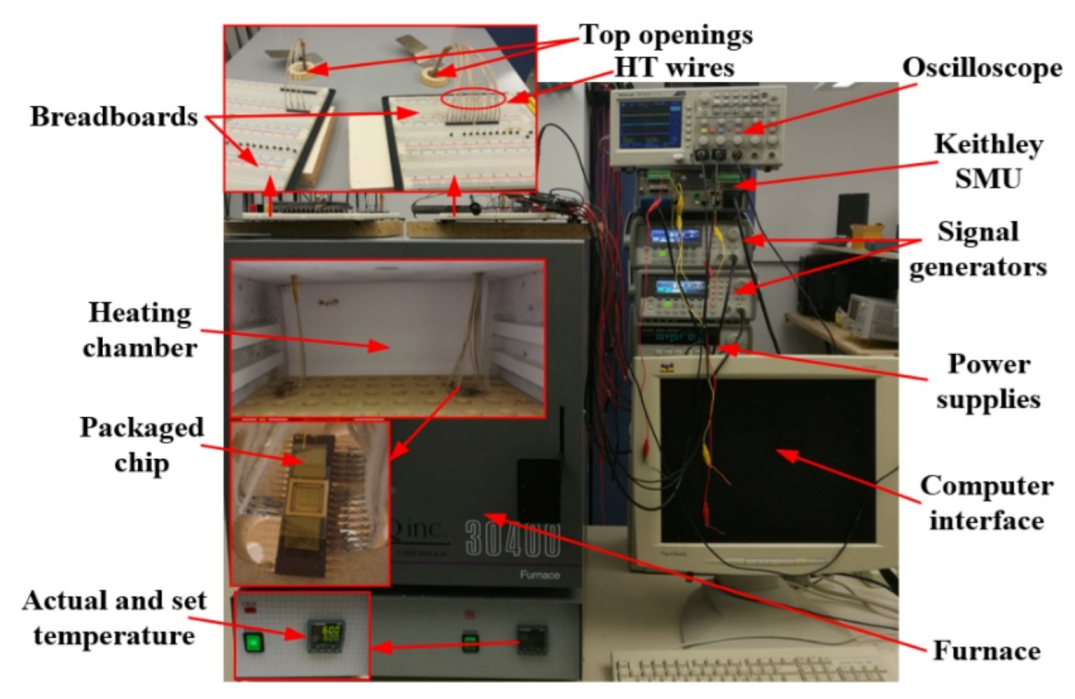

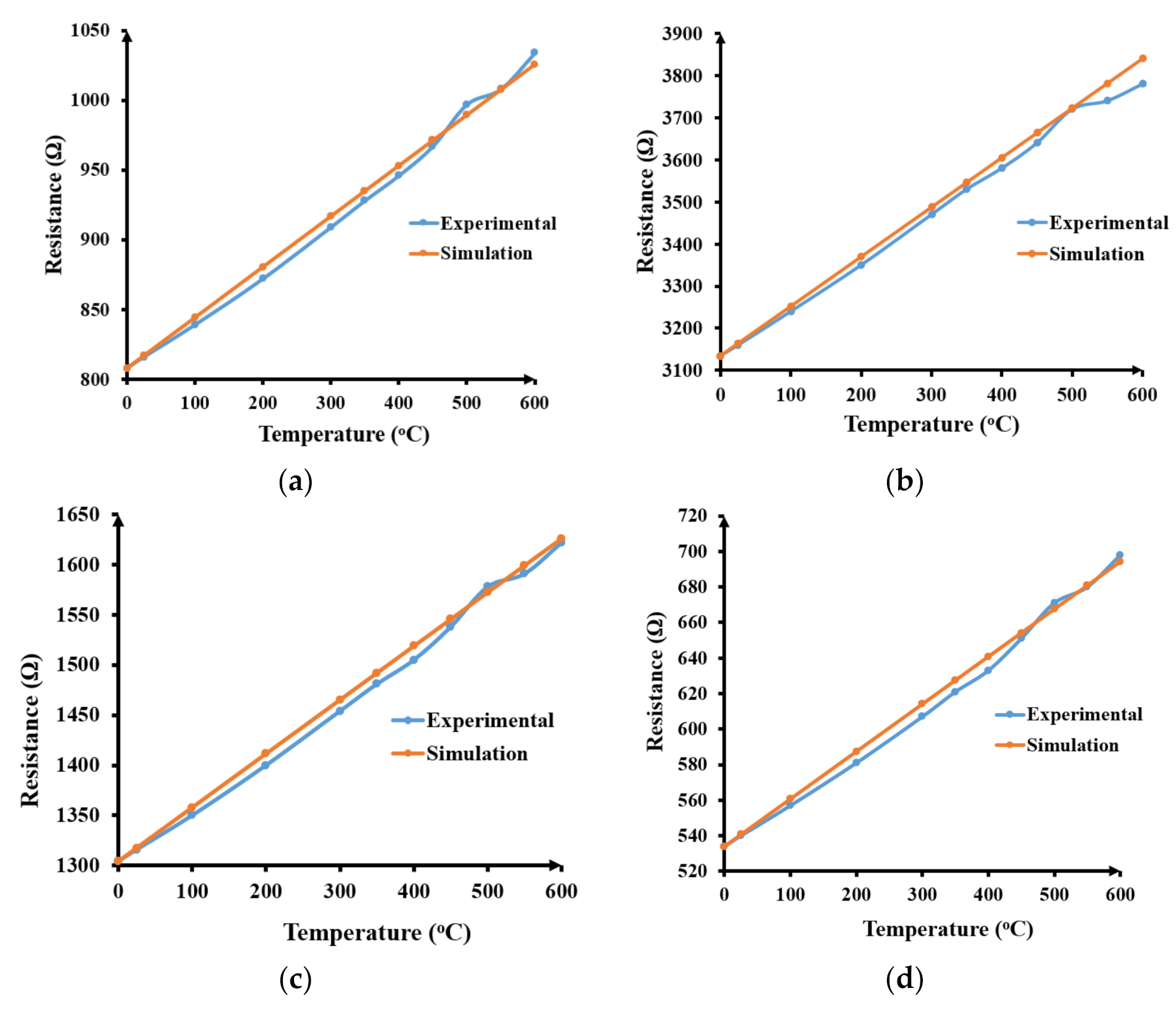

2.1. Integrated Resistors

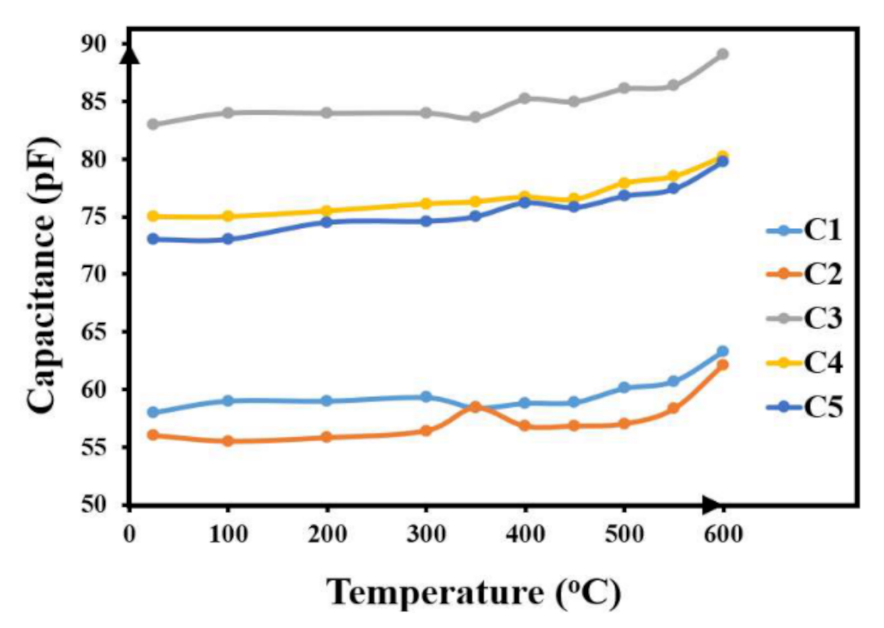

2.2. Integrated Capacitors

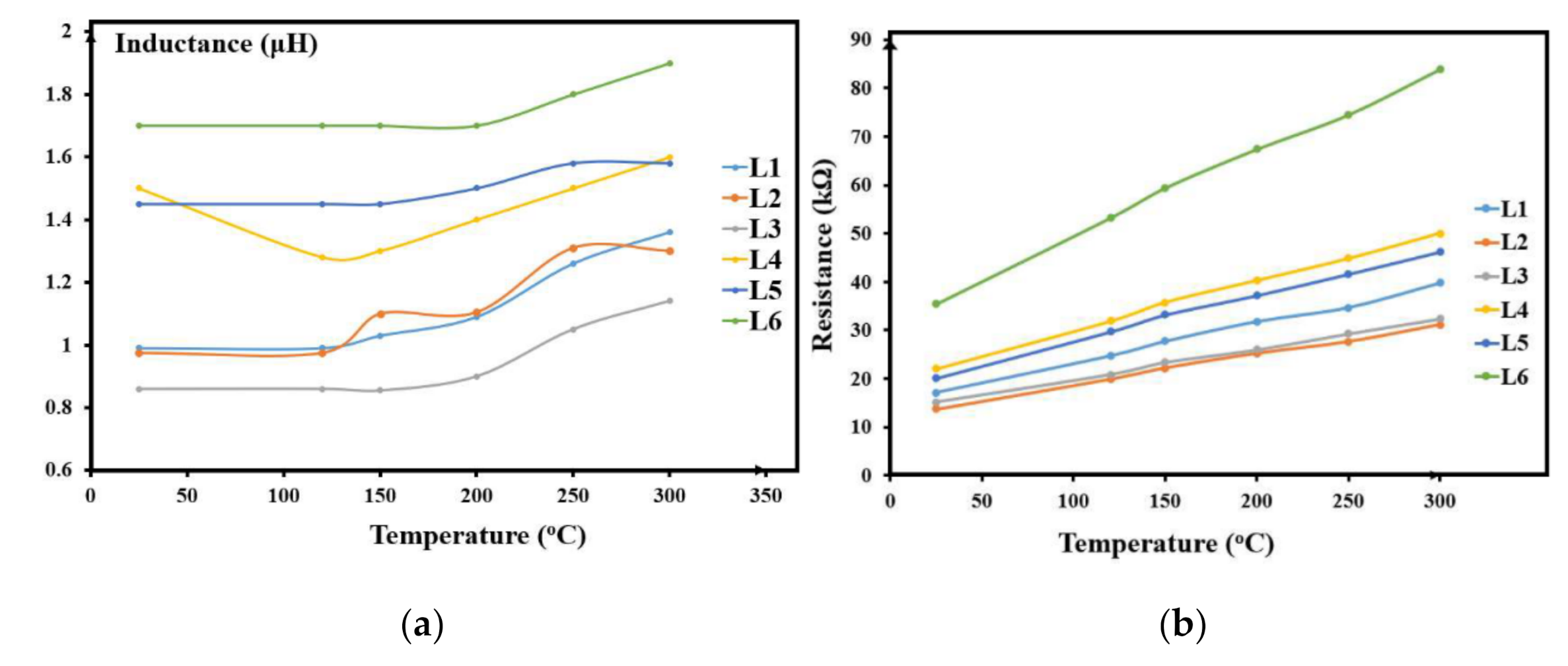

2.3. Integrated Inductors

3. Circuit Design and Measurements

3.1. Logic Gates: NOT, NAND, NOR

3.1.1. Inverter (NOT Gate)

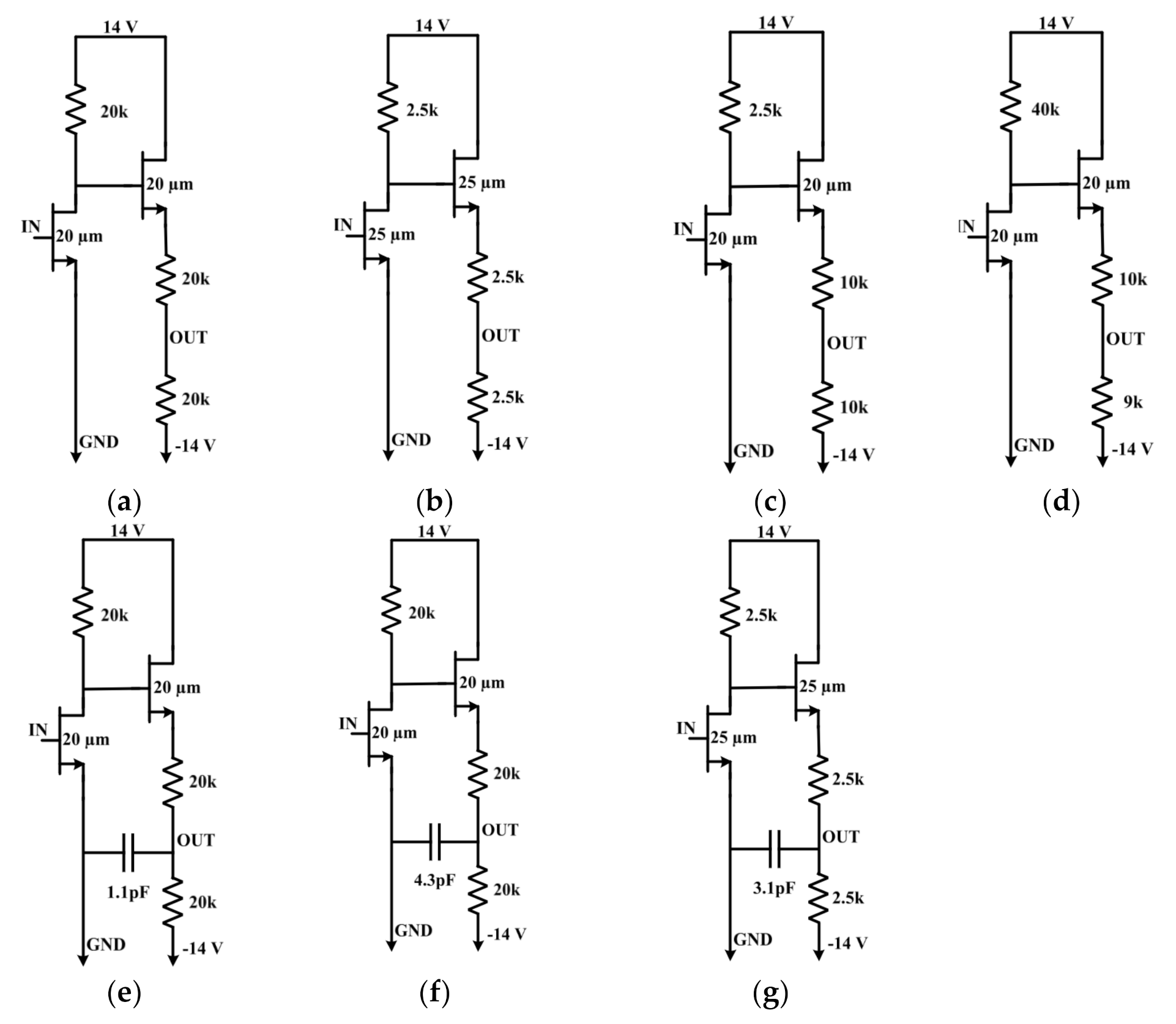

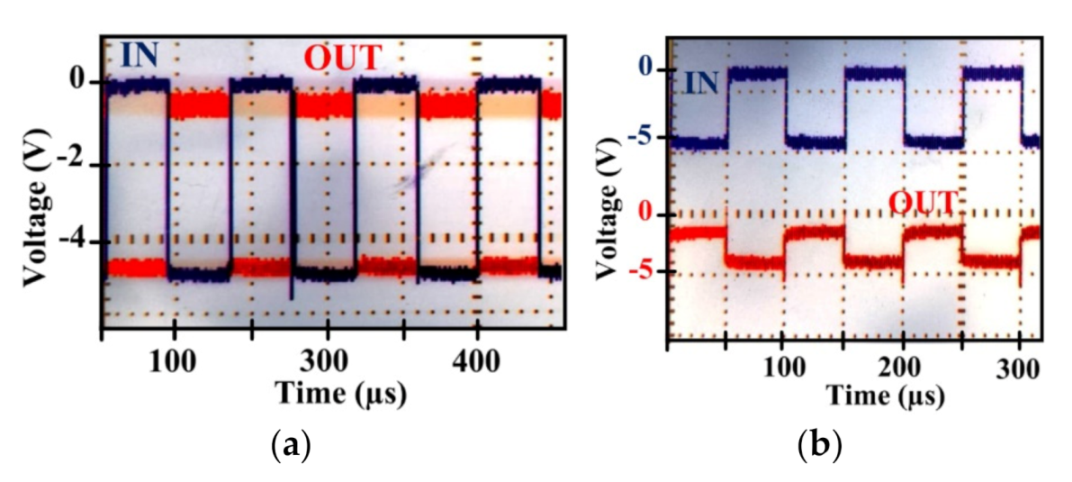

- INV1: This inverter is designed to have the lowest power consumption. Its transistors have the minimum size specified by the process (L = 500 nm, W = 20 µm) and resistors are very high resistance values (20 kΩ) to limit the current flow as much as possible. In this case, the current in each branch stemming from the power supply is less than 1 mA. The schematics of INV1 is shown in Figure 9a, and its micrograph is presented in Figure 10a. The experimental input-output response at 25 °C and 300 °C of INV1 are shown in Figure 11.

- INV3: This inverter is an intermediate solution between the normal inverter (INV2) and the power optimized one (INV1). Its main resistor R1 has a small resistance value (2.5 kΩ), however the level shifter resistors R2 and R3 have a large resistance value (20 kΩ). The schematics of INV3 is shown in Figure 9c, and its micrograph is presented in Figure 10c.

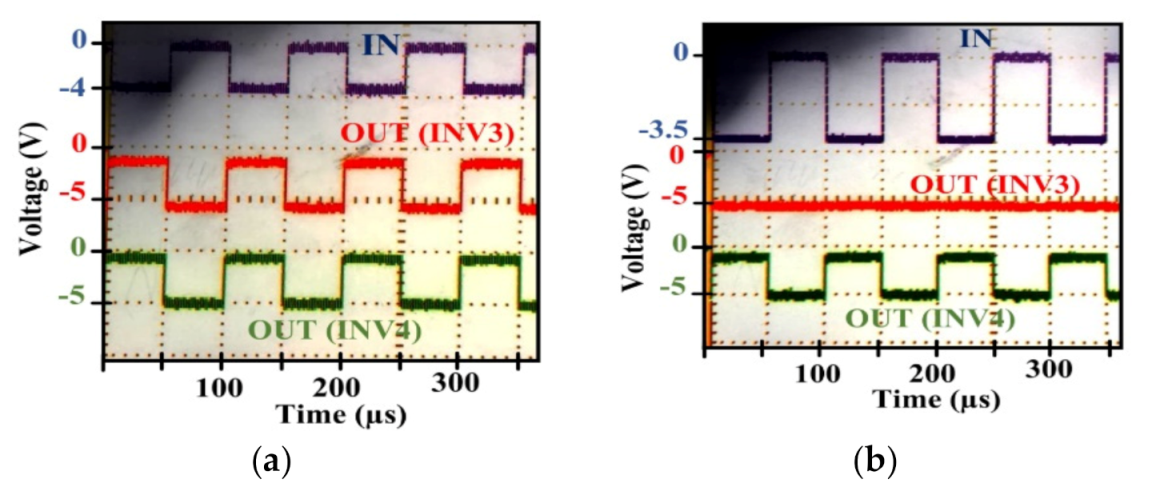

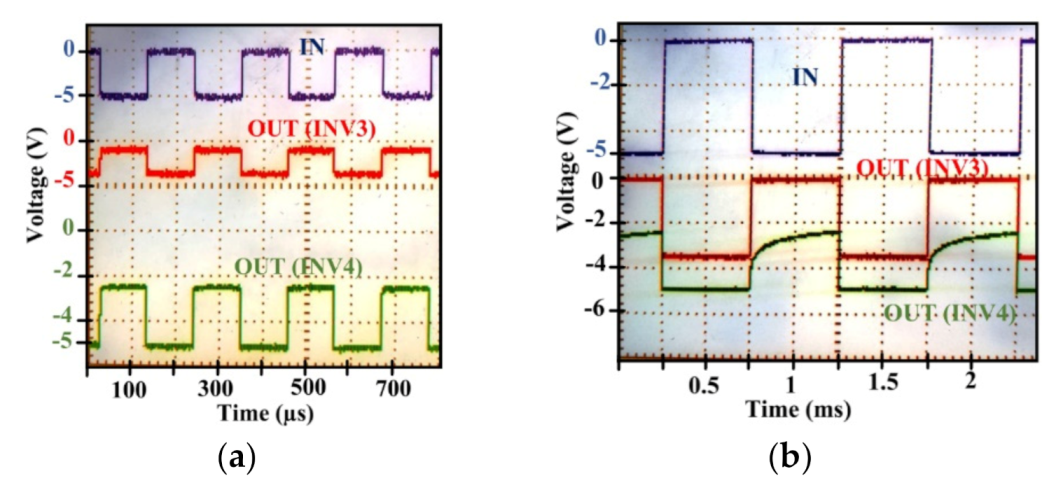

- INV4: This inverter is used along with INV3 in the digital demodulator system [18]. The schematics of INV4 is shown in Figure 9d, and its micrograph is presented in Figure 10d. Its main goal is to detect and convert a modulated signal with amplitude voltage only higher than −4 V (High-level). Any signal ≤ −4 V (Low-level) will not be detected and will produce a low output level (−5 V). Figure 13 shows how INV4 does not respond at input voltage of −3.5 V (Figure 13a) and starts responding at input voltage of −4 V (Figure 13b). By contrast, INV3 responds in both conditions of VIN. Both INV3 and INV4 keep working at HT as seen in Figure 14a at 400 °C and Figure 14b after cooling from 450 °C.

- INV5: This inverter is designed to allow building a 5 MHz ring oscillator (seven stages). A capacitor is added to its output to ensure the required signal delay that allow building a 5 MHz oscillator. The schematics of INV5 is shown in Figure 9e, and its micrograph is presented in Figure 10e. The experimental results of INV5 at 25 °C and 300 °C are shown in Figure 15.

- INV6: This inverter is designed to allow building a 1 MHz ring oscillator (seven stages). A capacitor is added to its output to produce the stage delay compatible with a 1 MHz oscillator. The schematics of INV6 is shown in Figure 9f, and its micrograph is presented in Figure 10f. The experimental results at 25 °C and 300 °C of INV6 are shown in Figure 16.

- INV7: This inverter is designed to build the DELAY circuit for high frequency applications (1–5 MHz). A capacitor is added to the output stage to ensure the required delay time. The schematics of INV7 is shown in Figure 9g, and its micrograph is presented in Figure 10g. The experimental results of INV7 at 25 °C and 300 °C are shown in Figure 17.

3.1.2. NAND Gate

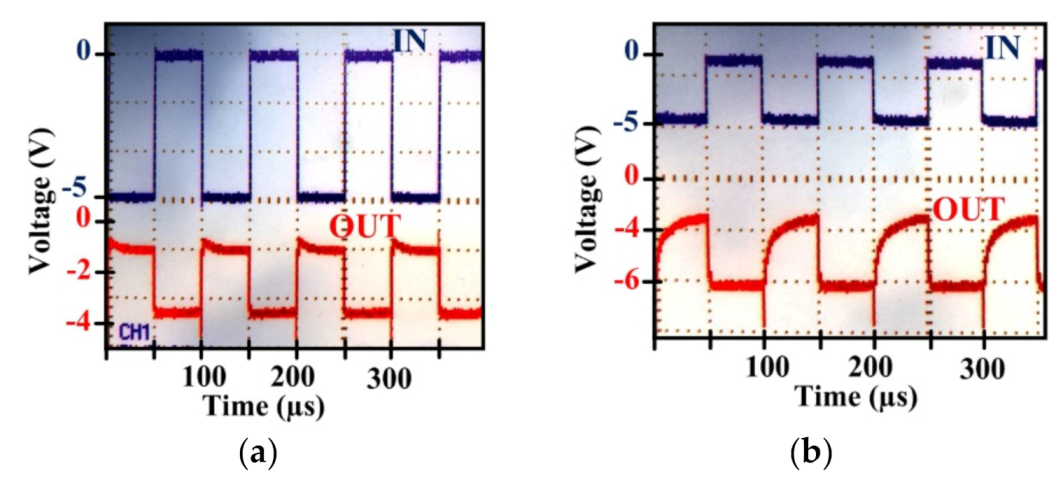

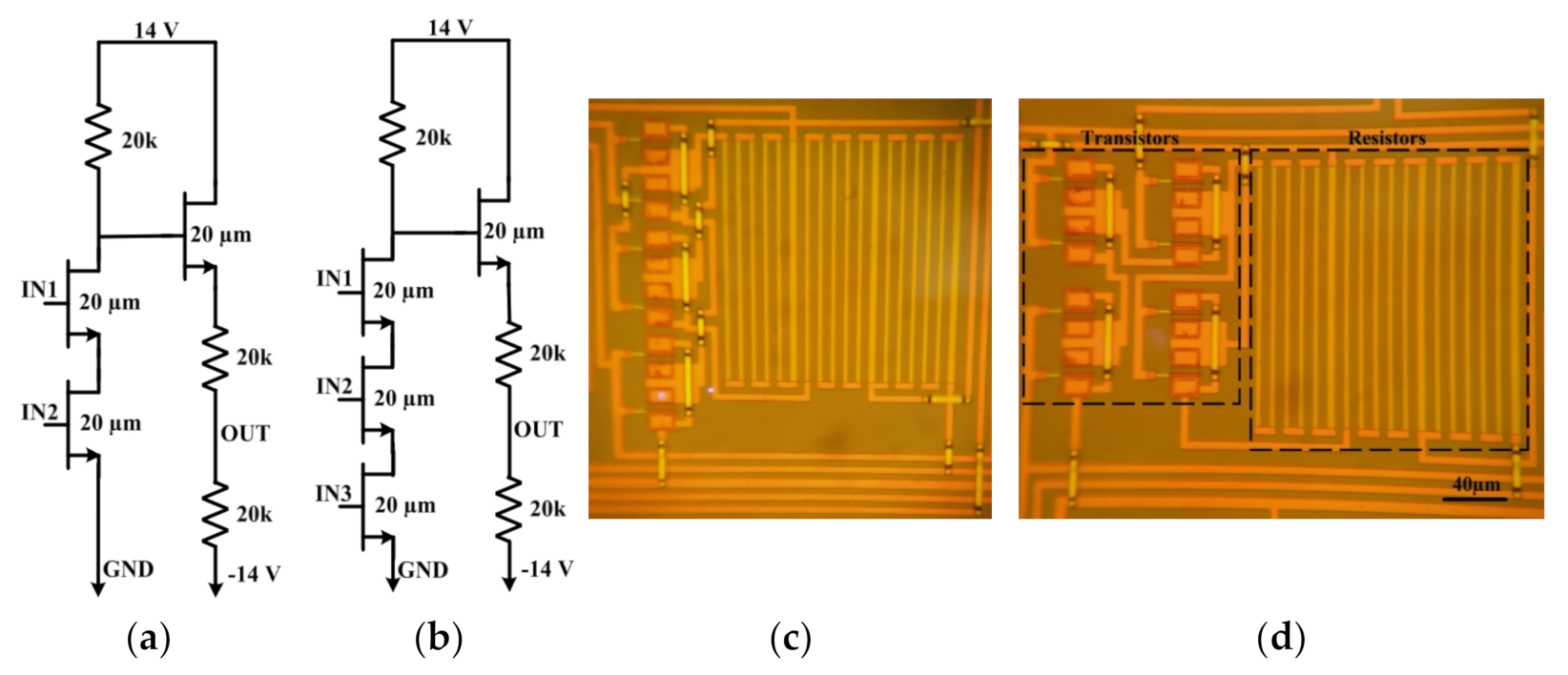

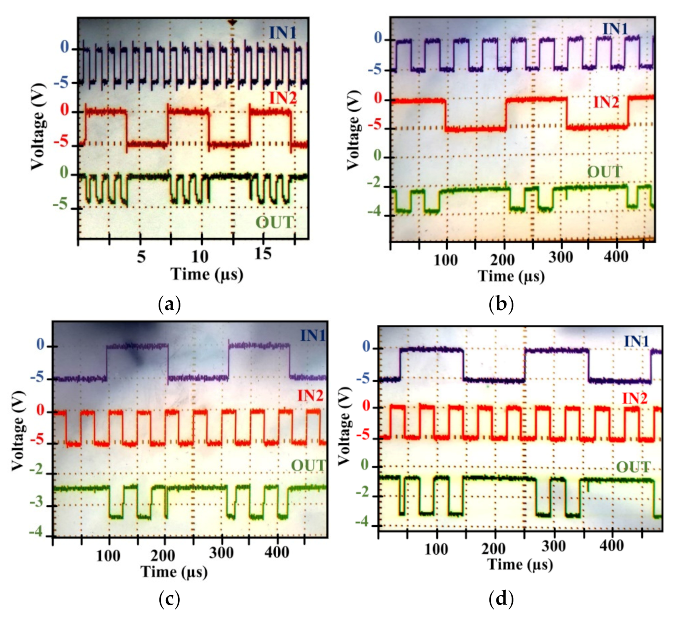

- NAND2: This gate is designed with optimized power consumption using the smallest transistors and large resistance values. The schematic of NAND2 is shown in Figure 18a, and its micrograph is given in Figure 18c. The transient characteristics of the NAND2 at 25 °C, 300 °C, and 400 °C are shown in Figure 19a–c, respectively. Figure 19d shows the measured response of NAND2 at 25 °C after it was heated to 450 °C. It is of interest that the output responses are different for the various reported experiments. However, these output responses always remain consistent with the respective different input signals that were applied in these experiments. Reproducing the same stimuli in the various experiment could be done easily with the available test setup.

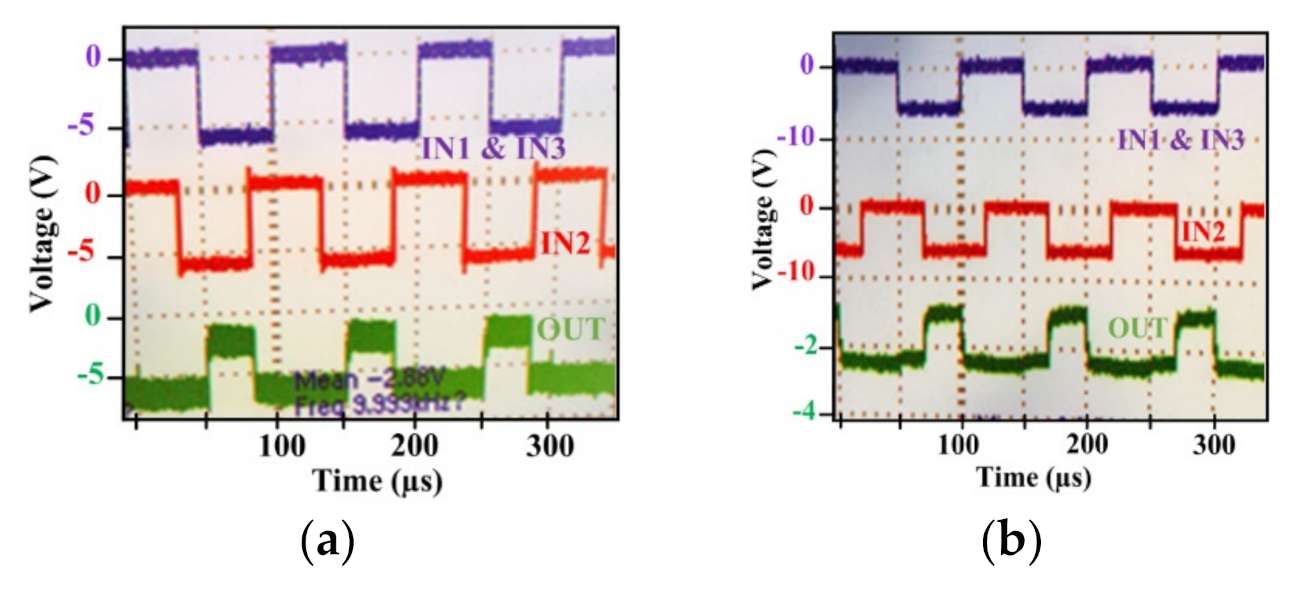

- NAND3: This gate is designed with optimized power consumption using small transistors and large resistance values. The schematics of NAND3 is shown in Figure 18b, and its micrograph is given in Figure 18d. The transient response of the NAND3 is shown in Figure 20 at 25, 170 and 300 °C. In Figure 18b, the third input is connected to IN1 due to the unavailability of a third signal generator at the testing time, however this connection is adequate to test the functionality of the gate.

3.1.3. NOR Gate

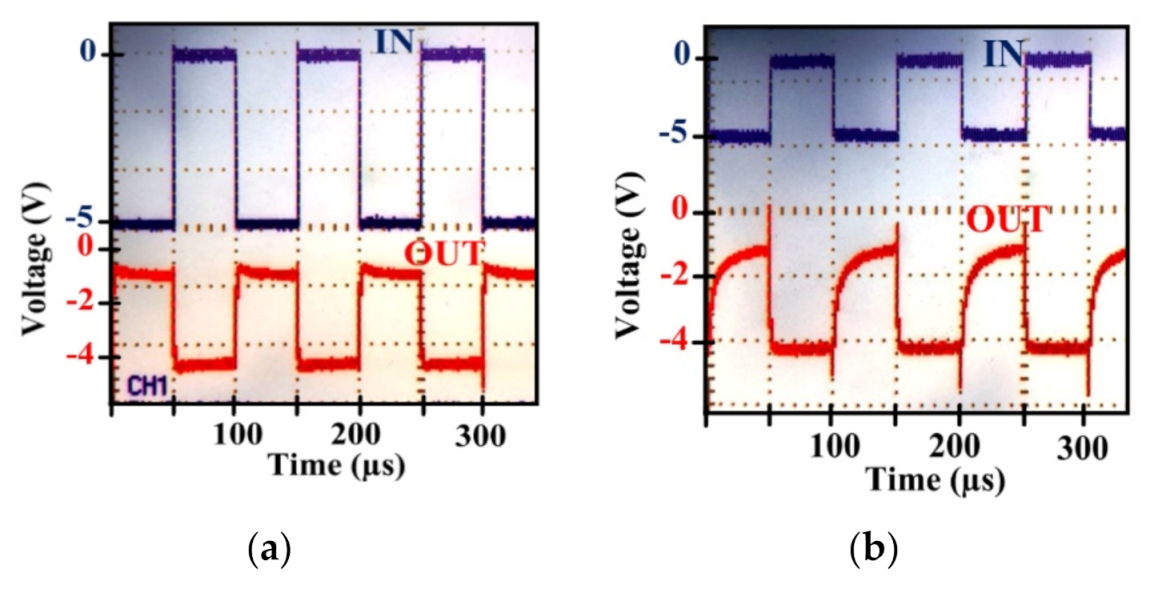

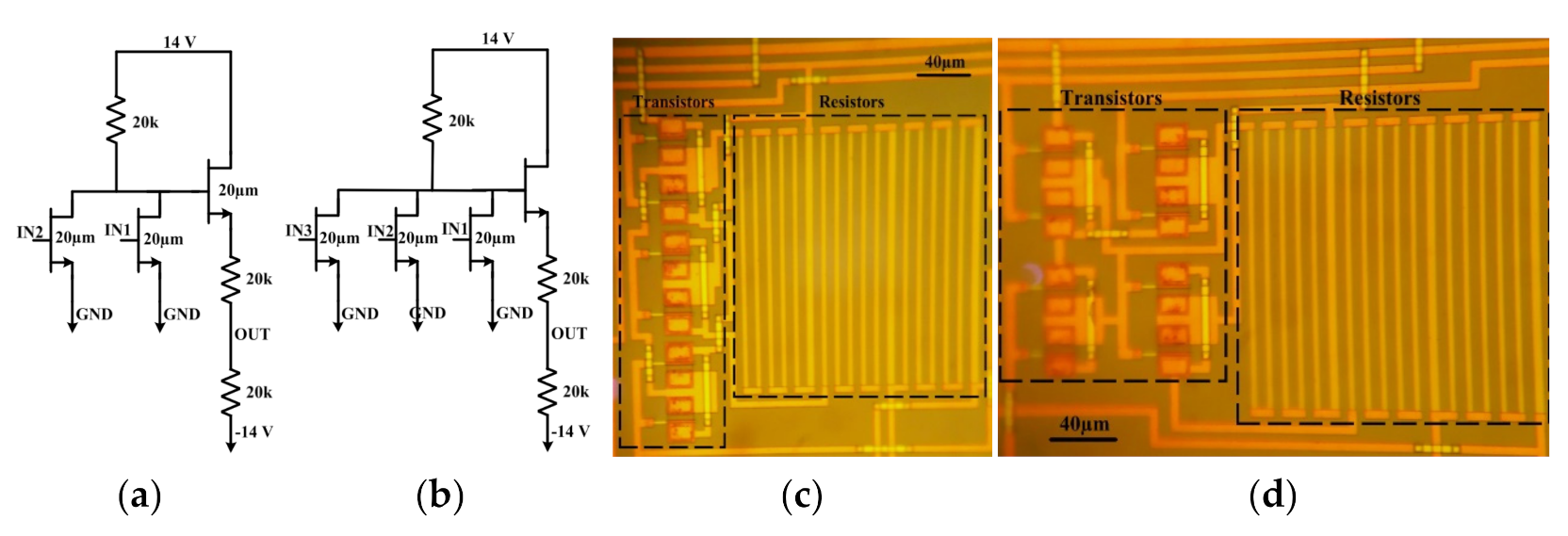

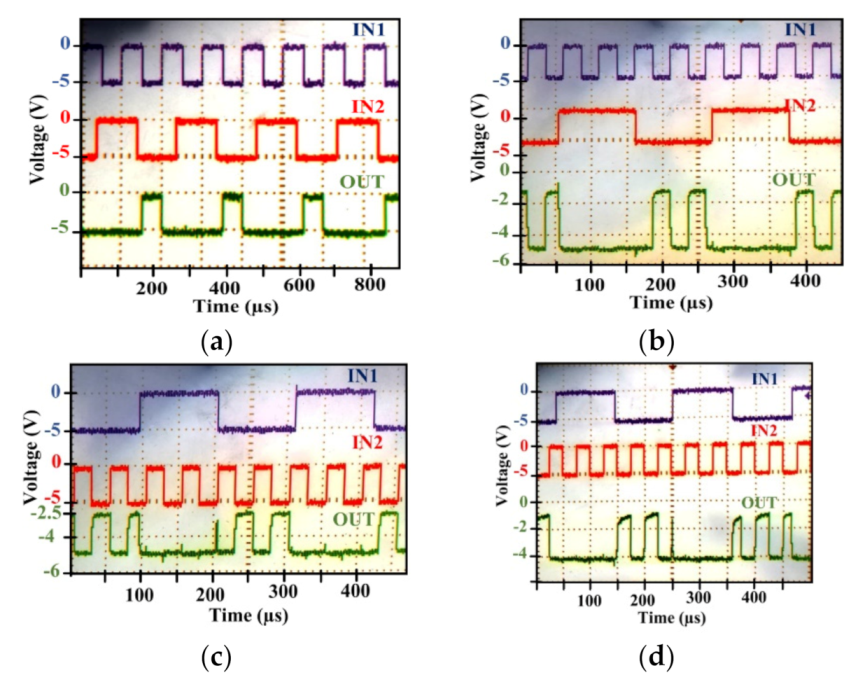

- NOR2: this gate is designed with optimized power consumption using the smallest transistors and large resistance values. The schematic of NOR2 is shown in Figure 21a, and its micrograph is given in Figure 21c. The transient response characteristics of NOR2 at 25, 300, and 400 °C are shown in Figure 22a–c, respectively. Figure 22d shows the measured transient response of NOR2 at 25 °C after it was heated to 450 °C.

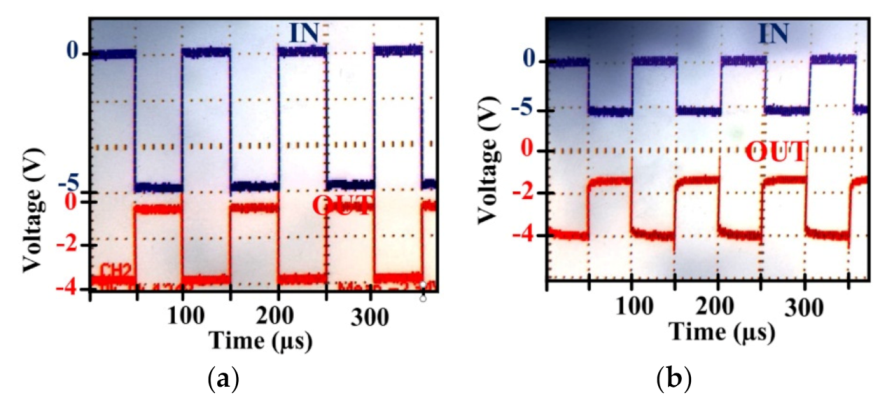

- NOR3: This gate is designed with optimized power consumption using the small transistors and large resistance values. The schematics of the NOR3 is shown in Figure 21b, and its micrograph is given in Figure 21d. The transient response characteristics of NOR3 are shown in Figure 23 at 25 and 300 °C. The third input is connected to IN1 due to the unavailability of a third signal generator at the testing time. However, this connection is sufficient to test the functionality of the gate.

3.2. Digital Circuits: Delay, D Flip-Flop, Ring Oscillator

3.2.1. Delay Circuit

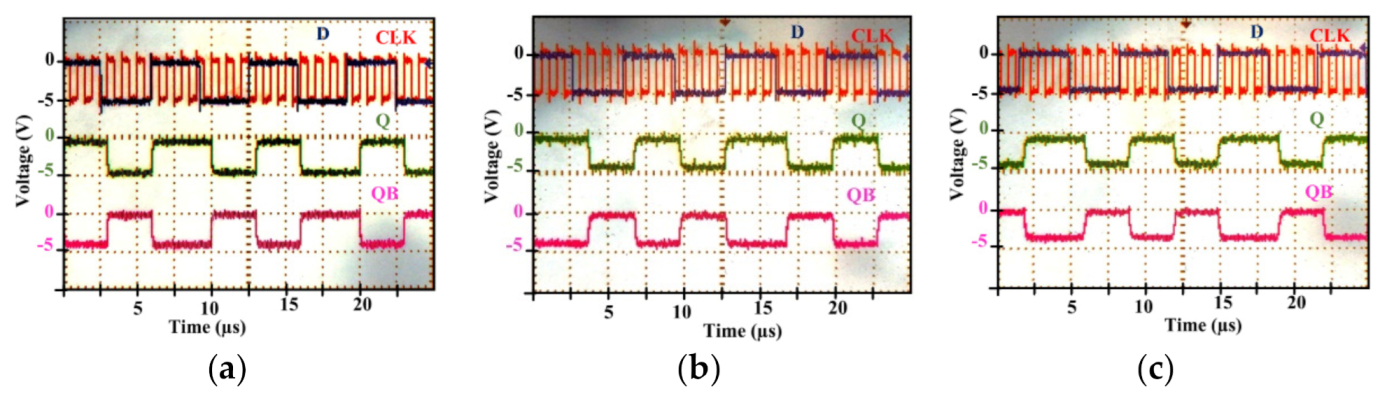

3.2.2. D Flip-Flop

3.2.3. Ring Oscillator

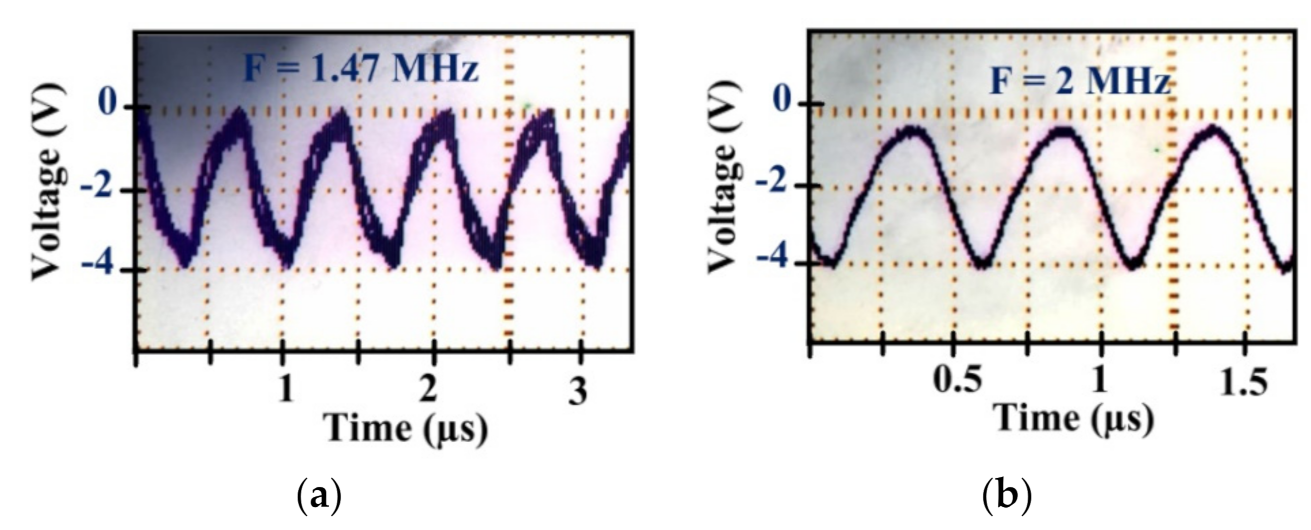

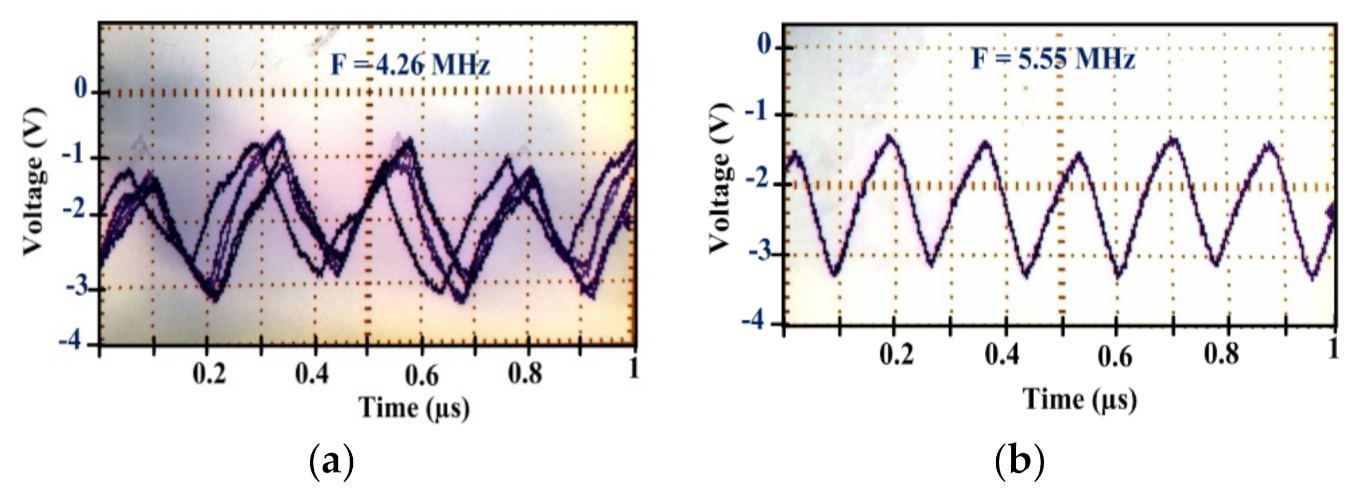

- OSC-1: In this circuit, 7 INV6 stages are used to build a ring oscillator with an oscillation frequency of 1.5 MHz. The micrograph of OSC-1 is depicted in Figure 25c and its transient response is shown in Figure 28a at 25 °C. Figure 28b shows the measured output signal produced by OSC-1 at 25 °C after it was heated to 450 °C.

- OSC-2: This oscillator is similar to OSC-1 but it is built using INV5. OSC-2 is designed to generate a 5 MHz oscillation frequency. The micrograph of OSC-2 is presented in Figure 25d and its measured output signal at 25 °C is shown in Figure 29a. Figure 29b shows the measurement of OSC-1 at 25 °C after heating to 450 °C.

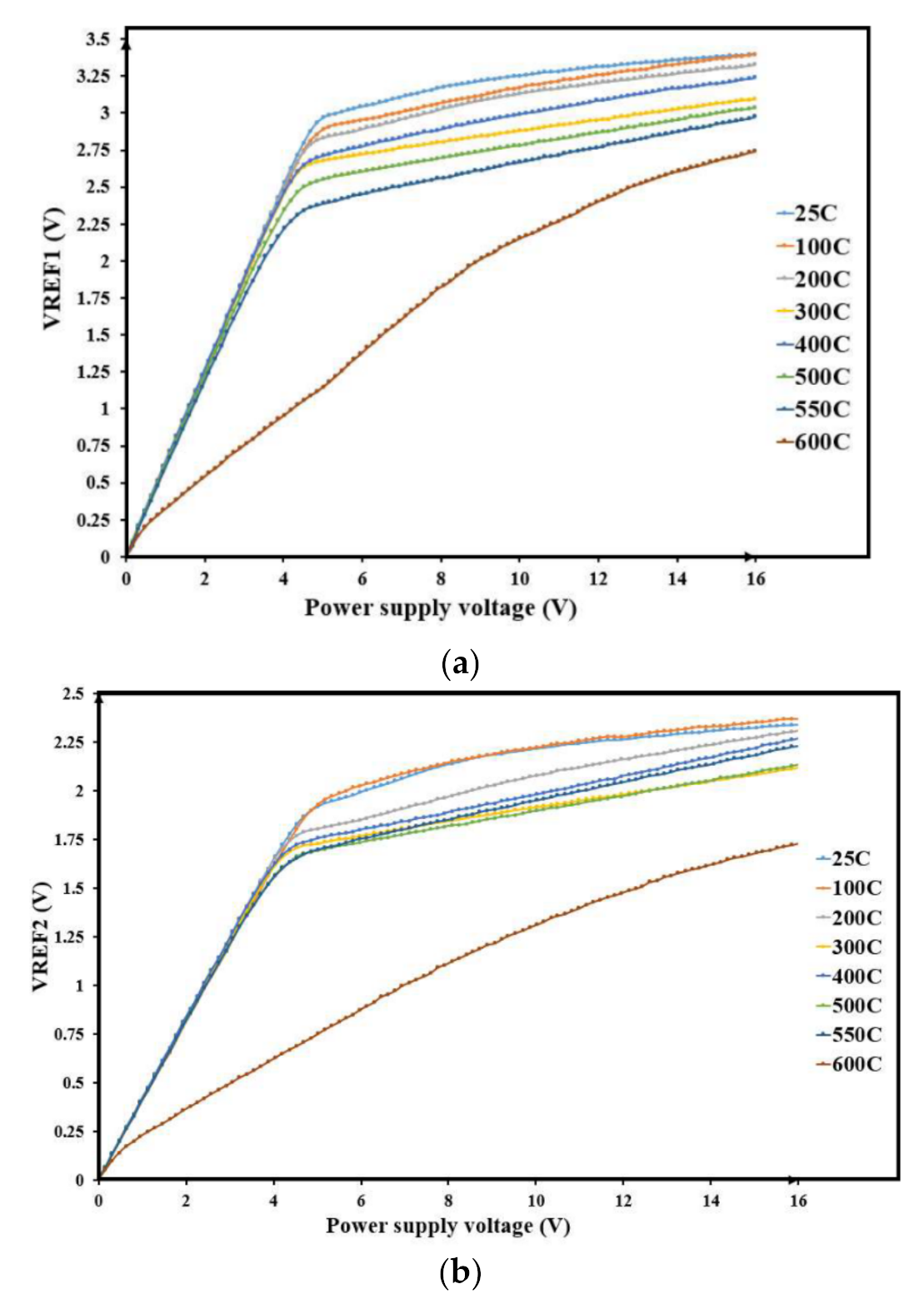

3.3. Voltage Reference Circuit

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hassan, A.; Savaria, Y.; Sawan, M. Electronics and Packaging Intended for Emerging Harsh Environment Applications: A Review. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2085–2098. [Google Scholar] [CrossRef]

- Dreike, P.; Fleetwood, D.; King, D.; Sprauer, D.; Zipperian, T. An overview of high-temperature electronic device technologies and potential applications. IEEE Trans. Compon. Packag. Manuf. Technol. Part A 1994, 17, 594–609. [Google Scholar] [CrossRef]

- Huque, M.A.; Islam, S.K.; Tolbert, L.M.; Blalock, B.J. A 200 °C universal gate driver integrated circuit for extreme en-vironment applications. IEEE Trans. Power Electron. 2012, 27, 4153–4162. [Google Scholar] [CrossRef]

- Hassan, A.; Savaria, Y.; Sawan, M. GaN Integration Technology, an Ideal Candidate for High-Temperature Applications: A Review. IEEE Access 2018, 6, 78790–78802. [Google Scholar] [CrossRef]

- Neudeck, P.G.; Okojie, R.S.; Chen, L.-Y. High-temperature electronics—A role for wide bandgap semiconductors? Proc. IEEE 2002, 90, 1065–1076. [Google Scholar] [CrossRef] [Green Version]

- Elasser, A.; Chow, T. Silicon carbide benefits and advantages for power electronics circuits and systems. Proc. IEEE 2002, 90, 969–986. [Google Scholar] [CrossRef]

- Kargarrazi, S.; Yalamarthy, A.S.; Satterthwaite, P.F.; Blankenberg, S.W.; Chapin, C.; Senesky, D.G. Stable Operation of AlGaN/GaN HEMTs for 25 hours at 400 °C in air. IEEE J. Electron Devices Soc. 2019, 7, 931–935. [Google Scholar] [CrossRef]

- Herfurth, P.; Maier, D.; Men, Y.; Rösch, R.; Lugani, L.; Carlin, J.F.; Grandjean, N.; Kohn, E. GaN-on-insulator technology for high-temperature electronics beyond 400 °C. Semicond. Sci. Technol. 2013, 28, 074026. [Google Scholar] [CrossRef]

- Medjdoub, F.; Ducatteau, D.; Gaquière, C.; Carlin, J.-F.; Gonschorek, M.; Feltin, E.; Py, M.; Grandjean, N.; Kohn, E. Evaluation of AlInN/GaN HEMTs on sapphire substrate in microwave, time and temperature domains. Electron. Lett. 2007, 43, 309–311. [Google Scholar] [CrossRef]

- Lu, X.; Ma, J.; Yue, C.P.; Lau, K.M. A GaN-based Lamb-wave oscillator on silicon for high-temperature integrated sensors. IEEE Microw. Wirel. Compon. Lett. 2013, 23, 318–320. [Google Scholar] [CrossRef]

- Xu, Z.; Wang, J.; Cai, Y.; Liu, J.; Yang, Z.; Li, X.; Wang, M.; Yu, M.; Xie, B.; Wu, W.; et al. High temperature characteristics of GaN-based inverter integrated with enhancement-mode (E-mode) MOSFET and depletion-mode (D-mode) HEMT. IEEE Electron Device Lett. 2013, 35, 33–35. [Google Scholar] [CrossRef]

- Tang, G.; Kwan, A.M.H.; Wong, R.K.Y.; Lei, J.; Su, R.Y.; Yao, F.W.; Lin, Y.M.; Yu, J.L.; Tsai, T.; Tuan, H.C.; et al. Digital Integrated Circuits on an E-Mode GaN Power HEMT Platform. IEEE Electron Device Lett. 2017, 38, 1282–1285. [Google Scholar] [CrossRef]

- Bergogne, D.; Regis, G.; Rat, V.; Rothan, F.; Delaine, J.; Bouchet, T. Integrated GaN ICs, development and performance. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ‘19 ECCE Europe), Genova, Italy, 3–5 September 2019; IEEE: Piscataway, NJ, USA, 2019; p. P-1. [Google Scholar]

- Chowdhury, N.; Xie, Q.; Yuan, M.; Cheng, K.; Then, H.W.; Palacios, T. Regrowth-free GaN-based complementary logic on a Si substrate. IEEE Electron Device Lett. 2020, 41, 820–823. [Google Scholar] [CrossRef]

- Hassan, A.; Ali, M.; Trigui, A.; Hached, S.; Savaria, Y.; Sawan, M. Stability of GaN150-based HEMT in high temperature up to 400 °C. In Proceedings of the 2017 15th IEEE International New Circuits and Systems Conference (NEWCAS), Strasbourg, France, 25–28 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 133–136. [Google Scholar]

- Hassan, A.; Ali, M.; Savaria, Y.; Sawan, M. GaN-based LSK demodulators for wireless data receivers in high-temperature applications. Microelectron. J. 2019, 84, 129–135. [Google Scholar] [CrossRef]

- Hassan, A.; Ali, M.; Trigui, A.; Savaria, Y.; Sawan, M. A GaN-Based Wireless Monitoring System for High-Temperature Applications. Sensors 2019, 19, 1785. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Hassan, A.; Amer, M.; Savaria, Y.; Sawan, M. Fully Integrated Digital GaN-Based LSK Demodulator for High-Temperature Applications. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1579–1583. [Google Scholar] [CrossRef]

- Hassan, A.; Amer, M.; Savaria, Y.; Sawan, M. Towards GaN500-based High Temperature ICs: Characterization and Modeling up to 600 °C. In Proceedings of the 2020 18th IEEE International New Circuits and Systems Conference (NEWCAS), Montreal, QC, Canada, 16–19 June 2020; IEEE: Piscataway, NJ, USA, 2020. [Google Scholar]

- POLYSTIM Neurotechnologies. Available online: http://polystim.org/ (accessed on 20 December 2021).

- Gaska, R.; Gaevski, M.; Jain, R.; Deng, J.; Islam, M.; Simin, G.; Shur, M. Novel AlInN/GaN integrated circuits operating up to 500 °C. Solid-State Electron. 2015, 113, 22–27. [Google Scholar] [CrossRef]

- Wang, H.; Kwan, A.M.H.; Jiang, Q.; Chen, K.J. A GaN Pulse Width Modulation Integrated Circuit for GaN Power Converters. IEEE Trans. Electron Devices 2015, 62, 1143–1149. [Google Scholar] [CrossRef]

- Cui, M.; Sun, R.; Bu, Q.; Liu, W.; Wen, H.; Li, A.; Liang, Y.C.; Zhao, C. Monolithic GaN Half-Bridge Stages with Integrated Gate Drivers for High Temperature DC-DC Buck Converters. IEEE Access 2019, 7, 184375–184384. [Google Scholar] [CrossRef]

| Resistor | Value @ 25 °C (Ω) | Resistor | Value @ 25 °C (Ω) | Capacitor | Value @ 25 °C (pF) | Inductor | Value @ 25 °C (µH) |

|---|---|---|---|---|---|---|---|

| R1 | 102 | R7 | 5160 | C1 | 58 | L1 | 0.99 |

| R2 | 220 | R8 | 1316 | C2 | 56 | L2 | 0.97 |

| R3 | 802 | R9 | 540 | C3 | 83 | L3 | 0.86 |

| R4 | 340 | - | - | C4 | 75 | L4 | 1.5 |

| R5 | 816 | - | - | C5 | 73 | L5 | 1.45 |

| R6 | 3610 | - | - | - | - | L6 | 1.7 |

| Resistor | @ 25 °C (Ω) | @ 100 °C (Ω) | @ 200 °C (Ω) | @ 300 °C (Ω) | @ 350 °C (Ω) | @ 400 °C (Ω) | @ 450 °C (Ω) | @ 500 °C (Ω) | @ 550 °C (Ω) | @ 600 °C (Ω) | Slope (Ω/°C) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R1 | 102 | 108 | 118 | 128 | 134 | 140 | 148 | 157 | 164 | 176 | 0.11 |

| R2 | 220 | 230 | 243 | 258 | 266 | 274 | 283 | 296 | 305 | 326 | 0.16 |

| R3 | 802 | 824 | 858 | 893 | 911 | 928 | 944 | 976 | 994 | 1039 | 0.36 |

| R4 | 340 | 353 | 371 | 391 | 400 | 410 | 422 | 440 | 450 | 460 | 0.2 |

| R5 | 816 | 839 | 872 | 909 | 928 | 946 | 967 | 997 | 1008 | 1034 | 0.37 |

| R6 | 3610 | 3240 | 3350 | 3470 | 3530 | 3580 | 3640 | 3720 | 3740 | 3780 | 1.1 |

| R7 | 5160 | 5270 | 5450 | 5640 | 5730 | 5810 | 5910 | 6010 | 6020 | 6050 | 1.6 |

| R8 | 1316 | 1350 | 1400 | 1454 | 1481 | 1505 | 1538 | 1578 | 1591 | 1622 | 0.52 |

| R9 | 540 | 557 | 581 | 607 | 621 | 633 | 651 | 671 | 680 | 698 | 0.26 |

| Capacitor | @ 25 °C (pF) | @ 100 °C (pF) | @ 200 °C (pF) | @ 300 °C (pF) | @ 350 °C (pF) | @ 400 °C (pF) | @ 450 °C (pF) | @ 500 °C (pF) | @ 550 °C (pF) | @ 600 °C (pF) |

|---|---|---|---|---|---|---|---|---|---|---|

| C1 | 58 | 59 | 59 | 59.3 | 58.4 | 58.8 | 58.87 | 60.1 | 60.7 | 63.3 |

| C2 | 56 | 55.5 | 55.8 | 56.4 | 58.4 | 56.8 | 56.82 | 57 | 58.3 | 62.1 |

| C3 | 83 | 84 | 84 | 84 | 83.6 | 85.2 | 85 | 86.1 | 86.4 | 89.1 |

| C4 | 75 | 75 | 75.5 | 76.1 | 76.3 | 76.7 | 76.5 | 77.9 | 78.5 | 80.2 |

| C5 | 73 | 73 | 74.5 | 74.6 | 75 | 76.2 | 75.8 | 76.79 | 77.4 | 79.8 |

| Inductor | @ 25 °C (µH) | @ 120 °C (µH) | @ 150 °C (µH) | @ 200 °C (µH) | @ 250 °C (µH) | @ 300 °C (µH) |

|---|---|---|---|---|---|---|

| L1 | 0.99 | 0.99 | 1.03 | 1.09 | 1.26 | 1.36 |

| L2 | 0.975 | 0.975 | 1.1 | 1.105 | 1.31 | 1.3 |

| L3 | 0.86 | 0.86 | 0.855 | 0.9 | 1.05 | 1.14 |

| L4 | 1.5 | 1.28 | 1.3 | 1.4 | 1.5 | 1.6 |

| L5 | 1.45 | 1.45 | 1.45 | 1.5 | 1.58 | 1.58 |

| L6 | 1.7 | 1.7 | 1.7 | 1.7 | 1.8 | 1.9 |

| Inductor | @ 25 °C (Ω) | @ 120 °C (Ω) | @ 150 °C (Ω) | @ 200 °C (Ω) | @ 250 °C (Ω) | @ 300 °C (Ω) |

|---|---|---|---|---|---|---|

| L1 | 17.1 | 24.7 | 27.7 | 31.8 | 34.7 | 39.8 |

| L2 | 13.7 | 19.9 | 22.2 | 25.2 | 27.6 | 31.1 |

| L3 | 35.4 | 53.2 | 59.4 | 67.4 | 74.5 | 83.9 |

| L4 | 22.1 | 31.9 | 35.8 | 40.3 | 44.8 | 50 |

| L5 | 20.1 | 29.7 | 33.2 | 37.2 | 41.6 | 46.2 |

| L6 | 15.2 | 20.9 | 23.4 | 26 | 29.3 | 32.4 |

| Circuit | IDD (mA) | IGND (mA) | ISS (mA) | Power (mW) | Circuit | IDD (mA) | IGND (mA) | ISS (mA) | Powermax (mW) |

|---|---|---|---|---|---|---|---|---|---|

| INV1 | <1 | <1 | <1 | 20 | NOR2 | <1 | <1 | <1 | 20 |

| INV2 | 9 | 5 | 4 | 182 | NOR3 | 1.5 | 1 | <1 | 25 |

| INV3 | 6 | 5 | 1 | 98 | VREF1 | <1 | <1 | NA | 0.7 |

| INV4 | <1 | <1 | <1 | 20 | VREF2 | <1 | <1 | NA | 0.6 |

| INV5 | <1 | <1 | <1 | 20 | D Flip-Flop | 6 | 3 | 3 | 126 |

| INV6 | <1 | <1 | <1 | 20 | OSC1 | 13 | 8 | 5 | 252 |

| INV7 | 9 | 5 | 4 | 182 | OSC2 | 13 | 8 | 5 | 252 |

| NAND2 | <1 | <1 | <1 | 20 | DELAY | 150 | 60 | 90 | 3360 |

| NAND3 | <1 | <1 | <1 | 20 | - | - | - | - | - |

| Reference | GaN Technology | Reported ICs | Temperature | Year |

|---|---|---|---|---|

| [10] | GaN HEMT | Oscillator | 250 °C | 2013 |

| [11] | GaN MOSFET/HEMT | Inverter | 300 °C | 2014 |

| [21] | GaN HEMT | Inverter, Dif. Amp | 500 °C | 2015 |

| [22] | GaN HEMT | PWM | 250 °C | 2015 |

| [12] | GaN HEMT | Inverter, Oscillator | 200 °C | 2017 |

| [23] | GaN MIS-HFET | Gate driver | 250 °C | 2019 |

| [14] | GaN HEMT | Gate drive, Level shifter | 200 °C | 2019 |

| [15] | GaN MOSFET | Inverter | 300 °C | 2020 |

| This work | GaN HEMT | NAND, NOR, NOT, D Flip-Flop *, Delay *, Oscillator 1, Voltage reference + | 400 °C, 160 °C *, 550 °C + | 2021 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hassan, A.; Noël, J.-P.; Savaria, Y.; Sawan, M. Circuit Techniques in GaN Technology for High-Temperature Environments. Electronics 2022, 11, 42. https://doi.org/10.3390/electronics11010042

Hassan A, Noël J-P, Savaria Y, Sawan M. Circuit Techniques in GaN Technology for High-Temperature Environments. Electronics. 2022; 11(1):42. https://doi.org/10.3390/electronics11010042

Chicago/Turabian StyleHassan, Ahmad, Jean-Paul Noël, Yvon Savaria, and Mohamad Sawan. 2022. "Circuit Techniques in GaN Technology for High-Temperature Environments" Electronics 11, no. 1: 42. https://doi.org/10.3390/electronics11010042