LIHL: Design of a Novel Loop Interlocked Hardened Latch

Abstract

:1. Introduction

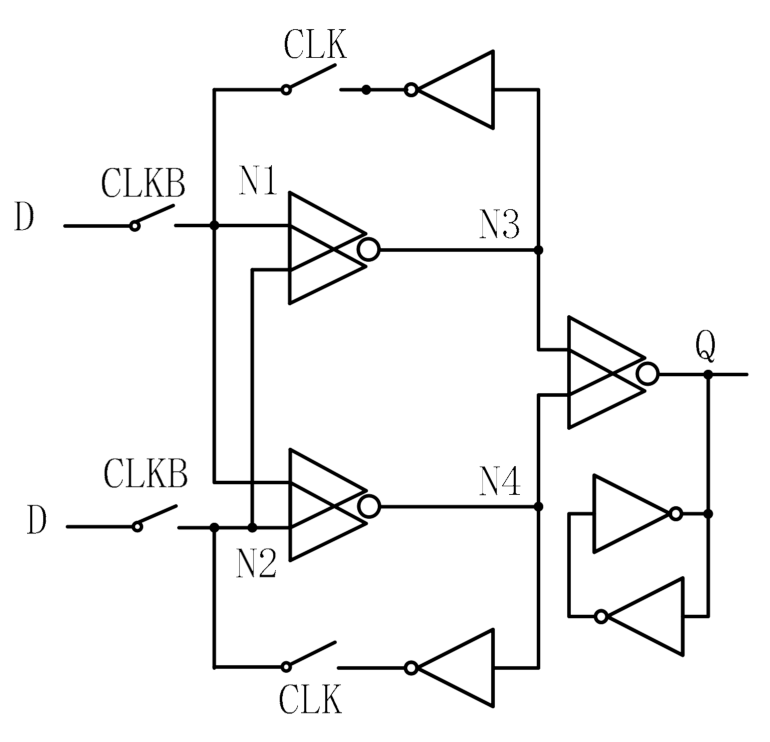

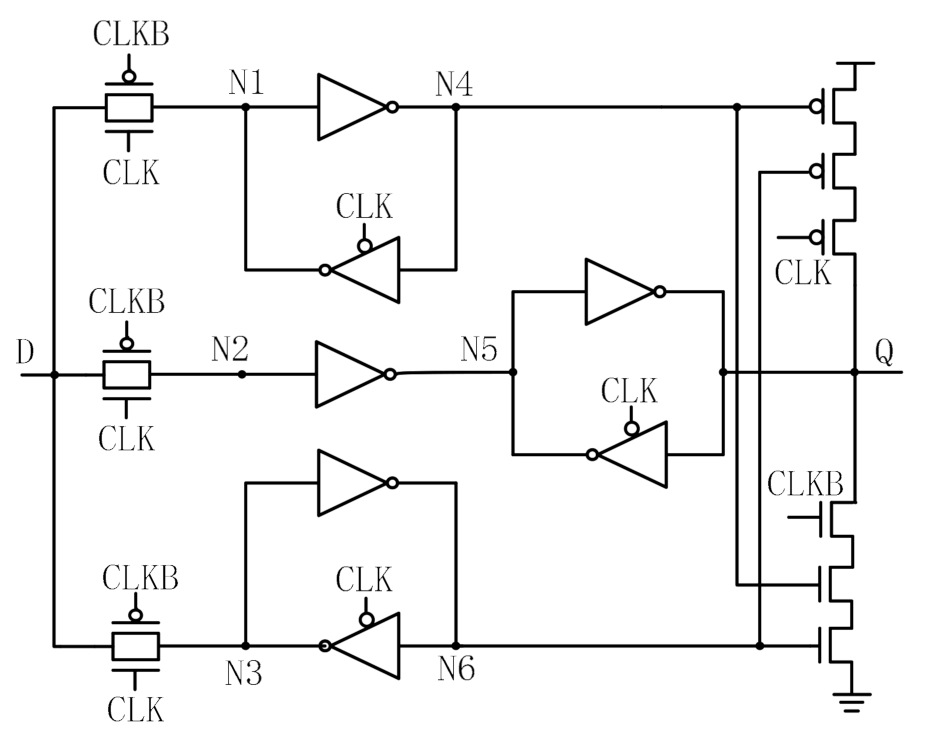

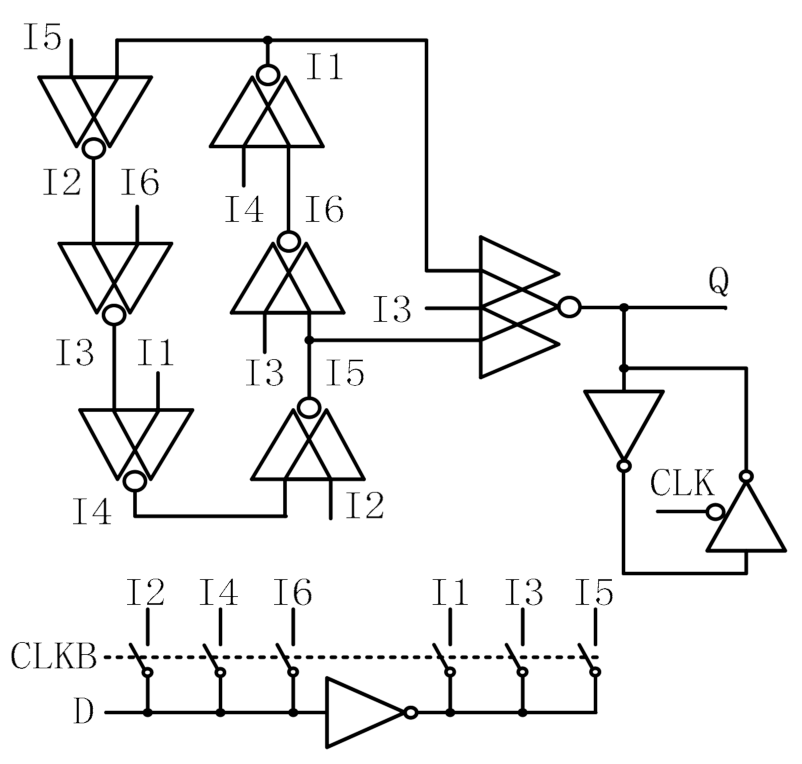

2. Previous Works

3. Proposed Design and Simulation Results

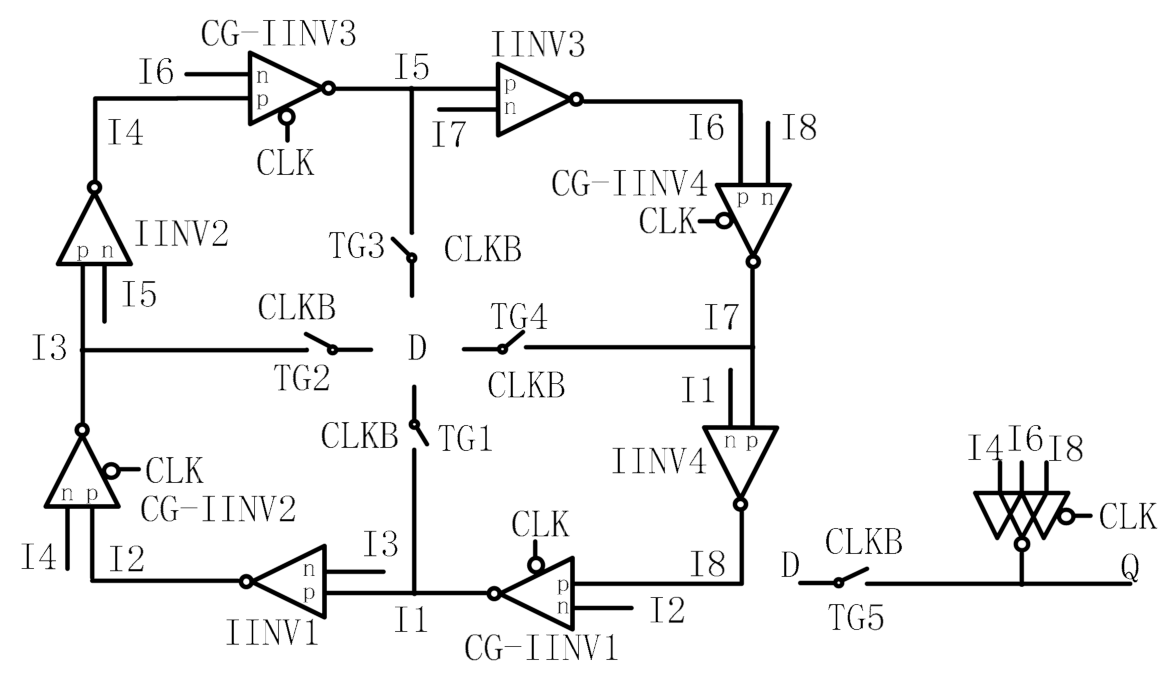

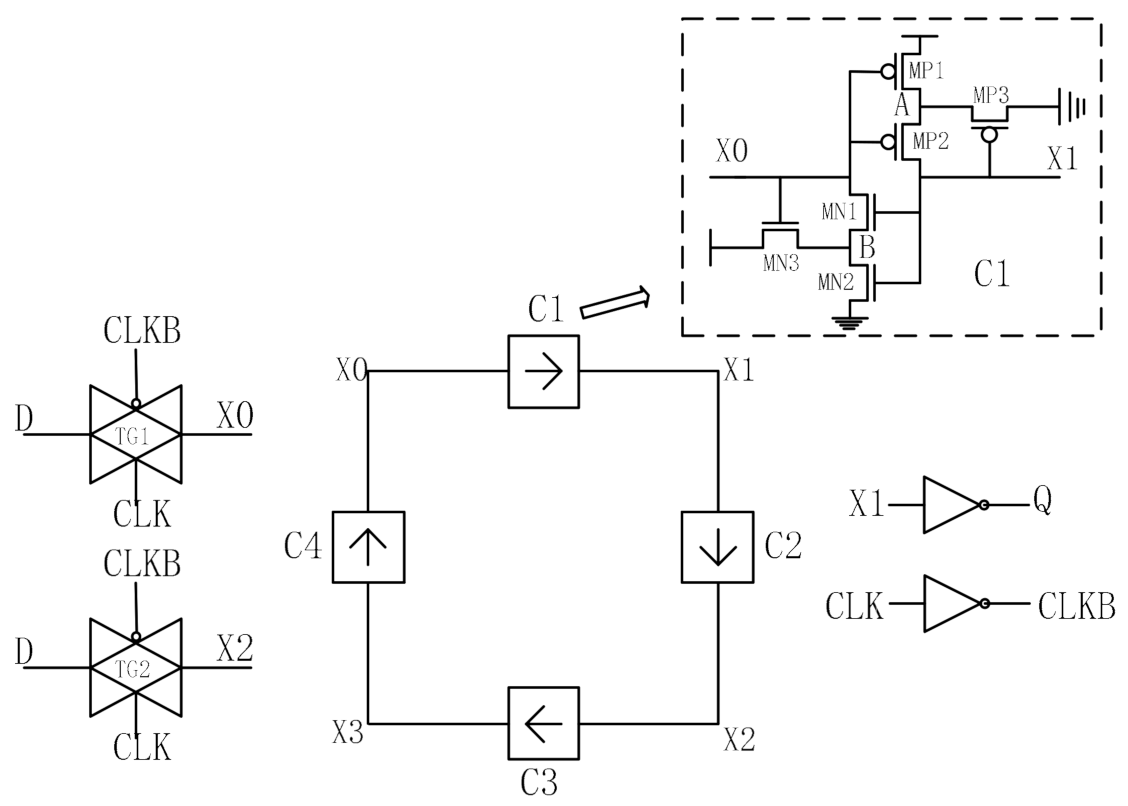

3.1. Proposed Design

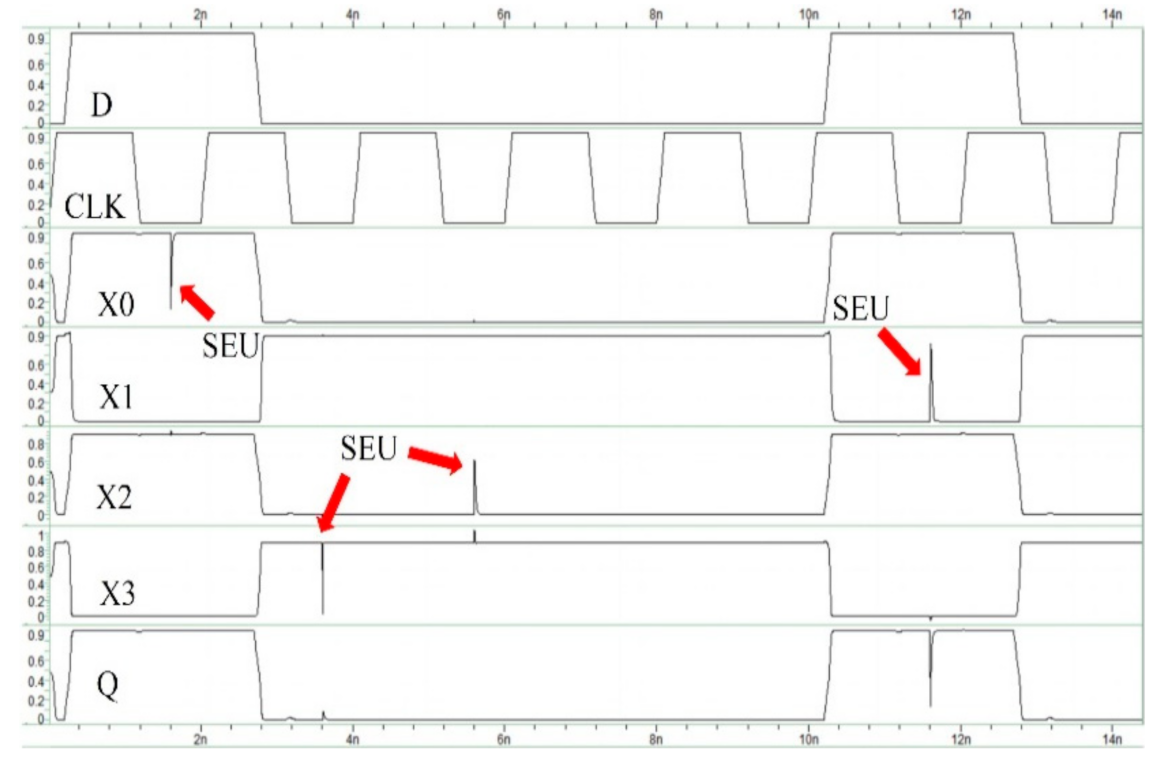

3.2. Single Node Upsets Analysis

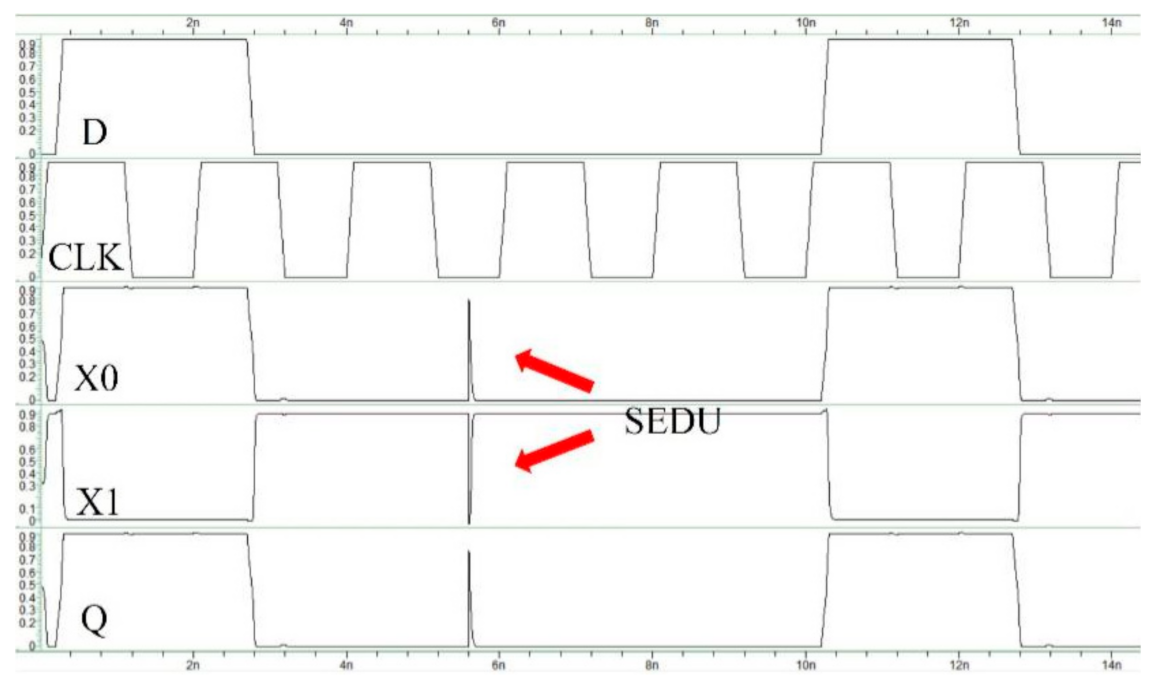

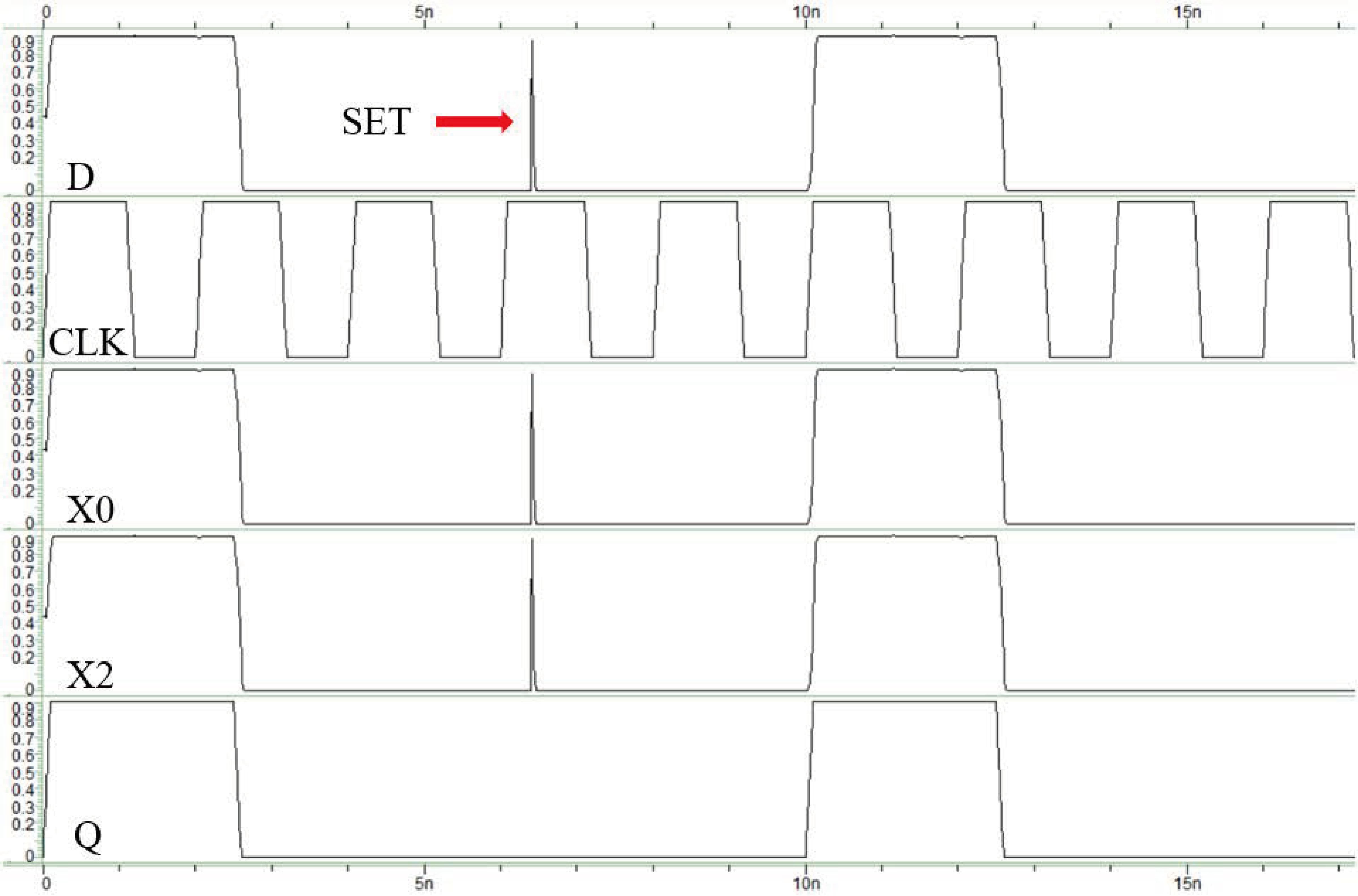

3.3. Double Node Upsets and SET Analysis

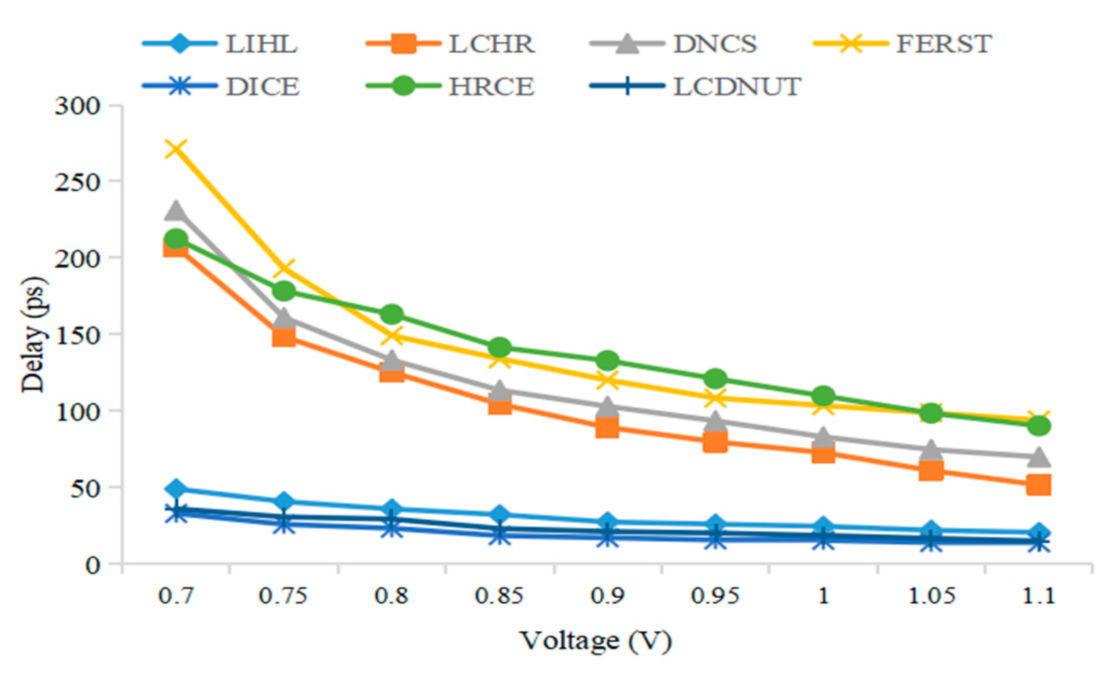

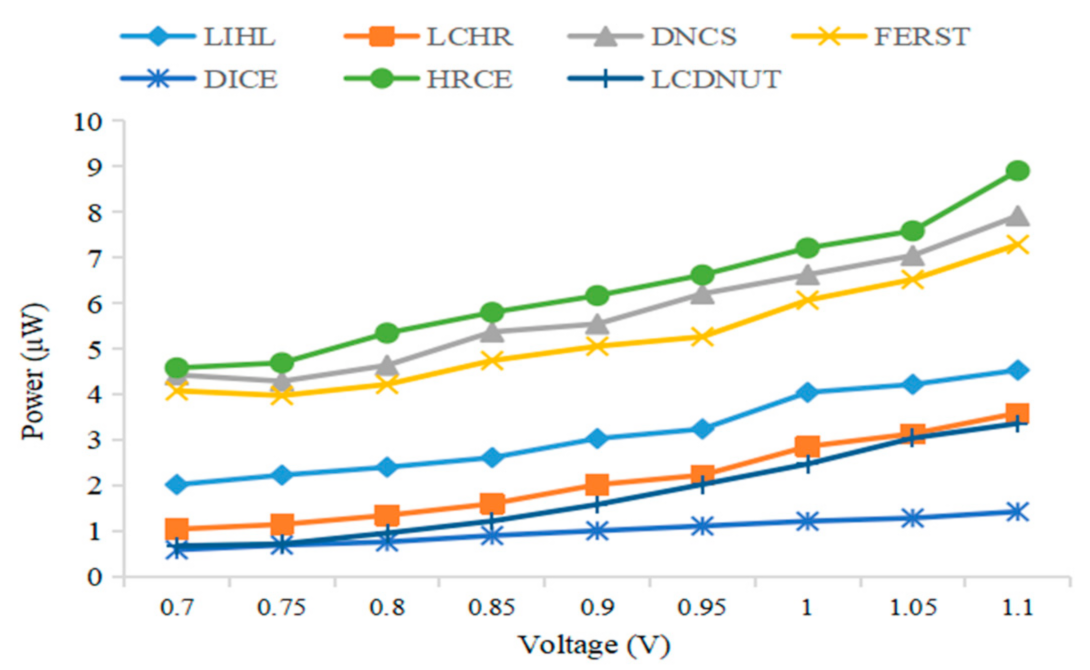

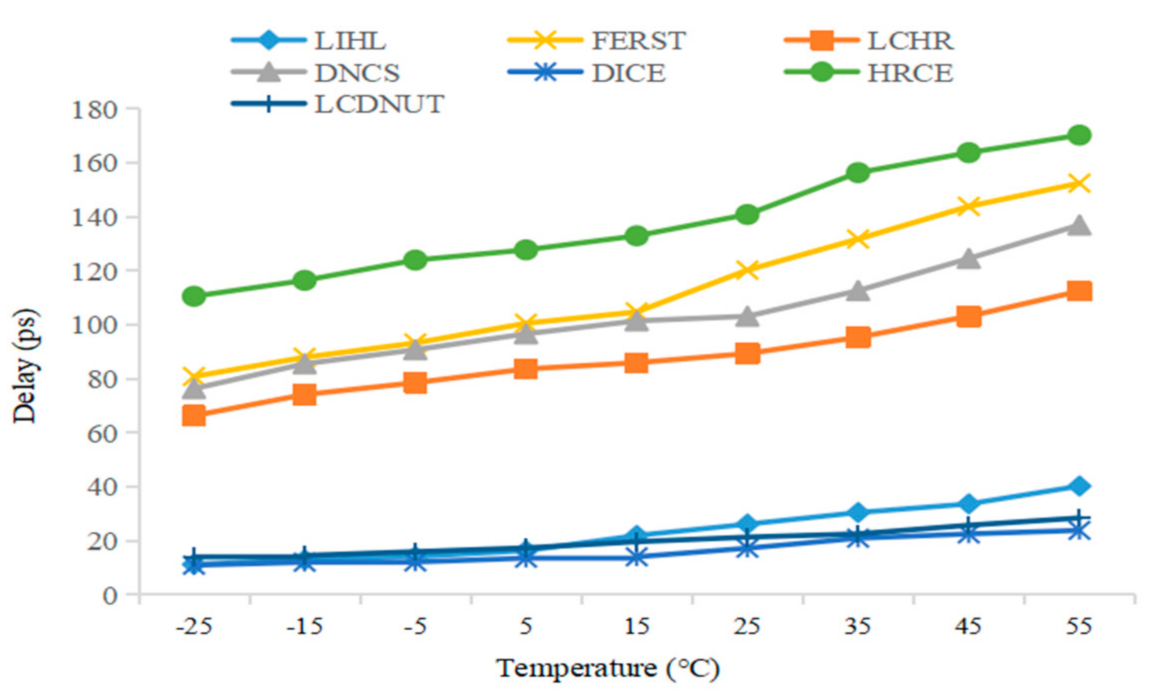

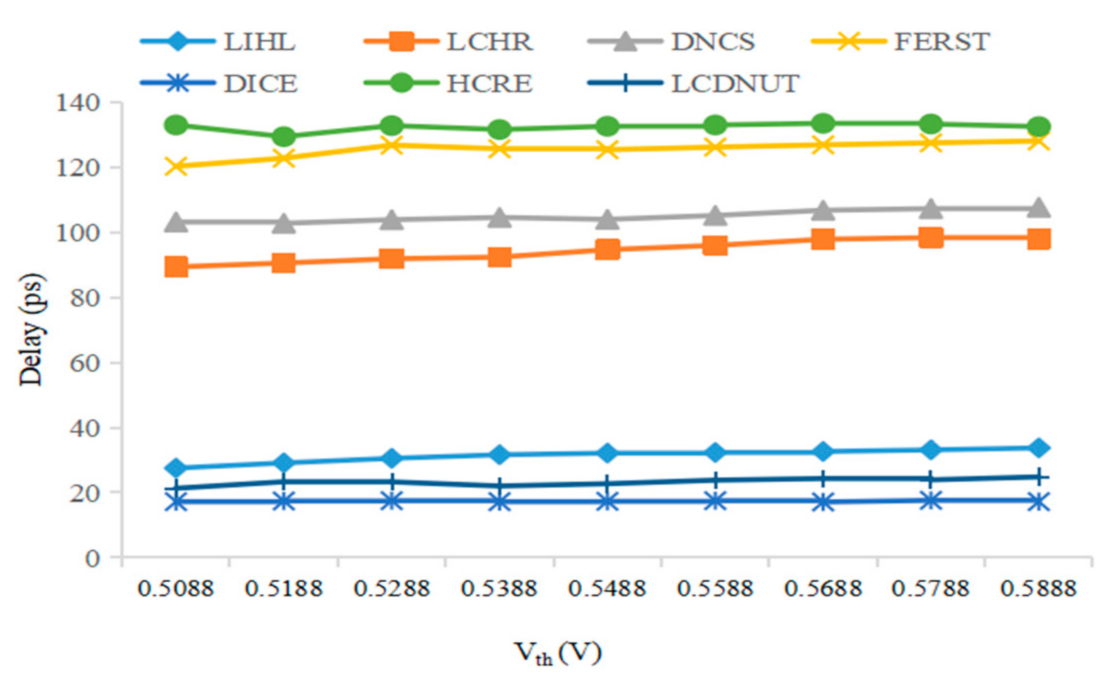

3.4. Comparisons

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Gadlage, M.J.; Roach, A.H.; Duncan, A.R.; Williams, A.M.; Bossev, D.P.; Kay, M.J. Soft errors induced by high energy electrons. IEEE Trans. Device Mater. Reliab. 2017, 17, 157–162. [Google Scholar] [CrossRef]

- Zhang, H.; Jiang, H.; Assis, T.R.; Ball, D.R.; Narasimham, B.; Anvar, A.; Massengill, L.W.; Bhuva, B.L. Angular Effects of Heavy-Ion Strikes on Single-Event Upset Response of Flip-Flop Designs in 16-nm Bulk FinFET Technology. IEEE Trans. Nucl. Sci. 2017, 64, 491–496. [Google Scholar] [CrossRef]

- Zhang, H.; Jiang, H.; Assis, T.R.; Mahatme, N.N.; Narasimham, B.; Massengill, L.W.; Bhuva, B.L.; Wen, S.; Wong, R. Effects of Threshold Voltage Variations on Single-Event Upset Response of Sequential Circuits at Advanced Technology Nodes. IEEE Trans. Nucl. Sci. 2017, 64, 457–463. [Google Scholar] [CrossRef]

- Gill, B.; Seifert, N.; Zia, V. Comparison of alpha particle and neutron-induced combinational and sequential logic error rates at the 32 nm technology node. In Proceedings of the IEEE International Reliability Physics Symposium, Montreal, QC, Canada, 26–30 April 2009; pp. 199–205. [Google Scholar] [CrossRef]

- Anjan, S.; Maryam, B. Robust soft error tolerant CMOS latch configurations. IEEE Trans. Comput. 2016, 65, 2820–2834. [Google Scholar] [CrossRef]

- Gill, B.S.; Papachristou, C.; Wolff, F.G.; Seifert, N. Node sensitivity analysis for soft errors in CMOS logic. In Proceedings of the IEEE International Conference on Test, Austin, TX, USA, 8–8 November 2005; pp. 1–9. [Google Scholar] [CrossRef]

- Yan, A.; Yang, K.; Huang, Z.; Zhang, J.; Cui, J.; Fang, X.; Yi, M.; Wen, X. A double-node-upset self-recoverable latch design for high performance and low power application. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 287–291. [Google Scholar] [CrossRef]

- Jagannathan, S.; Loveless, T.D.; Bhuva, B.L.; Wen, S.; Wong, R.; Sachdev, M.; Rennie, D.; Massengill, L.W. Single-event tolerant flip-flop design in 40nm bulk CMOS technology. IEEE Trans. Nucl. Sci. 2011, 58, 3033–3037. [Google Scholar] [CrossRef]

- Baumann, R.C. Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans. Device Mater. Reliab. 2005, 5, 305–316. [Google Scholar] [CrossRef]

- Chandra, V.; Aitken, R. Impact of voltage scaling on nanoscale SRAM reliability. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition, Nice, France, 20–24 April 2009; pp. 387–392. [Google Scholar] [CrossRef]

- Rajaei, R.; Asgari, B.; Tabandeh, M.; Fazeli, M. Design of robust SRAM cells against single-event multiple effects for nanometer technologies. IEEE Trans. Device Mater. Reliab. 2015, 15, 429–436. [Google Scholar] [CrossRef]

- Black, J.; Dodd, P.; Warren, K. Physics of multiple node charge collection and impacts on single-event characterization and soft error rate prediction. IEEE Trans. Nucl. Sci. 2013, 60, 1836–1851. [Google Scholar] [CrossRef]

- Yamamoto, Y.; Namba, K. Construction of Latch Design with Complete Double Node Upset Tolerant Capability Using C-Element. In Proceedings of the International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, Chicago, IL, USA, 8–10 October 2018; pp. 8–10. [Google Scholar] [CrossRef]

- Guo, J.; Zhu, L.; Liu, W.; Huang, H.; Liu, S.; Wang, T.; Xiao, L.; Mao, Z. Novel radiation-hardened-by-design (RHBD) 12T memory cell for aerospace applications in nanoscale CMOS technology. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 1593–1600. [Google Scholar] [CrossRef]

- Huang, Z.; Liang, H.; Hellebrand, S. A high performance SEU tolerant latch. J. Electron. Test. 2015, 31, 349–359. [Google Scholar] [CrossRef]

- Calin, T.; Nicolaidis, M.; Velazco, R. Upset hardened memory design for submicron CMOS technology. IEEE Trans. Nucl. Sci. 1996, 43, 2874–2878. [Google Scholar] [CrossRef]

- Alioto, M.; Consoli, E.; Palumbo, G. Variations in nanometer CMOS flip-flops: Part I-impact of process variations on timing. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2035–2043. [Google Scholar] [CrossRef]

- Omana, M.; Rossi, D.; Metra, C. High-performance robust latches. IEEE Trans. Comput. 2010, 59, 1455–1465. [Google Scholar] [CrossRef]

- She, X.; Li, N.; Tong, J. SEU tolerant latch based on error detection. IEEE Trans. Nucl. Sci. 2012, 59, 211–214. [Google Scholar] [CrossRef]

- Mitra, S.; Zhang, M.; Seifert, N.; Mak, T.; Kim, K.S. Built-in soft error resilience for robust system design. In Proceedings of the IEEE International Conference on Integrated Circuit Design and Technology, Austin, TX, USA, 30 May–1 June 2007; pp. 1–6. [Google Scholar] [CrossRef]

- She, X.; Mcelvain, K. Time multiplexed triple modular redundancy for single event upset mitigation. IEEE Trans. Nucl. Sci. 2009, 56, 2443–2448. [Google Scholar] [CrossRef]

- Yan, A.; Liang, H.; Huang, Z.; Jiang, C.; Yi, M. A self-recoverable, frequency-aware and cost-effective robust latch design for nanoscale CMOS technology. IEICE Trans. Electronic 2015, 98, 1171–1178. [Google Scholar] [CrossRef]

- Shah, J.; Nairn, D.; Sachdev, M. A 32 kb macro with 8T soft error robust, SRAM cell in 65nm CMOS. IEEE Trans. Nucl. Sci. 2015, 62, 1367–1374. [Google Scholar] [CrossRef]

- Wang, H.; Chen, L.; Liu, R.; Li, Y.; Kauppila, J.S.; Bhuva, B.L.; Lilja, K.; Wen, S.; Wong, R.; Fung, R.; et al. An Area Efficient Stacked Latch Design Tolerant to SEU in 28 nm FDSOI Technology. IEEE Trans. Nucl. Sci. 2016, 63, 3003–3009. [Google Scholar] [CrossRef]

- Alidash, H.K.; Oklobdzija, V. Low-power soft error hardened latch. J. Low Power Electron. 2010, 6, 218–226. [Google Scholar] [CrossRef]

- Rajaei, R.; Tabandeh, M.; Fazeli, M. Low cost soft error hardened latch designs for nano-scale CMOS technology in presence of process variation. Microelectron. Reliab. 2013, 53, 912–924. [Google Scholar] [CrossRef]

- Fazeli, M.; Miremadi, S.G.; Ejlali, A.; Patooghy, A. Low energy single event upset/single event transient-tolerant latch for deep submicron technologies. IET Comput. Digit. Tech. 2009, 3, 289–303. [Google Scholar] [CrossRef]

- Qi, C.; Xiao, L.; Guo, J.; Wang, T. Low cost and highly reliable radiation hardened latch design in 65 nm CMOS technology. Microelectron. Reliab. 2015, 55, 863–872. [Google Scholar] [CrossRef]

- Eftaxiopoulos, N.; Axelos, N.; Zervakis, G.; Tsoumanis, K.; Pekmestzi, K. Delta DICE: A Double Node Upset resilient latch. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Fort Collins, CO, USA, 2–5 August 2015; pp. 2–5. [Google Scholar] [CrossRef]

- Eftaxiopoulos, N.; Axelos, N.; Pekmestzi, K. DONUT: A double node upset tolerant latch. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, Montpellier, France, 8–10 July 2015; pp. 509–514. [Google Scholar] [CrossRef]

- Katsarou, K.; Tsiatouhas, Y. Soft error interception latch: Double node charge sharing SEU tolerant design. Electron. Lett. 2015, 51, 330–332. [Google Scholar] [CrossRef]

- Xu, H.; Zeng, Y. Circuit and layout combination technique to enhance multiple nodes upset tolerance in latches. IEICE Electron. Express 2015, 12, 1–7. [Google Scholar] [CrossRef] [Green Version]

- Li, Y.; Wang, H.; Yao, S.; Yan, X.; Gao, Z.; Xu, J. Double node upsets hardened latch circuits. J. Electron. Test. 2015, 31, 537–548. [Google Scholar] [CrossRef]

- Eftaxiopoulos, N.; Axelos, N.; Pekmestzi, K. DIRT latch: A novel low cost double node upset tolerant latch. Microelectron. Reliab. 2017, 68, 57–68. [Google Scholar] [CrossRef]

- Wei, W.; Namba, K.; Kim, Y.; Lombardi, F. A novel scheme for tolerating single event/multiple bit upsets (SEU/MBU) in non-volatile memories. IEEE Trans. Comput. 2016, 65, 781–790. [Google Scholar] [CrossRef]

- Li, H.; Xiao, L.; Li, J. High robust and cost effective double node upset tolerant latch design for nanoscale CMOS technology. Microelectron. Reliab. 2019, 93, 89–97. [Google Scholar] [CrossRef]

- Yan, A.; Lai, C.; Zhang, Y.; Cui, J.; Huang, Y.; Song, J.; Guo, J.; Weng, X. Novel Low Cost, Double-and-Triple-Node-Upset-Tolerant Latch Designs for Nano-scale CMOS. IEEE Trans. Emerg. Top. Comput. 2021, 9, 520–533. [Google Scholar] [CrossRef] [Green Version]

- Predictive Technology Model. Available online: http://ptm.asu.edu (accessed on 22 February 2006).

- Weste, N.H.E.; Harris, D.M. CMOS VLSI Design: A Circuits and Systems Perspective, 4th ed.; Addison-Wesley: Boston, MA, USA, 2011; p. 318. [Google Scholar]

- Yan, A.; Ling, Y.; Cui, J.; Chen, Z.; Huang, Z.; Song, J.; Girard, P.; Wen, X. Graduate School of Computer Science and Systems Engineering, Kyushu Institute of Technology, Fukuoka, Japan Quadruple Cross-Coupled Dual-Interlocked-Storage-Cells-Based Multiple-Node-Upset- Tolerant Latch Designs. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 879–890. [Google Scholar] [CrossRef]

| Latch | SEU Tolerance | SEDU Tolerance | SET Tolerance |

|---|---|---|---|

| DICE [16] | YES | NO | NO |

| FERST [27] | YES | NO | YES |

| DNCS [31] | YES | YES | NO |

| LCHR [28] | YES | NO | YES |

| HRCE [36] | YES | YES | NO |

| LCDNUT [37] | YES | YES | NO |

| LIHL (proposed) | YES | YES | YES |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, H.; Liu, X.; Yu, G.; Liang, H.; Huang, Z. LIHL: Design of a Novel Loop Interlocked Hardened Latch. Electronics 2021, 10, 2090. https://doi.org/10.3390/electronics10172090

Xu H, Liu X, Yu G, Liang H, Huang Z. LIHL: Design of a Novel Loop Interlocked Hardened Latch. Electronics. 2021; 10(17):2090. https://doi.org/10.3390/electronics10172090

Chicago/Turabian StyleXu, Hui, Xuan Liu, Guo Yu, Huaguo Liang, and Zhengfeng Huang. 2021. "LIHL: Design of a Novel Loop Interlocked Hardened Latch" Electronics 10, no. 17: 2090. https://doi.org/10.3390/electronics10172090