Strained Si0.2Ge0.8/Ge multilayer Stacks Epitaxially Grown on a Low-/High-Temperature Ge Buffer Layer and Selective Wet-Etching of Germanium

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

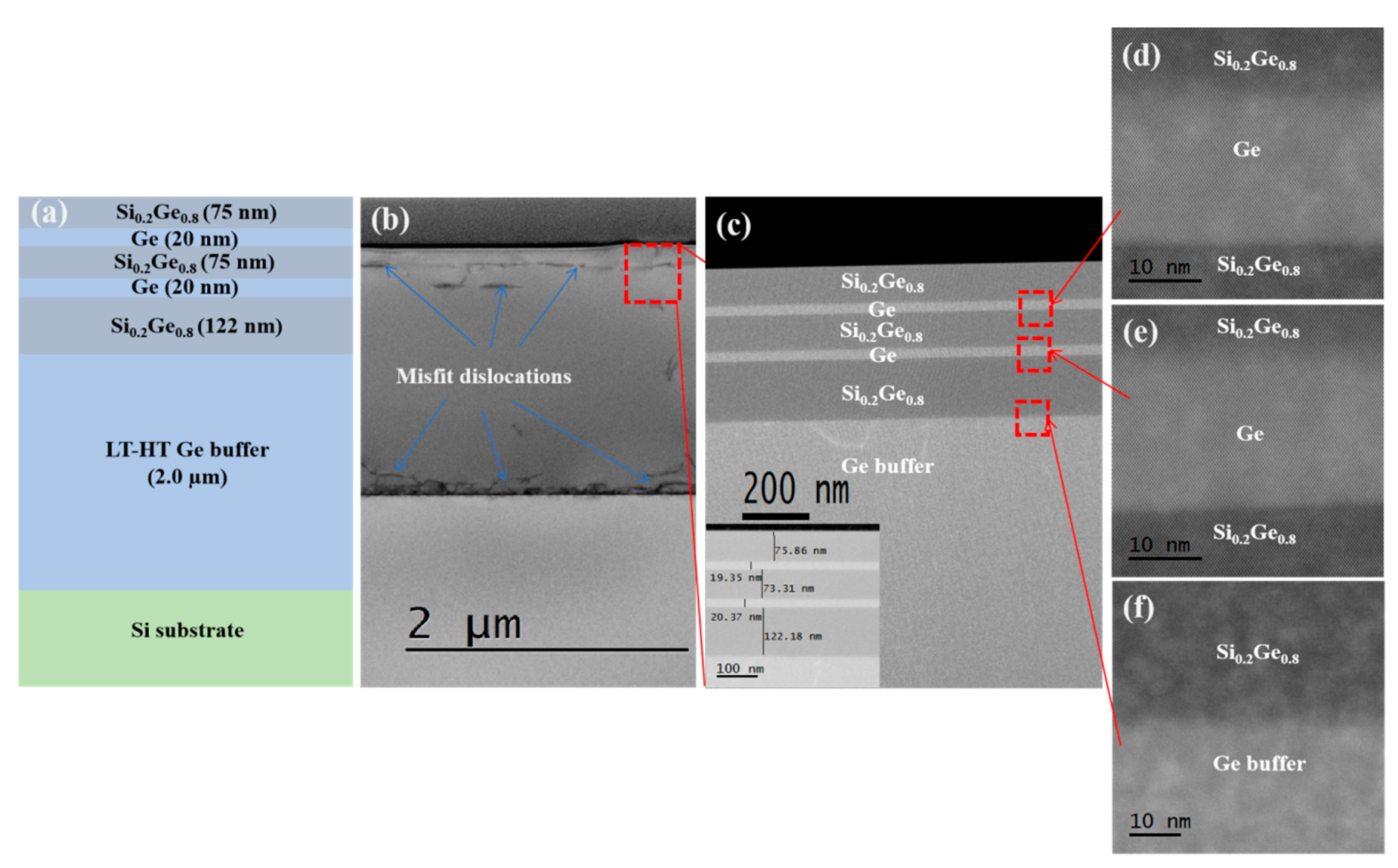

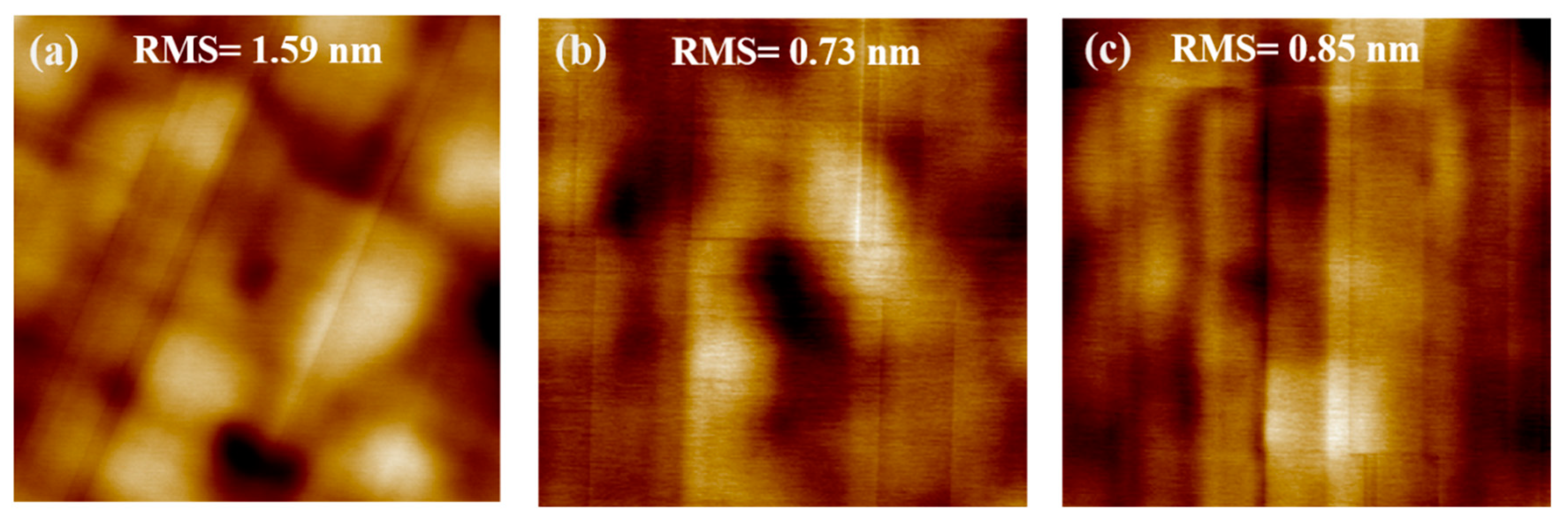

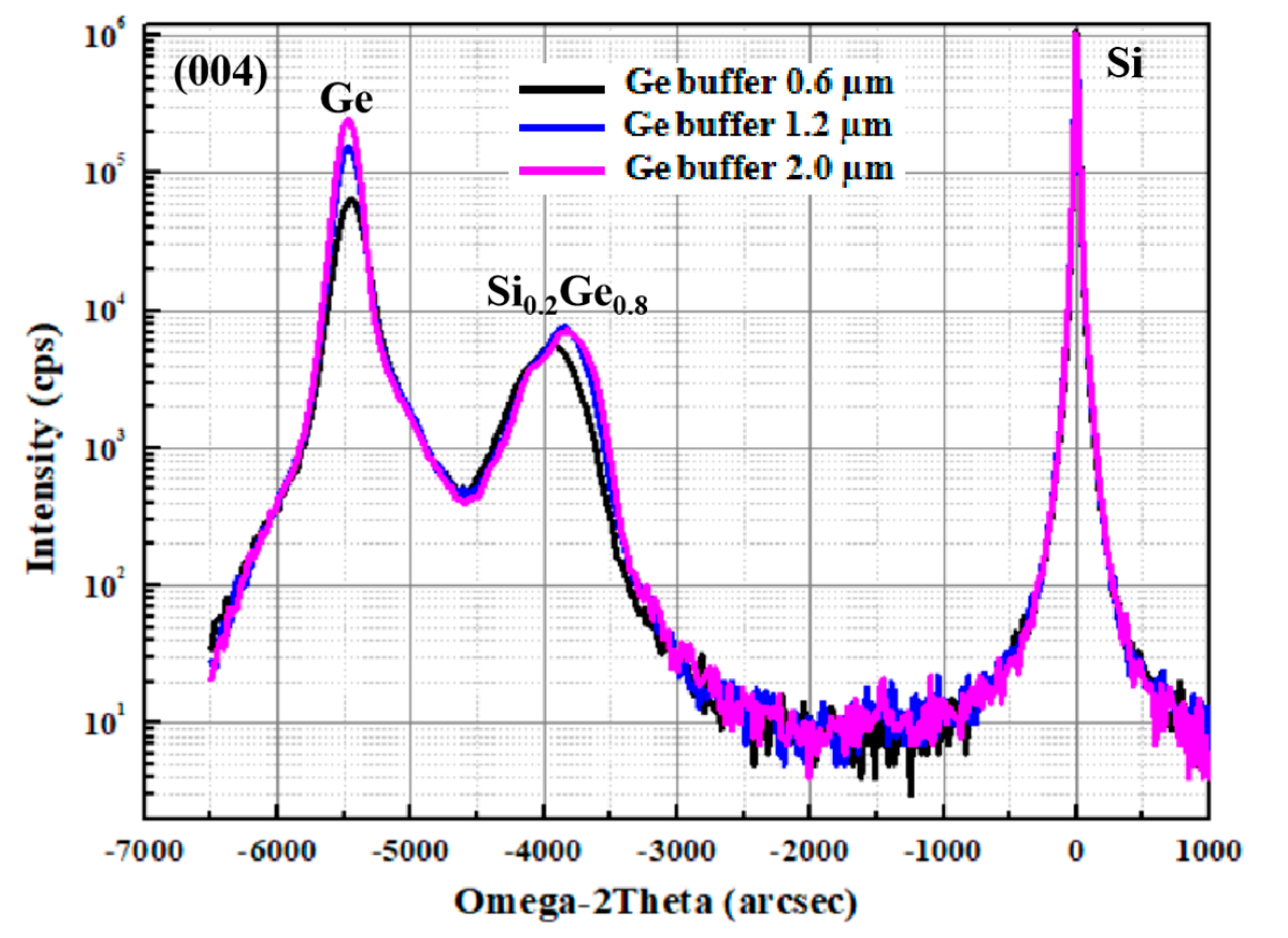

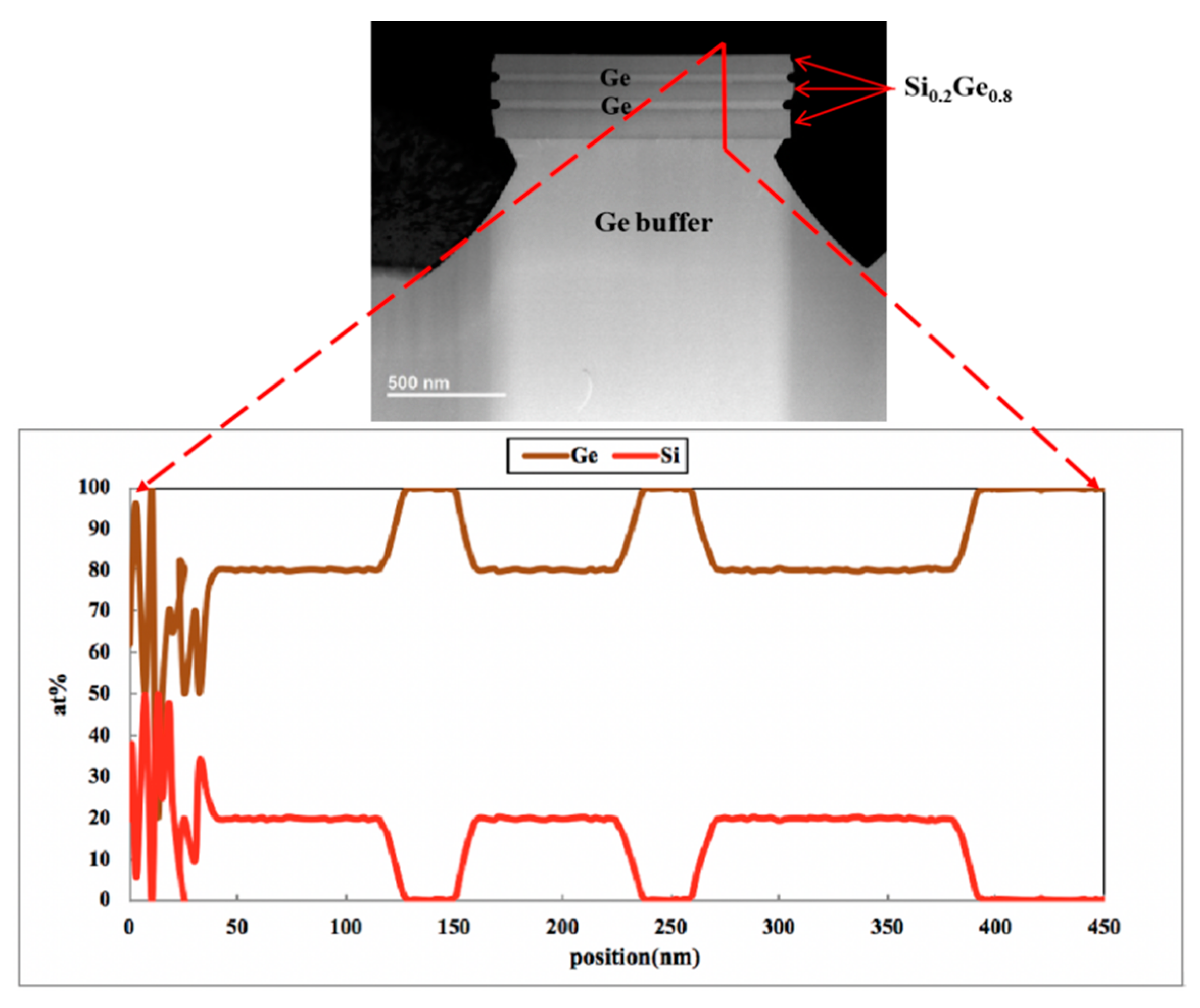

3.1. High Epitaxial Quality of the Si0.2Ge0.8/Ge Stack Structure

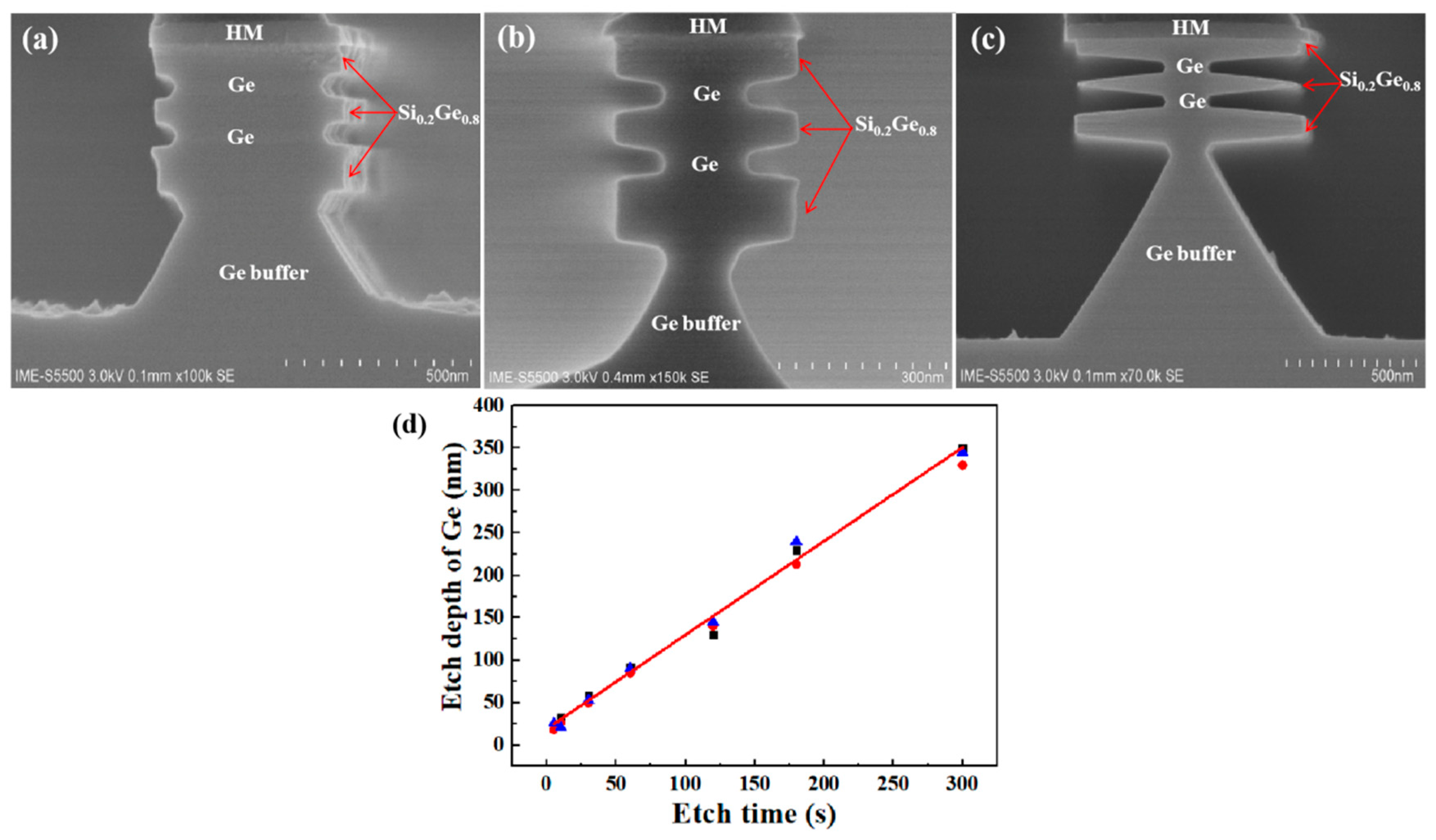

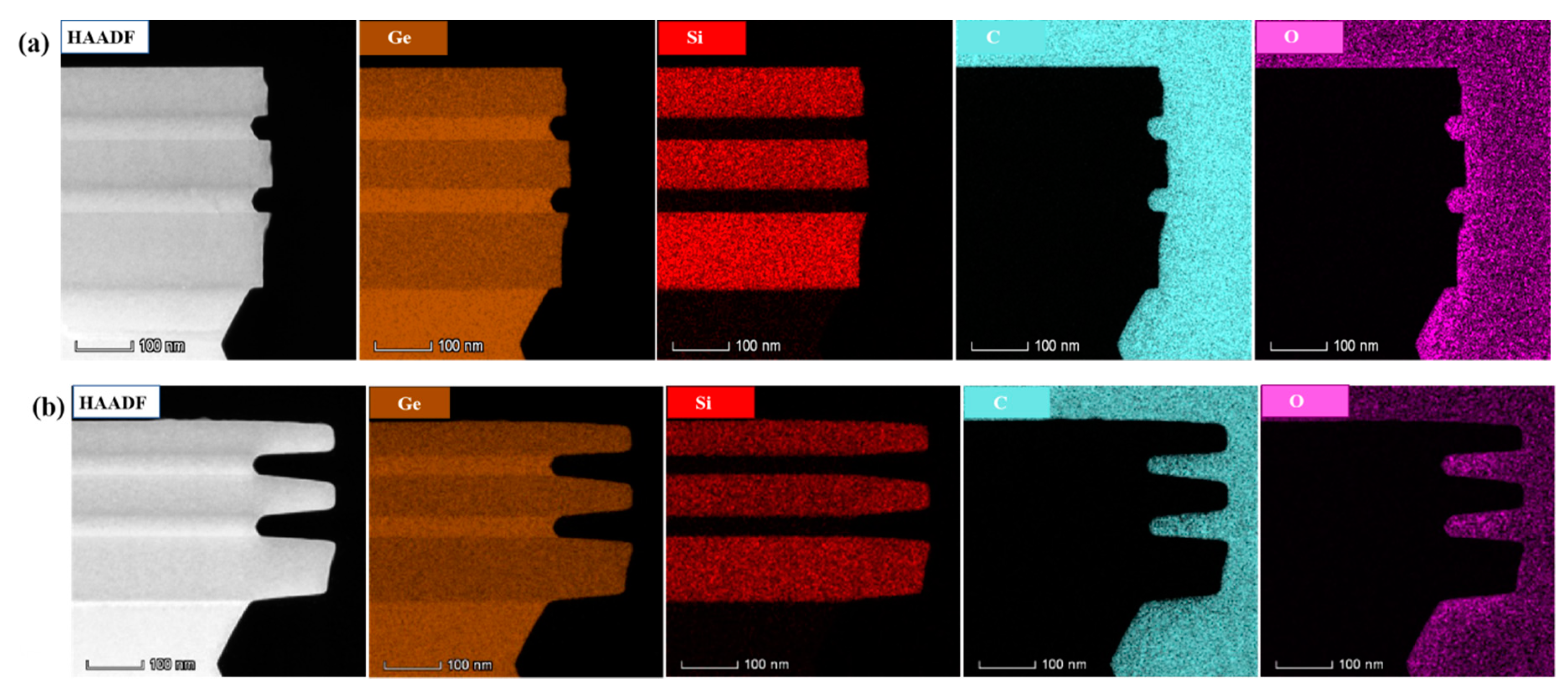

3.2. Selective Wet-Etching of Ge to Si0.2Ge0.8

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Radamson, H.H.; Luo, J.; Simoen, E.; Zhao, C. CMOS Past, Present and Future; Woodhead Publishing: Cambridge, UK, 2018. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Yin, X.; Yang, H.; Xie, L.; Ai, X.Z.; Zhang, Y.B.; Jia, K.P.; Wu, Z.; Ma, X.; Zhang, Q.Z.; Mao, S.; et al. Vertical Sandwich Gate-All-Around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variation. IEEE Electron Device Lett. 2019, 41, 8–11. [Google Scholar] [CrossRef]

- Liu, M.; Scholz, S.; Mertens, K.; Bae, J.H.; Hartmann, J.; Knoch, J.; Buca, D.; Zhao, Q. First Demonstration of Vertical Ge0.92Sn0.08/Ge and Ge GAA Nanowire pMOSFETs with Low SS of 66 mV/dec and Small DIBL of 35 mV/V. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Radamson, H.H.; Zhang, Y.; He, X.; Cui, H.; Li, J.; Xiang, J.; Liu, J.; Gu, S.; Wang, G. The Challenges of Advanced CMOS Process from 2D to 3D. Appl. Sci. 2017, 7, 1047. [Google Scholar] [CrossRef]

- Bera, L.K.; Nguyen, H.S.; Singh, N.; Liow, T.Y.; Huang, D.X.; Hoe, K.M.; Tung, C.H.; Fang, W.W.; Rustagi, S.C.; Jiang, Y.; et al. Three Dimensionally Stacked SiGe Nanowire Array and Gate-All-Around p-MOSFETs. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Dupré, C.; Hubert, A.; Beçu, S.; Jublot, M.; Maffini-Alvaro, V.; Vizioz, C.; Aussenac, F.; Arvet, C.; Barnola, S.; Hartmann, J.-M.; et al. 15nm-Diameter 3D Stacked Nanowires with Independent Gates Operation: ΦFET. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Gu, J.J.; Wang, X.W.; Shao, J.; Neal, A.T.; Manfra, M.J.; Gordon, R.G.; Ye, P.D. III-V Gate-All-Around Nanowire MOSFET Process Technology: From 3D to 4D. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 23.7.1–23.7.4. [Google Scholar]

- Radamson, H.; Thylén, L. Monolithic Nanoscale Photonics–Electronics Integration in Silicon and Other Group IV Elements; Academic Press: Cambridge, MA, USA, 2015. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Hikavyy, A.; Kim, M.S.; Tao, Z.; Wostyn, K.; Chew, S.A.; De Keersgieter, A.; Mannaert, G.; Rosseel, E.; et al. Gate-All-Around MOSFETs based on Vertically Stacked Horizontal Si Nanowires in a Replacement Metal Gate Process on Bulk Si Substrates. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Huang, Y.-S.; Lu, F.-L.; Tsou, Y.-J.; Tsai, C.-E.; Lin, C.-Y.; Huang, C.-H.; Liu, C.W. First Vertically Stacked GeSn Nanowire pGAAFETs with Ion = 1850μA/μm (Vov = Vds = −1V) on Si by GeSn/Ge CVD Epitaxial Growth and Optimum Selective Etching. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 37.5.1–37.5.4. [Google Scholar] [CrossRef]

- Chu, C.L.; Wu, K.; Luo, G.-L.; Chen, B.-Y.; Chen, S.-H.; Wu, W.-F.; Yeh, W. Stacked Ge-Nanosheet GAAFETs Fabricated by Ge/Si Multilayer Epitaxy. IEEE Electron Device Lett. 2018, 39, 1133–1136. [Google Scholar] [CrossRef]

- Radamson, H.H.; He, X.; Zhang, Q.; Liu, J.; Cui, H.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; Gao, J.; et al. Miniaturization of CMOS. Micromachines 2019, 10, 293. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Rishinaramangalam, A.K.; Masabih, S.M.U.; Fairchild, M.N.; Wright, J.B.; Shima, D.M.; Balakrishnan, G.; Brener, I.; Brueck, S.; Feezell, D.F. Controlled Growth of Ordered III-Nitride Core–Shell Nanostructure Arrays for Visible Optoelectronic Devices. J. Electron. Mater. 2014, 44, 1255–1262. [Google Scholar] [CrossRef]

- Yeh, T.-W.; Lin, Y.-T.; Ahn, B.; Stewart, L.S.; Dapkus, P.D.; Nutt, S.R. Vertical nonpolar growth templates for light emitting diodes formed with GaN nanosheets. Appl. Phys. Lett. 2012, 100, 033119. [Google Scholar] [CrossRef] [Green Version]

- Kim, R.; Avci, U.E.; Young, I.A. CMOS Performance Benchmarking of Si, InAs, GaAs, and Ge Nanowire n- and pMOSFETs with Lg=13 nm based on Atomistic Quantum Transport Simulation including Strain Effects. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 34.1.1–34.1.4. [Google Scholar] [CrossRef]

- Wang, G.L.; Qin, C.L.; Yin, H.X.; Luo, J.; Duan, N.Y.; Yang, P.; Gao, X.Y.; Yang, T.; Li, J.F.; Yan, J.; et al. Study of SiGe selective epitaxial process integration with high-k and metal gate for 16/14nm nodes FinFET technology. Microelectron. Eng. 2016, 163, 49–54. [Google Scholar] [CrossRef]

- Wang, G. Investigation on SiGe Selective Epitaxy for Source and Drain Engineering in 22 nm CMOS Technology Node and Beyond; Springer: Singapore, 2019. [Google Scholar]

- Orlowski, M. Si, SiGe, Ge, and III-V Semiconductor Nanomembranes and Nanowires Enabled by SiGe Epitaxy. ECS Meet. Abstr. 2010, 33, 777–789. [Google Scholar] [CrossRef] [Green Version]

- Raissi, M.; Regula, G.; Belgacem, C.H.; Rochdi, N.; Bozzo-Escoubas, S.; Coudreau, C.; Hollander, B.; Fnaiech, M.; D’Avitaya, F.; Lazzari, J.-L. Different architectures of relaxed Si1−xGex/Si pseudo-substrates grown by low-pressure chemical vapor deposition: Structural and morphological characteristics. J. Cryst. Growth 2011, 328, 18–24. [Google Scholar] [CrossRef]

- Radamson, H.H.; Kolahdouz, M. Selective epitaxy growth of Si1−xGex layers for MOSFETs and FinFETs. J. Mater. Sci. Mater. Electron. 2015, 26, 4584–4603. [Google Scholar] [CrossRef]

- Sebaai, F.; Witters, L.; Holsteyns, F.; Wostyn, K.; Rip, J.; Yukifumi, Y.; Lieten, R.R.; Bilodeau, S.; Cooper, E. Wet Selective SiGe Etch to Enable Ge Nanowire Formation. Solid State Phenom. 2016, 255, 3–7. [Google Scholar] [CrossRef]

- Sioncke, S.; Brunco, D.P.; Meuris, M.; Uwamahoro, O.; Van Steenbergen, J.; Vrancken, E.; Heyns, M.M. Etch Rates of Ge, GaAs and InGaAs in Acids, Bases and Peroxide Based Mixtures. ECS Trans. 2008, 16, 451–460. [Google Scholar] [CrossRef]

- Hollaender, B.; Buca, D.; Mantl, S.; Hartmann, J.M. Wet Chemical Etching of Si, Si1−xGex, and Ge in HF:H2O2:CH3COOH. J. Electrochem. Soc. 2010, 157, H643–H646. [Google Scholar]

- Liu, W.D.; Lee, Y.-C.; Sekiguchi, R.; Yoshida, Y.; Komori, K.; Wostyn, K.; Sebaai, F.; Holsteyns, F. Selective Wet Etching in Fabricating SiGe and Ge Nanowires for Gate-all-Around MOSFETs. Solid State Phenom. 2018, 282, 101–106. [Google Scholar] [CrossRef]

- Peralagu, U.; Li, X.; Ignatova, O.; Fu, Y.; Millar, D.A.J.; Steer, M.J.; Povey, I.M.; Hossain, K.; Jain, M.; Golding, T.G.; et al. Towards a Vertical and Damage Free Post-Etch InGaAs Fin Profile: Dry Etch Processing, Sidewall Damage Assessment and Mitigation Options. ECS Trans. 2015, 69, 15–36. [Google Scholar] [CrossRef] [Green Version]

- Oehrlein, G.S.; Tromp, R.M.; Lee, Y.H.; Petrillo, E.J. Study of silicon contamination and near-surface damage caused by CF4/H2 reactive ion etching. Appl. Phys. Lett. 1984, 45, 420–422. [Google Scholar] [CrossRef]

- Petti, C.; McVittie, J.; Plummer, J. Characterization of Surface Mobility on the Sidewalls of Dry-Etched Trenches. In Technical Digest, Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 11–14 December 1988; IEEE: Piscataway, NJ, USA, 1988; pp. 104–107. [Google Scholar] [CrossRef]

- Radamson, H.H.; Zhu, H.; Wu, Z.; He, X.; Lin, H.; Liu, J.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. Nanomaterials 2020, 10, 1555. [Google Scholar] [CrossRef]

- Radamson, H.; Joelsson, K.; Ni, W.-X.; Birch, J.; Sundgren, J.-E.; Hultman, L.; Hansson, G. Strain characterization of Ge1−xSix and heavily B-doped Ge layers on Ge(001) by two-dimensional reciprocal space mapping. J. Cryst. Growth 1996, 167, 495–501. [Google Scholar] [CrossRef]

- Ni, W.-X.; Ekberg, J.; Joelsson, K.; Radamson, H.; Henry, A.; Shen, G.-D.; Hansson, G. A silicon molecular beam epitaxy system dedicated to device-oriented material research. J. Cryst. Growth 1995, 157, 285–294. [Google Scholar] [CrossRef]

- Bolkhovityanov, Y.B.; Deryabin, A.S.; Gutakovskii, A.K.; Sokolov, L.V.; Vasilenko, A.P. Dislocation interaction of layers in the Ge/Ge-seed/GexSi1−x/Si (001) (x~0.3–0.5) system: Trapping of misfit dislocations on the Ge-seed/GeSi interface. Acta Mater. 2013, 61, 5400–5405. [Google Scholar] [CrossRef]

- Chen, C.; Zhou, Z.; Chen, Y.; Li, C.; Lai, H.; Chen, S. Thermal stability of SiGe films on an ultra thin Ge buffer layer on Si grown at low temperature. Appl. Surf. Sci. 2010, 256, 6936–6940. [Google Scholar] [CrossRef]

- Kim, H.-W.; Shin, K.W.; Lee, G.-D.; Yoon, E. High quality Ge epitaxial layers on Si by ultrahigh vacuum chemical vapor deposition. Thin Solid Film. 2009, 517, 3990–3994. [Google Scholar] [CrossRef]

- Bogumilowicz, Y.; Hartmann, J.; Rochat, N.; Salaun, A.; Martin, M.; Bassani, F.; Baron, T.; David, S.; Bao, X.-Y.; Sanchez, E. Threading dislocations in GaAs epitaxial layers on various thickness Ge buffers on 300 mm Si substrates. J. Cryst. Growth 2016, 453, 180–187. [Google Scholar] [CrossRef]

- Wostyn, K.; Sebaai, F.; Rip, J.; Mertens, H.; Witters, L.; Loo, R.; Hikavyy, A.Y.; Milenin, A.; Thean, A.; Horiguchi, N.; et al. Selective Etch of Si and SiGe for Gate All-Around Device Architecture. ECS Transactions 2015, 69, 147–152. [Google Scholar] [CrossRef]

- Cretella, M.C.; Gatos, H.C. The Reaction of Germanium with Nitric Acid Solutions. J. Electrochem. Soc. 1958, 105, 487. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xie, L.; Zhu, H.; Zhang, Y.; Ai, X.; Wang, G.; Li, J.; Du, A.; Kong, Z.; Yin, X.; Li, C.; et al. Strained Si0.2Ge0.8/Ge multilayer Stacks Epitaxially Grown on a Low-/High-Temperature Ge Buffer Layer and Selective Wet-Etching of Germanium. Nanomaterials 2020, 10, 1715. https://doi.org/10.3390/nano10091715

Xie L, Zhu H, Zhang Y, Ai X, Wang G, Li J, Du A, Kong Z, Yin X, Li C, et al. Strained Si0.2Ge0.8/Ge multilayer Stacks Epitaxially Grown on a Low-/High-Temperature Ge Buffer Layer and Selective Wet-Etching of Germanium. Nanomaterials. 2020; 10(9):1715. https://doi.org/10.3390/nano10091715

Chicago/Turabian StyleXie, Lu, Huilong Zhu, Yongkui Zhang, Xuezheng Ai, Guilei Wang, Junjie Li, Anyan Du, Zhenzhen Kong, Xiaogen Yin, Chen Li, and et al. 2020. "Strained Si0.2Ge0.8/Ge multilayer Stacks Epitaxially Grown on a Low-/High-Temperature Ge Buffer Layer and Selective Wet-Etching of Germanium" Nanomaterials 10, no. 9: 1715. https://doi.org/10.3390/nano10091715