Assessment of Appropriate MMC Topology Considering DC Fault Handling Performance of Fault Protection Devices

Abstract

:1. Introduction

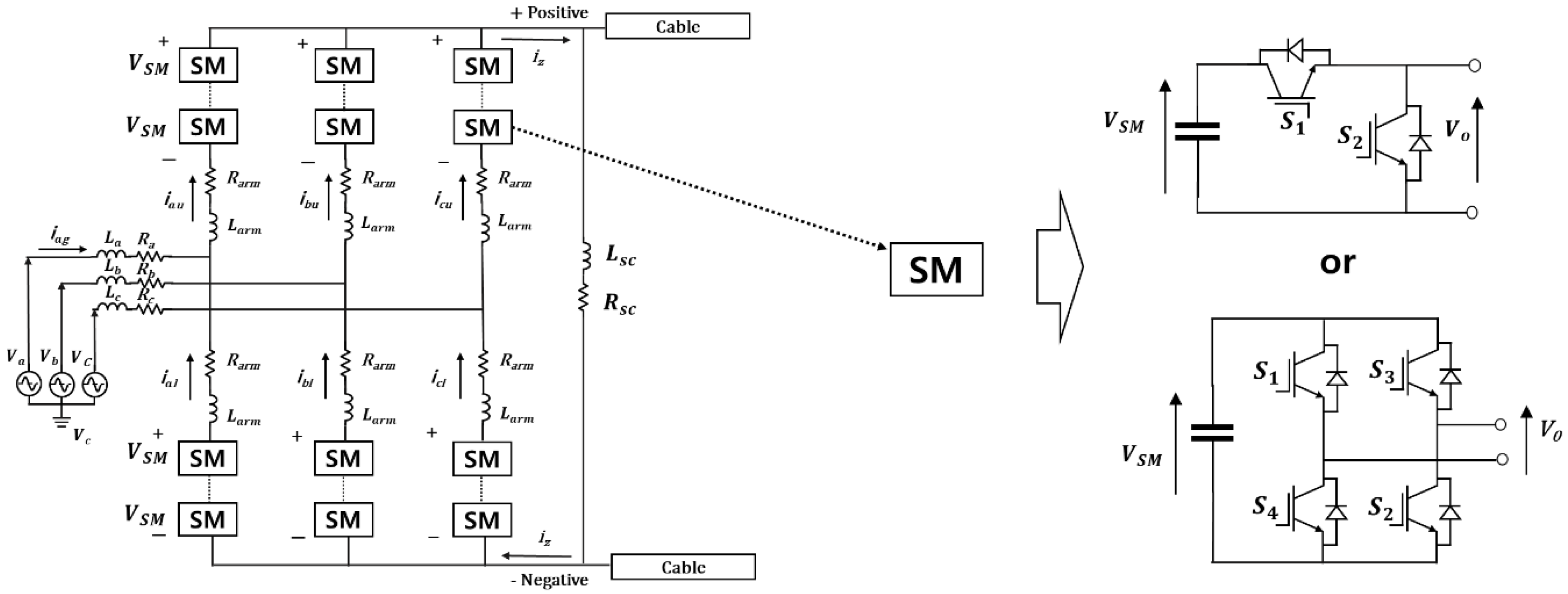

2. The Operation Characteristics of an MMC System

2.1. DC Fault Analysis of an MMC Before Blocking

2.2. DC Fault Analysis of an MMC after Blocking

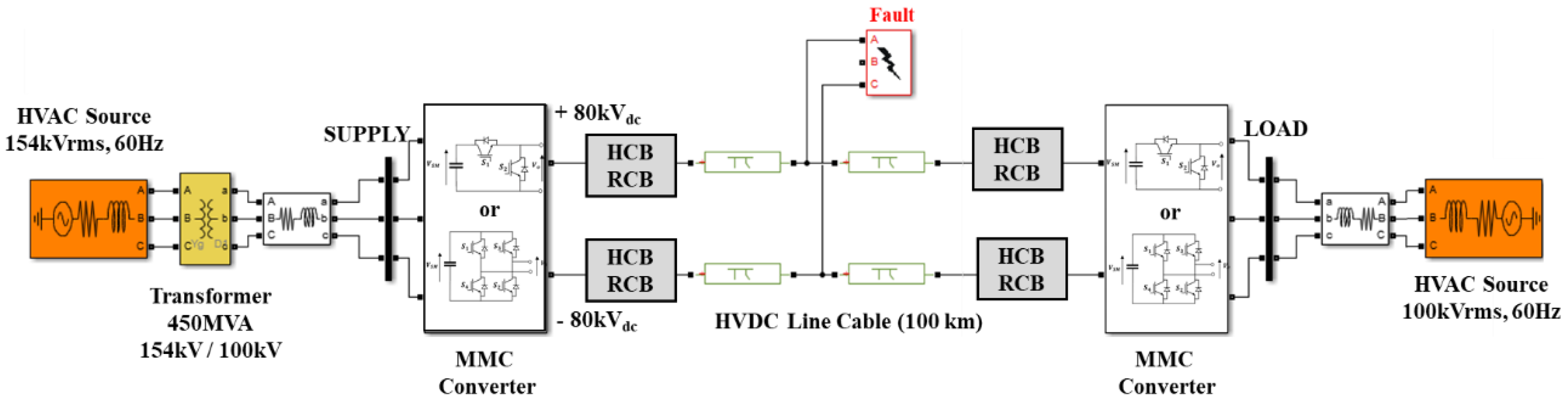

3. Simulation Model

3.1. Test Bed Model

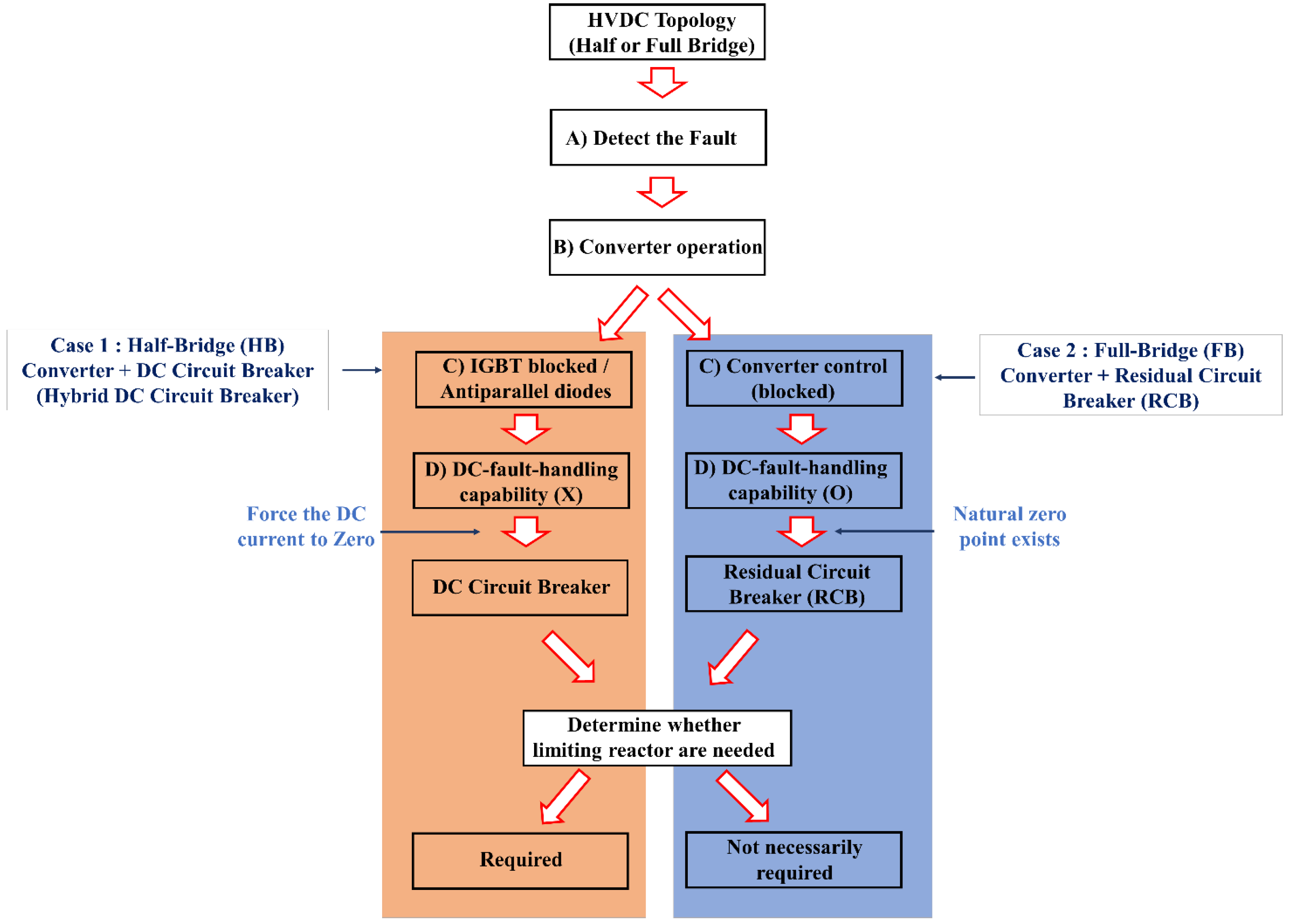

3.2. Comparison of System Operating Characteristics and Necessary Components by Case Types

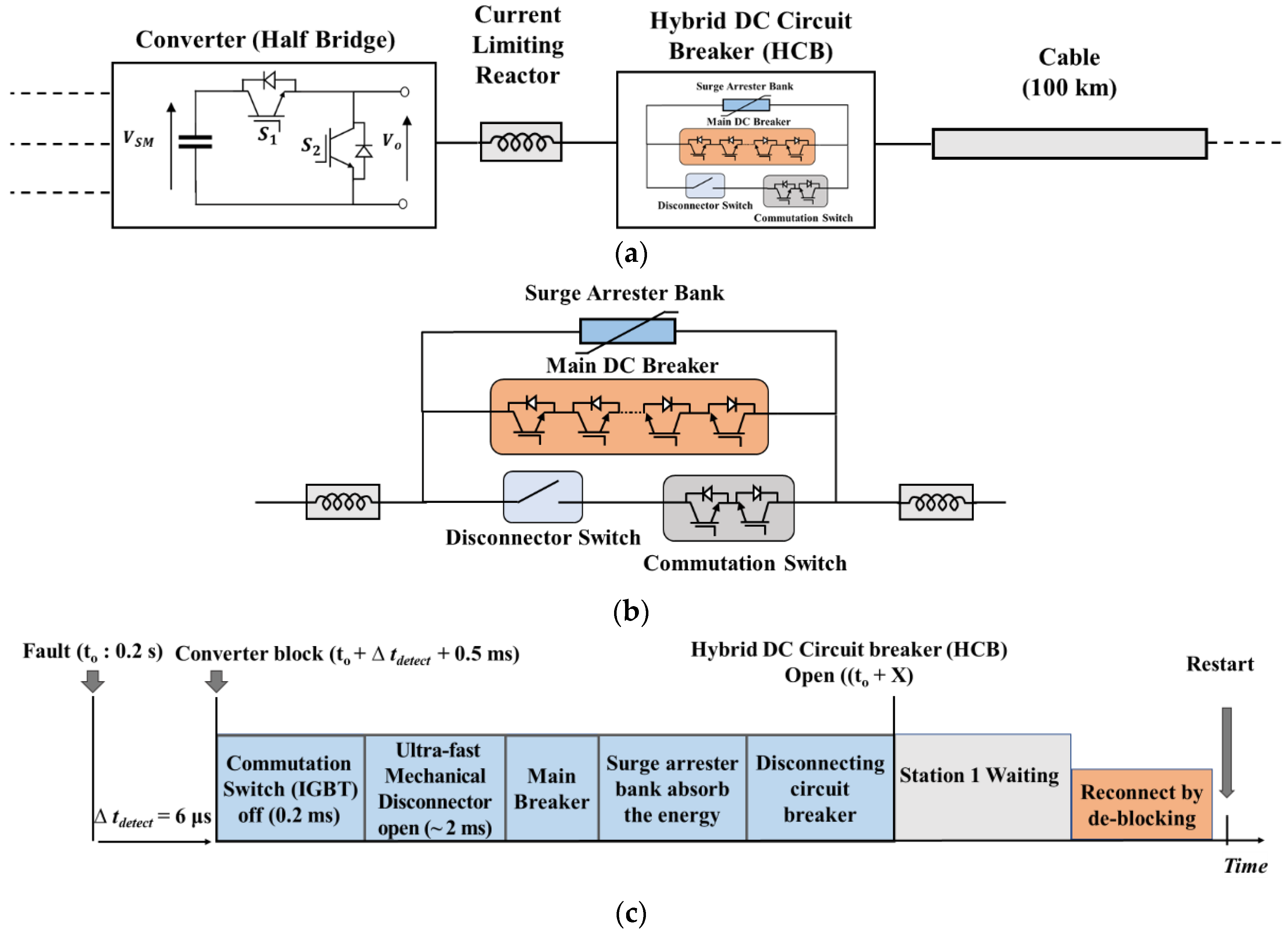

3.2.1. Case-1: Fault Management in an HB-MMC DC System Through DCCB

3.2.2. Case-2: Fault Management in an FB-MMC Using RCB

4. Interruption Performance of HB- vs FB-MMC DC Grids

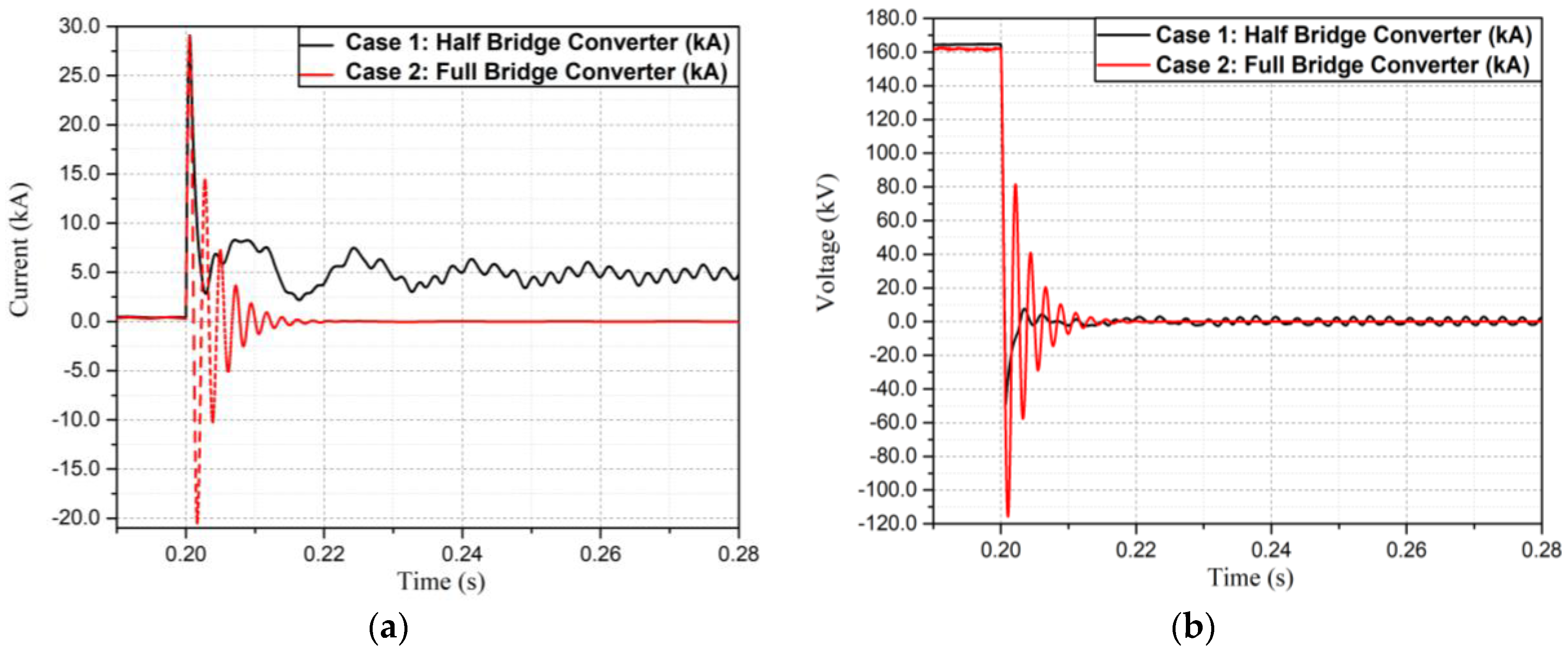

4.1. Comparison of Fault Current Blocking Performance (Pole-to-Pole Fault)

4.2. Comparison of Fault Current Blocking Performance (Pole-to-Ground Fault)

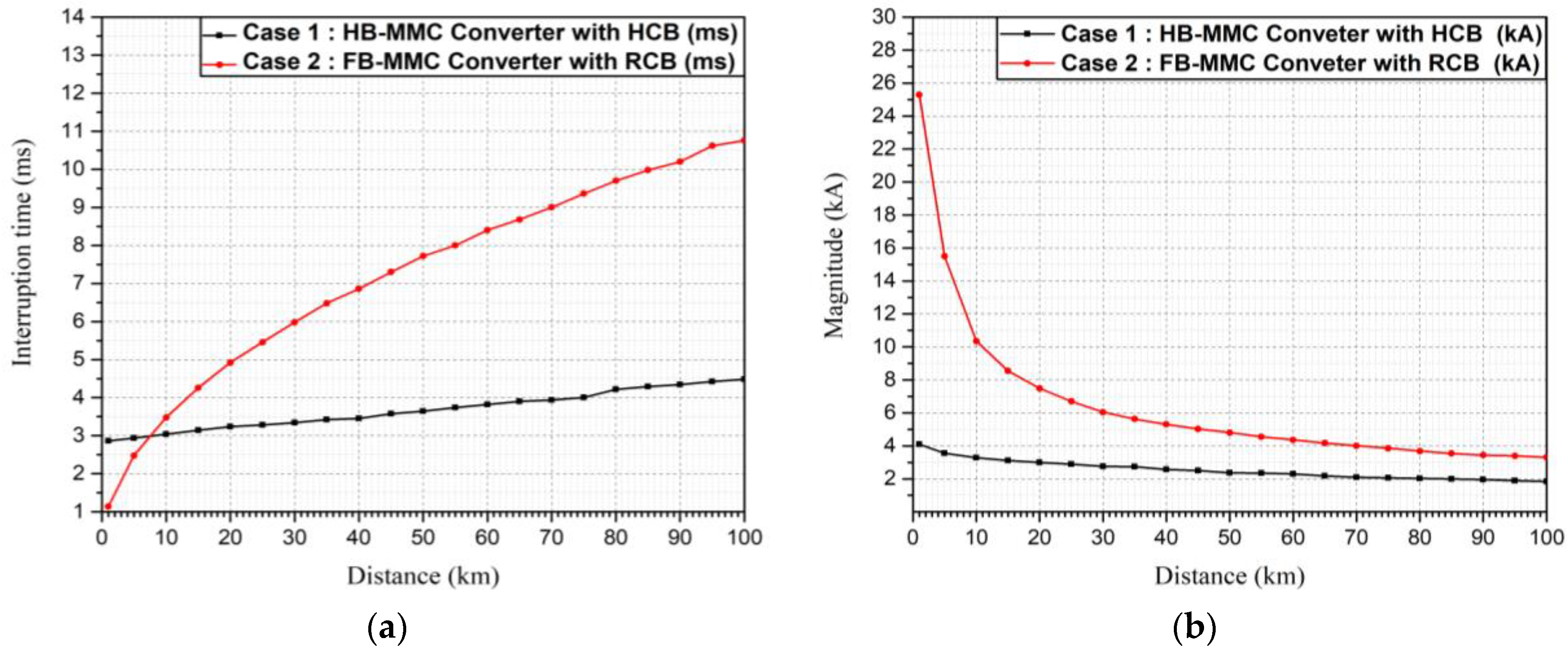

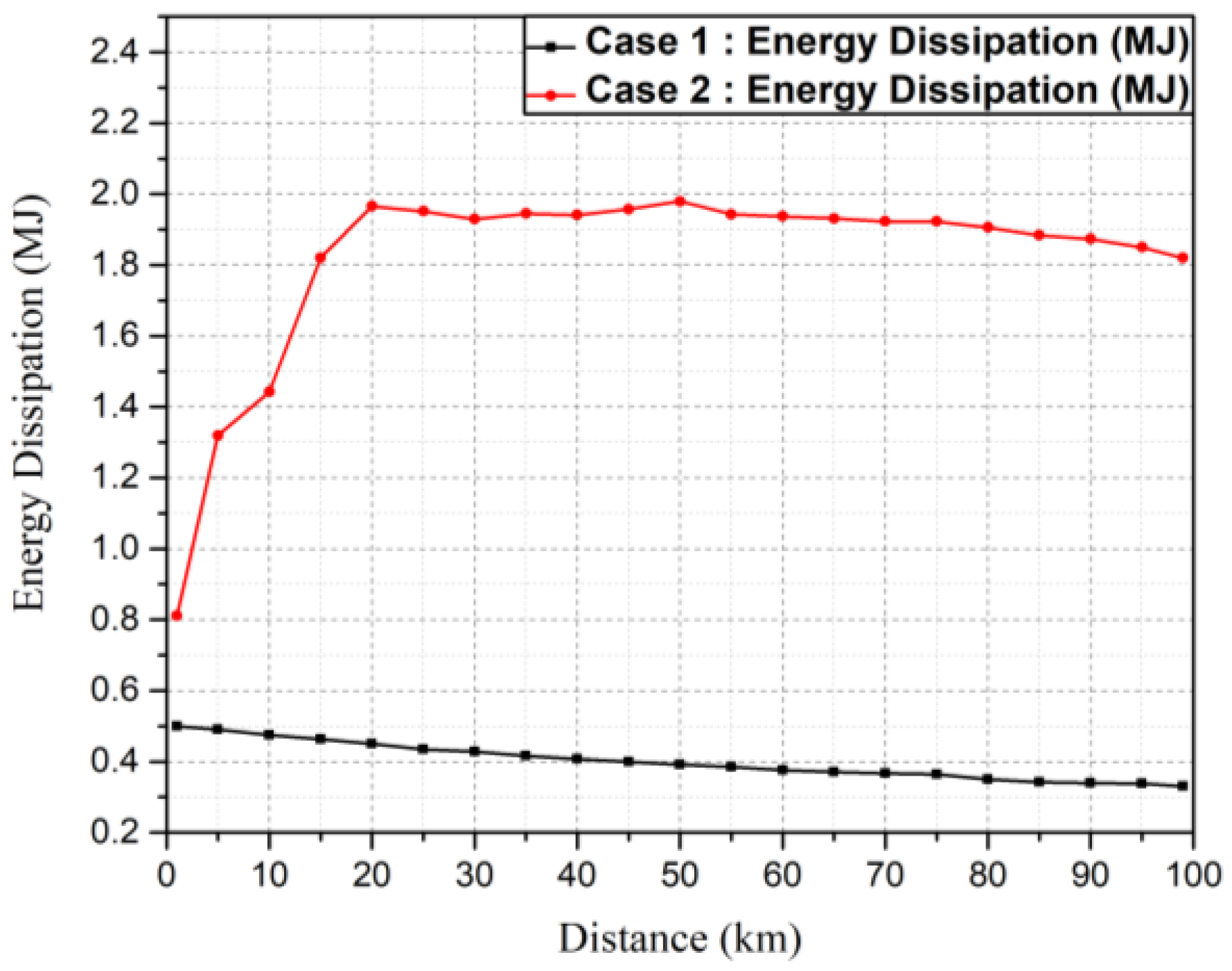

4.3. Comparison of Fault Interruption Performance

5. Transient Performance of the System in DC Faults

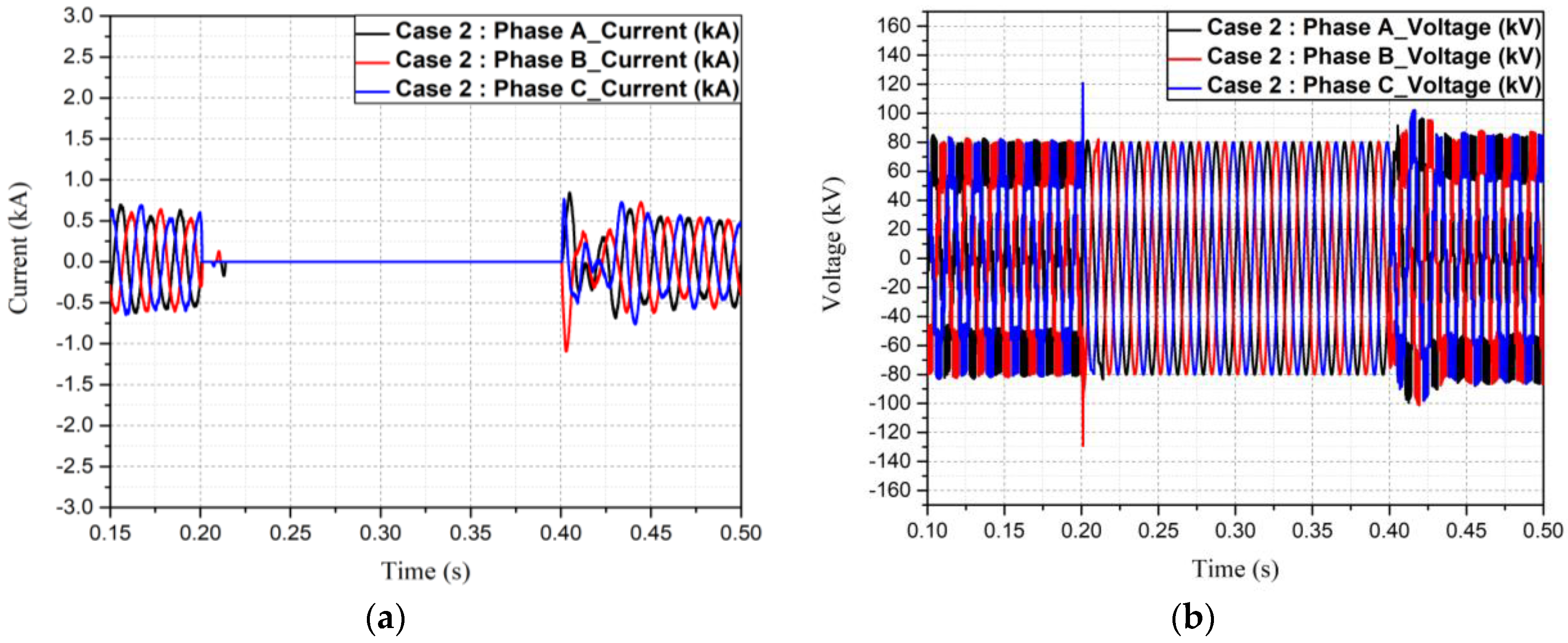

5.1. Analysis of the Current and Voltage Transient of the AC and DC Sides Considering a Reclosing Operation

5.1.1. Transient Current and Voltage of the AC System

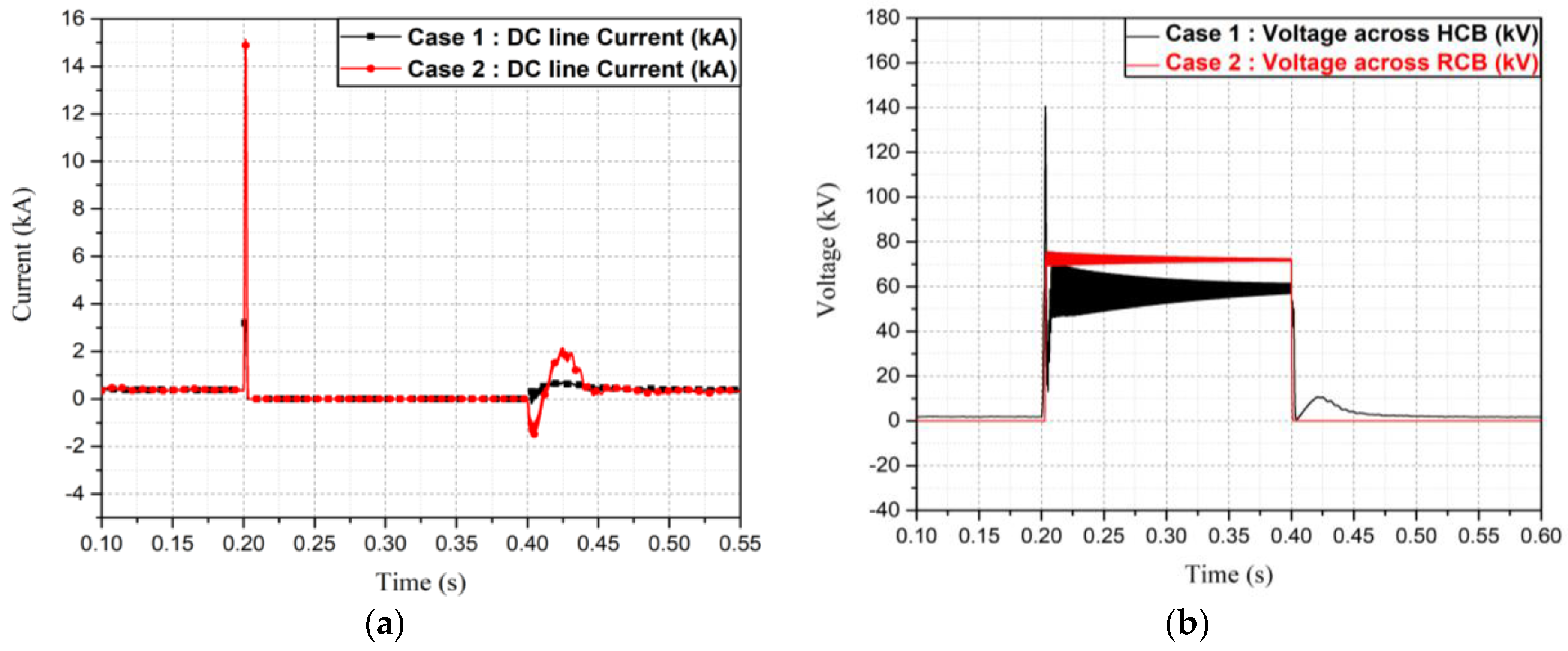

5.1.2. The Analysis of the DC Current and Voltage Waveform Across the HCB and RCB in the Transient State

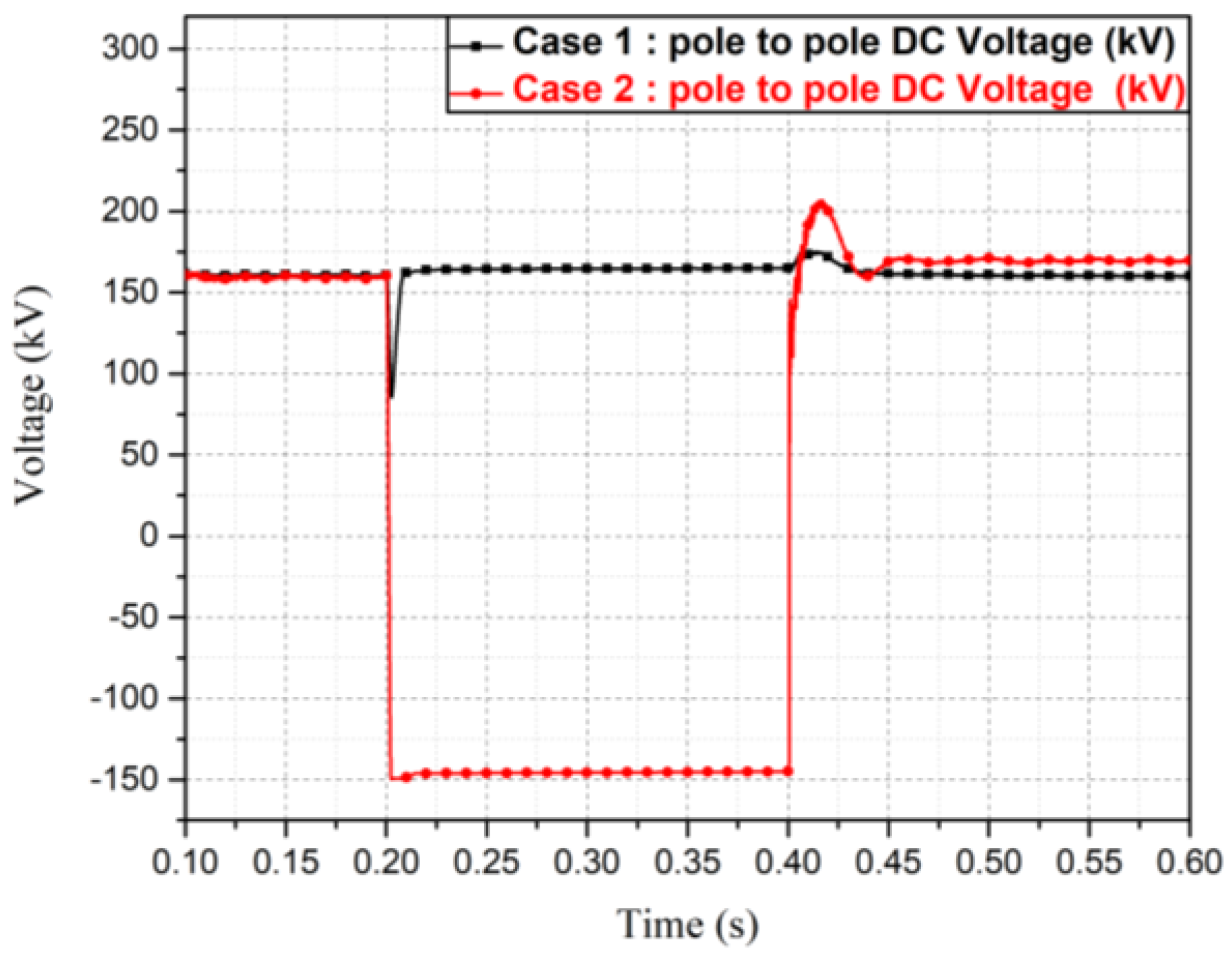

5.1.3. The Transient Overvoltage Analysis During DC Faults

5.2. The Preferable Case for HVDC Grid Application

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Shabestari, P.M.; Ziaeinejad, S.; Mehrizi-Sani, A. Reachability analysis for a grid-connected voltage-sourced converter (VSC). In Proceedings of the 2018 IEEE Applied Power Conference and Exposition (APEC), San Antonio, TX, USA, 4 March 2015; pp. 2349–2354. [Google Scholar]

- Yazdani, A.; Iravani, R. Voltage-Sourced Converters in Power Systems: Modeling, Control, and Applications; Wiley-IEEE Press: Hoboken, NJ, USA, 2010; pp. 115–125. ISBN 978-0-470-52156-4. [Google Scholar]

- Shewarega, F. Simplified modeling of VSC-HVDC in power system stability studies. IFAC Proc. Vol. 2014, 47, 9099–9104. [Google Scholar] [CrossRef]

- Frank, C.M. HVDC circuit breakers: A review identifying future research needs. IEEE Trans. Power Deliv. 2011, 26, 998–1007. [Google Scholar] [CrossRef]

- Mokhberdoran, A.; Carvalho, A. A review on HVDC circuit breakers. In Proceedings of the 3rd Renewable Power Generation Conference (RPG 2014), Naples, Italy, 24–25 September 2014. [Google Scholar]

- Rodriguez, J. Multilevel converters: An enabling technology for high-power applications. Proc. IEEE 2009, 97, 1791–1792. [Google Scholar] [CrossRef]

- He, Z.; Hu, J. Mechanical DC circuit breaker and FBSM-based mmc in a high-voltage MTDC networks: Coordinated operation for network riding through dc fault. In Proceedings of the Renewable Power Generation (RPG 2015), Beijing, China, 17–18 October 2015; pp. 1–6. [Google Scholar]

- Chen, X.; Zhao, C. Research on the fault characteristics of HVDC based on modular multilevel converter. In Proceedings of the 2011 IEEE Electrical Power and Energy Conference, Winnipeg, MB, Canada, 3–5 October 2011. [Google Scholar]

- Jonsson, T.; Lundberg, S. Converter Technologies and Functional Requirements for Reliable and Economical HVDC Grid Design. In Proceedings of the 2013 CIGRE Canada Conference, Calgary, AB, Canada, 9–11 September 2013. [Google Scholar]

- Najmi, V. Modelling, Control and Design Considerations for Modular Multilevel Converters. Master’s Thesis, Electrical Engineering Department, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, May 2015. [Google Scholar]

- Henry, S.; Denis, A.M. Feasibility study of off-shore HVDC grids. In Proceedings of the IEEE PES General Meeting, Providence, RI, USA, 25–29 July 2010. [Google Scholar]

- Bucher, M.K.; Walter, M.M. Options for ground fault clearance in HVDC offshore networks. In Proceedings of the 2012 Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012. [Google Scholar]

- Petino, C.; Heidemann, M. Application of multilevel full bridge converters in HVDC multiterminal systems. IET Power Electron. 2016, 9, 297–304. [Google Scholar] [CrossRef]

- Xu, Z.; Xiao, H. DC Fault Analysis of Clearance Solutions of MMC-HVDC systems. Energies 2018, 11, 941. [Google Scholar] [CrossRef]

- Zhang, Z. Short-Circuit Current Calculation and performance requirement of HVDC Breakers for MMC-MTDC Systems. IEEJ Trans. Electr. Electron. Eng. 2016, 11, 168–177. [Google Scholar] [CrossRef]

- Khan, U.A.; Lee, B.W. Feasibility analysis of a novel hybrid-type superconducting circuit breaker in multiterminal HVDC networks. Phys. C Supercond. Appl. 2015, 518, 154–158. [Google Scholar] [CrossRef]

- Think Grid. Available online: http://www.think-grid.org/fault-blocking-converters-dc-networks-1 (accessed on 20 July 2018).

- Win, J.; Saeedifard, M. Hybrid design of modular multilevel converters for HVDC systems based on various submodule circuits. IEEE Trans. Power Deliv. 2015, 30, 385–394. [Google Scholar]

- Nami, A.; Liang, J. Analysis of Modular Multilevel Converters with DC Short Circuit Fault Blocking Capability in Bipolar HVDC Transmission Systems. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8 September 2015; pp. 1–10. [Google Scholar]

- Fazel, S.S. Investigation and Comparison of Multi-Level Converters for Medium Voltage Applications. Ph.D. Thesis, Berlin University, Berlin, Germany, July 2015. [Google Scholar]

- Kontos, E.; Pinto, R.T. Impact of HVDC transmission system topology on multiterminal DC network faults. IEEE Trans. Power. Deliv. 2013, 30, 844–852. [Google Scholar] [CrossRef]

- Tahata, K. HVDC circuit breakers for HVDC grid applications. In Proceedings of the 11th IET International Conference on AC and DC Power Transmission, Birmingham, UK, 10–12 February 2015. [Google Scholar]

- Hafner, J.; Jacobson, B. Proactive hybrid HVDC breakers—A key innovation for reliable HVDC grids. In Proceedings of the CIGRE International Conference, Bologna, Italy, 13–15 September 2011. [Google Scholar]

| Parameters | Specifications |

|---|---|

| Voltage source converter (VSC) HVDC type | Bipolar HB-/FB-MMC |

| AC source voltage (rectifier side) | 154 kV |

| Number of submodules per arm | 40 |

| Equivalent capacitance | 10 uF |

| Current-limiting reactor | 20 mH |

| Transformer power rating | 450 MVA |

| Transformer voltage ratio | 154 kV/100 kV |

| DC cable resistance | 0.0133 Ω/km |

| DC cable inductance | 0.8273 mH/km |

| DC cable capacitance | 0.0139 uF/km |

| Length of transmission line | 100 km |

| Parameter | Simulation Condition | Case-1 | Case-2 |

|---|---|---|---|

| Structure | - | HB-MMC + HCB | FB-MMC + RCB |

| DC-fault-handling capability | O | O | |

| Current-limiting reactor | Required | Not necessarily required | |

| Total interruption time (ms) | Variable fault location | 3~4.5 (ms) | ~11 (ms) |

| Maximum DC fault current in fault period (kA) | 2~4 (kA) | 3~25 (kA) | |

| Energy dissipation across circuit breaker (MJ) | 0.32~0.51 (MJ) | 0.01~0.05 (MJ) | |

| Maximum AC current in fault period (kA) | 5 km from the sending end converter side | 2 (kA) | 0.15 (kA) |

| Maximum AC current in reclosing period (kA) | 0.62 (kA) | 1.02 (kA) | |

| Maximum DC current in reclosing period (kA) | 5 km from the sending end converter side (pole-to-pole) | 0.8 (kA) | 2 (kA) |

| Maximum DC system overvoltage (kV) | 175 (kV) | 205 (kV) | |

| Time to recovery (ms) | ~0.1 (s) | 10 (s) | |

| Maximum DC overvoltage in reclosing period (kV) | 5 km from the sending end converter side (pole-to-ground) | 91 (kV) | 152 (kV) |

| Stress on insulation | - | Relatively low | Relatively high |

| Feasibility in HVDC grid application | - | ★★★★★ | ★★☆☆☆ |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, H.-Y.; Asif, M.; Park, K.-H.; Lee, B.-W. Assessment of Appropriate MMC Topology Considering DC Fault Handling Performance of Fault Protection Devices. Appl. Sci. 2018, 8, 1834. https://doi.org/10.3390/app8101834

Lee H-Y, Asif M, Park K-H, Lee B-W. Assessment of Appropriate MMC Topology Considering DC Fault Handling Performance of Fault Protection Devices. Applied Sciences. 2018; 8(10):1834. https://doi.org/10.3390/app8101834

Chicago/Turabian StyleLee, Ho-Yun, Mansoor Asif, Kyu-Hoon Park, and Bang-Wook Lee. 2018. "Assessment of Appropriate MMC Topology Considering DC Fault Handling Performance of Fault Protection Devices" Applied Sciences 8, no. 10: 1834. https://doi.org/10.3390/app8101834

APA StyleLee, H.-Y., Asif, M., Park, K.-H., & Lee, B.-W. (2018). Assessment of Appropriate MMC Topology Considering DC Fault Handling Performance of Fault Protection Devices. Applied Sciences, 8(10), 1834. https://doi.org/10.3390/app8101834