Bias Stress and Temperature Impact on InGaZnO TFTs and Circuits

Abstract

:1. Introduction

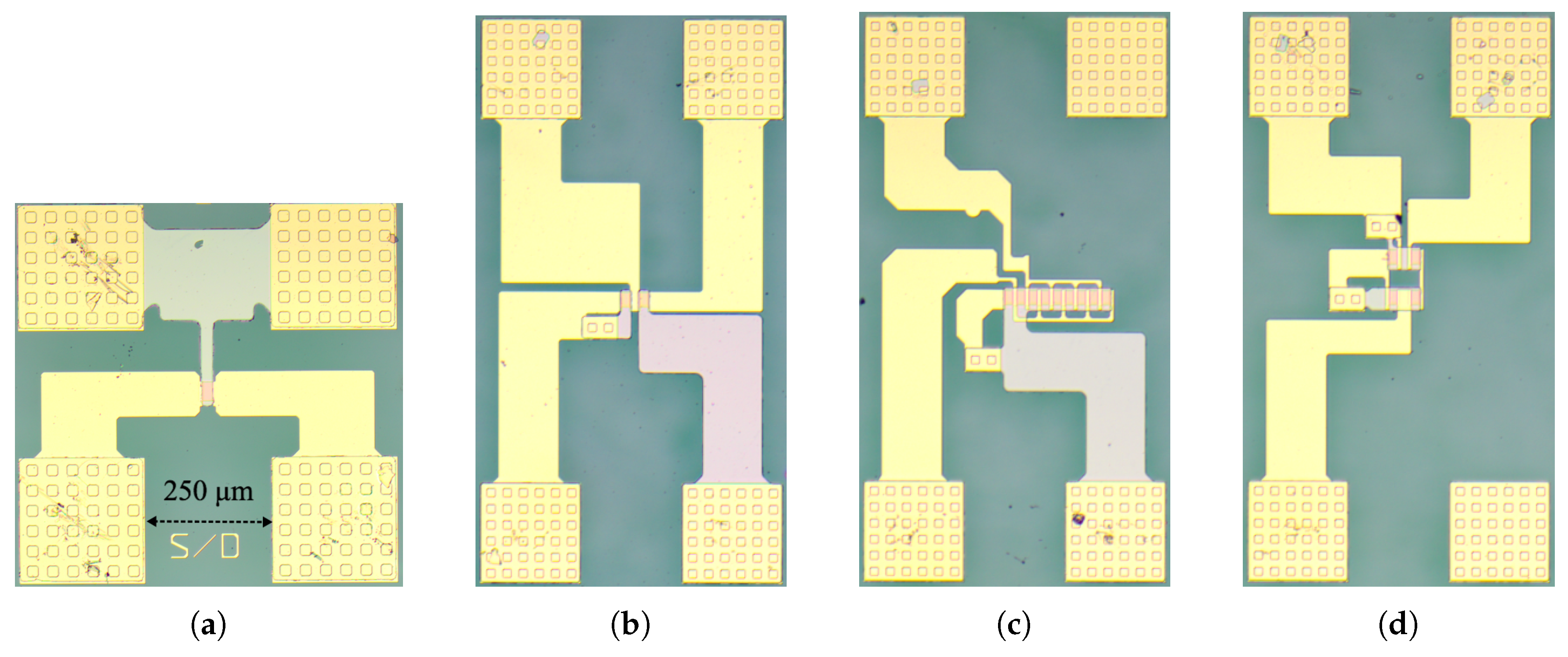

2. Transistor and Circuit Fabrication and Characterization

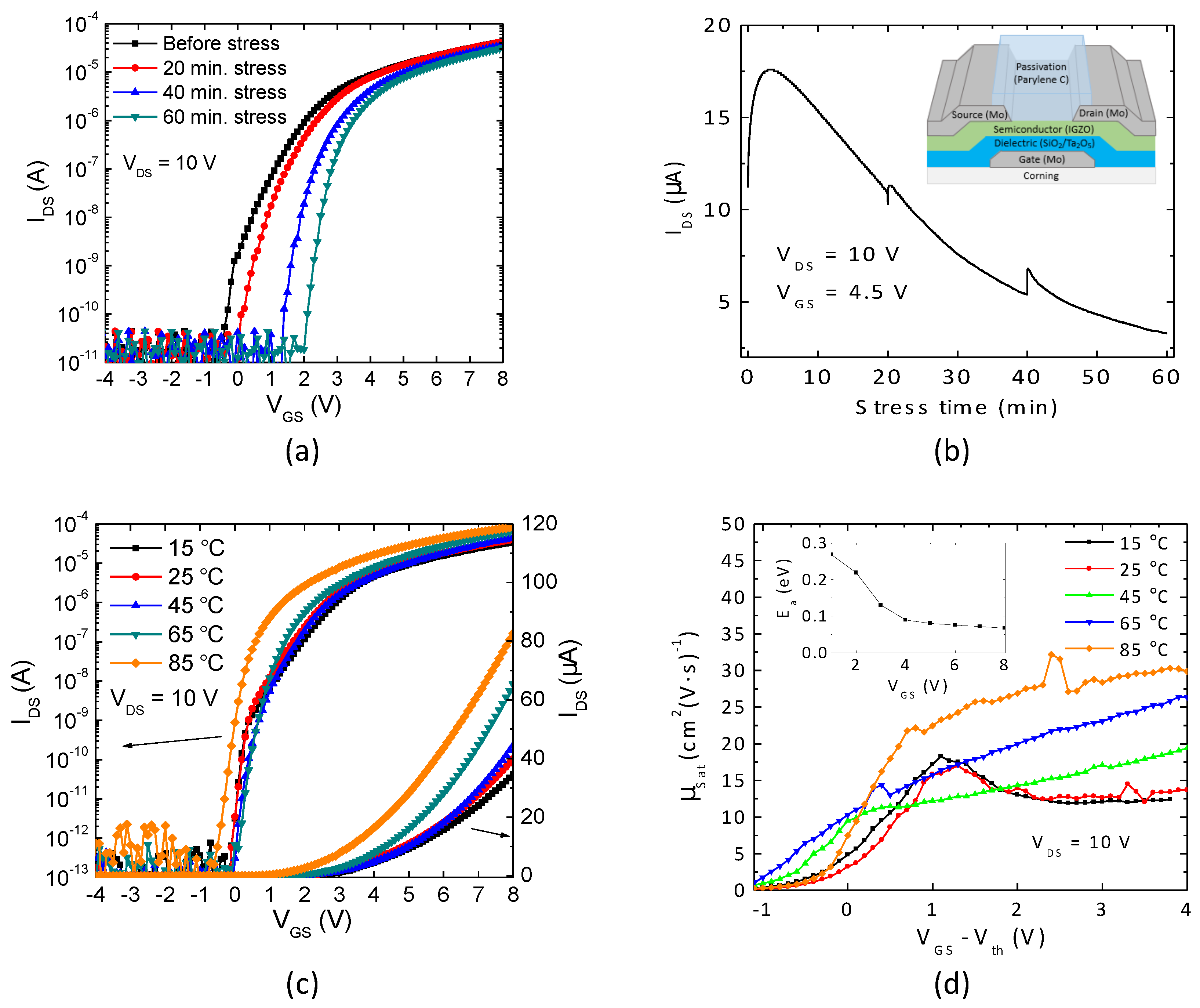

3. Isolated TFT Behavior

3.1. Stress-Dependent Behavior

3.2. Temperature-Dependent Behavior

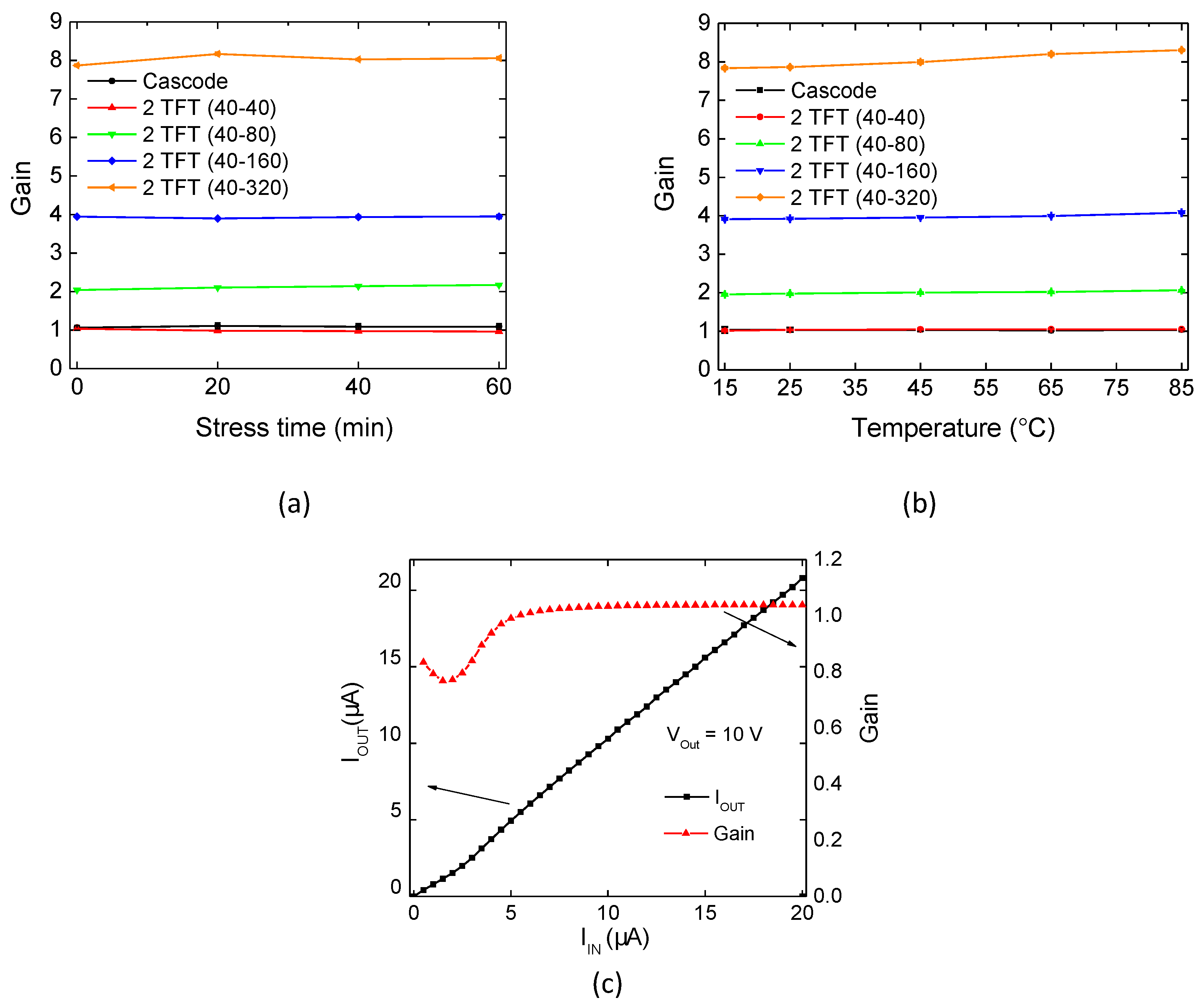

4. Robust Circuits against Bias Stress and Temperature: Theoretical Analysis

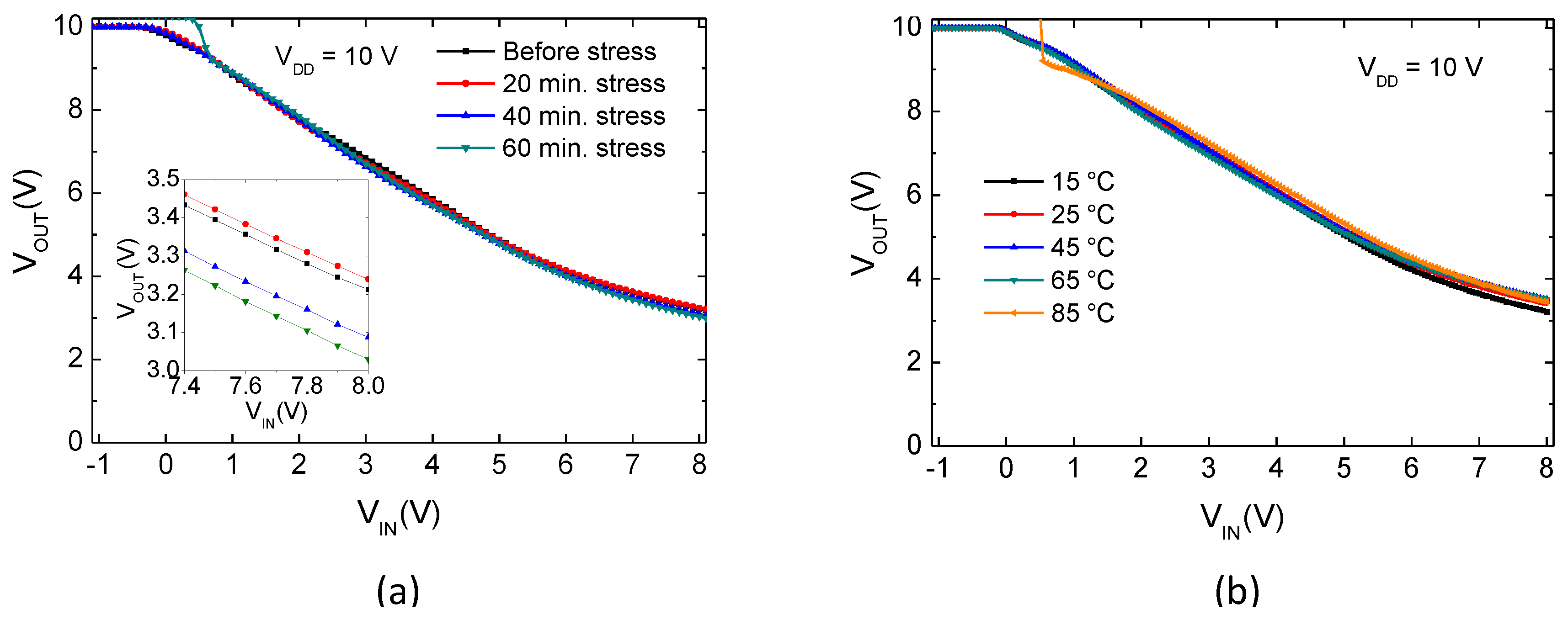

5. Circuits Measurements and Discussion

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations

| a-IGZO | amorphous Indium Gallium Zinc Oxide |

| TFT | Thin-film Transistor |

| NFC | Near-field communication |

| a-Si:H | Hydrogenated amorphous silicon |

| RF | Radio Frequency |

| RT | Room Temperature |

| LAE | Large area electronics |

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Bahubalindruni, P.G.; Tavares, V.G.; Borme, J.; de Oliveira, P.G.; Martins, R.; Fortunato, E.; Barquinha, P. InGaZnO Thin-Film-Transistor-Based Four-Quadrant High-Gain Analog Multiplier on Glass. Electron Device Lett. 2016, 37, 419–421. [Google Scholar] [CrossRef]

- Ishida, K.; Shabanpour, R.; Boroujeni, B.; Meister, T.; Carta, C.; Ellinger, F.; Petti, L.; Munzenrieder, N.; Salvatore, G.; Troster, G. 22.5 dB open-loop gain, 31 kHz GBW pseudo-CMOS based operational amplifier with a-IGZO TFTs on a flexible film. In Proceedings of the Asian Solid-State Circuits Conference (A-SSCC), Kaohsiung, Taiwan, 10–12 November 2014; pp. 313–316. [Google Scholar]

- Raiteri, D.; Torricelli, F.; Myny, K.; Nag, M.; van der Putten, B.; Smits, E.; Steudel, S.; Tempelaars, K.; Tripathi, A.; Gelinck, G.; et al. A 6 b 10 MS/s current-steering DAC manufactured with amorphous Gallium-Indium-Zinc-Oxide TFTs achieving SFDR >30 dB up to 300 kHz. In Proceedings of the International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2012; pp. 314–316. [Google Scholar]

- Bahubalindruni, P.G.; Tavares, V.G.; Fortunato, E.; Martins, R.; Barquinha, P. Novel linear analog-adder using a-IGZO TFTs. In Proceedings of the International Symposium on Circuits and Systems (ISCAS), Montréal, QC, Canada, 22–25 May 2016; pp. 2098–2101. [Google Scholar]

- Myny, K.; Steudel, S. 16.6 Flexible thin-film NFC transponder chip exhibiting data rates compatible to ISO NFC standards using self-aligned metal-oxide TFTs. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016. [Google Scholar]

- Rogers, J.A.; Ghaffari, R.; Kim, D.H. Stretchable Bioelectronics for Medical Devices and Systems; Springer: Berlin, Germany, 2016. [Google Scholar]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Lopes, M.; Gomes, H.L.; Medeiros, M.; Barquinha, P.; Pereira, L.; Fortunato, E.; Martins, R.; Ferreira, I. Gate-bias stress in amorphous oxide semiconductors thin-film transistors. Appl. Phys. Lett. 2009, 95, 063502. [Google Scholar] [CrossRef]

- Suresh, A.; Muth, J. Bias stress stability of indium gallium zinc oxide channel based transparent thin film transistors. Appl. Phys. Lett. 2008, 92, 033502. [Google Scholar] [CrossRef]

- Hiromichi, G.; Daisuke, K.; Shuhei, Y.; Toshinari, S.; Shunichi, I.; Hiroki, O.; Akiharu, M.; Shunpei, Y. Numerical Analysis on Temperature Dependence of Characteristics of Amorphous In-Ga-Zn-Oxide TFT. SID Symp. Dig. Tech. Pap. 2009, 40, 1110–1112. [Google Scholar]

- Hossain Chowdhury, M.D.; Migliorato, P.; Jang, J. Low temperature characteristics in amorphous indium-gallium-zinc-oxide thin-film transistors down to 10 K. Appl. Phys. Lett. 2013, 103, 152103. [Google Scholar] [CrossRef]

- Sambandan, S. High-gain amplifiers with amorphous-silicon thin-film transistors. Electron Device Lett. 2008, 29, 882–884. [Google Scholar] [CrossRef]

- Kiazadeh, A.; Gomes, H.L.; Barquinha, P.; Martins, J.; Rovisco, A.; Pinto, J.V.; Martins, R.; Fortunato, E. Improving positive and negative bias illumination stress stability in parylene passivated IGZO transistors. Appl. Phys. Lett. 2016, 109, 051606. [Google Scholar] [CrossRef]

- Olziersky, A.; Barquinha, P.; Vilà, A.; Pereira, L.; Gonçalves, G.; Fortunato, E.; Martins, R.; Morante, J.R. Insight on the SU-8 resist as passivation layer for transparent Ga2O3-In2O3-ZnO thin-film transistors. J. Appl. Phys. 2010, 108, 064505. [Google Scholar] [CrossRef]

- Carlos, E.; Branquinho, R.; Kiazadeh, A.; Barquinha, P.; Martins, R.; Fortunato, E. UV-Mediated Photochemical Treatment for Low-Temperature Oxide-Based Thin-Film Transistors. ACS Appl. Mater. Interfaces 2016, 8, 31100–31108. [Google Scholar]

- Xu, W.; Dai, M.; Liang, L.; Liu, Z.; Sun, X.; Wan, Q.; Cao, H. Anomalous bias-stress-induced unstable phenomena of InZnO thin-film transistors using Ta2O5 gate dielectric. J. Phys. D Appl. Phys. 2012, 45, 205103. [Google Scholar] [CrossRef]

- Jin, J.W.; Nathan, A.; Barquinha, P.; Pereira, L.; Fortunato, E.; Martins, R.; Cobb, B. Interpreting anomalies observed in oxide semiconductor TFTs under negative and positive bias stress. AIP Adv. 2016, 6, 085321. [Google Scholar] [CrossRef]

- Chen, C.; Abe, K.; Kumomi, H.; Kanicki, J. Density of states of a-InGaZnO from temperature-dependent field-effect studies. IEEE Trans. Electron Devices 2009, 56, 1177–1183. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In-Ga-Zn-O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef] [PubMed]

- Kamiya, T.; Nomura, K.; Hosono, H. Electronic structures above mobility edges in crystalline and amorphous In-Ga-Zn-O: Percolation conduction examined by analytical model. J. Disp. Technol. 2009, 5, 462–467. [Google Scholar] [CrossRef]

- Yang, S.; Shin, J.H.; Park, S.H.K.; Cheong, W.S.; Hwang, C.S.; Yoon, S.M.; Cho, D.H.; Ryu, M.K.; Chu, H.Y.; Cho, K.I.; et al. P-12: Stability of Nano-Crystalline ZnO and Amorphous IGZO TFTs under Bias Stress. SID Symp. Dig. Tech. Pap. 2009, 40, 1121–1123. [Google Scholar] [CrossRef]

- Park, S.; Cho, E.N.; Yun, I. Threshold voltage shift prediction for gate bias stress on amorphous InGaZnO thin film transistors. Microelectron. Reliab. 2012, 52, 2215–2219. [Google Scholar] [CrossRef]

- Bahubalindruni, P.G.; Tavares, V.G.; Barquinha, P.; Duarte, C.; de Oliveira, P.G.; Martins, R.; Fortunato, E. Transparent current mirrors with a-GIZO TFTs: Neural modeling, simulation and fabrication. J. Disp. Technol. 2013, 9, 1001–1006. [Google Scholar] [CrossRef]

| Stress (Min.) | Temperature (°C) | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 20 | 40 | 60 | 15 | 25 | 45 | 65 | 85 | |

| (A) | 11.3 | 10.7 | 6.8 | 5.0 | 6.8 | 8.1 | 7.1 | 11.5 | 21.9 |

| Relative variation (%) | 0.0 | −5.2 | −39.5 | −56.0 | −15.5 | 0.0 | −12.2 | 43.3 | 172.3 |

| Stress (Min.) | Temperature (°C) | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 20 | 40 | 60 | 15 | 25 | 45 | 65 | 85 | |

| Gain | 0.99 | 0.95 | 0.94 | 0.92 | 0.98 | 0.98 | 0.97 | 0.94 | 0.97 |

| Relative variation (%) | 0.0 | −4.0 | −4.9 | −7.3 | 0.1 | 0.0 | −1.2 | −4.3 | −1.3 |

| Gain | Stress (Min.) | Temperature (°C) | |||||||

|---|---|---|---|---|---|---|---|---|---|

| 0 | 20 | 40 | 60 | 15 | 25 | 65 | 45 | 85 | |

| Cascode | 1.06 | 1.11 | 1.09 | 1.09 | 1.04 | 1.04 | 1.04 | 1.02 | 1.04 |

| Relative variation (%) | 0.0 | 4.7 | 2.8 | 2.8 | −0.2 | 0.0 | 0.0 | −1.7 | 0.0 |

| 40–40 | 1.03 | 0.96 | 0.95 | 0.94 | 1.02 | 1.04 | 1.05 | 1.05 | 1.05 |

| Relative variation (%) | 0.0 | −6.6 | −7.9 | −8.7 | −1.9 | 0.0 | 1.0 | 1.0 | 1.0 |

| 40–80 | 2.03 | 2.12 | 2.15 | 2.19 | 1.96 | 1.98 | 2.01 | 2.02 | 2.07 |

| Relative variation (%) | 0.0 | 4.1 | 6.0 | 7.6 | −1.1 | 0.0 | 1.3 | 2.1 | 4.2 |

| 40–160 | 3.95 | 3.85 | 3.86 | 3.86 | 3.91 | 3.92 | 3.95 | 3.99 | 4.08 |

| Relative variation (%) | 0.0 | −2.5 | −2.4 | −2.4 | −0.2 | 0.0 | 0.8 | 1.8 | 4.0 |

| 40–320 | 7.90 | 8.15 | 7.85 | 7.88 | 7.84 | 7.86 | 7.99 | 8.20 | 8.30 |

| Relative variation (%) | 0.0 | 3.2 | −0.6 | −0.2 | −0.4 | 0.0 | 1.7 | 4.3 | 5.6 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Martins, J.; Bahubalindruni, P.; Rovisco, A.; Kiazadeh, A.; Martins, R.; Fortunato, E.; Barquinha, P. Bias Stress and Temperature Impact on InGaZnO TFTs and Circuits. Materials 2017, 10, 680. https://doi.org/10.3390/ma10060680

Martins J, Bahubalindruni P, Rovisco A, Kiazadeh A, Martins R, Fortunato E, Barquinha P. Bias Stress and Temperature Impact on InGaZnO TFTs and Circuits. Materials. 2017; 10(6):680. https://doi.org/10.3390/ma10060680

Chicago/Turabian StyleMartins, Jorge, Pydi Bahubalindruni, Ana Rovisco, Asal Kiazadeh, Rodrigo Martins, Elvira Fortunato, and Pedro Barquinha. 2017. "Bias Stress and Temperature Impact on InGaZnO TFTs and Circuits" Materials 10, no. 6: 680. https://doi.org/10.3390/ma10060680

APA StyleMartins, J., Bahubalindruni, P., Rovisco, A., Kiazadeh, A., Martins, R., Fortunato, E., & Barquinha, P. (2017). Bias Stress and Temperature Impact on InGaZnO TFTs and Circuits. Materials, 10(6), 680. https://doi.org/10.3390/ma10060680