1. Introduction

Series-connected batteries or electric double-layer capacitors (EDLCs) are widely used in handheld and portable consumer products, electric vehicles, as well as renewable energy applications such as photovoltaic and wind power generation systems. As a unit, the series string is charged and discharges together. Because of non-uniform individual cell properties, united operation causes the small imbalance in the form of unequal voltages among series cells during charging and discharging periods. Overcharge and deep discharge both will cause the battery cell to be deteriorated forever or even worse [

1,

2]. The poor performance of single cell will limit the normal operation of the whole series string [

3] The voltage balancing device, also known as voltage equalizer, is therefore indispensable equipment in battery management systems (BMS) [

4].

From the viewpoint of the attributes of components used for voltage equalization, voltage equalizers could be grouped into three types. The first ones are known as “resistor bleeding balancing” [

5]. This method uses resistors which are connected in parallel with each cell though switches to reduce the excess voltage. The excess energy from the higher voltage cells is consumed by resistors in the form of heat and this method is also called an energy-consuming voltage equalizer.

In order to avoid the waste of energy during the voltage balancing process, another type of voltage equalizer is developed by employing DC-DC converters to charge the lower voltage battery cells or discharge the higher ones. As a result, various switch-mode converters are introduced and been reconfigured to be voltage equalizers for battery or EDLC strings [

6,

7]. A common characteristic of this type of voltage equalization system is that bulky magnetic components are used as the energy transfer device. The closed loop controller with voltage sensors is therefore usually required to avoid the risk of magnetic saturation in inductors and the uniform leakage inductances are required for multi-winding transformers. Additionally, it is of interest that a large number of diodes is found in the voltage balancing systems as suggested in [

8]. In low voltage applications, the inherent voltage drop of diodes may cause a large amount of power losses and make the efficiency difficult to improve.

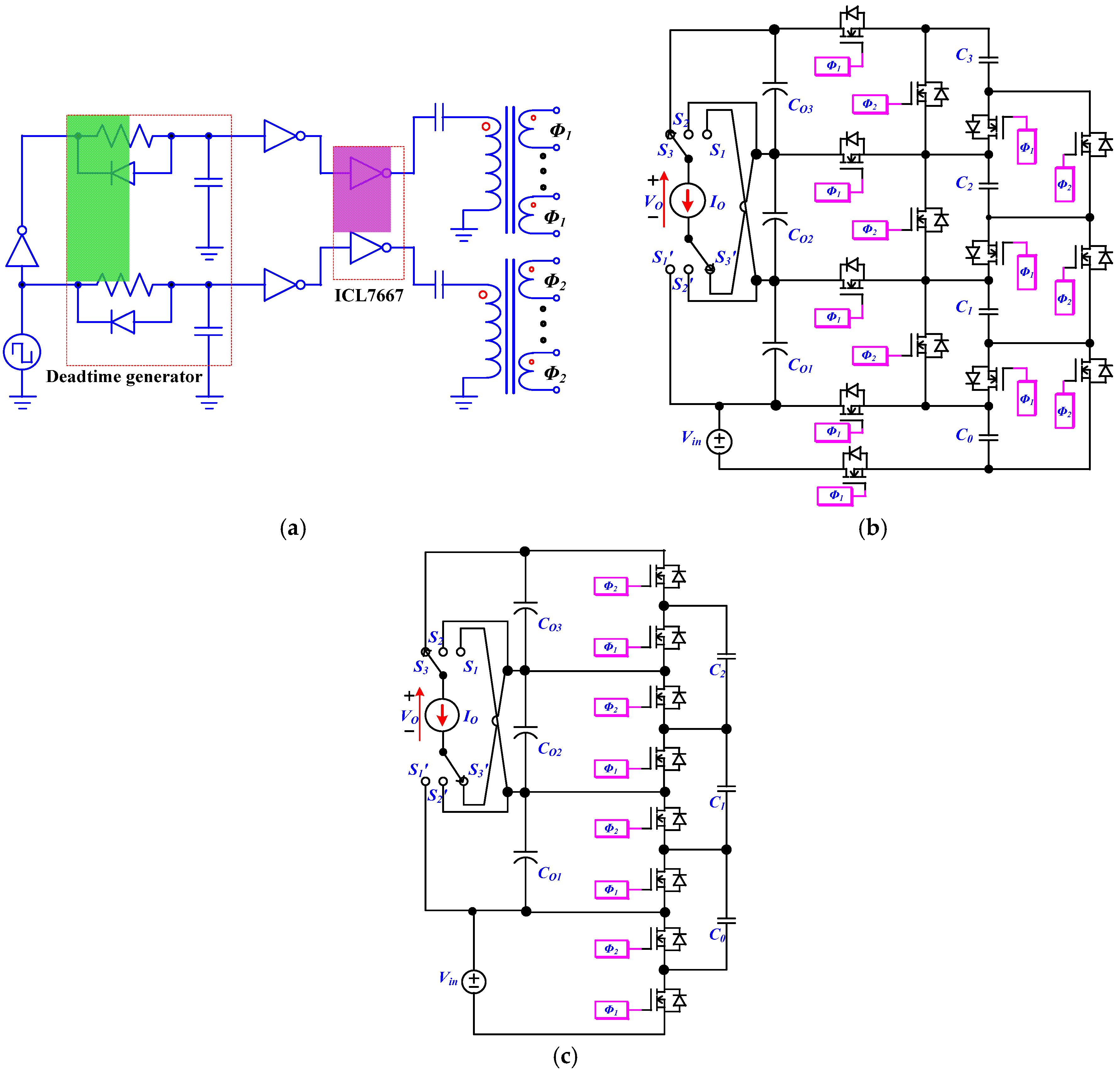

Switched-capacitor (SC) voltage equalizers, as the third voltage balancing technology, are developed by using SC converters to directly transfer charge from the higher voltage battery/EDLC cells to the lower ones. The main advantages of this technique are that the bulky magnetic components are no longer needed and just a pair of complementary pulse signals with fixed duty ratio 0.5 is required to control all switches [

9,

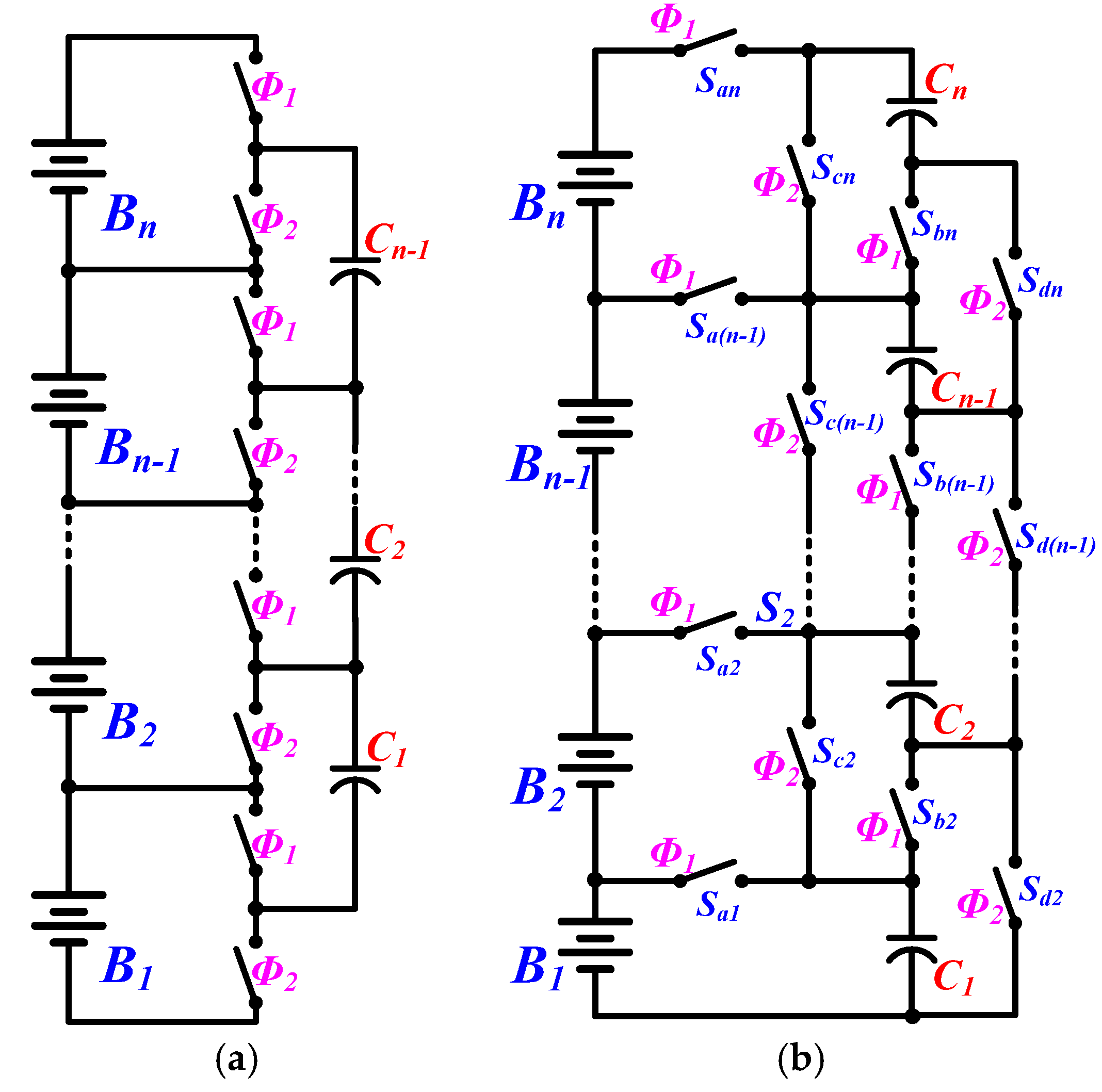

10]. It means SC voltage equalizer can be designed with smaller size and lower cost. The conventional structure of SC voltage equalizers is shown in

Figure 1a [

11]. Its resonant versions are also developed in [

12] for high efficiency applications. In this structure, the charge flows just in two adjacent battery cells. The balancing speed is therefore limited, which makes this structure difficult to apply in those series strings with larger numbers of cells. The double-tiered version of this structure is presented in [

13] to improve this balancing speed. However, this novel method does not fundamentally solve the problem that charge cannot be transferred from the highest voltage cell to the lowest one directly.

In this paper, a novel design concept of SC voltage equalization system is presented to overcome the problem existed in the conventional structure (see

Figure 1a). The structure of the proposed system is shown in

Figure 1b, which is also developed based on the two-phase SC technique. All switches are therefore controlled by just a pair of complementary pulse signals with fixed frequency and duty ratio. These features are very similar to the previous work presented in [

14] but with different topology and circuit configuration. The main advantage of the proposed SC voltage equalizer compared to the conventional one is that charge can be transferred from any one battery cell with higher voltage to any one lower voltage cell directly. It means the voltage balancing speed could be significantly higher than the conventional one and makes the SC voltage balancing technique usable for those battery strings with a larger number of series cells.

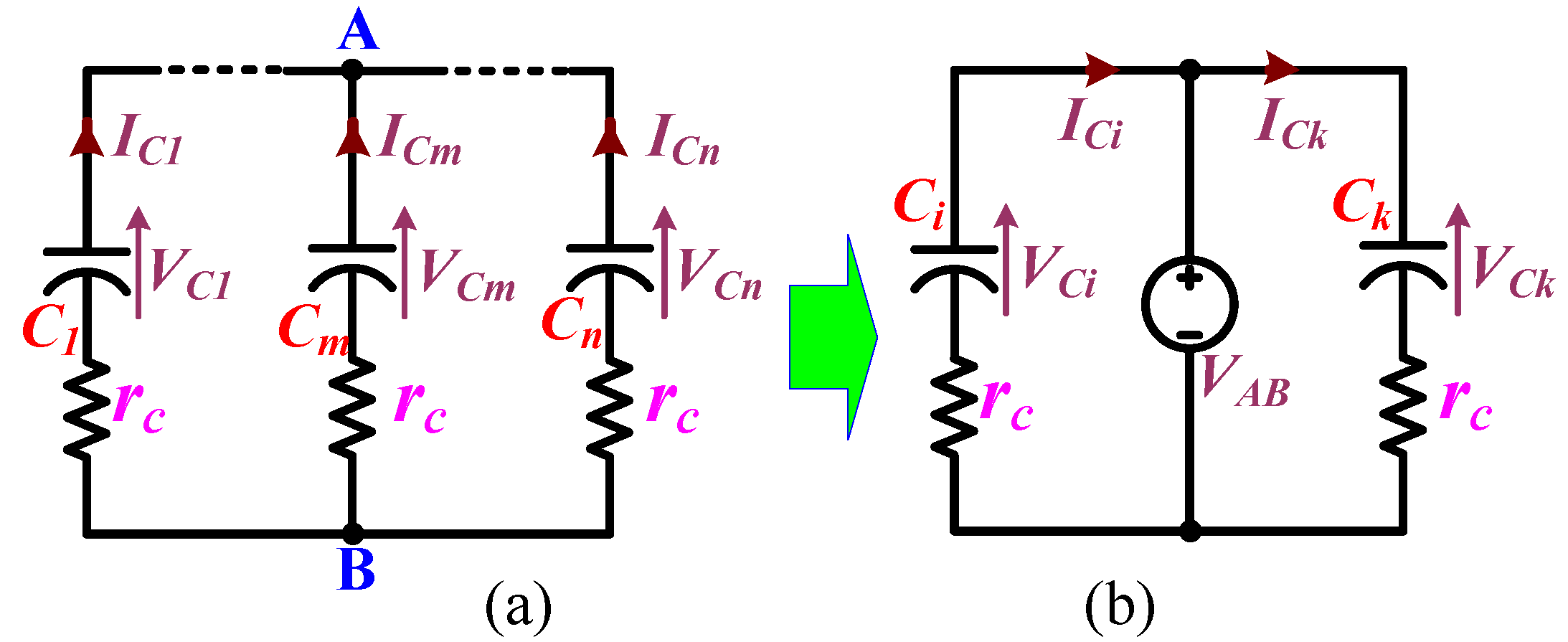

3. Modeling of Proposed SC Voltage Equalizer

In order to facilitate analysis, the following assumptions are made: (i) the on-resistance of switches is so small as compared to the ESR of capacitors that it could be neglected or regarded as a part of the ESR of capacitors; (ii) all capacitors employed in the system have the same capacitance

C and ESR

rC. In this case, the state circuit of

Figure 3c is redrawn in

Figure 7a.

The voltage difference between the points

A and

B can be expressed as:

By using Kirchhoff’s current law (KCL) at the point of

A, the KCL equation could be obtained as given by:

When the KCL Equation (14) is substituted into Equation (13), the voltage

VAB could be further expressed as:

where

qCm is the amount of charge stored in the capacitor

Cm and

qtotal is the total amount of charge of all capacitors. During the whole capacitor balancing process of the phase Φ

2, though charge is transferred from capacitors with the higher voltage to those with the lower voltage, the total charge is constant and the voltage

VAB is therefore can be seen as a constant voltage source. As a result, the equivalent circuit for the phase Φ

2 is derived form above analysis as shown in

Figure 7b.

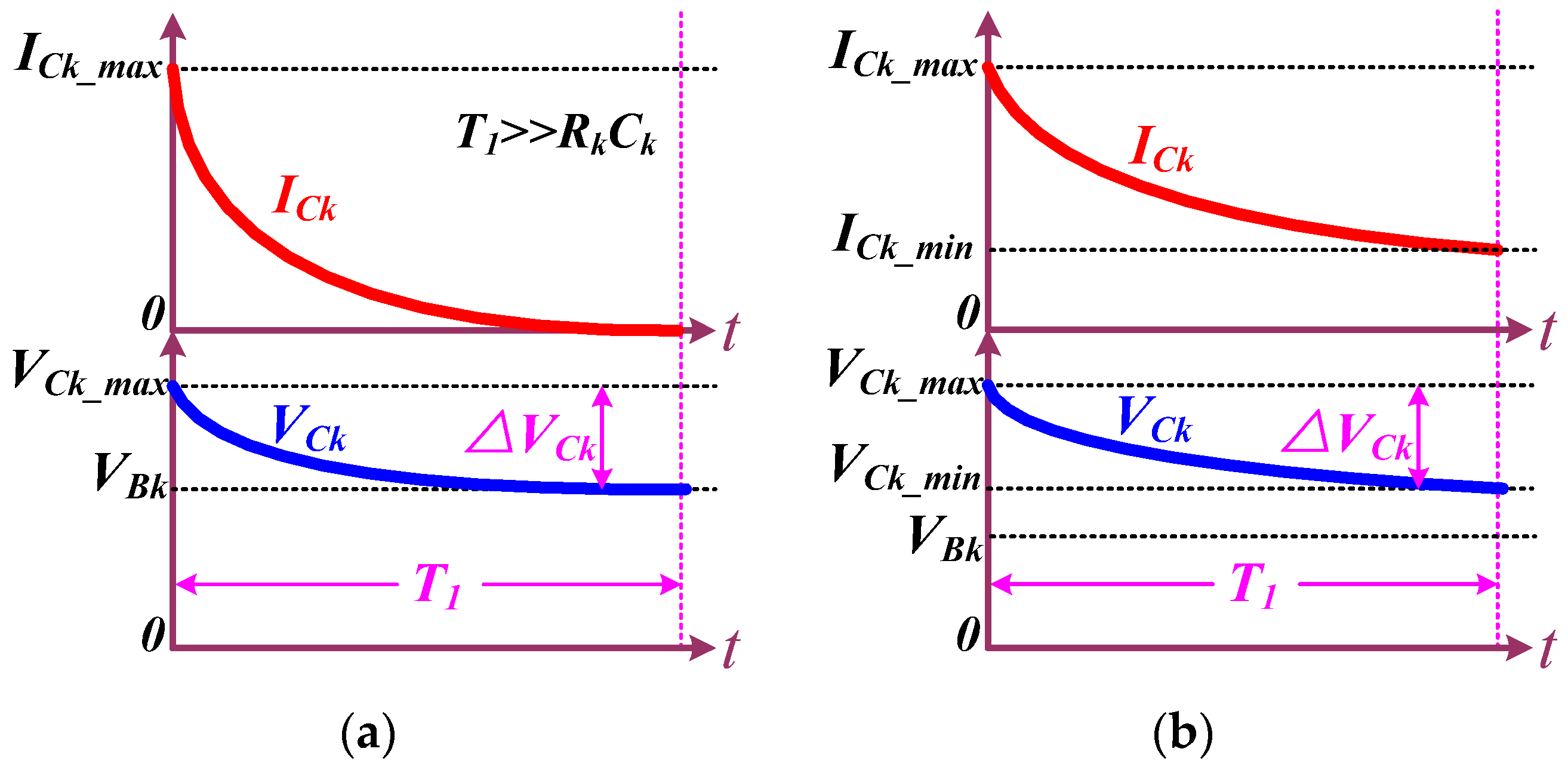

Based on the assumptions made before, the variation of the voltage across the capacitor

Ck, which corresponds to the battery cell

Bk with lower voltage, can be expressed as:

Considering the minimum and maximum values of the capacitor voltage

VCk are obtained at the end of the periods of the phases Φ

1 and Φ

2, respectively, the relationship of the voltages

VBk and

VAB can be derived as:

where

IBk is the average current flowing into the battery cell

Bk and

RBk is the equivalent resistance of the switched capacitor power conversion circuit between

VBk and

VAB. They are expressed as:

where

is the switching frequency,

i.e.,

.

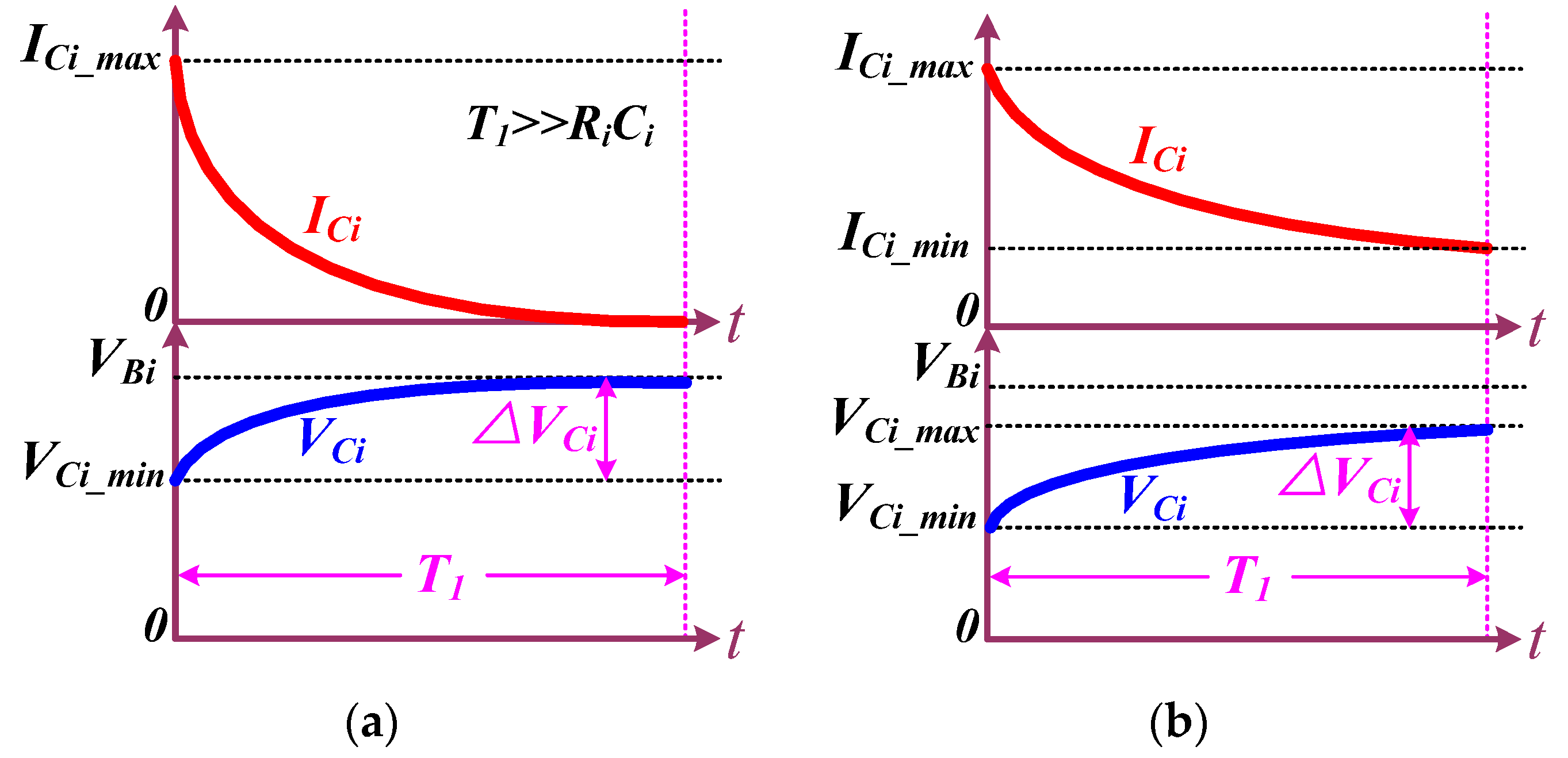

Similarly, the variation of the voltage across the capacitor

Ci, which corresponds to the battery cell

Bi with higher voltage, can be expressed as:

The maximum and minimum capacitor voltages are obtained at the end of the periods of the phases Φ

1 and Φ

2, respectively, the relationship of the voltages

VBi and

VAB can be therefore expressed by:

where

IBi is the average current flowing out of the battery cell

Bi and

RBi is the equivalent resistance between

VBk and

VAB. They are given as:

It can be seen from the Equations (20) and (25) that there is the same equivalent resistance between the constant voltage source VAB and any one battery cell, regards of the cell Bi with higher voltage or the cell Bk with lower voltage.

As well known, an SC power conversion circuits can be equivalent to a combination of an ideal DC transformer and an equivalent resistance [

15,

16,

17]. The model of the proposed automatic voltage equalizer with battery string is derived based on the above analysis, as depicted in

Figure 8. The turns of the ideal multi-winding DC transformer are the same. The value of the equivalent resistor

RB is the same as

RBk and

RBi given in Equations (20) and (25). In the case that ignoring the impact of parasitic resistance, the equivalent resistor

RB could be simplified as given by:

4 Comparison of Proposed Switched-Capacitor Voltage Equalizer with Conventional One

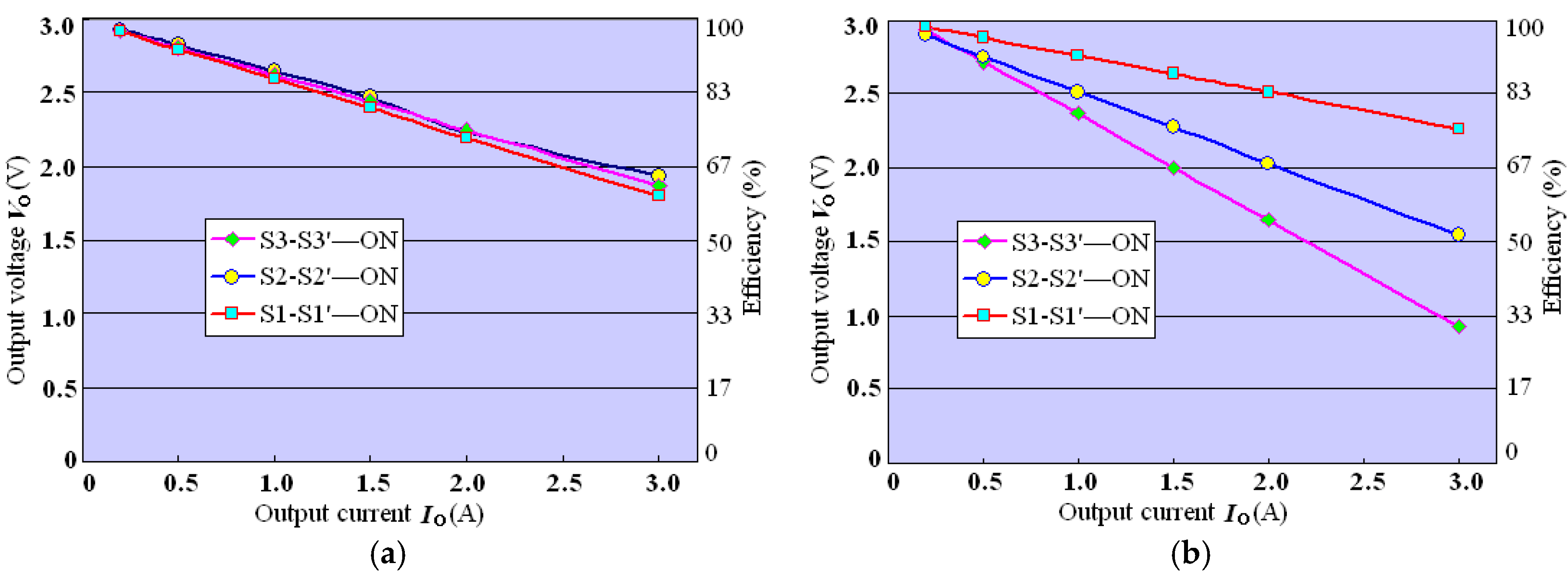

4.1. Switch Stress Comparison

For the switch stress, all of switches in the conventional one share the same voltage stress

VB which is the battery’s cell voltage. The same switch stress is also found across all switches

Sbi,

Sci and

Sdi (i = 2

, …, n) in the proposed voltage equalizer (see

Figure 1b). For the switch

Saj (j = 1, 2

, …, n), it withstands the blocking voltage

(j − 1

)VB. It means the blocking voltage increases along with the increase of the number

j and the maximum switch stress

(n − 1

)VB is found across the switch

San. Considering the cell voltage

VB is usually not higher than 4 V for lithium batteries or 3 V for EDLCs, there is no difficulty to select appropriate transistors to meet the requirement of switch stresses.

For the conventional SC voltage equalizer, a switch is connected to the midpoint tap of two nearby switched capacitors when it is ON. We denote that the capacitor current is positive during charging process whereas it is negative for discharging process. The switch current is therefore the algebraic difference of the two capacitors’ charging or discharging current, i.e., (iCk + 1 − iCk). The same current is also found for the group of switches Saj in the proposed equalization system. For the switch Sbj, its current is the same as the capacitor current iCj. Additionally, the currents flowing though Scj and Sdj are the same and both equal to the algebraic sum of all capacitor currents iCk (k = 1, 2, …, j − 1). The blocking current of each switch can be therefore derived from the maximum charging and discharging currents of corresponding switched capacitors.

4.2. Model Comparison

Using the same modeling method described in the

Section 3 for the voltage equalizer of

Figure 1a, its model is obtained as shown in

Figure 9. The equivalent resistance

RB is the same as that for the model of the proposed one as shown in

Figure 8 with the premise that there are same capacitors and switching frequency in the two voltage equalizers. It could be seen clearly that there are multiple ideal DC transformers with two windings in the model of

Figure 9. The two windings of each transformer are connected with the two adjacent battery cells. In contrast, there is only one ideal DC transformer with multiple windings in the model of the proposed voltage equalizer as shown in

Figure 8.

Comparing the two models, the equivalent resistance between two adjacent battery/EDLC cells is

2RB is

Figure 8 whereas is

RB in

Figure 9. It means the charge-balancing speed of the conventional equalizer (see

Figure 1a) is twice that of the proposed one. However, when charge is need to transfer from the battery cell

Bi with higher initial voltage to

Bk with lower initial voltage, the speed is no longer the same as that for two adjacent cells. In order to facilitate analysis, assuming the cell number

k is larger than

i,

i.e.,

k > i. It could be obtained from the model of

Figure 9 that the equivalent resistance between the two cells

Bk and

Bi is

(k − i)RB, whereas the equivalent resistance

2RB is still found between

Bk and

Bi in the model of

Figure 8.

Hence, the balancing speed of the conventional equalizer is directly related to the interval between the cells Bk and Bi. The farther the interval, the slower the speed is. For the proposed voltage equalizer, however, the balancing speed is independent of the cells’ interval.

Assuming the same power (Vin × Iin) flows into the cell-port of Bi and the cell-port of Bk is configured as the output terminal in the two compared systems, it could be found that the power loss during the transferring process is (k − i)RBIin2 for the conventional equalizer whereas 2RBIin2 for the proposed one. Clearly, the power conversion efficiency of the proposed voltage equalizer is higher than that for the conventional one when the interval (k − i) is larger than 2.

Summing up the above analysis, the conventional voltage equalizer of

Figure 1a is more suitable for the battery/EDLC strings including two series cells. For strings composed by a large number of series cells, the proposed voltage equalizer is superior to the conventional one in the aspect of balancing speed and power conversion efficiency. The larger the number of series battery/EDLC cells, the more obvious the superiority is.

4.3. Simulation Comparison

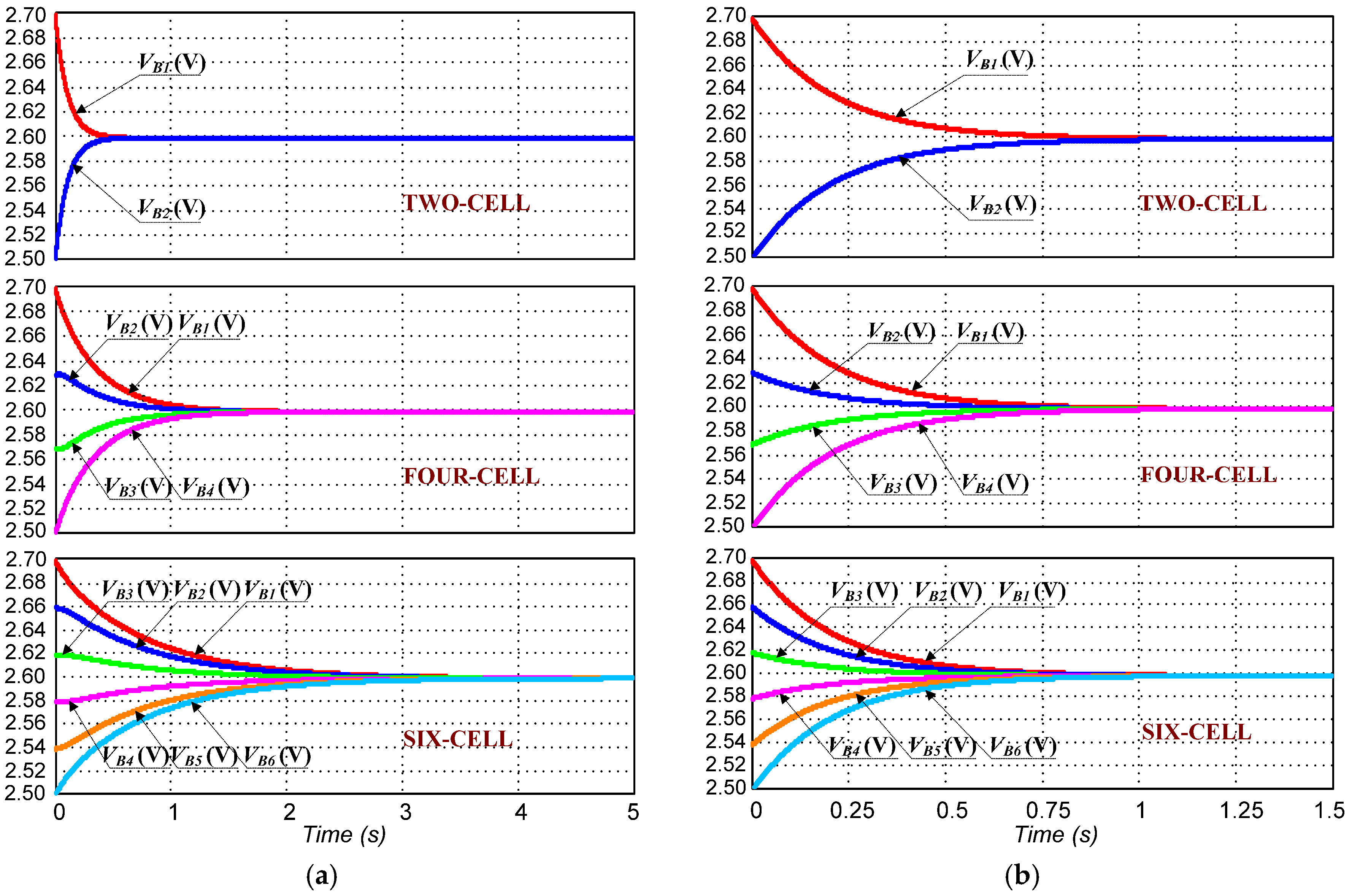

Figure 10a,b shows the simulation cell-voltage waveforms of the balancing process for two-, four- and six-cell EDLC strings with the conventional and proposed SC voltage equalizers, respectively.

The value of each switched capacitor employed in the both simulation equalization circuits is 220 μF. The two systems both operate at 22 kHz switching frequency and every one switching cycle is evenly divided by the two phases Φ

1 and Φ

2. Capacitors with 1 F capacitance and different initial voltages are used as cells. For the two-cell string, the initial voltages of cells are 2.7 V and 2.5 V. It could be seen from the upper of

Figure 10a that the voltage gap between the two cells changes from 0.2 V to zero for about 0.5 s with the conventional equalizer, which is shorter than that with proposed one, 1.1 s given in the upper of

Figure 10b. For the four-cell system with initial cell voltages (2.5 V 2.57 V 2.63 V 2.7 V), the balancing process consumes about 1.9 s for the conventional equalizer while 1.1 s for the proposed one, as shown in the middles of

Figure 10a,b. With initial cell voltages (2.5 V 2.54 V 2.58 V 2.62 V 2.66 V 2.7 V), the equalization process for six-cell is given in the lower of both subfigures. It shows that the balancing time is more than 4.5 s for the conventional equalizer while still about 1.1 s for the proposed one.

Comparing the three balancing processes given in both

Figure 10a,b, it could be seen that the balancing time increases significantly along with the increase of the number of series EDLC cells for the conventional SC voltage equalizer. For the proposed SC equalizer, however, the balancing duration is almost independent from the number of the series cells. Thus, the same conclusions that the proposed voltage equalizer is superior to the conventional one for the multi-cell string and the latter is more suitable for two-cell system are found in both model comparison and simulation results.