Voltage Jump Suppression and Capacitor Voltage Fluctuation Analysis for a Four-Level Hybrid Flying Capacitor T-Type Converter

Abstract

:1. Introduction

2. Analysis of the Converter Topology

2.1. Comparison of Four-Level Topologies

2.2. Operation of the Converter

3. Flying Capacitor Voltage Control Method

3.1. Analysis of the Flying Capacitor Voltages

3.2. Control of the Flying Capacitor Voltages

4. Simulation Results

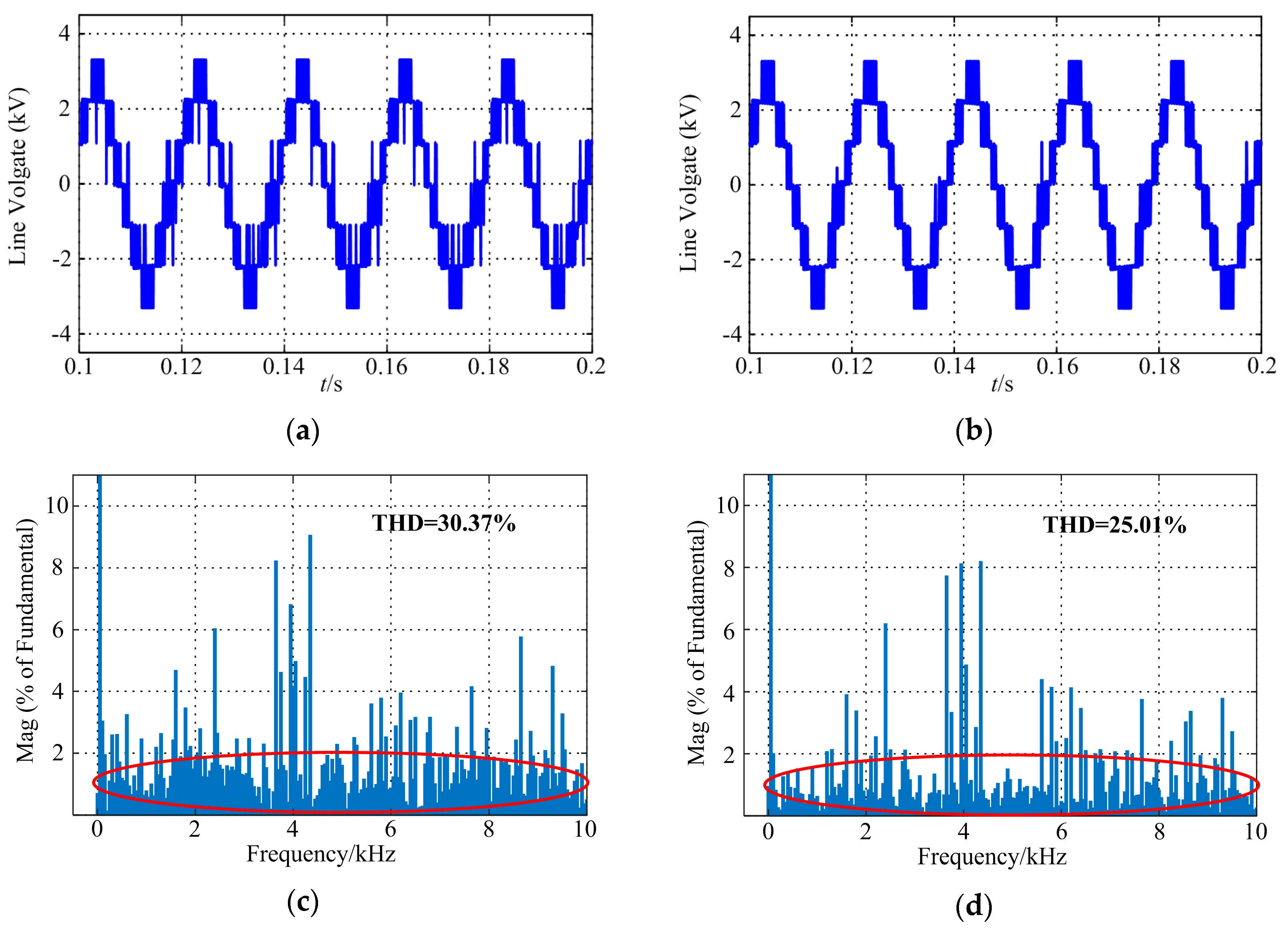

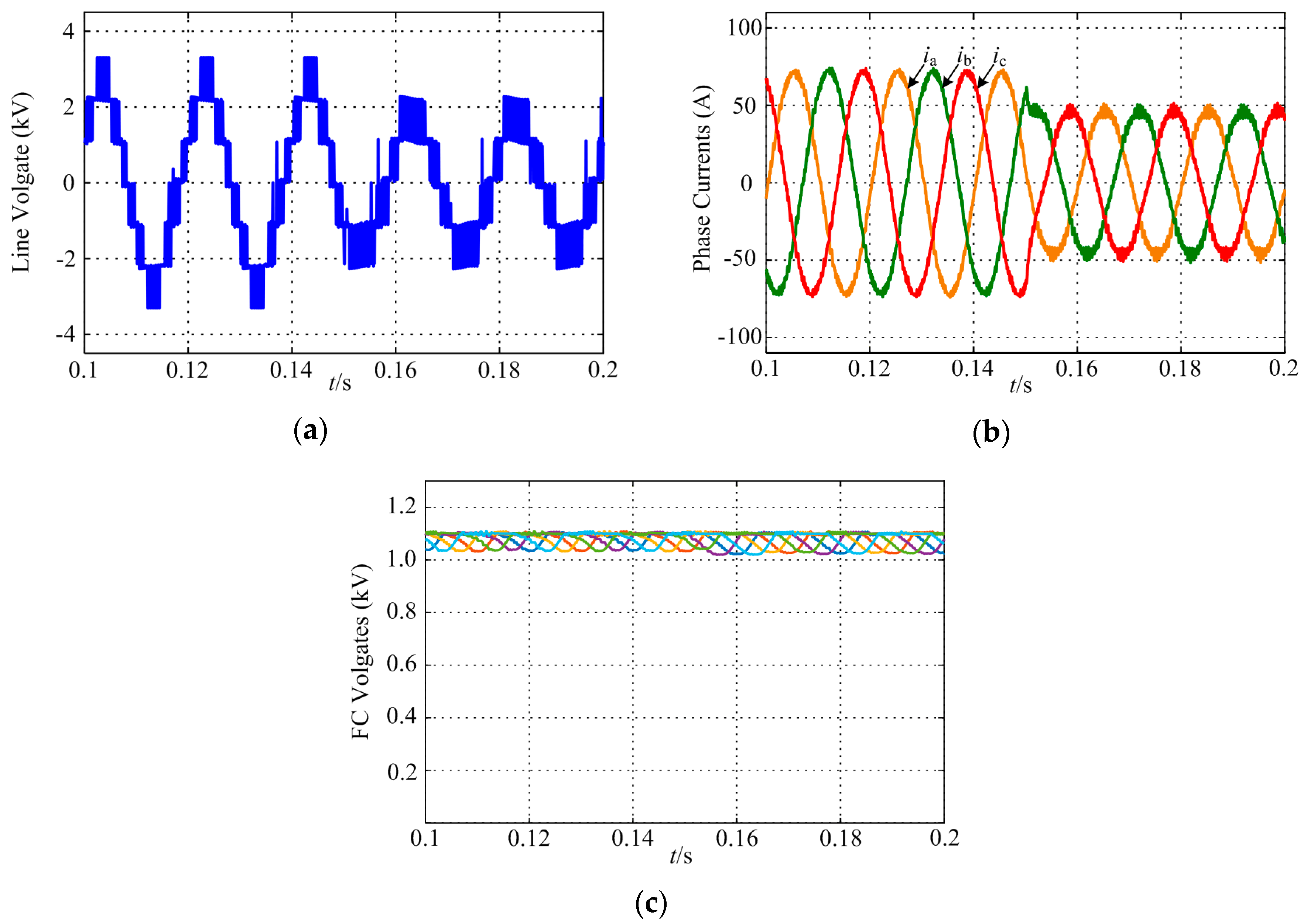

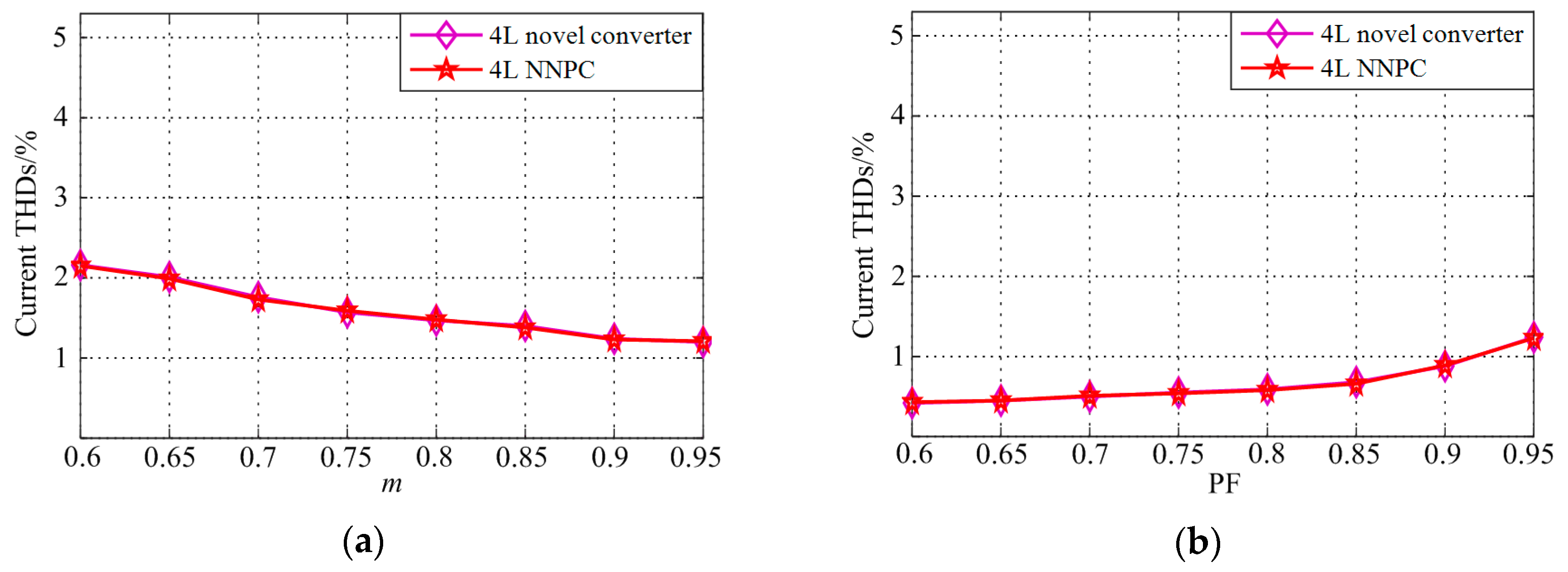

4.1. Steady State Simulation Recults

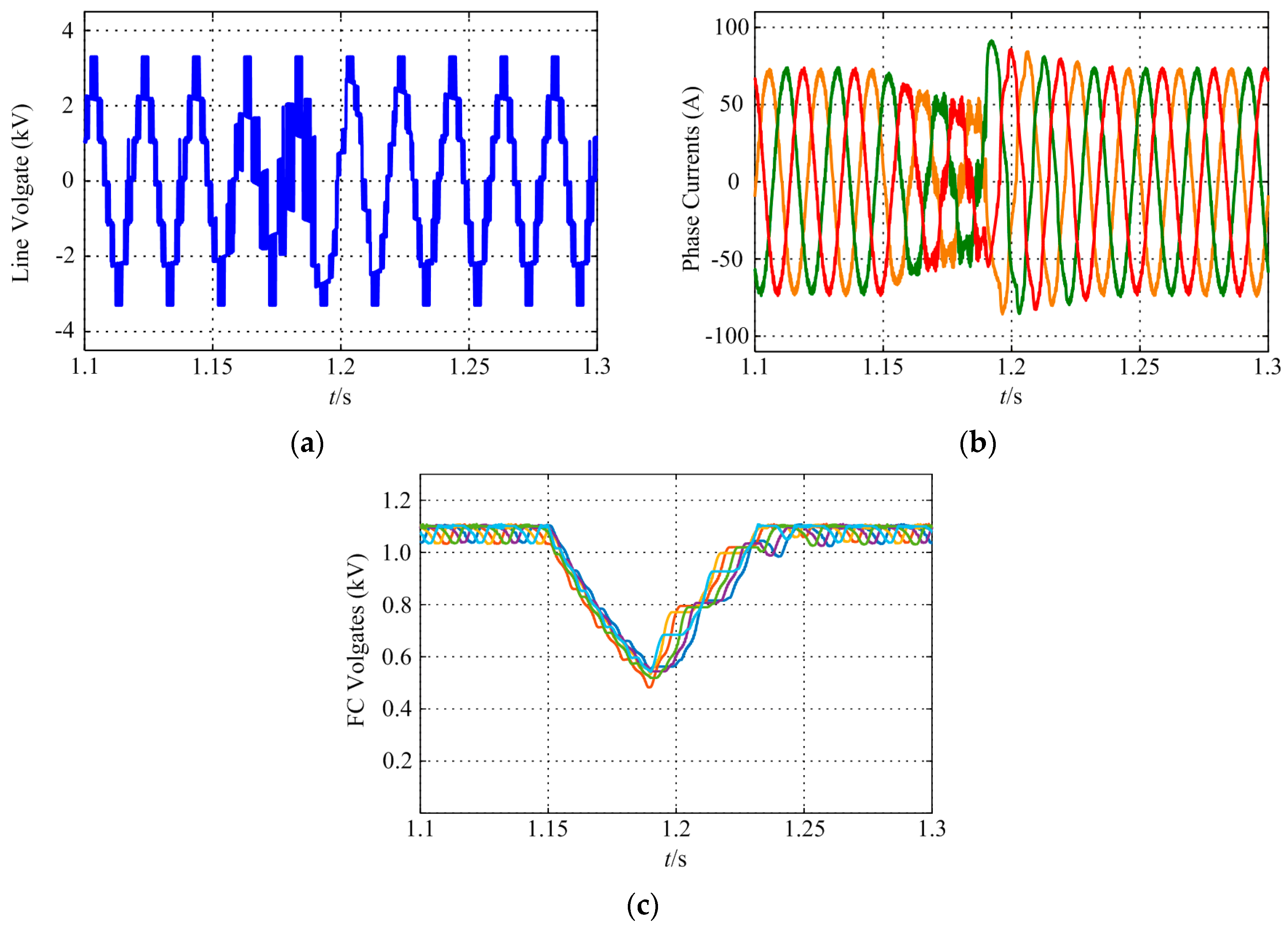

4.2. Transient State Simulation Results

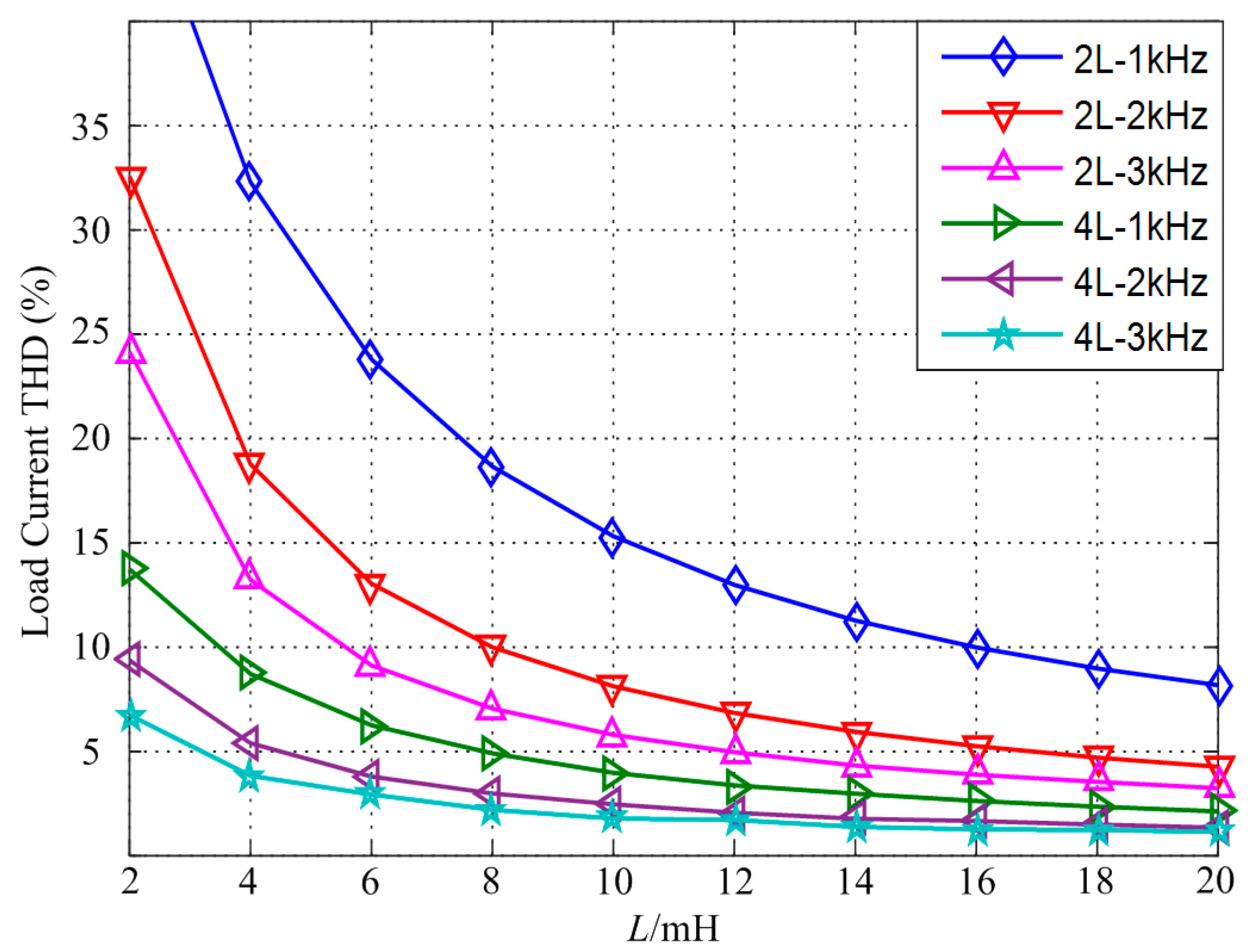

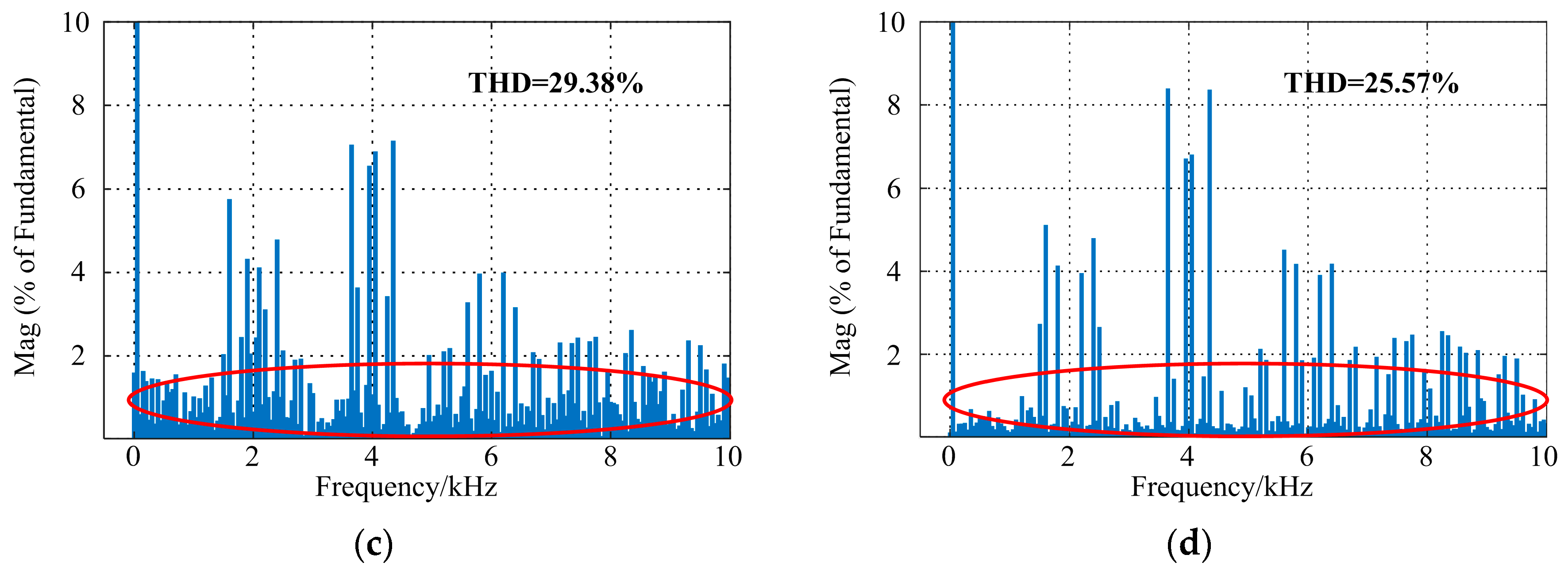

4.3. Comparison with Two-Level Converter

4.4. Analysis of the Capacitor Voltage Fluctuations

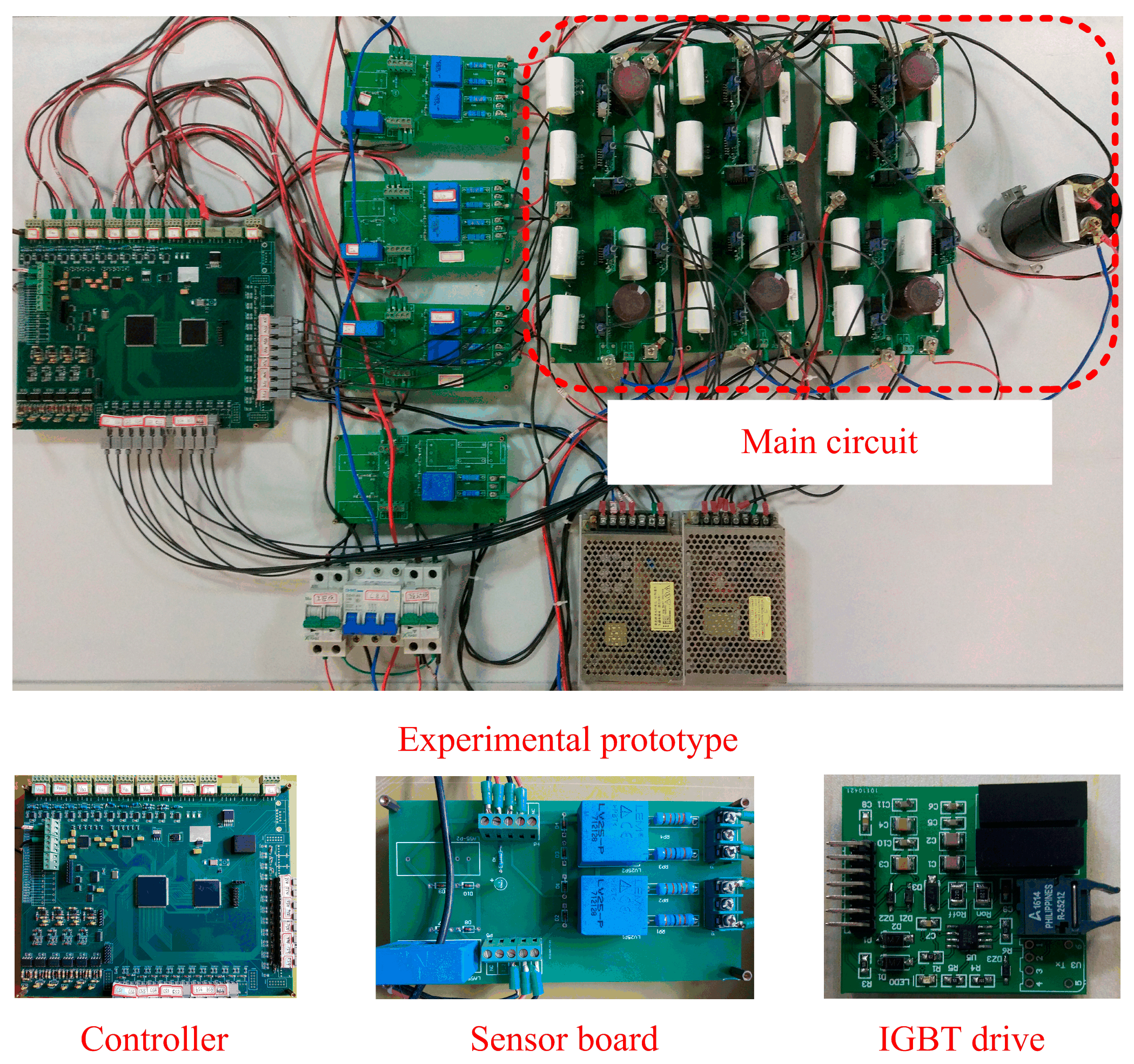

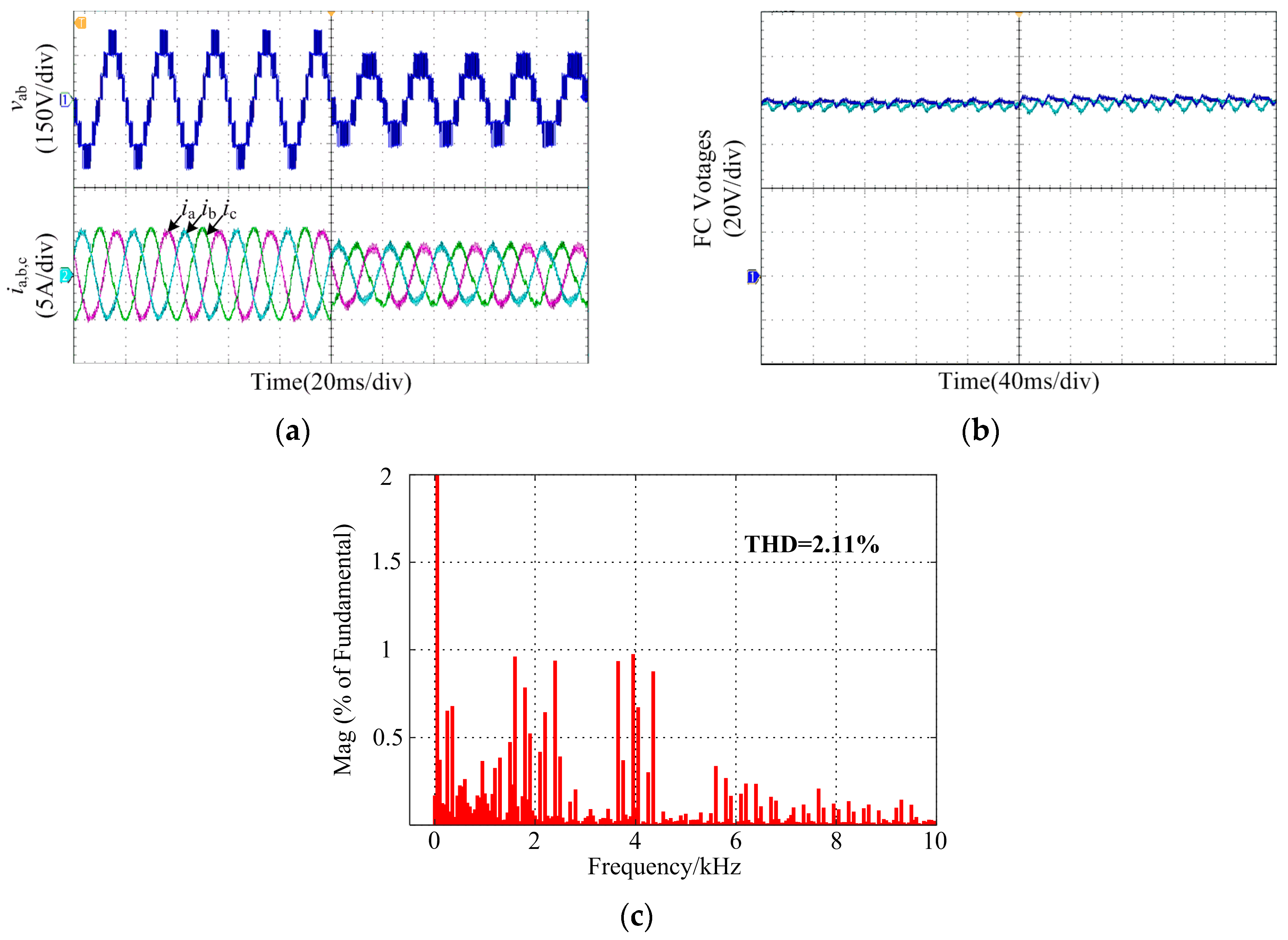

5. Experimental Results

6. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Kouro, S.; Malinowski, M.; Gopakunmar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Gong, Z.; Cui, Q.; Zheng, X.; Dai, P.; Cao, D. An improved inperialist competitive algorithm to solve the selected harmonic elimination pulse-width modulation in multilevel converters. Energies 2018, 11, 3080. [Google Scholar] [CrossRef]

- Yang, D.; Yin, L.; Xu, S.; Wu, N. Power and voltage control for single-phase cascaded H-bridge multilevel converters under unbalanced loads. Energies 2018, 11, 2435. [Google Scholar] [CrossRef]

- Yuan, X. A new nine-switch non-regenerative four-level rectifier. In Proceedings of the 16th European Conference on Power Electronics and Applications (EPE’ 14-ECCE Europe), Lappeenranta, Finland, 26–28 August 2014. [Google Scholar]

- Yuan, X. Derivation of multilevel voltage source converter topologies. In Proceedings of the IECON 2016 42nd Annual Conference on IEEE Industrial Electronics, Florence, Italy, 23–26 October 2016. [Google Scholar]

- Holtz, J. Self-communtated inverters with staircase output voltage for large power and high frequency. Siemens Res. Dev. Rep. 1977, 6, 164–171. [Google Scholar]

- Schweizer, M.; Kolar, J.W. Design and implementation of a highly efficient three-level T-type converter for low-voltage applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Aghdam, G.H. Optimised active harmonic elimination technique for three-level T-type inverters. IET Power Electron. 2013, 6, 425–433. [Google Scholar] [CrossRef]

- Xu, S.; Zhang, J.; Hang, J. Investigation of a fault-tolerant three-level T-type inverter system. IEEE Trans. Ind. Appl. 2017, 53, 4613–4623. [Google Scholar] [CrossRef]

- Li, J.; Englebretson, S.; Huang, A.Q. Reliability comparison for 3L-NPC and 3L-ANPC converters for drives application. In Proceedings of the 2011 IEEE International Electric Machines & Drives Conference (IEMDC), Niagara Falls, ON, Canada, 15–18 May 2011; pp. 271–276. [Google Scholar]

- Jiao, Y.; Lee, F.C. New modulation scheme for three-level active neutral-point-clamped converter with loss and stress reduction. IEEE Trans. Ind. Electron. 2015, 62, 5468–5479. [Google Scholar] [CrossRef]

- Hu, C.; Holmes, G.; Shen, W.; Yu, X.; Wang, Q.; Luo, F. Neutral-point potential balancing control strategy of three-level active NPC inverter based on SHEPWM. IET Power Electron. 2017, 10, 1943–1950. [Google Scholar] [CrossRef]

- Li, J.; Huang, A.Q.; Liang, Z.; Bhattacharya, S. Analysis and design of active NPC (ANPC) inverters for fault-tolerant operation of high-power electrical drives. IEEE Trans. Power Electron. 2012, 27, 519–533. [Google Scholar] [CrossRef]

- Burguete, E.; López, J.; Zabaleta, M. New five-level active neutral-point-clamped converter. IEEE Trans. Ind. Appl. 2015, 51, 440–447. [Google Scholar] [CrossRef]

- Taallah, A.; Mekhilef, S. Active neutral point clamped converter for equal loss distribution. IET Power Electron. 2014, 7, 1859–1867. [Google Scholar] [CrossRef]

- Burguet, E.; López, J.; Zabaleta, M. A new five-level active neutral-point-clamped converter with reduced overvoltages. IEEE Trans. Ind. Electron. 2016, 63, 7175–7183. [Google Scholar] [CrossRef]

- Wang, K.; Li, Y.; Zheng, Z.; Xu, L. A novel hybrid-clamped four-level converter. In Proceedings of the 27th Annual Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 2442–2447. [Google Scholar]

- Wang, K.; Zheng, Z.; Xu, L.; Li, Y. A four-level hybrid-clamped converter with natural capacitor voltage balancing ability. IEEE Trans. Power Electron. 2014, 29, 1152–1162. [Google Scholar] [CrossRef]

- Wang, K.; Xu, L.; Zheng, Z.; Li, Y. Voltage balancing control of a four-level hybrid-clamped converter based on zero-sequence voltage injection using phase-shifted PWM. IEEE Trans. Power Electron. 2016, 31, 5389–5399. [Google Scholar] [CrossRef]

- Narimani, M.; Wu, B.; Cheng, Z.; Zargari, N.R. A new nested neutral point-clamped (NNPC) converter for medium-voltage (MV) power conversion. IEEE Trans. Power Electron. 2014, 29, 6375–6382. [Google Scholar] [CrossRef]

- Narimani, M.; Wu, B.; Cheng, Z.; Zargari, N.R. A novel and simple single-phase modular for the nested neutral-point clamped (NNPC) converter. IEEE Trans. Power Electron. 2015, 30, 4069–4078. [Google Scholar] [CrossRef]

- Tian, K.; Wu, B.; Narimani, M.; Xu, D.; Cheng, Z.; Zargari, N.R. A capacitor voltage-balancing method for nested neutral point clamped (NNPC) inverter. IEEE Trans. Power Electron. 2016, 31, 2575–2583. [Google Scholar] [CrossRef]

- Hajirayat, A.; Faraji, F.; Birjandi, A.A.M. A novel nested T-type four-level inverter for medium voltage applications. In Proceedings of the 31st International Power System Conference (PSC), Tehran, Iran, 24–26 October 2016. [Google Scholar]

- Wei, C.; Yuan, X.; Wu, X.; Zhou, J.; Yuan, Y.; Zhu, Y. A new four-level converter for low and medium voltage applications. In Proceedings of the IECON 2017 43rd Annual Conference on IEEE Industrial Electronics, Beijing, China, 29 October–1 November 2017; pp. 6351–6356. [Google Scholar]

- Bahrami, A.; Narimani, M. A sinusoidal pulse width modulation (SPWM) technique for capacitor voltage balancing of nested T-type four-level inverter. IEEE Tran. Power Electron. 2019, 34, 1008–1012. [Google Scholar] [CrossRef]

- Mcgrath, B.P.; Holmes, D.G. Multicarrier PWM strategies for multilevel inverters. IEEE Tran. Ind. Electron. 2002, 49, 858–867. [Google Scholar] [CrossRef]

- Jin, B.; Yuan, X. Topology, efficiency analysis and control of a four-level π-type converter. IEEE J. Energy Sel. Top. Power Electron. 2018. [Google Scholar] [CrossRef]

| Topology | Switches | Clamping Diodes | Flying Capacitors | DC-Link Capacitors |

|---|---|---|---|---|

| 4L-NPC | 18 | 12 | - | 3 |

| 4L-FC | 18 | - | 9 | 1 |

| 4L-HC | 24 | - | 3 | 3 |

| 4L-NNPC | 18 | 6 | 6 | 1 |

| 4L hybrid converter | 18 | - | 6 | 1 |

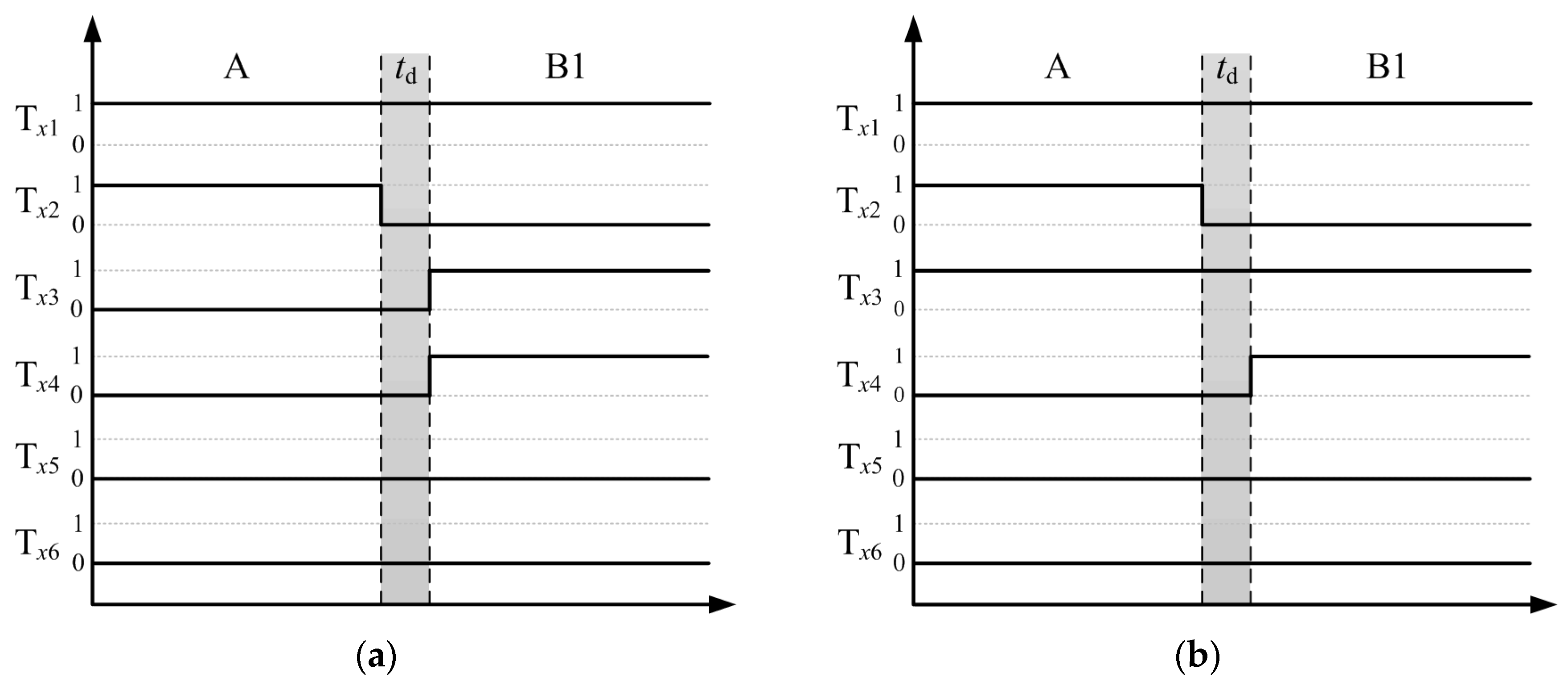

| Output Level | Vxo | Tx1 | Tx2 | Tx3 | Tx4 | Tx5 | Tx6 | Switching State |

|---|---|---|---|---|---|---|---|---|

| 3 | Vdc | 1 | 1 | 0 | 0 | 0 | 0 | A |

| 2 | 2Vdc/3 | 1 | 0 | 1 | 1 | 0 | 0 | B1 |

| 0 | 1 | 0 | 0 | 0 | 1 | B2 | ||

| 1 | Vdc/3 | 1 | 0 | 0 | 0 | 1 | 0 | C1 |

| 0 | 0 | 1 | 1 | 0 | 1 | C2 | ||

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | D |

| Output Level | Vxo | Tx1 | Tx2 | Tx3 | Tx4 | Tx5 | Tx6 | Switching State |

|---|---|---|---|---|---|---|---|---|

| 3 | Vdc | 1 | 1 | 1 | 0 | 0 | 0 | A |

| 2 | 2Vdc/3 | 1 | 0 | 1 | 1 | 0 | 0 | B1 |

| 0 | 1 | 1 | 0 | 0 | 1 | B2 | ||

| 1 | Vdc/3 | 1 | 0 | 0 | 1 | 1 | 0 | C1 |

| 0 | 0 | 1 | 1 | 0 | 1 | C2 | ||

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | D |

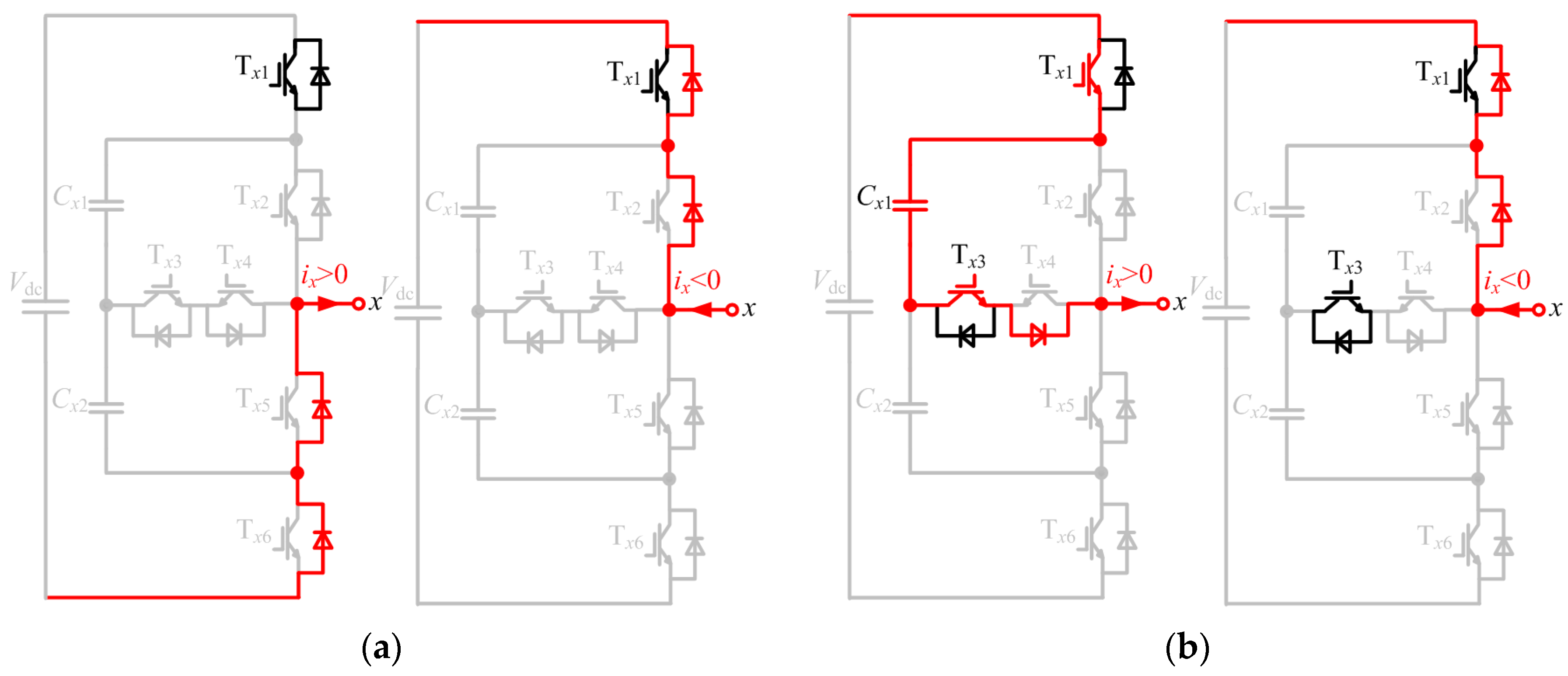

| Output Level | Phase Current, ix | Cx1 | Cx2 | Switching State |

|---|---|---|---|---|

| 3 | - | No effect | No effect | A |

| 2 | >0 | Charging | No effect | B1 |

| <0 | Discharging | No effect | ||

| >0 | Discharging | Discharging | B2 | |

| <0 | Charging | Charging | ||

| 1 | >0 | Charging | Charging | C1 |

| <0 | Discharging | Discharging | ||

| >0 | No effect | Discharging | C2 | |

| <0 | No effect | Charging | ||

| 0 | - | No effect | No effect | D |

| Parameters | Values |

|---|---|

| DC Voltage | 3300 V |

| Flying Capacitor | 1000 μF |

| Output Frequency | 50 Hz |

| Load Inductance | 7.5 mH |

| Load Resistance | 20 Ω |

| Switching Frequency | 2 kHz |

| Dead-time | 4 μs |

| Parameters | Values |

|---|---|

| DC Voltage | 240 V |

| Flying Capacitor | 1000 μF |

| Output Frequency | 50 Hz |

| Load Inductance | 7.5 mH |

| Load Resistance | 20 Ω |

| Switching Frequency | 2 kHz |

| Dead-time | 4 μs |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wei, C.; Yuan, X.; Zhou, J.; Wang, K.; Zhang, Y.; Wu, X. Voltage Jump Suppression and Capacitor Voltage Fluctuation Analysis for a Four-Level Hybrid Flying Capacitor T-Type Converter. Energies 2019, 12, 698. https://doi.org/10.3390/en12040698

Wei C, Yuan X, Zhou J, Wang K, Zhang Y, Wu X. Voltage Jump Suppression and Capacitor Voltage Fluctuation Analysis for a Four-Level Hybrid Flying Capacitor T-Type Converter. Energies. 2019; 12(4):698. https://doi.org/10.3390/en12040698

Chicago/Turabian StyleWei, Chen, Xibo Yuan, Juan Zhou, Kangan Wang, Yonglei Zhang, and Xiaojie Wu. 2019. "Voltage Jump Suppression and Capacitor Voltage Fluctuation Analysis for a Four-Level Hybrid Flying Capacitor T-Type Converter" Energies 12, no. 4: 698. https://doi.org/10.3390/en12040698