Power and Voltage Control for Single-Phase Cascaded H-Bridge Multilevel Converters under Unbalanced Loads

Abstract

:1. Introduction

2. Control Method Principles

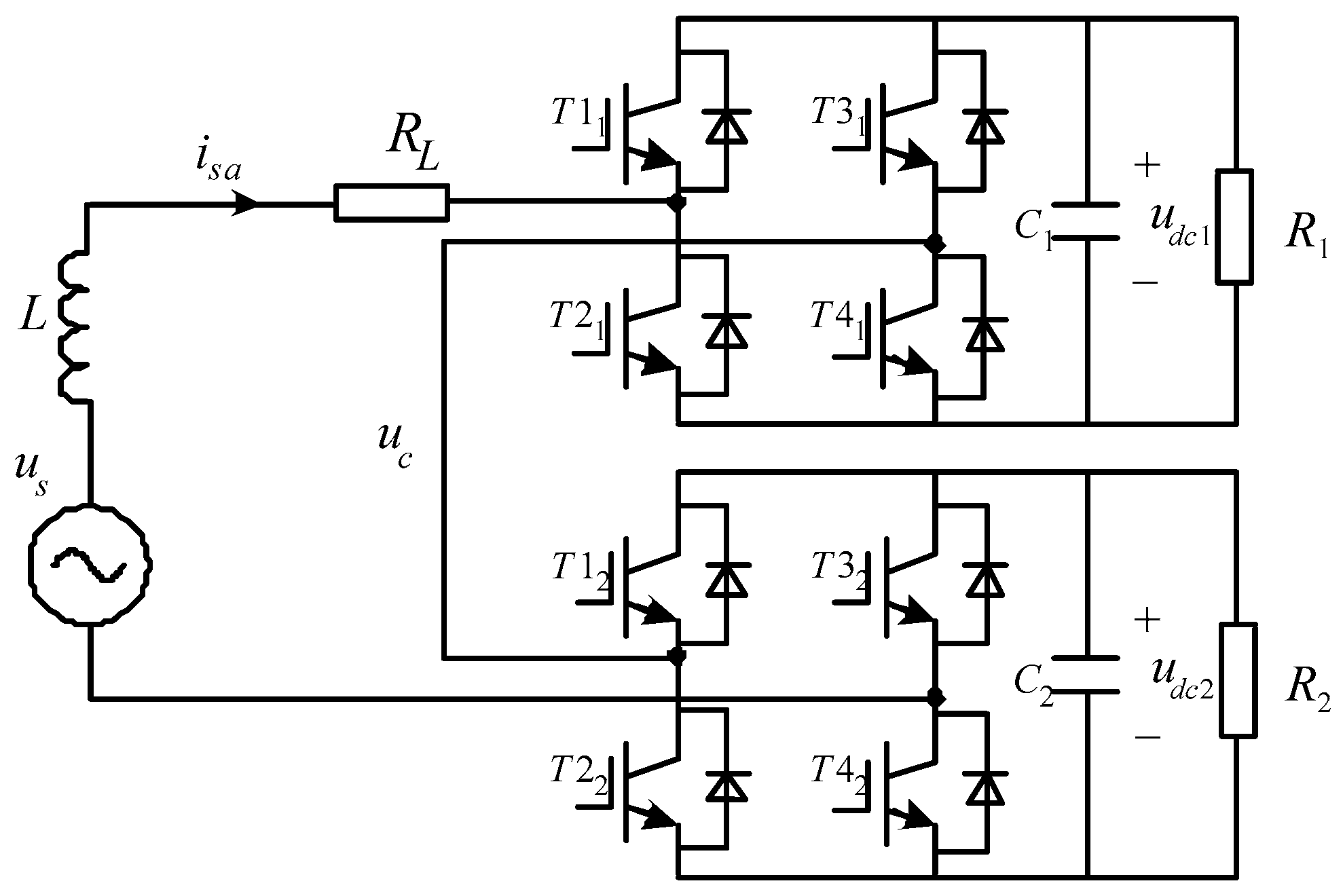

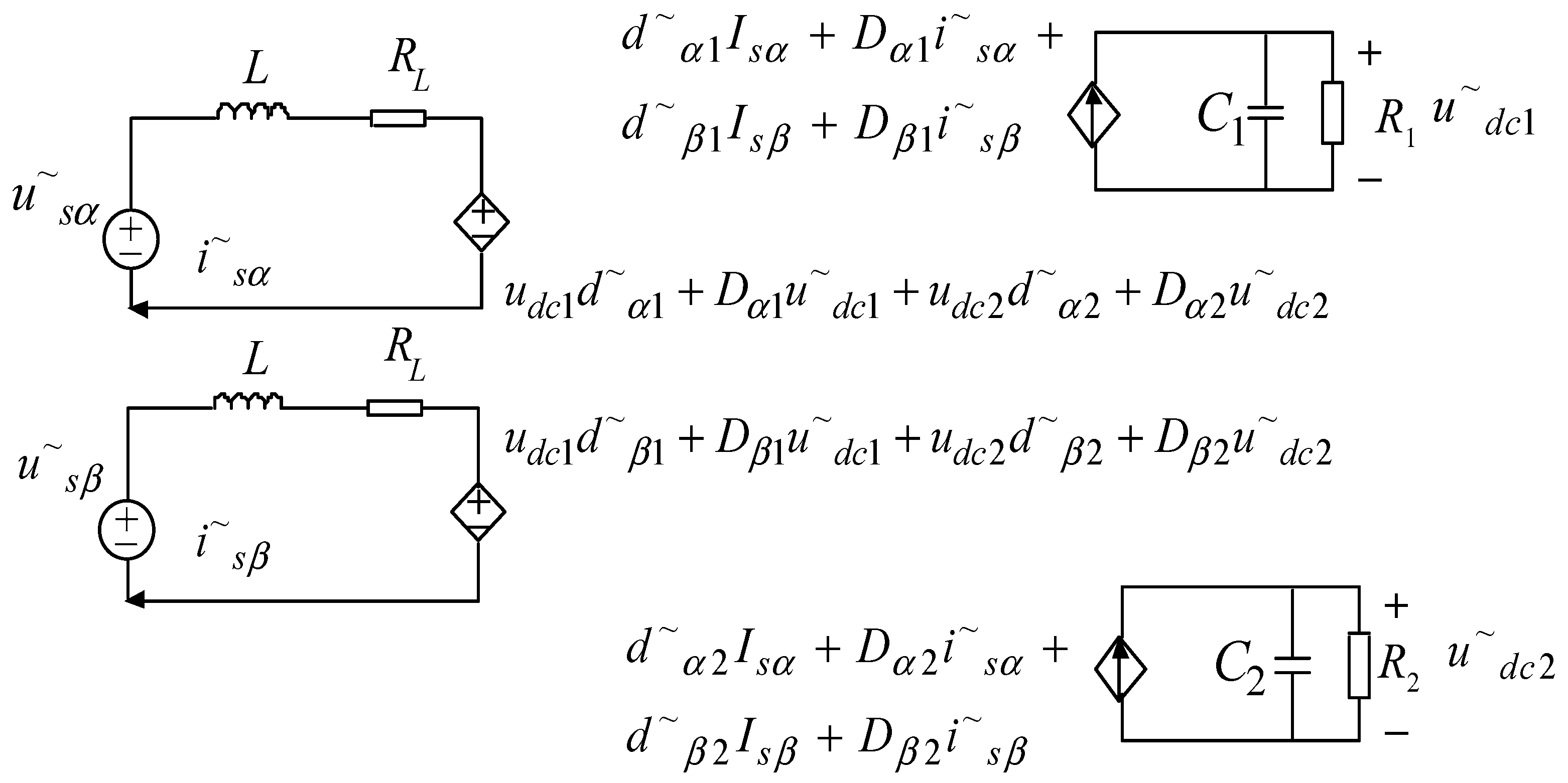

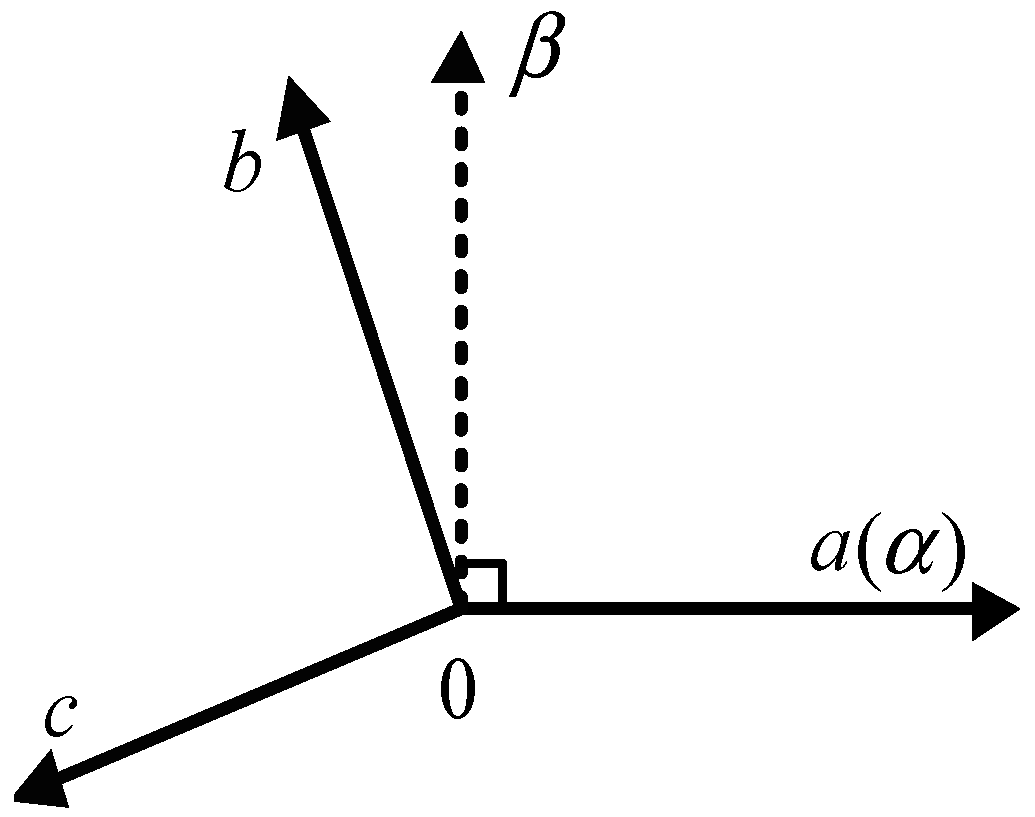

2.1. Model of the Cascaded H-Bridge Multilevel Converter

2.2. Principle of the Proposed Power Control Method

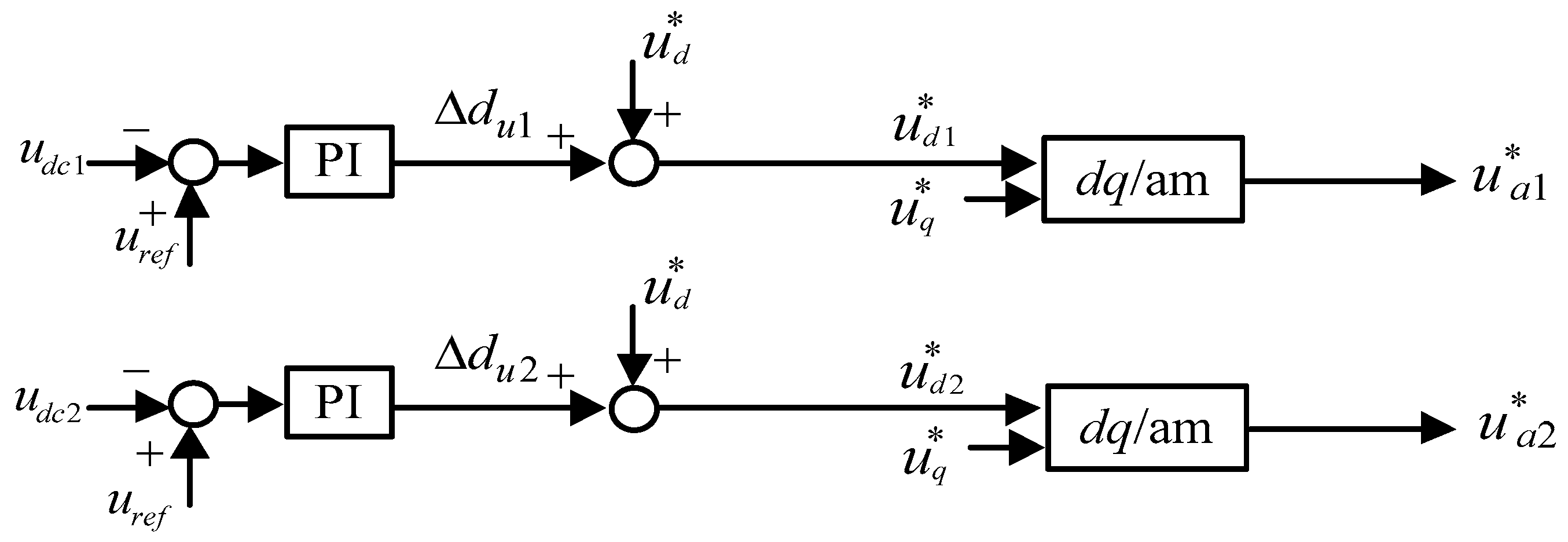

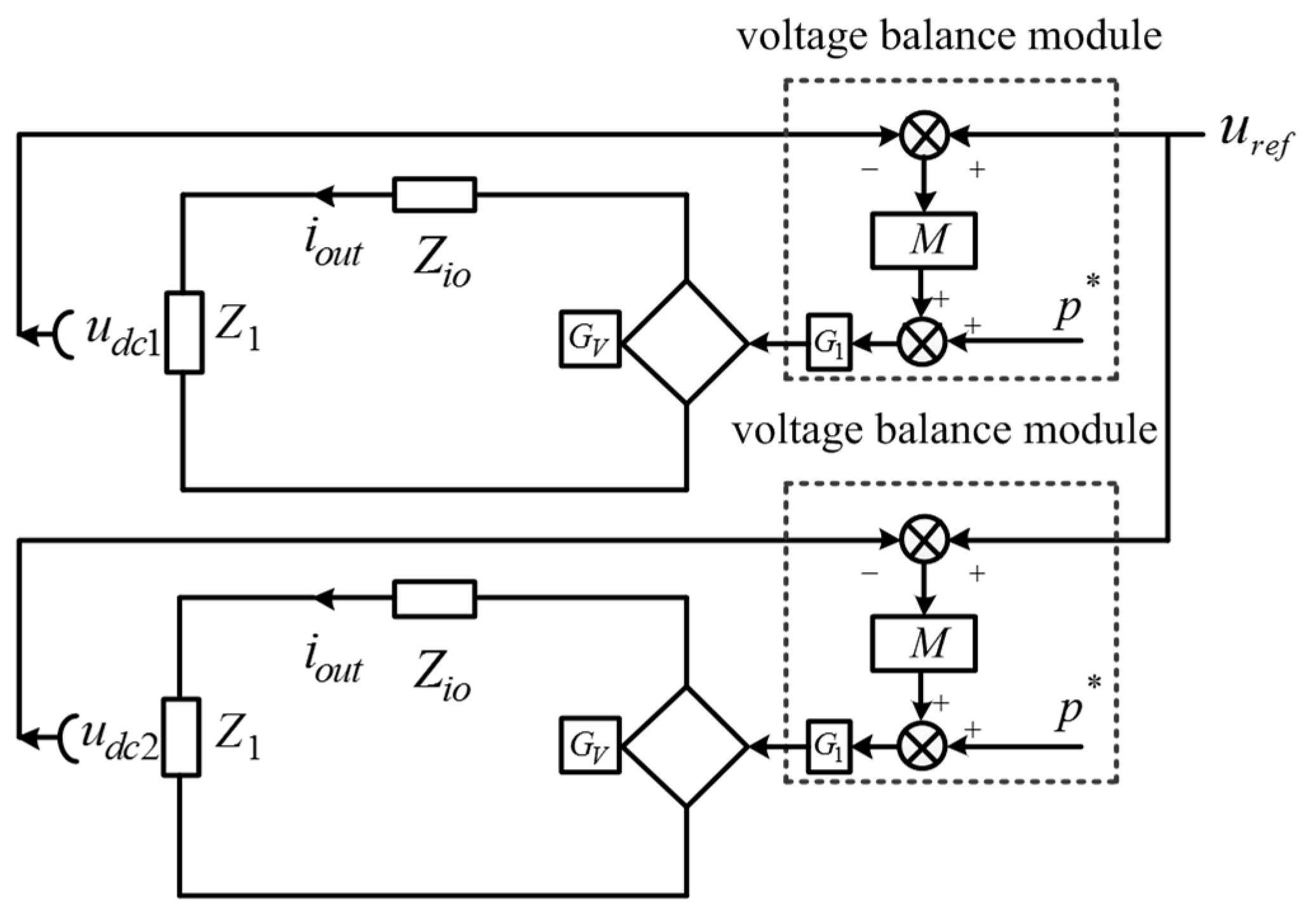

2.3. Presentation of Proposed Dc-Link Balance Controller

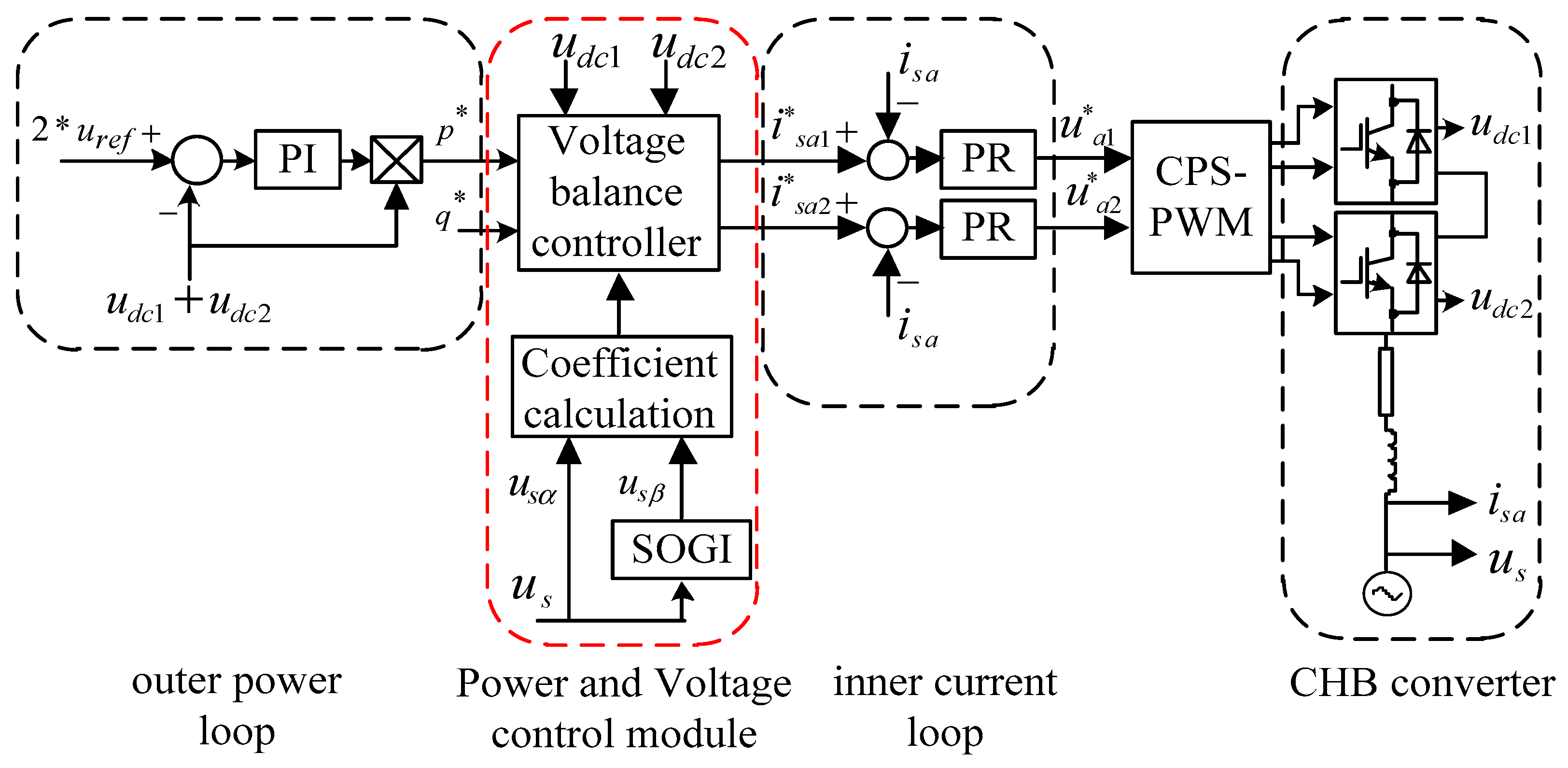

2.4. Proposed Power Control of the Cascaded H-Bridge Multilevel Converter

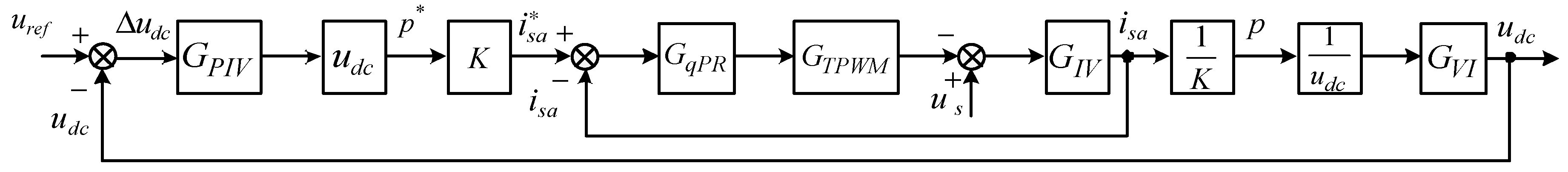

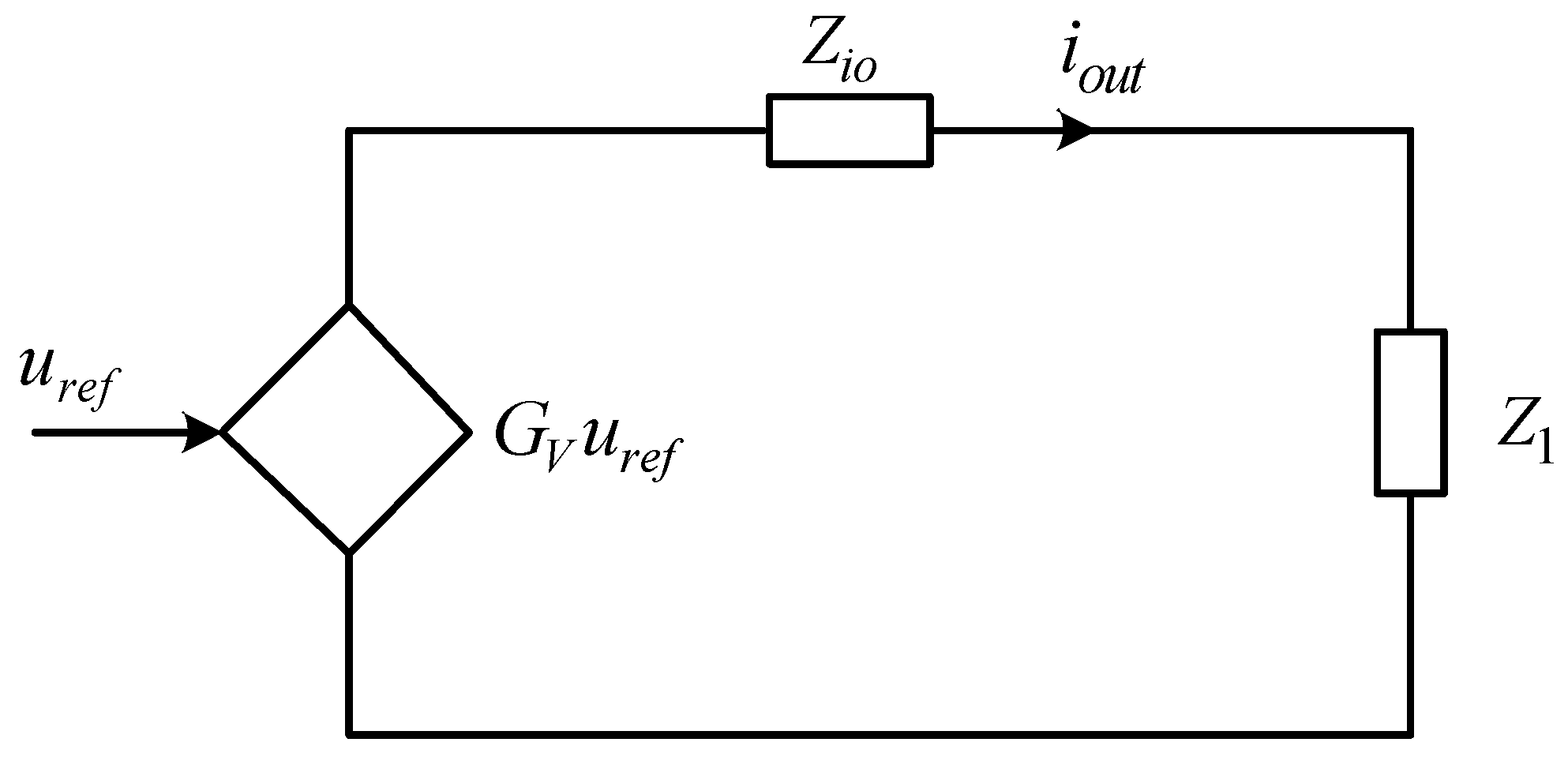

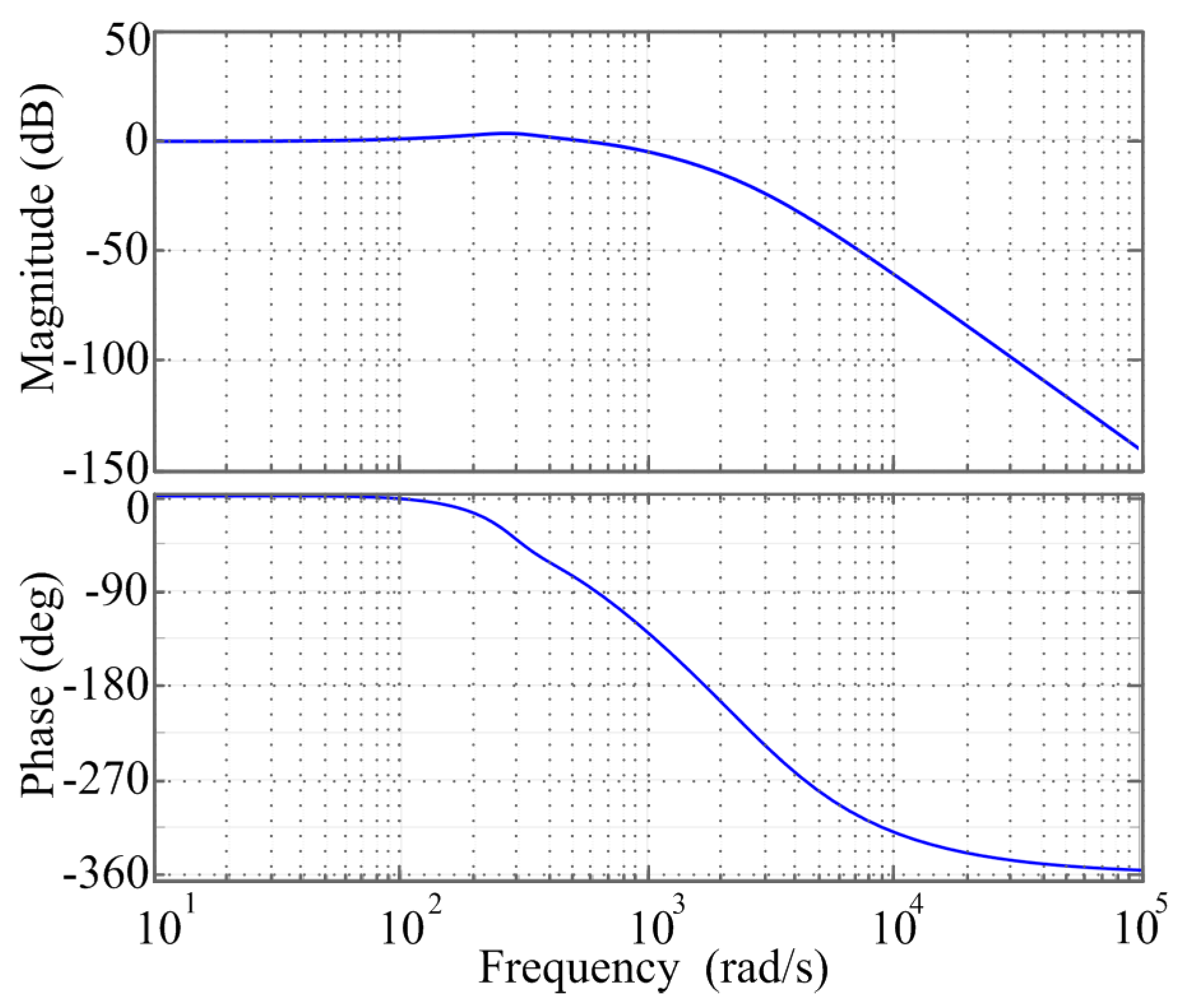

2.5. Stability Analysis of the Power and Voltage Control Scheme

3. Simulation Results

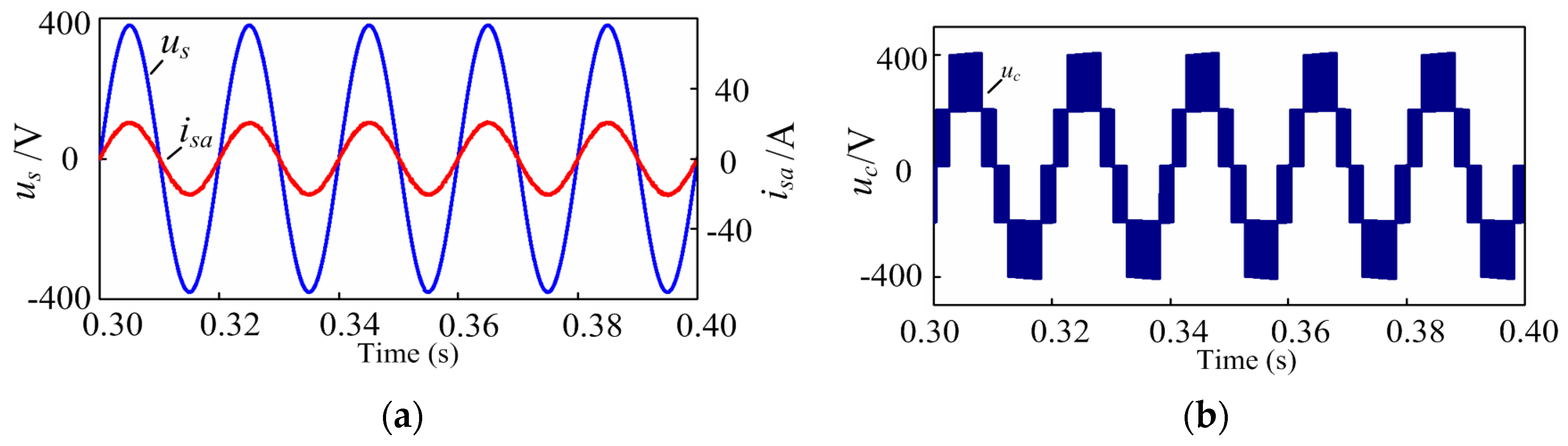

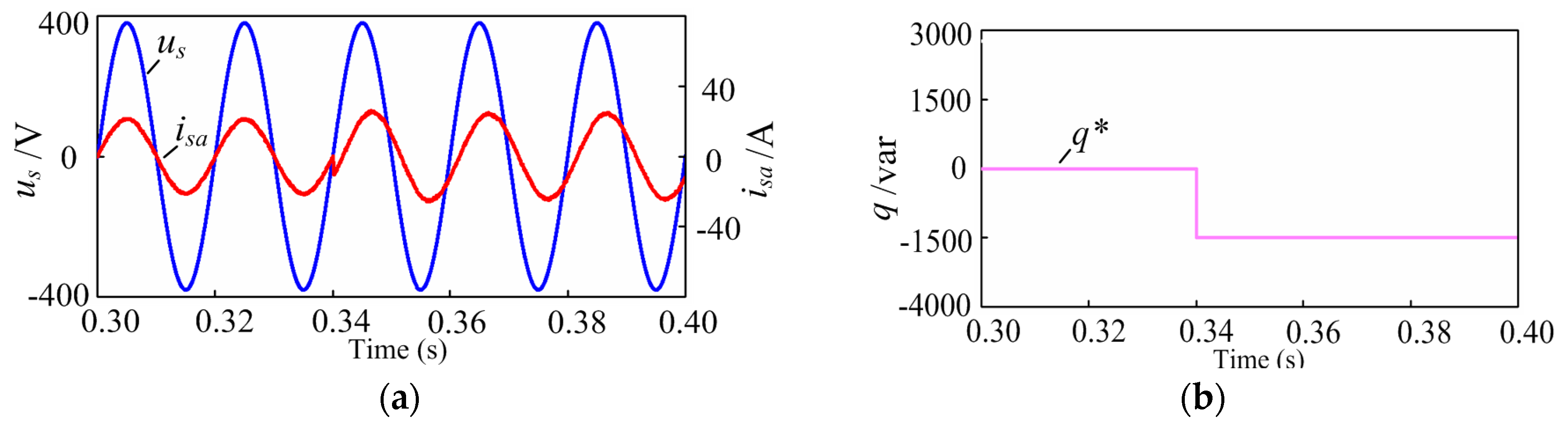

3.1. Proposed Power Control Scheme Simulation

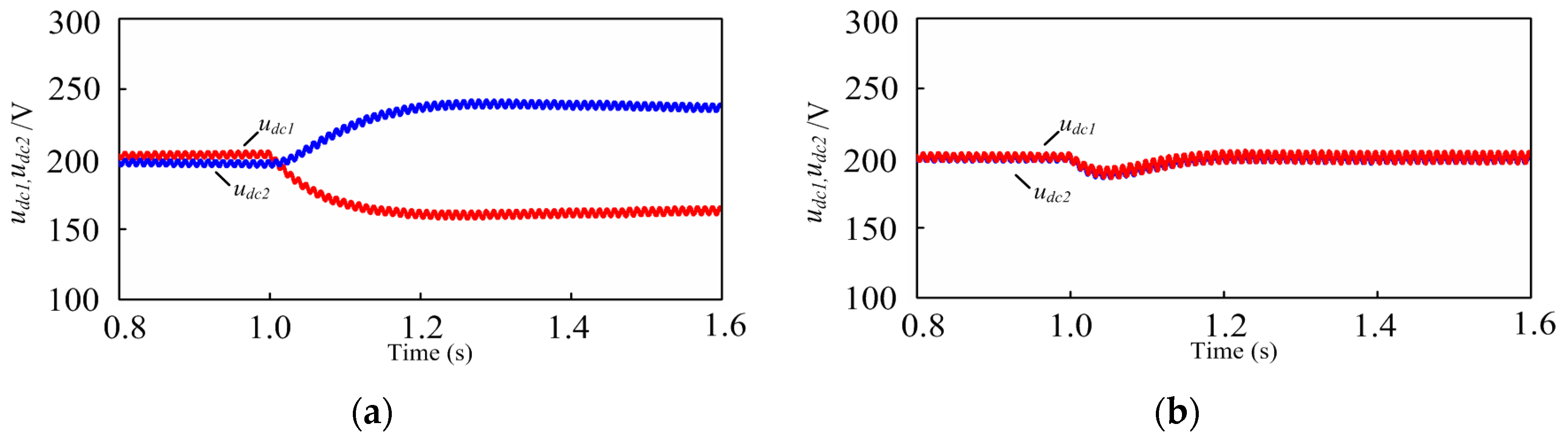

3.2. Power-Based Voltage Balance Control Simulation

4. Experimental Results

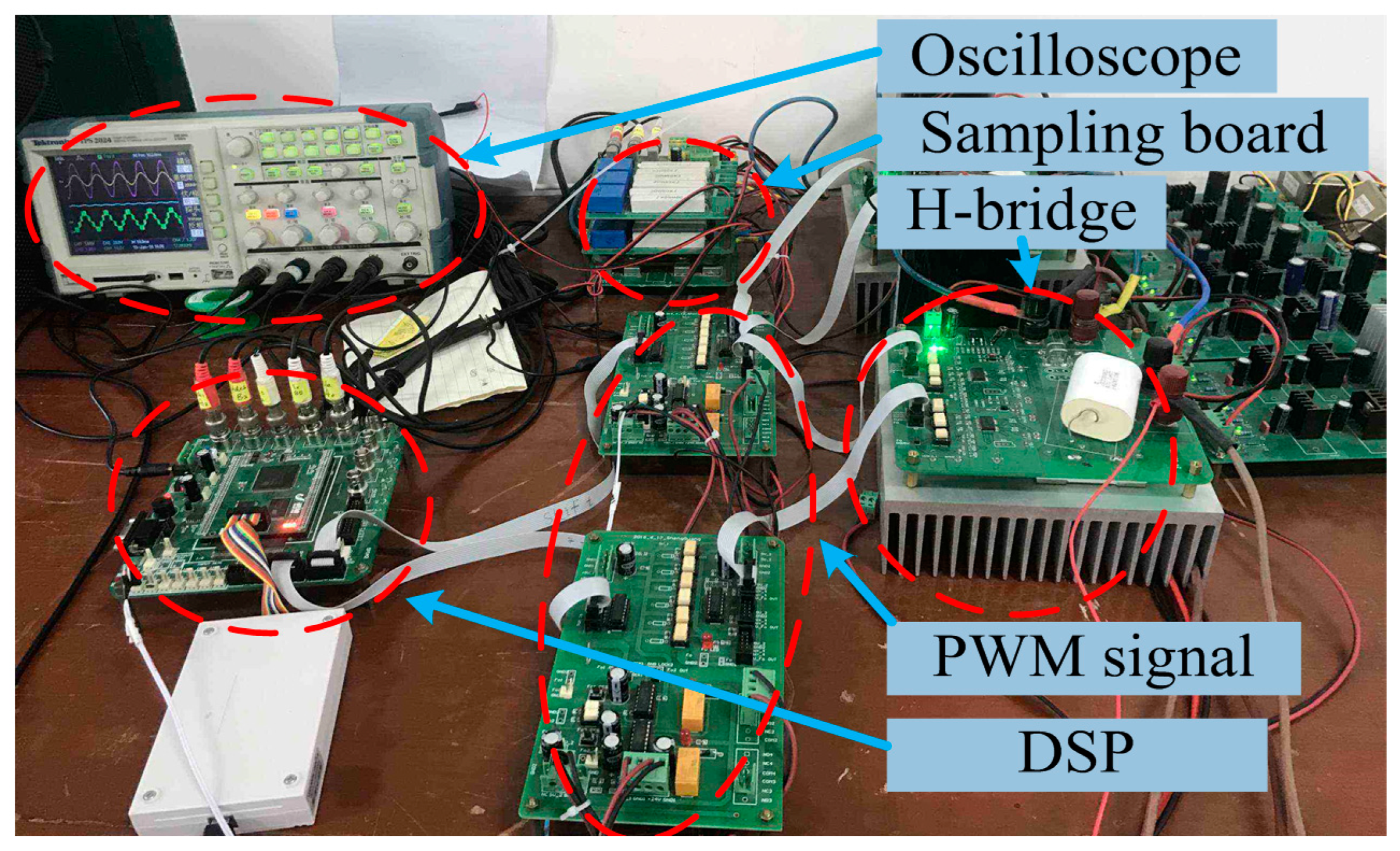

4.1. Experimental Prototype

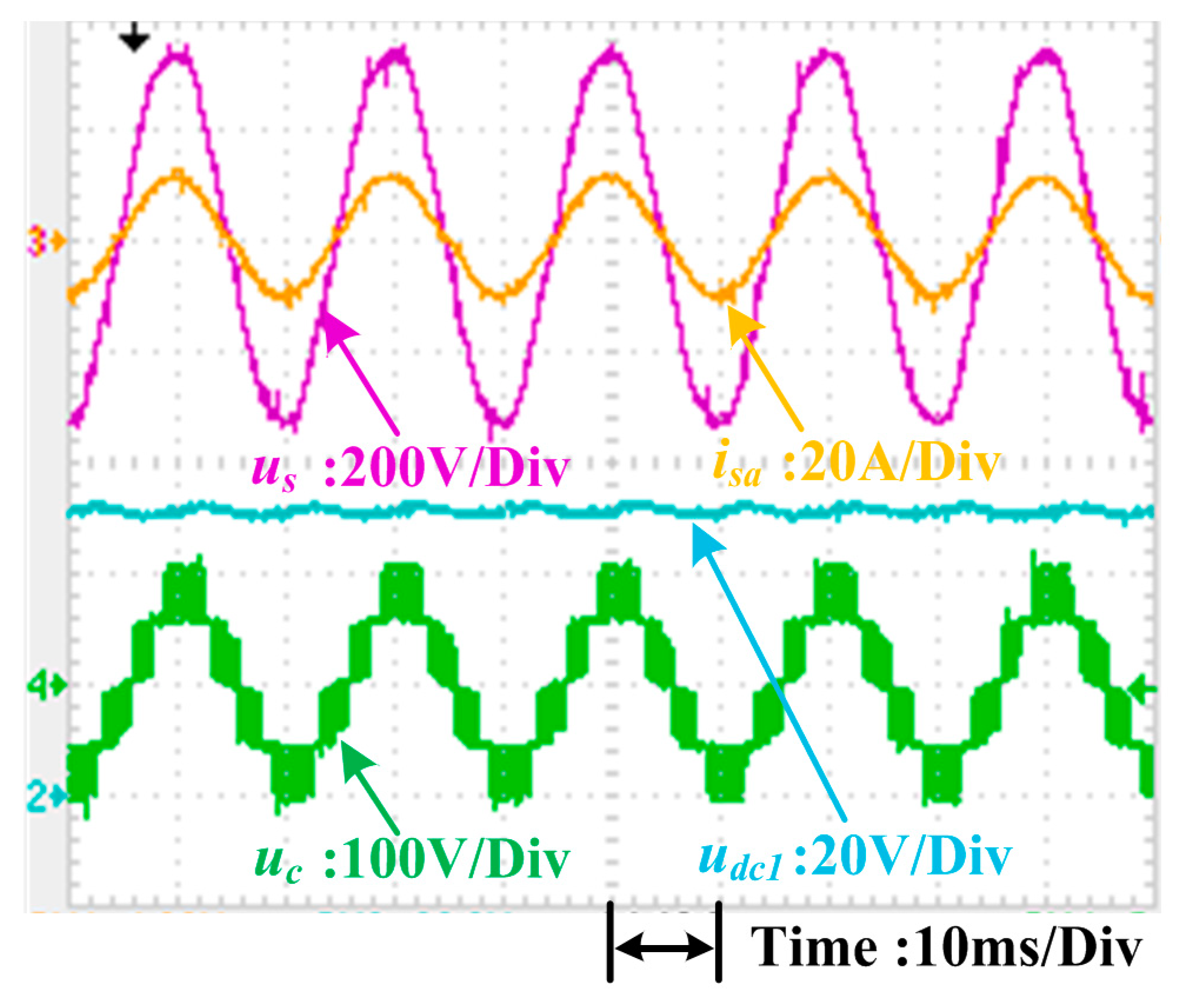

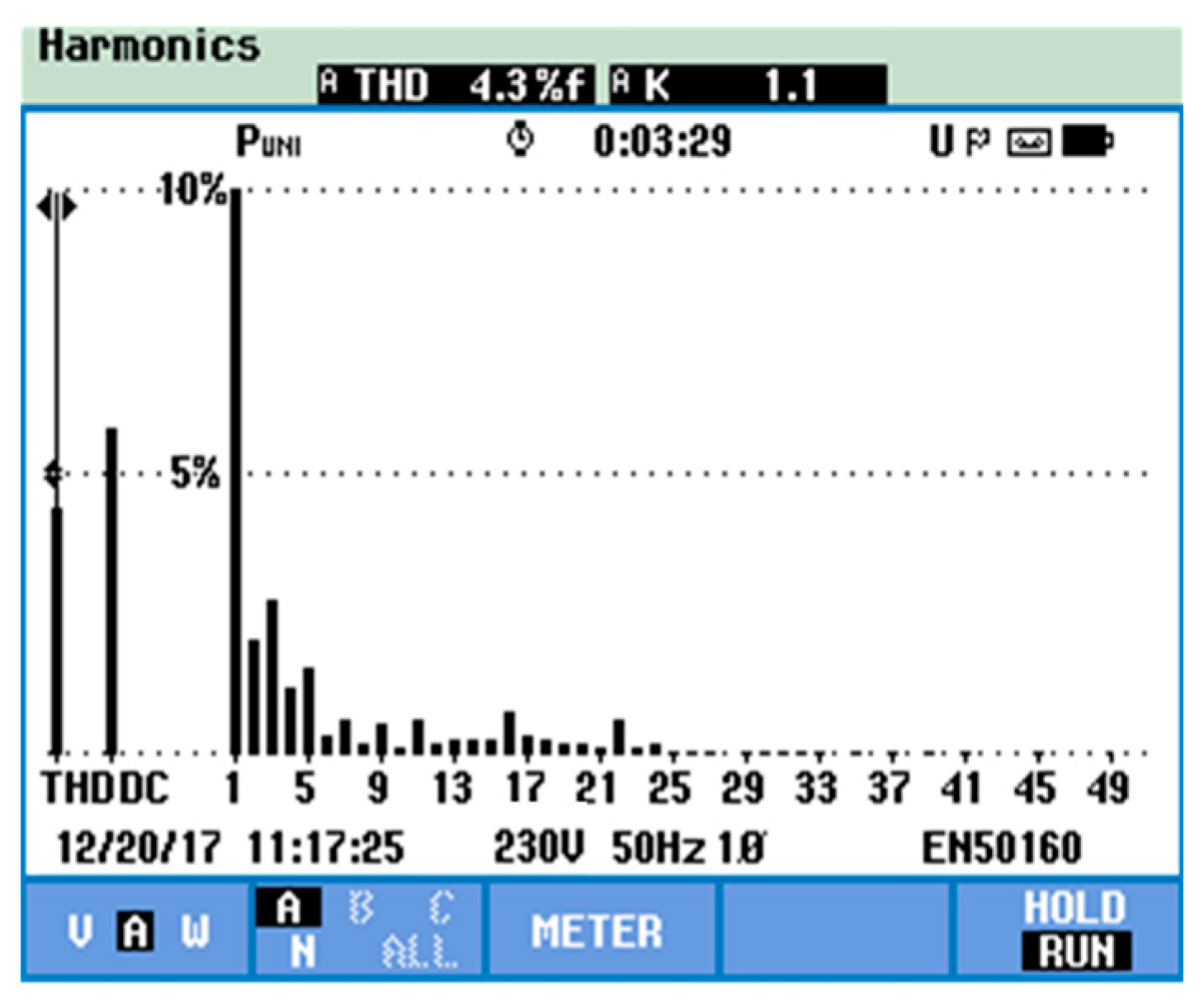

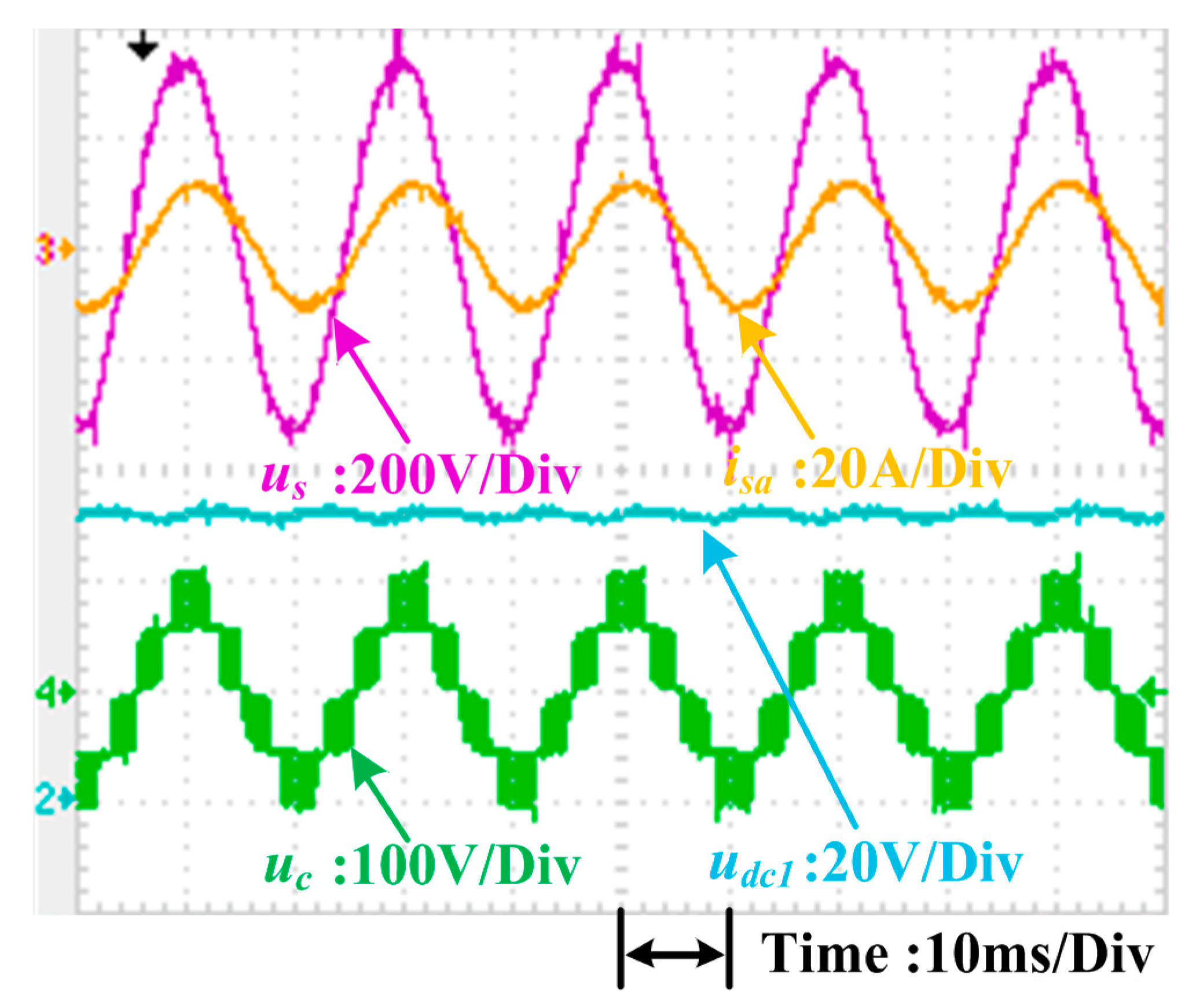

4.2. Steady State

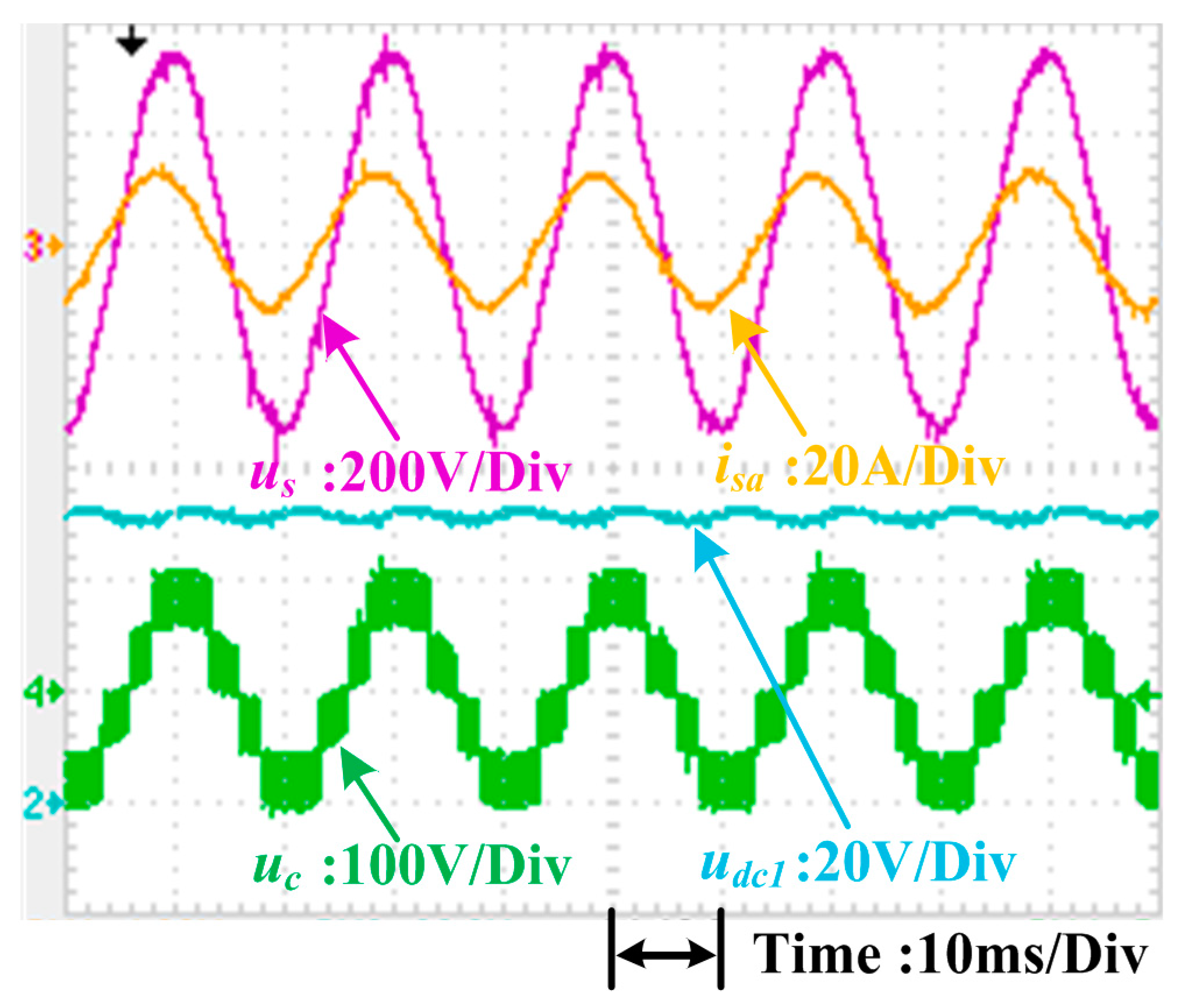

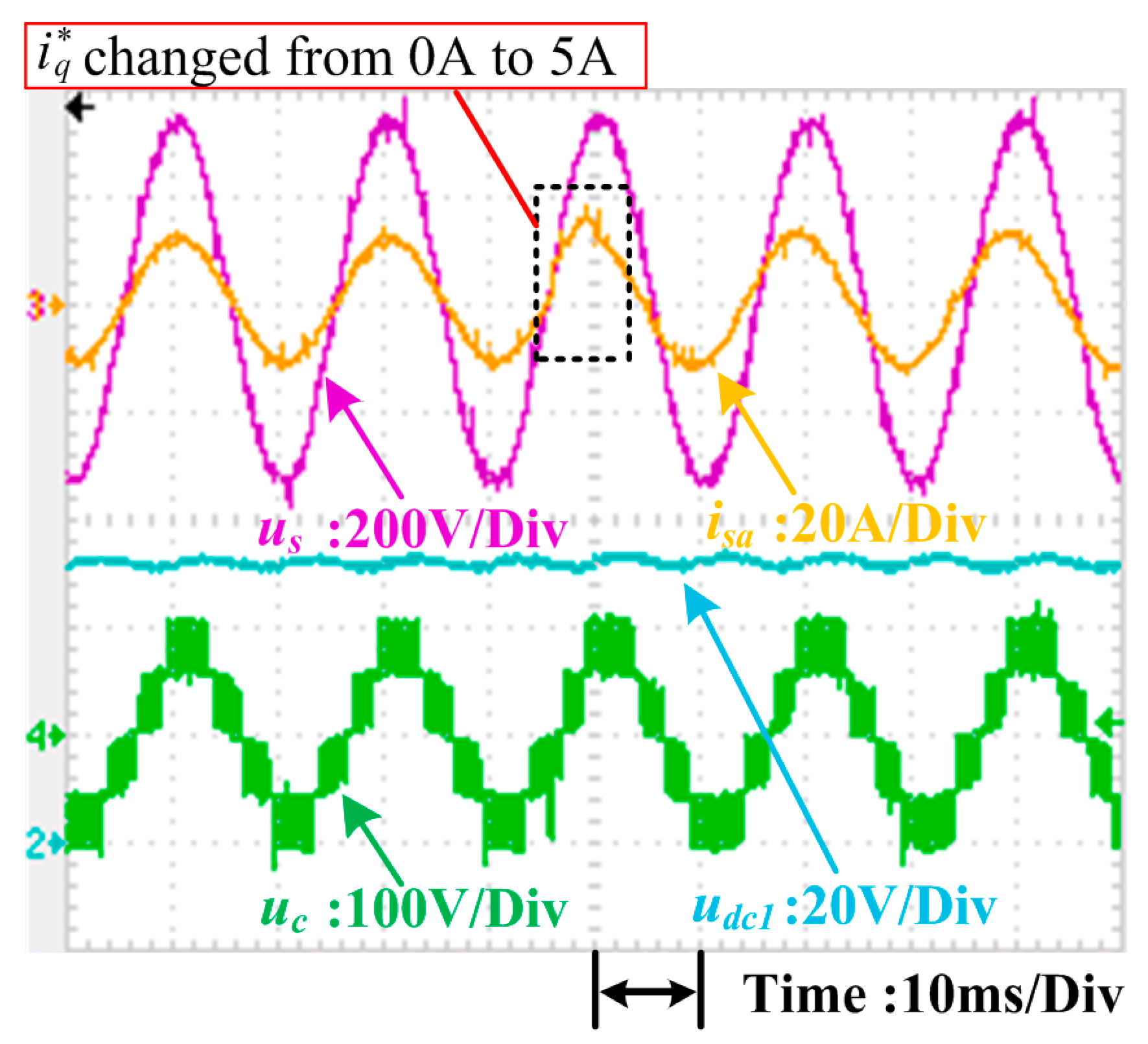

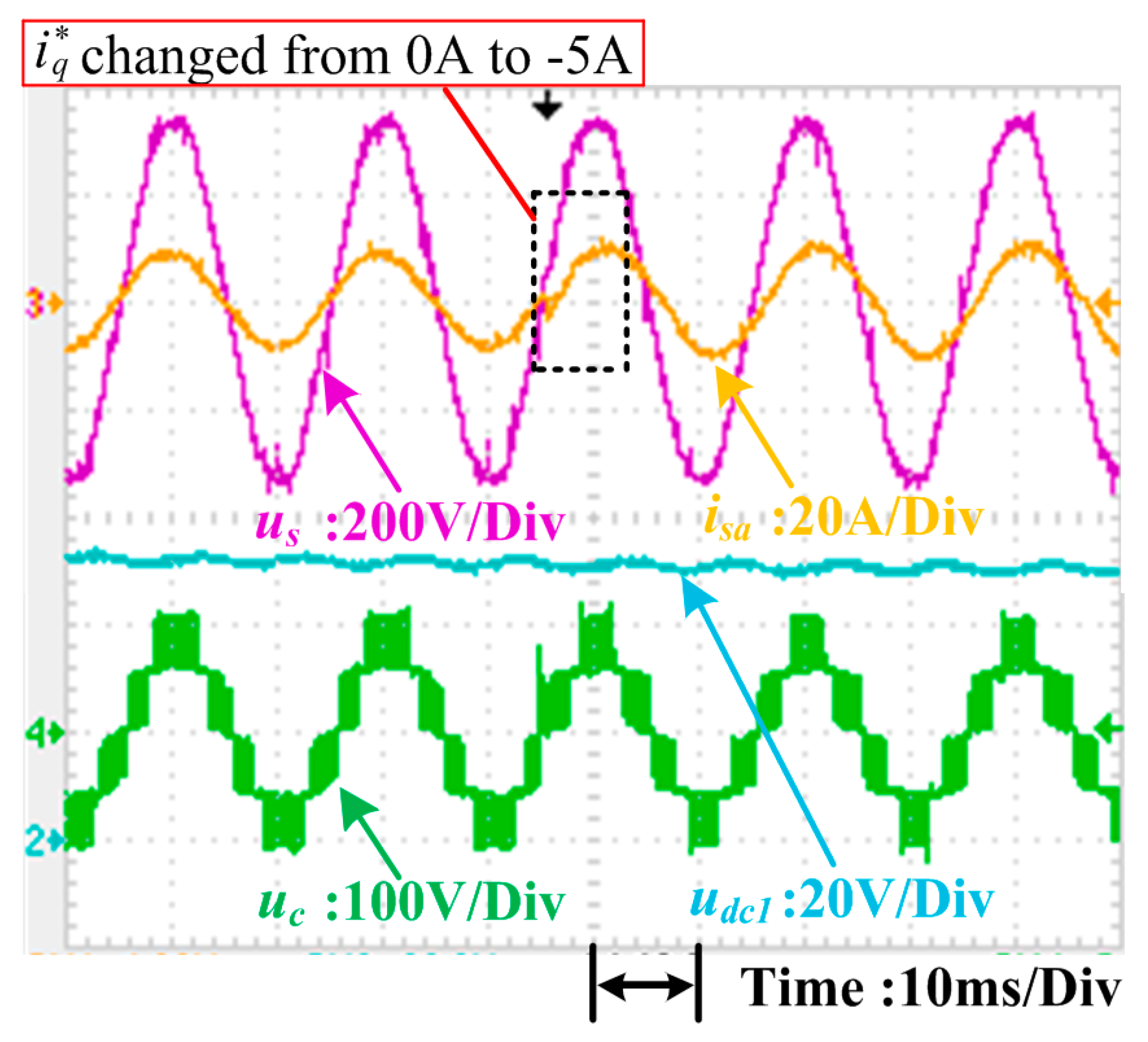

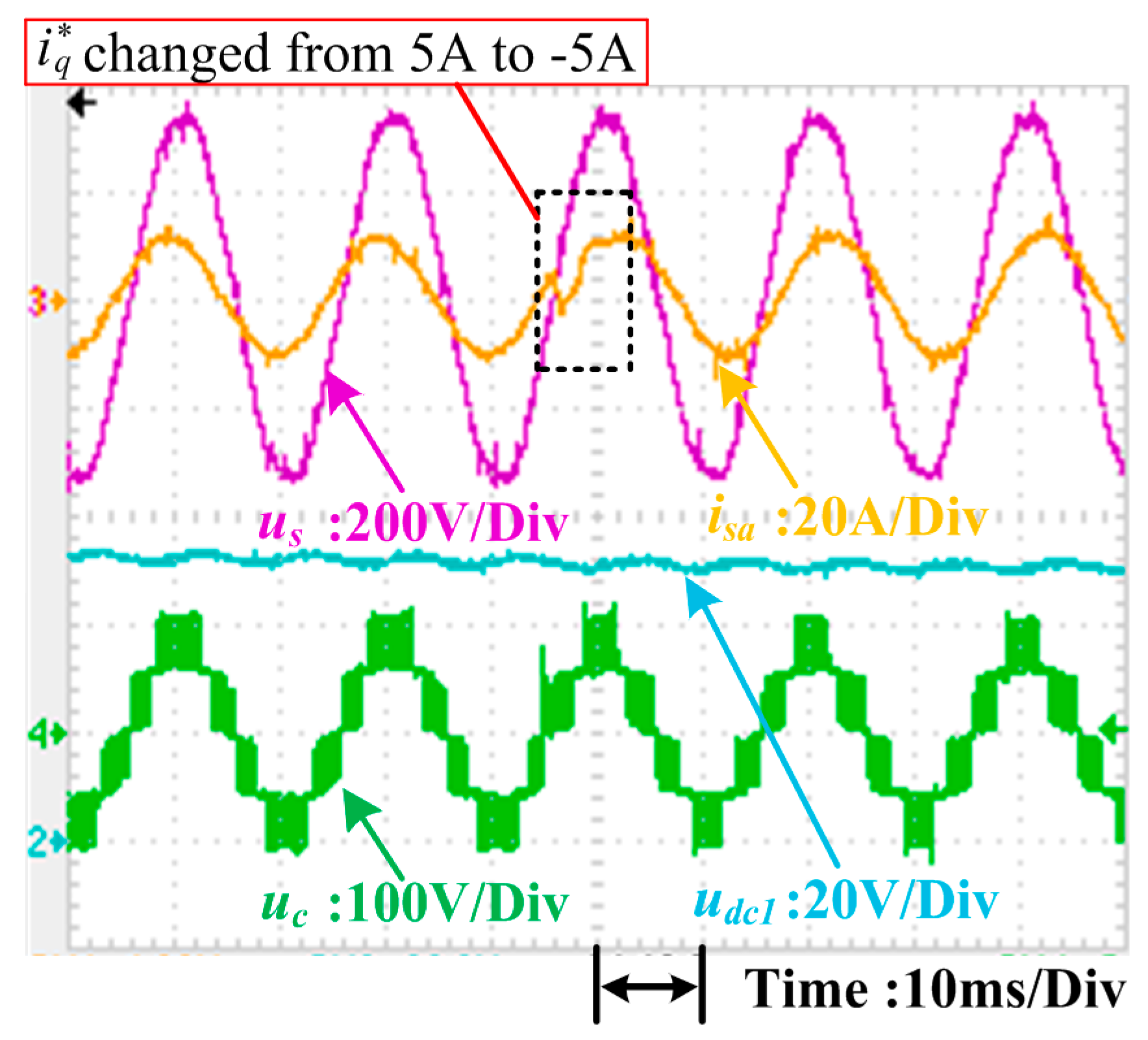

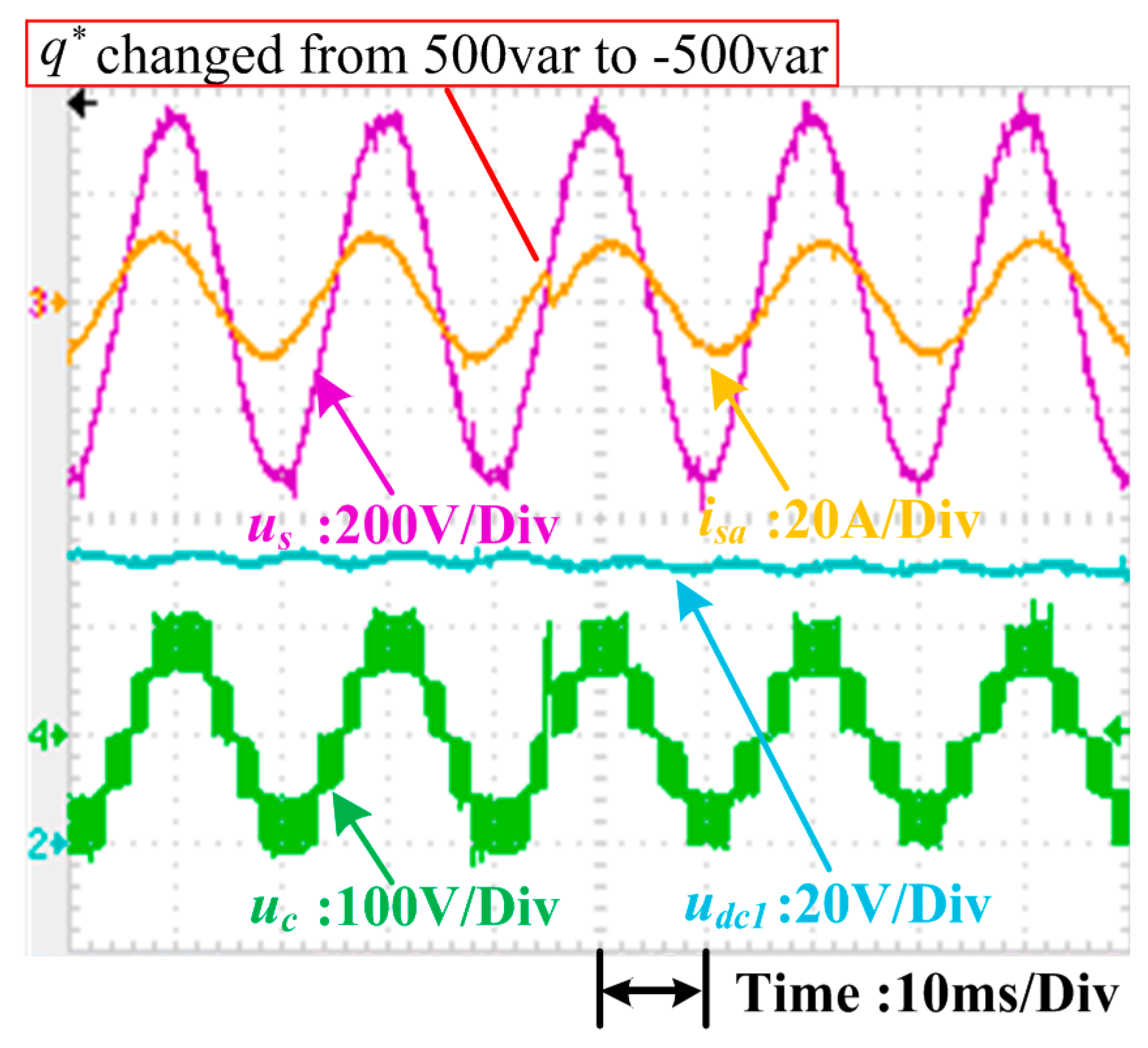

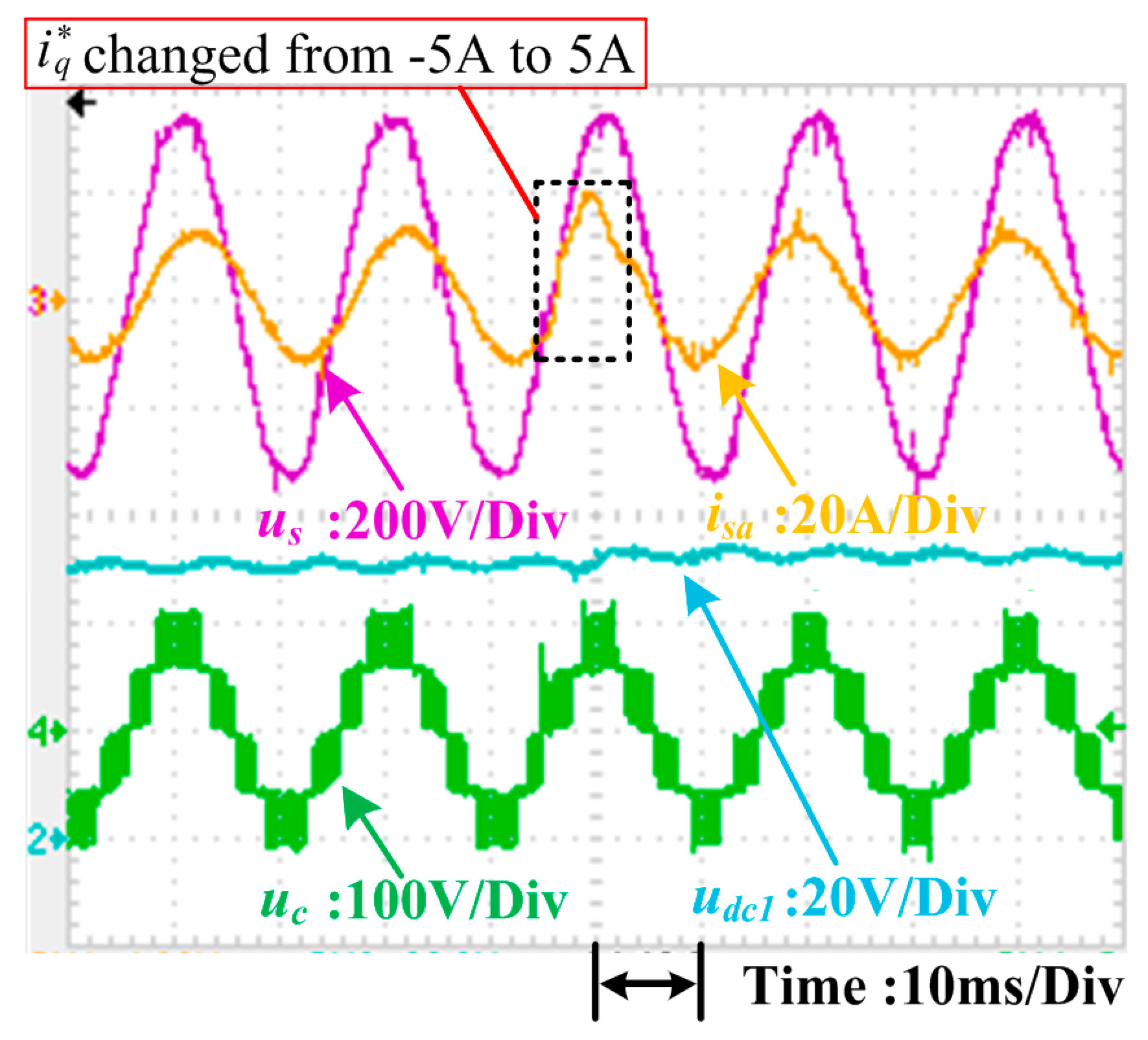

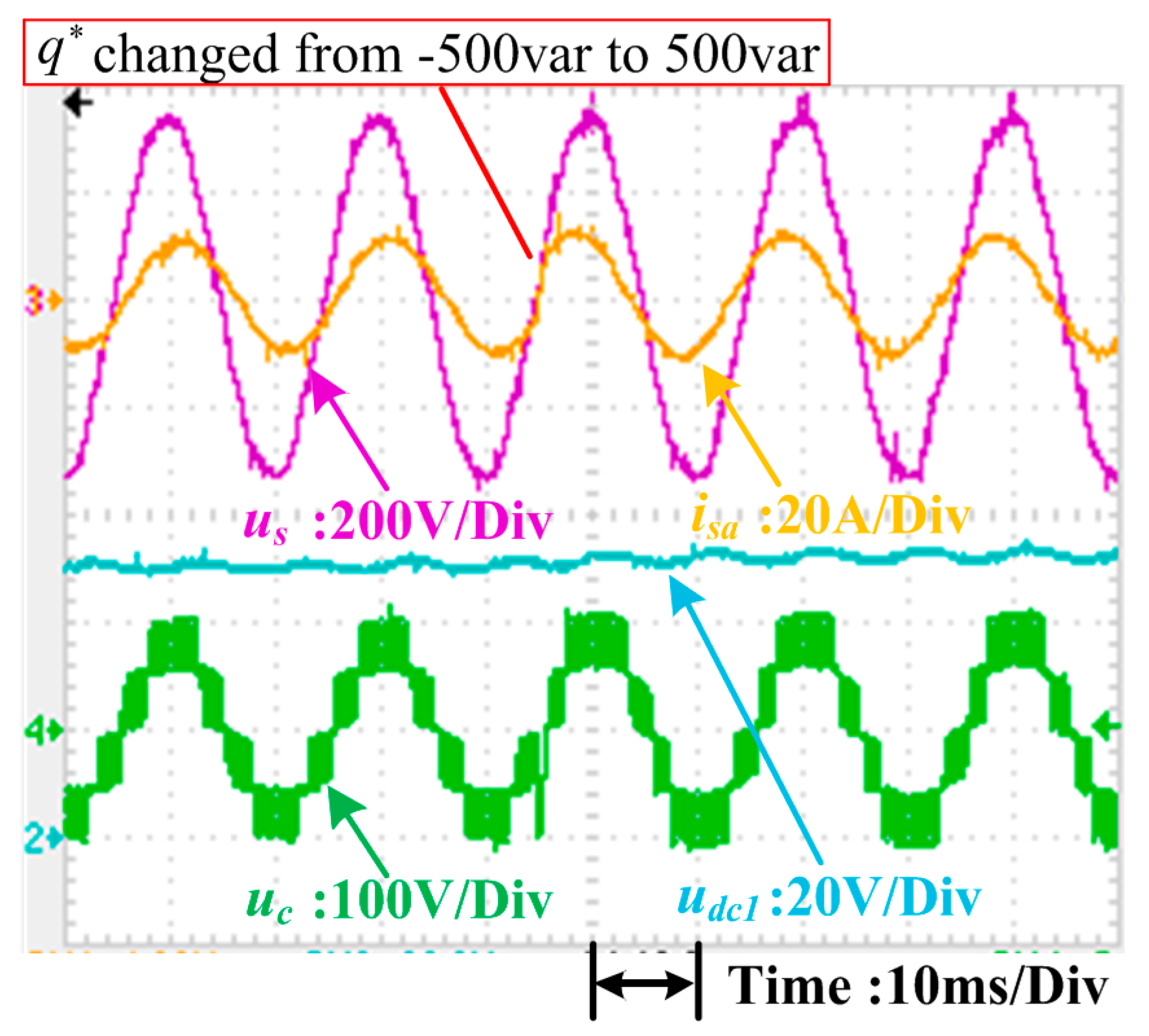

4.3. Dynamic Response Compared with dq Control

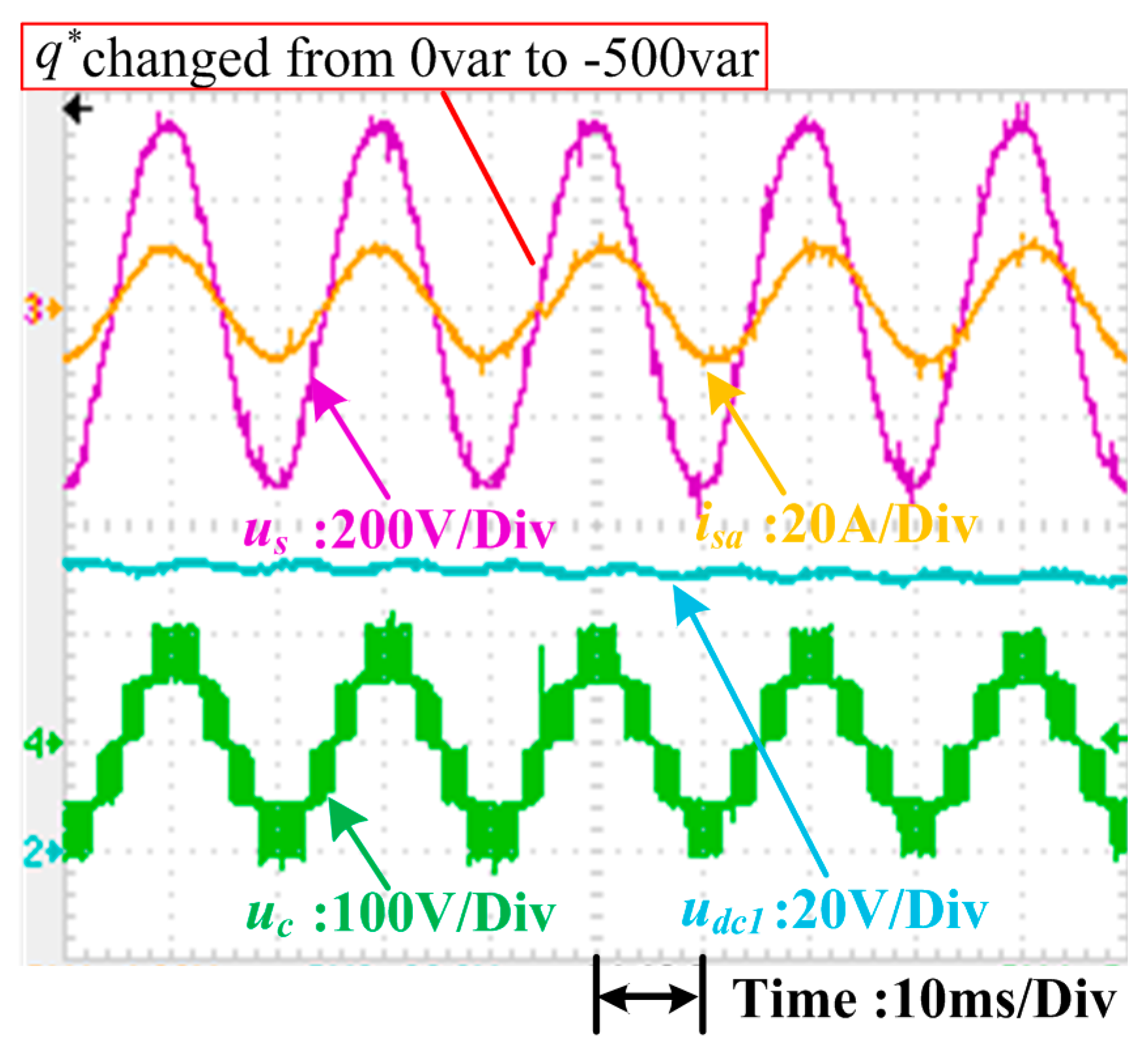

4.4. Voltage Balance Control

5. Discussion

6. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

Nomenclature

| CHB | Cascaded H-bridge |

| PWM | Pulse Width Modulation |

| DPC | Direct Power Control |

| DCC | Direct Current Control |

| P-DPC | Predictive DPC |

| PLL | Phase-Locked Loop |

| DSP | Digital Signal Processor |

| MPC | Model-Predictive Control |

| SOGI | Second-Order Generalized Integrator |

| PI | Proportional-Integral |

| PR | Proportional-plus-Resonant |

| CPS-PWM | Carrier, Phase-Shifted PWM |

| THD | Total Harmonic Distortion |

References

- Noman, A.M.; Al-Shamma’a, A.A.; Addoweesh, K.E.; Alabduljabbar, A.A.; Alolah, A.I. Cascaded Multilevel Inverter Topology Based on Cascaded H-Bridge Multilevel Inverter. Energies 2018, 11, 895. [Google Scholar] [CrossRef]

- Aquila, A.D.; Liserre, M.; Monopoli, V.G.; Rotondo, P. Overview of PI-based solutions for the control of DC buses of a single-phase H-bridge multilevel active rectifier. IEEE Trans. Ind. Appl. 2008, 44, 857–866. [Google Scholar] [CrossRef]

- Yu, Y.; Konstantinou, G.; Townsend, C.D.; Agelidis, V.G. Comparison of zero-sequence injection methods in cascaded H-bridge multilevel converters for large-scale photovoltaic integration. IET Renew. Power Gener. 2017, 11, 603–613. [Google Scholar] [CrossRef]

- Wang, L.; Zhang, D.; Wang, Y.; Wu, B.; Athab, H.S. Power and voltage balance control of a novel three-phase solid-state transformer using multilevel cascaded H-bridge inverters for microgrid applications. IEEE Trans. Power Electron. 2016, 31, 3289–3310. [Google Scholar] [CrossRef]

- Yang, Z.; Sun, J.; Li, S.; Huang, M.; Zha, X.; Tang, Y. An adaptive carrier frequency optimization method for harmonic energy unbalance minimization in a cascaded H-bridge-based active power filter. IEEE Trans. Power Electron. 2018, 33, 1024–1037. [Google Scholar] [CrossRef]

- Song, W.; Ma, J.; Zhou, L.; Feng, X. Deadbeat predictive power control of single-phase three-level neutral-point-clamped converters using space-vector modulation for electric railway traction. IEEE Trans. Power Electron. 2016, 31, 721–732. [Google Scholar] [CrossRef]

- Ohnishi, T. Three PWM converter/inverter by means of instantaneous active and reactive power control. In Proceedings of the International Conference on Industrial Electronics, Control and Instrumentation. (IECON 1991), Kobe, Japan, 28 October–1 November 1991; pp. 819–824. [Google Scholar]

- Wang, X.; Sun, D. Three-vector-based low-complexity model predictive direct power control strategy for doubly fed induction generators. IEEE Trans. Power Electron. 2017, 32, 773–782. [Google Scholar] [CrossRef]

- Kim, I.; Chan, R.; Kwak, S. A voltage level based predictive direct power control for modular multilevel converter. IEEE Trans. Power Appl. 2017, 11, 784–792. [Google Scholar]

- Cheng, C.; Nian, H.; Wang, X.; Sun, D. Dead-beat predictive direct power control of voltage source inverters with optimised switching patterns. IET. Power Electron. 2017, 10, 1438–1451. [Google Scholar] [CrossRef]

- Ma, H.; Xie, Y.; Shi, Z. Improved direct power control for Vienna-type rectifiers based on sliding mode control. IET. Power Electron. 2016, 9, 427–434. [Google Scholar] [CrossRef]

- Ma, J.; Song, W.; Wang, S.; Feng, X. Model predictive direct power control for single phase three-level rectifier at low switching frequency. IEEE Trans. Power Electron. 2018, 33, 1050–1062. [Google Scholar] [CrossRef]

- Behrouzian, E.; Bongiorno, M. Investigation of negative-sequence injection capability of cascaded H-bridge converters in star and delta configuration. IEEE Trans. Power Electron. 2017, 32, 1675–1683. [Google Scholar] [CrossRef]

- Adam, G.P.; Abdelsalam, I.A.; Ahmed, K.H.; Williams, B.W. Hybrid multilevel converter with cascaded H-bridge cells for HVDC applications: Operating principle and scalability. IEEE Trans. Power Electron. 2015, 30, 65–77. [Google Scholar] [CrossRef]

- Wang, X.; He, Z.; Yang, J. Electric Vehicle Fast-Charging Station Unified Modeling and Stability Analysis in the dq Frame. Energies 2018, 11, 1195. [Google Scholar] [CrossRef]

- Liu, J.; Liu, Z. Harmonic Analyzing of the Double PWM Converter in DFIG Based on Mathematical Model. Energies 2017, 10, 2087. [Google Scholar] [CrossRef]

- Gu, Y.; Wang, Y.; Xiang, X.; Li, W.; He, X. Improved virtual vector control of single-phase inverter based on unified model. IEEE Trans. Energy Convers. 2014, 29, 611–618. [Google Scholar] [CrossRef]

- Zheng, X.; Xiao, L.; Wang, Z.; Lei, Y.; Wang, C. Control strategy without phase-locked loop based on coordinate transformation for three-phase AC/DC converter. IET. Power Electron. 2015, 8, 1701–1709. [Google Scholar] [CrossRef]

- Li, Y.; Yang, J.; Wang, H.; Ge, W.; Ma, Y. A Hybrid Filtering Technique-Based PLL Targeting Fast and Robust Tracking Performance under Distorted Grid Conditions. Energies 2018, 11, 973. [Google Scholar] [CrossRef]

- Hamed, H.A.; Abdou, A.F.; Bayoumi, E.; EL-Kholy, E.E. Effective design and implementation of GSS-PLL under voltage dip and phase interruption. IET. Power Electron. 2018, 11, 1018–1028. [Google Scholar] [CrossRef]

- Xiao, F.; Dong, L.; Li, L.; Liao, X. A frequency-fixed SOGI-based PLL for single-phase grid-connected converters. IEEE Trans. Power Electron. 2017, 21, 1713–1719. [Google Scholar] [CrossRef]

- Sahoo, S.; Prakash, S.; Mishra, S. Power quality improvement of grid-connected DC microgrids using repetitive learning-based PLL under abnormal grid conditions. IEEE Trans. Ind. Appl. 2018, 54, 82–90. [Google Scholar] [CrossRef]

- Yang, D.; Wu, N.; Yin, L.; Lu, Z. Natural frame control of single-phase cascaded H-bridge multilevel converter based on fictive-phases construction. IEEE Trans. Ind. Electron. 2018, 54, 3848–3857. [Google Scholar] [CrossRef]

- Chan, R.; Kwak, S. Improved Finite-Control-Set Model Predictive Control for Cascaded H-Bridge Inverters. Energies. 2018, 11, 355. [Google Scholar] [CrossRef]

- Zhang, Y.; Wu, X.; Yuan, X.; Wang, Y.; Dai, P. Fast model predictive control for multilevel cascaded H-bridge STATCOM with polynomial computation time. IEEE Trans. Ind. Electron. 2016, 63, 5231–5243. [Google Scholar] [CrossRef]

- Qi, C.; Chen, X.; Tu, P.; Wang, P. Deadbeat control for a single-phase cascaded H-bridge rectifier with voltage balancing modulation. IET Power Electron. 2018, 11, 610–617. [Google Scholar] [CrossRef]

- Song, W.; Deng, Z.; Wang, S.; Feng, X. A Simple Model Predictive Power Control Strategy for Single-Phase PWM Converters With Modulation Function Optimization. IEEE Trans. Power Electron. 2016, 31, 5279–5289. [Google Scholar] [CrossRef]

- Blahnik, V.; Kosan, T.; Peroutka, Z.; Talla, J. Control of a single-phase cascaded H-bridge active rectifier under unbalanced load. IEEE Trans. Power Electron. 2018, 33, 5519–5527. [Google Scholar] [CrossRef]

- Somkun, S.; Chunkag, V. Unified unbalanced synchronous reference frame current control for single-phase grid-connected voltage source converters. IEEE Trans. Ind. Electron. 2016, 63, 5425–5436. [Google Scholar] [CrossRef]

- Sha, D.; Xu, G.; Xu, Y. Utility direct interfaced charger/discharger employing unified voltage balance control for cascaded H-bridge units and decentralized control for CF-DAB modules. IEEE Trans. Ind. Electron. 2017, 64, 7831–7841. [Google Scholar] [CrossRef]

- Ebrahimi, M.; Khajehoddin, S.; Ghartemani, M.K. Fast and robust single-phase dq current controller for smart inverter applications. IEEE Trans. Power Electron. 2016, 31, 3968–3976. [Google Scholar] [CrossRef]

- Shi, J.; Gou, W.; Yuan, H.; Zhao, T.; Huang, A.Q. Research on voltage and power balance control for cascaded modular solid-state transformer. IEEE Trans. Power Electron. 2011, 26, 1154–1166. [Google Scholar] [CrossRef]

- Farivar, G.; Townsend, C.D.; Hredzak, B.; Pou, J.; Agelidis, V.G. Low-capacitance cascaded H-bridge multilevel STATCOM. IEEE Trans. Power Electron. 2016, 32, 1744–1754. [Google Scholar] [CrossRef]

- Qi, C.; Chen, X.; Tu, P.; Wang, P. Cell-by-cell-based finite-control- set model predictive control for a single-phase cascaded H-bridge rectifier. IEEE Trans. Power Electron. 2018, 33, 1654–1665. [Google Scholar] [CrossRef]

- Moeini, A.; Wang, S. A DC Link Sensor-Less Voltage Balancing Technique for Cascaded H-Bridge Multilevel Converters with Asymmetric Selective Harmonic Current Mitigation-PWM. IEEE Trans. Power Electron. 2018, 33, 7571–7581. [Google Scholar] [CrossRef]

- Farivar, G.; Hredzak, B.; Agelidis, V.G. Decoupled control system for cascaded H-bridge multilevel converter based STATCOM. IEEE Trans. Ind. Electron. 2016, 63, 322–331. [Google Scholar] [CrossRef]

- Zhao, T.; Wang, G.; Bhattacharya, S.; Huang, A.Q. Voltage and power balance control for a cascaded H-bridge converter-based solid-state transformer. IEEE Trans. Power Electron. 2013, 28, 1523–1532. [Google Scholar] [CrossRef]

- Chen, H.; Wu, P.; Lee, C.; Wang, C.; Yang, C.; Cheng, P. A flexible DC voltage balancing control based on the power flow management for star-connected cascaded H-bridge converter. IEEE Trans. Ind. Appl. 2016, 2, 4946–4954. [Google Scholar] [CrossRef]

- Moeini, A.; Wang, S. The state of charge balancing techniques for electrical vehicle charging stations with cascaded H-bridge multilevel converters. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition—APEC, San Antonio, TX, USA, 4–8 March 2018; pp. 637–644. [Google Scholar]

- Yang, Y.; Zhou, K.; Wang, H.; Blaabjerg, F.; Wang, D.; Zhang, B. Frequency adaptive selective harmonic control for grid-connected inverters. IEEE Trans. Power Electron. 2015, 30, 3912–3924. [Google Scholar] [CrossRef]

| Parameter | Symbol | Simulation Value |

|---|---|---|

| Grid voltage rms value | us | 220 V |

| Grid frequency | fg | 50 Hz |

| Input inductance | L | 3.0 mH |

| dc-link total voltage | Udc | 400 V |

| dc-link capacitance | C1, C2 | 4700 μF |

| dc-link load resistance | R1, R2 | 10 Ω, 15 Ω |

| Switching frequency | fsw | 10 kHz |

| Inner current loop control parameters | P, R, wc | 0.5, 100, 6.28 |

| Outer power loop control parameters | P, I | 0.1, 8 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, D.; Yin, L.; Xu, S.; Wu, N. Power and Voltage Control for Single-Phase Cascaded H-Bridge Multilevel Converters under Unbalanced Loads. Energies 2018, 11, 2435. https://doi.org/10.3390/en11092435

Yang D, Yin L, Xu S, Wu N. Power and Voltage Control for Single-Phase Cascaded H-Bridge Multilevel Converters under Unbalanced Loads. Energies. 2018; 11(9):2435. https://doi.org/10.3390/en11092435

Chicago/Turabian StyleYang, Daliang, Li Yin, Shengguang Xu, and Ning Wu. 2018. "Power and Voltage Control for Single-Phase Cascaded H-Bridge Multilevel Converters under Unbalanced Loads" Energies 11, no. 9: 2435. https://doi.org/10.3390/en11092435

APA StyleYang, D., Yin, L., Xu, S., & Wu, N. (2018). Power and Voltage Control for Single-Phase Cascaded H-Bridge Multilevel Converters under Unbalanced Loads. Energies, 11(9), 2435. https://doi.org/10.3390/en11092435