1. Introduction

In recent years, high voltage direct current (HVDC) technology has attracted growing attention for power transmission between networks. The first commercial HVDC system was installed in Sweden in 1954; a total transmission line capacity of 191,000 MW is currently installed around the world across 172 HVDC system projects [

1]. Although voltage-source converters (VSCs) have been used in HVDC systems, line-commutated converter (LCC) schemes are also advantageous because they are a mature technology and are available at higher capacities for HVDC systems than current VSCs [

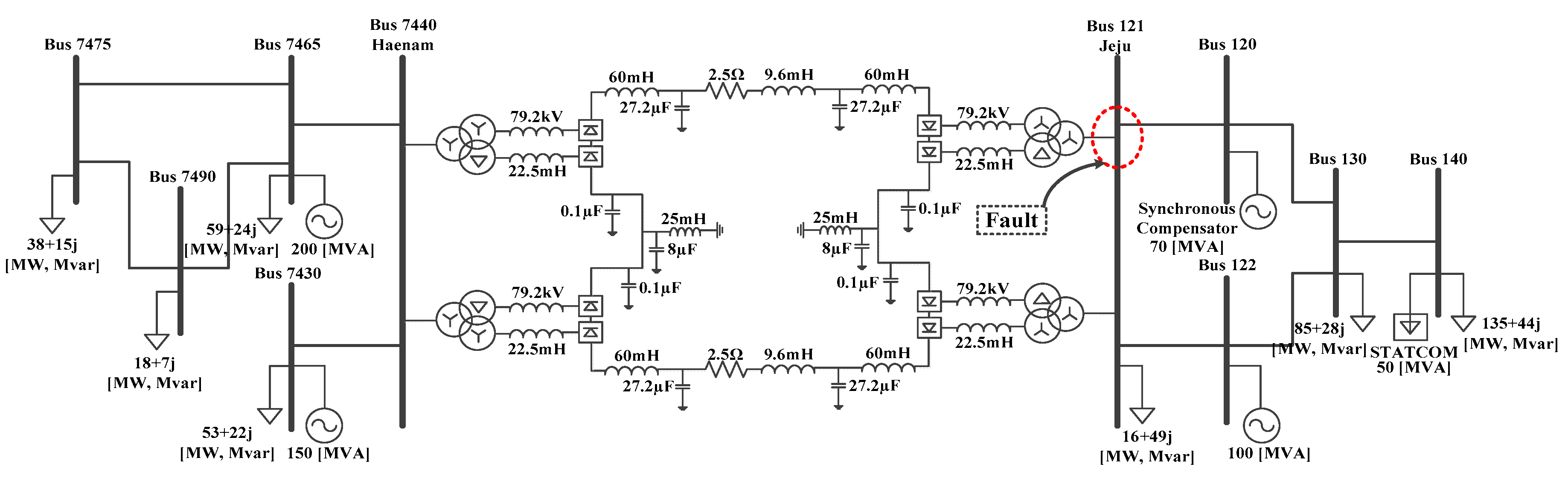

2]. Based on these advantages, the 180-kV, 300-MW LCC–HVDC system installed by Korea Electric Power Corporation (KEPCO) has been used to convey relatively cheap electrical power from the Haenam substation on the Korean mainland to the Jeju substation on Jeju Island, via 100-km undersea cables [

3].

Various models of HVDC systems have been developed to estimate operating conditions and analyze the transient and steady-state stabilities of LCC–HVDC systems and connected AC networks [

4,

5,

6,

7]. For example, in [

4], the DC voltages and currents of LCC–HVDC systems were calculated in the common

dq-reference frame of the associated AC network. Linearized models of LCC–HVDC systems were developed in [

5,

6] to analyze the dynamic power grid stability and the small-signal stability of multi-feed HVDC systems, respectively. In [

7], the conseil international des grands reseaux electriques (CIGRE) benchmark HVDC system model was adopted to simulate a VSC-integrated LCC–HVDC system to connect an offshore wind farm to a mainland network. In [

8,

9], the operation of LCC–HVDC systems was investigated during commutation failure using the CIGRE benchmark model with respect to variations in the DC-line voltage and the valve current, respectively. However, the HVDC system models discussed so far need additional modifications to incorporate the operating characteristics of real HVDC systems because the parameters (e.g., rated power, voltage, etc.), controllers, and operations of some real HVDC systems often differ from those of the CIGRE benchmark. For example, the HVDC system in the Taiwan power grid was modeled in [

10], where the CIGRE benchmark model was extended to include an extinction angle controller at the rectifier side, a DC current controller at the inverter side, and a voltage-dependent current order limit (VDCOL) function. The Anshun–Zhaoqing HVDC system model developed in [

11] was not based on the CIGRE benchmark model, as the challenge of integrating it with the system operating characteristics was too difficult. Furthermore, the DC-lines in the above-mentioned system models were represented using a simple T-equivalent circuit, which has a limited accuracy for calculating variations in DC-line voltage and current. This inhibits direct application of the models and analyses to real systems, such as the Jeju–Haenam HVDC system (i.e., the KEPCO benchmark model).

Meanwhile, LCC–HVDC systems are susceptible to commutation failure on a weak AC grid or under AC line-to-ground fault conditions, which will interrupt the transmitted power and stress the converter equipment [

12]. Therefore, there have been many studies on commutation failure recognition caused by the AC faults [

13] and commutation failure mitigation by using the modified controllers [

14,

15] or by adding additional components/power electronic devices [

16,

17]. In [

13], the method to calculate the maximum-allowable balanced voltage drop at an inverter AC busbar was proposed to determine the onset of commutation failures. The objectives of the modified controllers were either to reduce the probability of commutation failure or to increase the recovery speed of the DC system after commutation failure. One of the common methods is to advance the firing angle at the inverter side immediately after the detection of AC voltage disturbance in order to give a larger commutation margin [

14]. Another method is to reduce the commutated DC current by decreasing the current order at the rectifier side upon detection of AC voltage disturbance [

15]. Among the methods with additions of components/power electronic devices, capacitor-commutated converters (CCC) have been considered the most popular, as they can operate at a better power factor and have a lower probability of commutation failures [

16]. In addition, the improved line-commutated converter with thyristor-based full-bridge module (TFBM), which is embedded in the converter valve, was proposed to enhance the commutation failure immunity in [

17]. However, these papers discussed so far were concerned with the recognition or mitigation of commutation failure caused by AC line-to-ground fault. In the studies, the maximum DC current and voltage of the HVDC system have not been considered when commutation failures occur due to the AC line-to-ground fault. The maximum fault current and voltage are the primary concern for analyzing the transient stabilities of the AC network and HVDC system; for example, to determine the setting parameters of protection relays and the capacities of DC transmission lines and AC/DC converter valves [

18,

19,

20].

In addition, several digital simulators have been adopted for simulation studies on LCC–HVDC systems. In particular, power systems computer aided design/electromagnetic transients including DC (PSCAD/EMTDC, or simply PSCAD) and

Matlab/Simulink have been used to elaborate the control schemes of CIGRE HVDC benchmark system models [

21,

22,

23]. However, the AC network models used in these studies were simplified by using voltage sources and equivalent impedances, primarily because of the models’ limited ability to model complex, large-scale AC networks. Therefore, real power grids—such as those on the Korean mainland and Jeju Island connected via the Jeju–Haenam HVDC system—are difficult to model using these simulators; i.e., real-time analysis of the HVDC systems will become computationally onerous.

The power system simulator for engineering (PSS/E) is a powerful time-domain simulator for the analysis of AC grids and associated controllers. It provides transmission planning and operation engineers with a broad range of methods for the design and operation of reliable networks. Many companies have therefore used PSS/E to analyze large-scale power grids. Moreover, PSS/E enables use of real AC grid data to describe interactions between an HVDC system and the AC power grid. There are also a few useful examples of HVDC models such as CDC4T, CDC6T, and CDC7T in PSS/E [

24]. However, these models require large sets of parameters, which are typically difficult to obtain from real HVDC systems because of modeling discrepancies and confidentiality issues imposed by device manufacturers. Power grid operators and utility companies therefore require new PSS/E models for real-time analysis of practical HVDC systems; in designing such a model, we focused on the Jeju–Haenam HVDC system in Korea.

Based on the above observations, this paper describes a new modeling method for an HVDC system in the PSS/E simulation environment. The proposed method consists of three modules for (a) equation conversion; (b) control-mode selection; and (c) DC-line modeling, which are parameterized based on the unique characteristics of the Jeju–Haenam HVDC system and the Korea–Jeju power grid as a particular example. The results of the proposed model are compared with measured data for the actual HVDC system to demonstrate the effectiveness of the proposed modeling method. The main contributions of this paper are summarized as follows:

The converting equations for abnormal operation, which particularly arise because of commutation failure under the conditions of fault occurrence in the AC transmission network, are developed and integrated into PSS/E to estimate the variations in the DC voltages and currents of the HVDC system.

The HVDC system converters are equipped with feedback controllers. These enable us to easily determine the firing angles and obtain sufficiently accurate characteristic V-I curves, particularly with respect to the VDCOL function. Furthermore, the DC line is modeled using multiple π-sections for accurate estimation of the DC voltages and currents of the HVDC system.

The proposed modeling method provides accurate estimates of the DC voltages and currents arising from AC line-to-ground faults. To the best of our knowledge, this paper is the first demonstration of an HVDC system model developed specifically with a quasi steady state (QSS)-type simulator using actual operating data from a real HVDC system for a single line-to-ground fault. The proposed model is also verified through comparisons with simulation results obtained from the comprehensive HVDC system model, developed using PSCAD, for the three-phase line-to-ground fault.

The proposed method leads to a significant reduction in computational time. This will allow grid operators to perform efficient case studies of LCC-based HVDC systems under a variety of conditions. Furthermore, the proposed method can be implemented in coordination with commercial software, and independently of the built-in subsystems or algorithms for other dynamic power devices. It is easy to adapt the model to reflect the operating characteristics of specific HVDC systems without affecting the built-in functions. Hence, this model has a wide range of potential applications.

Section 2 explains the modeling justifications of the HVDC system in the PSS/E simulation environment.

Section 3 presents the proposed modeling methods for an HVDC system based on the Jeju–Haenam HVDC system.

Section 4 discusses the simulation case study results for both single-phase and three-phase line-to-ground faults at the inverter side.

Section 5 provides our conclusions.

2. Modeling the HVDC System in the PSS/E Simulation Environment

An HVDC system can be modeled with various simulation time-steps depending on simulation tools such as PSCAD,

Matlab/Simulink, and PSS/E. Specifically, PSCAD and

Matlab/Simulink use 50-μs and 1-ms base simulation time-steps, respectively. These simulation tools are appropriate for developing a detailed model of an HVDC system, particularly at the valve- and firing-control levels. However, models of AC power transmission networks interconnected with HVDC systems require simplification. This is because the small time-steps in the simulation tools are inappropriate for dynamic analysis of large-scale transmission networks that include a number of loads, generators, and other components with non-linear operational characteristics. For example, in [

25,

26], valve-control methods for HVDC systems were proposed using these simulation tools; however, the test transmission networks were simply modeled using ideal voltage sources and equivalent Thevenin impedances.

The PSS/E software package is for simulating system phenomena at the fundamental frequency or below. PSS/E is thus appropriate for analyzing HVDC systems with respect to interaction with interconnected transmission networks. Measured data for a real transmission network can also be readily incorporated into PSS/E. Power flow calculation (PFC) is a PSS/E module that solves a set of algebraic equations to estimate the power outputs of generators and power flows in the network for a given load demand. Dynamic simulation (DS) is a module for calculating sets of differential equations, to analyze the electromagnetic transient operation of AC transmission networks [

27]. Because of the relatively large simulation time-steps in PSS/E, HVDC system modeling scopes in PSS/E often include a constant current loop level, voltage-dependent current order limit (VDCOL), and master control. Furthermore, it normally takes only a few seconds to analyze the dynamics of an HVDC system, which is advantageous for both power grid operators and researchers.

In view of these benefits, the CIGRE HVDC benchmark system was recently modeled using PSS/E [

28]. However, the CIGRE benchmark model needs to be modified when evaluating the transient-state operation of a real HVDC system triggered by transmission network events. The rated power and rated DC and AC voltages of a real HVDC system often differ significantly from those in the CIGRE HVDC system; for example, see

Table 1 for the Jeju–Haenam HVDC system in Korea. In addition, the CIGRE benchmark only includes the DC current controller and extinction angle controller at the rectifier and inverter sides, respectively. Therefore, additional controllers are required to control the DC voltage at the rectifier side of the Jeju–Haenam HVDC system. Furthermore, the built-in VDCOL function provided in the CIGRE benchmark model only takes two set points, the pair (

Vdc,

Idc), as input. This is often inconsistent with the operating characteristics of real HVDC systems; for example, the Jeju–Haenam HVDE system takes nine set points. Additionally, although there are sample models for HVDC systems in PSS/E, such as CDC4T, CDC6T, and CDC7T, they require 25, 35, and 79 system parameters, respectively. Furthermore, specific parameters representing the characteristics of an HVDC system must be implemented separately in PSS/E to analyze the transient-state operation of a real HVDC system accurately. For example, the sample models do not have a parameter for the gradual restoration of the DC voltage, as occurs during operation of the Jeju–Haenam HVDC system.

To use the PSS/E software to bridge the divide between academic research and practical applications, we therefore modeled a real HVDC system, the Jeju–Haenam HVDC system as a specific example, while considering fault events in the Jeju AC power grid.

3. Proposed Modeling Method for Improved Transient-State Analysis of HVDC Systems

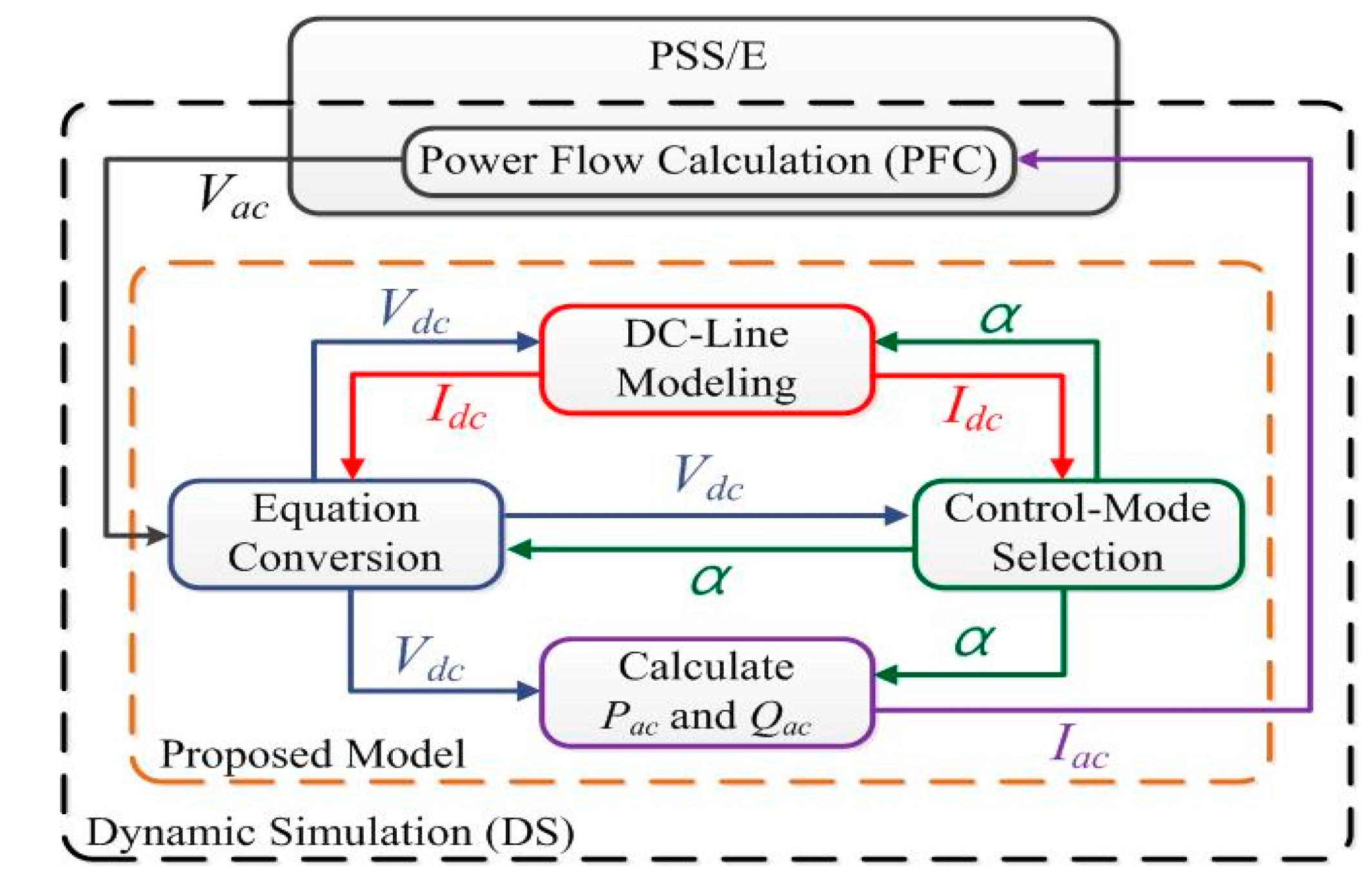

Figure 1 shows a schematic diagram of the proposed modeling method, which includes three modules for (a) equation conversion; (b) control-mode selection; and (c) DC-line modeling. The AC voltage

Vac on the primary side of the converter transformer is calculated using the PFC module of PSS/E. The DC-line current

Idc and converter firing angle

α are obtained from the modules for DC-line modeling and control-mode selection, respectively. The DC-line voltage

Vdc and other quantities associated with

Vac,

Idc and

α are calculated in the equation conversion module. In the module for control-mode selection,

α is then updated using the calculated

Vdc and

Idc. The updated

Vdc and

α are used to update

Idc in the module for DC-line modeling. The converter output power

Pac and

Qac are calculated using

Vdc and

α to provide the value of

Iac to PSS/E. PSS/E then updates

Vac using the updated

Iac in the PFC module. These calculations are performed iteratively as part of the DS process.

3.1. Equation Conversion

The main objective of the equation conversion module is to calculate the DC voltage of an HVDC system using

Idc and

α, which are calculated by the DC-line modeling and the control-mode selection modules, respectively. The algebraic equations for

Pac and

Qac, are then solved in the “calculate

Pac and

Qac module” to calculate the

Iac, which is injected into the AC grid under normal and abnormal operating conditions. Under normal conditions, the overlap angle

μ is less than 60° and two or three valves (i.e., Valves 1, 2, or 3) are conducted, as shown in

Figure 2a. When a commutation occurs, the next valve is fired when its voltage exceeds the voltage of the valve currently operating; for example, Valve 3 will commutate from Valve 1 when

vb >

va (i.e., the point A in

Figure 2b). However, because of

α, the next valve to be fired (i.e., Valve 3) will not conduct during time period

α (i.e., the point B) and then the two Valves 1 and 3 on the upper side will conduct during the period

μ, as shown in

Figure 2b. Under abnormal conditions,

μ is larger than 60° and four valves (i.e., Valves 1, 2, 3 and 6) are conducted. This results in a short circuit (i.e., the conducting of Valves 3 and 6), as shown in

Figure 2a.

va and

vb then become equal to

ea and (

eb +

ec)/2, respectively. Therefore, Valve 3 is ignited at the point C, where

vb >

va under the abnormal condition.

The initial AC active and reactive powers of the HVDC converters are calculated from the AC voltage and current inputs; these values are calculated using the PFC module in PSS/E. Using the power flow calculation results, the DC voltage of the HVDC system is calculated using Equation (1), where α is obtained from the control-mode selection module. The overlap angle μ can also be calculated using the value of α in Equation (2). The active power Pac and the power factor angle ϕ are then acquired using the updated values of Vdc, α, and μ, as shown in Equations (3) and (4), respectively. For the next iteration of the AC power flow calculation, the reactive power Qac is also obtained using Equation (5) such that the injected AC current to the HVDC converters can be calculated using Equations (3) and (5).

This paper focuses on the abnormal condition that arise in an HVDC system in the event of commutation failure; i.e., when the extinction angle

γ falls below

γmin or where

μ exceeds 60° [

18,

19,

20,

21]. If

μ exceeds 60°, the subsequent commutation (i.e., from Valve 1 to Valve 3) will commence before completion of the current commutation (i.e., from Valve 2 to Valve 6). This results in a short circuit (i.e., the conducting of Valves 3 and 6), as shown in

Figure 2a.

va and

vb then become equal to

ea and (

eb +

ec)/2, respectively, as shown in

Figure 2b. Valve 3 is ignited at the point C, where

vb >

va under the abnormal condition, whereas it is fired at the point B due to

α under the normal operation, as shown in

Figure 2b. Thus, the DC voltage and current will be modified under the abnormal condition, as seen in Equations (6) and (7).

By substituting Equation (7) into Equation (6), Vdc can be represented as (8). Furthermore, γ and Equations (3)–(5) are accordingly modified under the abnormal condition to Equations (8)–(12). These equations are not reflected in the conventional sample models (i.e., CDC4T, CDC6T, and CDC7T) in PSS/E. Therefore, the proposed modeling method improves estimation of the DC voltage, DC current, and AC current that is injected into the converters during the transient operation of the HVDC system triggered by commutation failure.

3.2. Control-Mode Selection

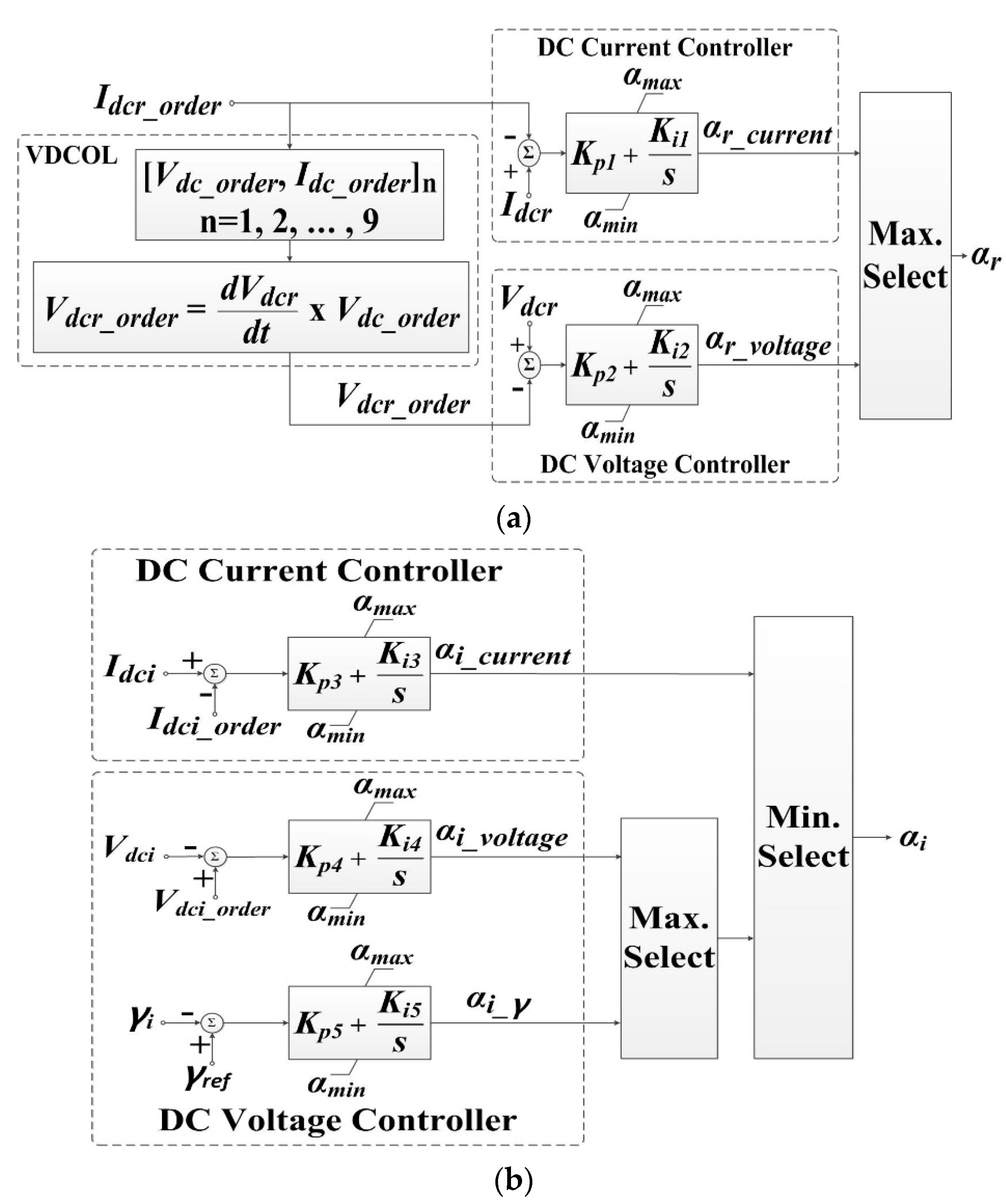

The module for control-mode selection calculates

α for the rectifier and the inverter. The control mode of HVDC converters can be changed from current control to voltage control, and vice versa, according to the AC voltage conditions at the converter output ports. Many HVDC system device manufacturers (e.g., ABB, SIEMENS, and ALSTOM) have developed methods for selecting the control mode. For example, ABB implements control mode selection by changing the minimum or maximum limits of the DC current controllers [

29]. In their system, DC voltage control is executed first, and the output of the DC voltage controller is set to the minimum or maximum limits of the DC current controller on both sides [

28]. However, different HVDC systems may have differing

V-

I characteristics, which makes implementation difficult using either the CIGRE benchmark model or the proprietary control models developed by particular manufacturers. Therefore, in this paper, a rather simple and straightforward HVDC controller is proposed to facilitate analysis of dynamic variations in DC-line voltages and currents. With some minor modifications, the proposed controller is easily applicable to other types of HVDC systems; e.g., KEPCO has used a controller to model the Jeju–Jindo HVDC system [

30].

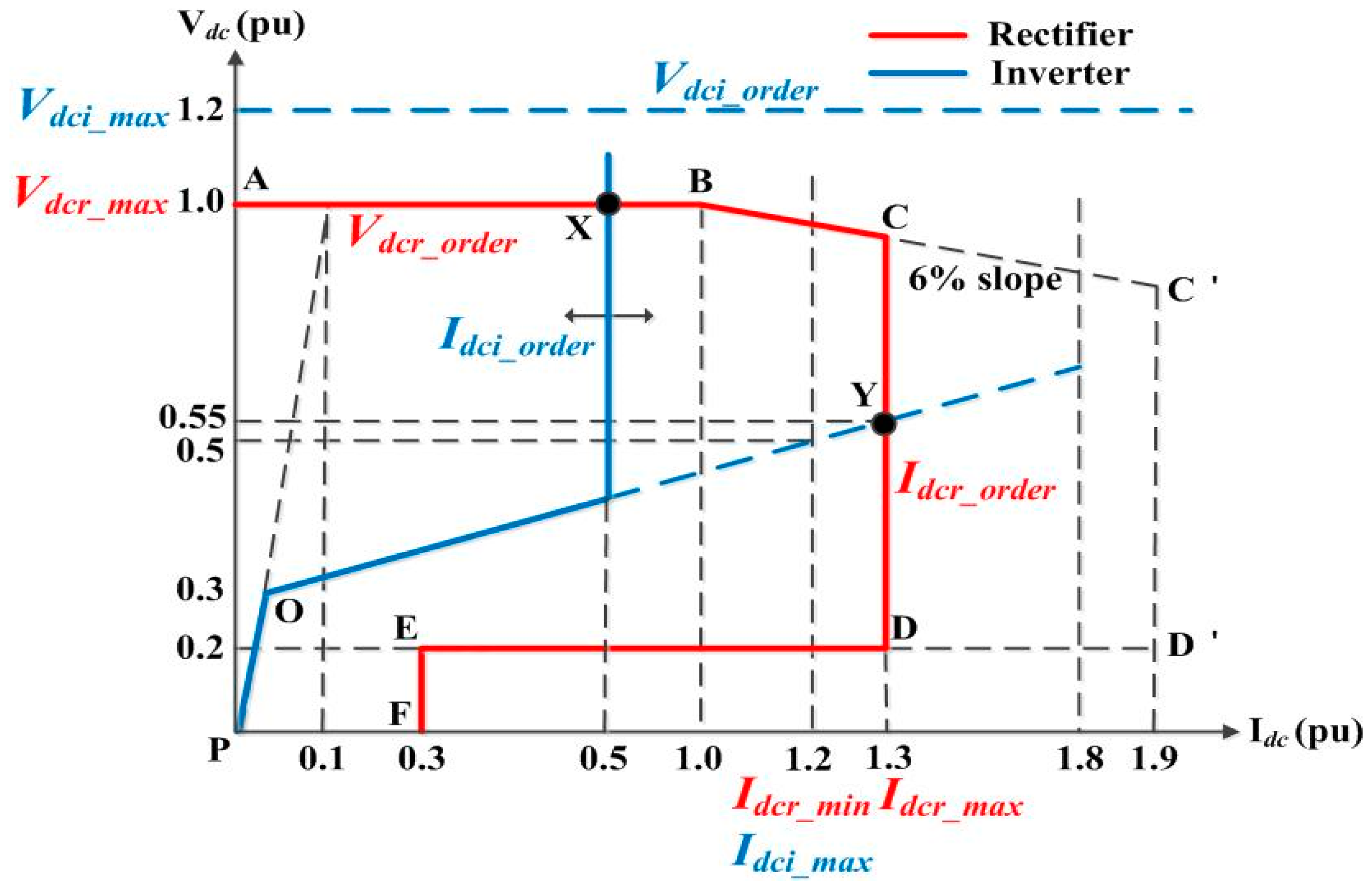

Figure 3 shows a simplified schematic diagram of the proposed scheme for control-mode selection for the rectifier and inverter of the Jeju–Haenam HVDC system, which has a

V-I characteristic curve as shown in

Figure 4. In the proposed scheme, the control mode to achieve the smallest difference between the reference and current values of the DC voltage and current is determined. For the rectifier, there are two proportional integral (PI) controllers with pre-determined maximum and minimum output limitations. If the rectifier controls the DC voltage under the normal operations (i.e., the point X in

Figure 4), then the DC voltage and current of the rectifier become very close to

Vdcr = 1.0 pu and

Idcr = 0.5 pu. The reference DC voltage and current at the rectifier side are

Vdcr_order = 1.0 pu and

Idcr_order = 1.3 pu, as shown in

Figure 4. Therefore, the difference between

Vdcr_order and

Vdcr is so small that the output signal

αr_voltage of the DC voltage controller at the rectifier is close to the current rectifier firing angle

αr, which is normally within the range from 15° to 20°. On the other hand, the DC current controller decreases the output signal

αr_current so as to increase

Idcr up to

Idcr_order. This is because

Idcr is calculated using the difference between

Vdcr, which is proportional to cos

αr, and the DC voltage at the middle of the DC line. In other words, a decrease in

αr is equivalent to an increase in

Idcr by increasing

Vdcr. Therefore,

αr_current is smaller than

αr_voltage, which is chosen as an updated

αr using the maximum selection function.

Furthermore, the rectifier controls the DC current when the AC network voltage drops (i.e., the point Y in

Figure 4). The voltage and current become very close to

Vdcr = 0.55 pu and

Idcr = 1.3 pu.

Vdcr_order and

Idcr_order are similar, as discussed above (1.0 and 1.3 pu, respectively). Thus, the DC voltage controller decreases

αr_voltage so as to increase

Vdcr up to

Vdcr_order. However,

αr_current is close to current

αr due to the small difference between

Idcr_order and

Idcr. Consequently, the updated

αr is chosen from the DC current controller.

αmin is normally larger than 5° to ensure adequate voltage across the valve before firing and

αmax is normally between 90° and 170° to operate in the inverter region to assist the system under certain fault conditions.

The control-mode selection of the inverter side is similar to that at the rectifier side, apart from the additional PI controller for γ selection as shown in

Figure 3b. Under normal operation (i.e., point X in

Figure 4), the inverter DC voltage and current become very close to

Vdci = 1.0 pu and

Idci = 0.5 pu. The reference DC voltage and current at the inverter side are

Vdci_order = 1.2 pu and

Idci_order = 0.5 pu. Thus, the difference between

Idci_order and

Idcr is so small that the output signal

αi_current of the DC current controller at the inverter is close to the current inverter firing angle

αi. However, the DC voltage controller increases the output signal

αi_voltage so as to increase

Vdci up to

Vdci_order;

Vdci is proportional to cos (π –

αi). Therefore,

αi_voltage is larger than

αi_current, which is chosen as an updated

αi using the minimum selection function.

Analogously, when the inverter controls the DC voltage (i.e., the point Y in

Figure 4),

αi_current is increased so as to decrease the DC current from

Idci = 1.3 pu to

Idci_order = 0.5 pu. This is because

Idci is calculated using the difference between the DC voltage at the middle of the DC line and

Vdci. In other words, an increase in

αi means a decrease in

Idci by increasing

Vdci. On the other hand,

αi_voltage is similar to the current

αi due to the small difference between

Vdci and

Vdci_order of 0.55 pu. Therefore, the updated

αi is chosen from the DC voltage controller. The γ controller is an auxiliary controller and is not discussed further for brevity.

3.3. DC-Line Modeling

In the DC-line modeling module, the DC currents at the rectifier and inverter are calculated using the updated DC voltages (i.e., Equations (1) and (8)) under the normal and abnormal operating conditions, respectively, as well as

α at each simulation time-step.

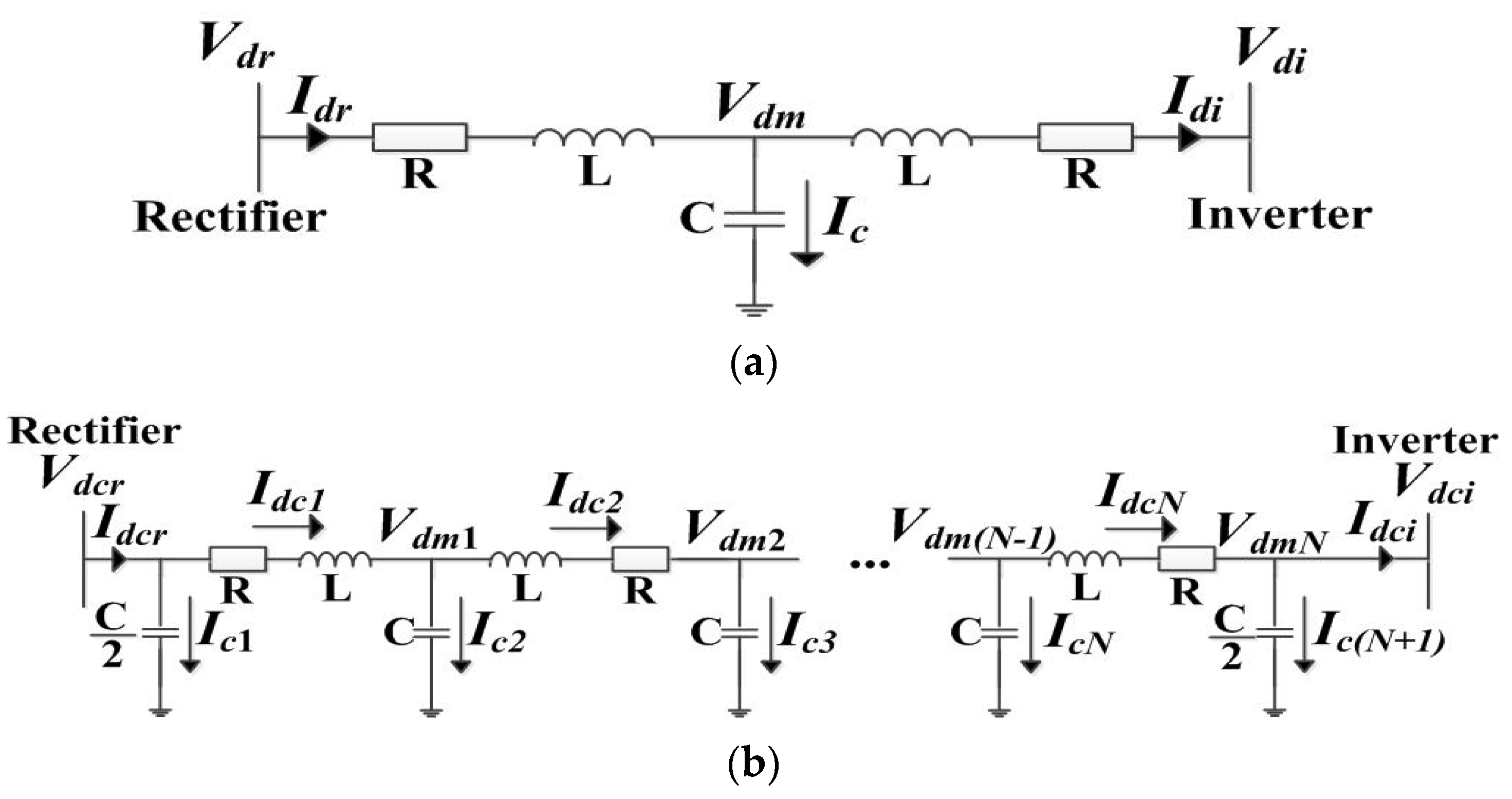

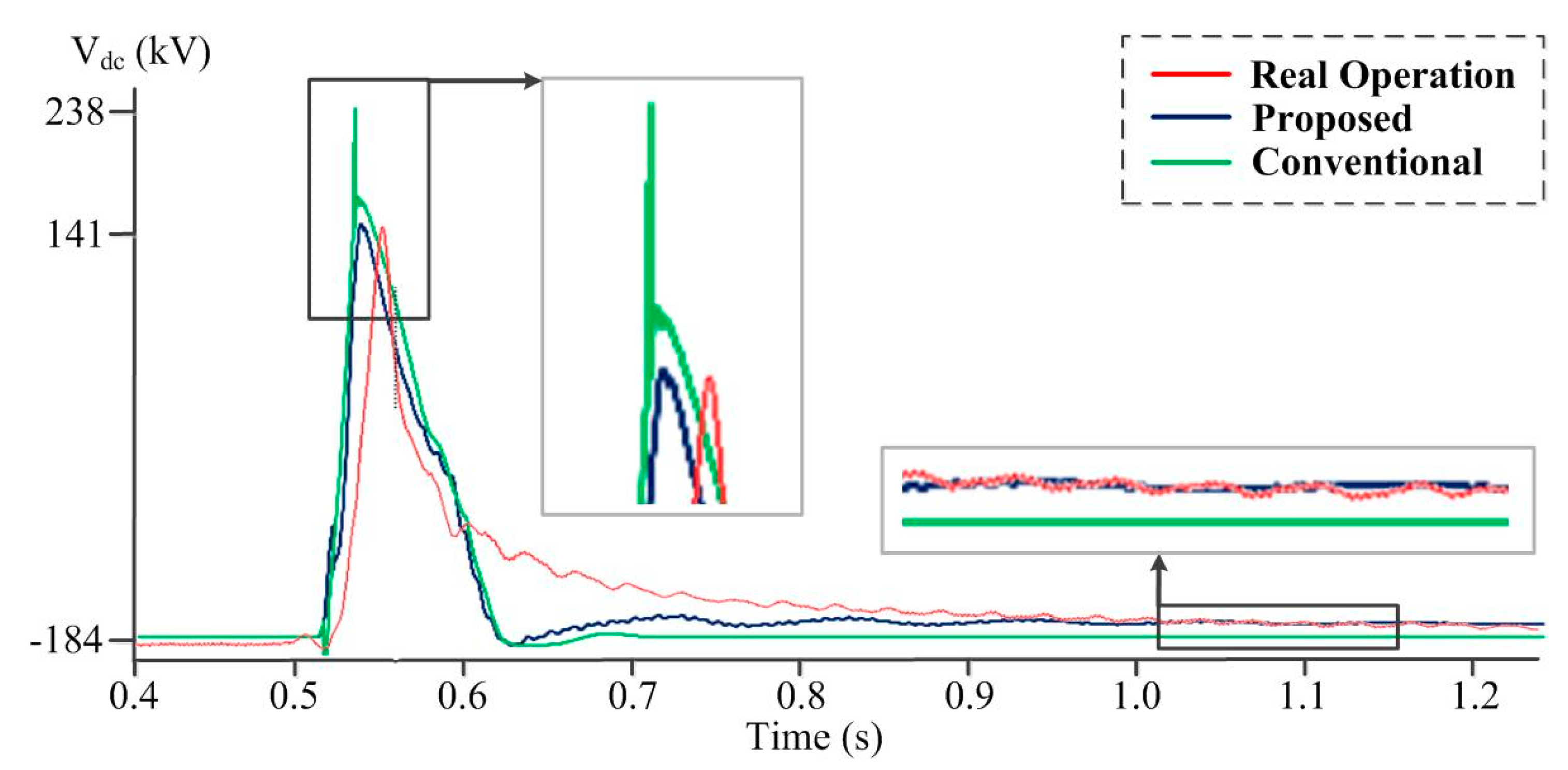

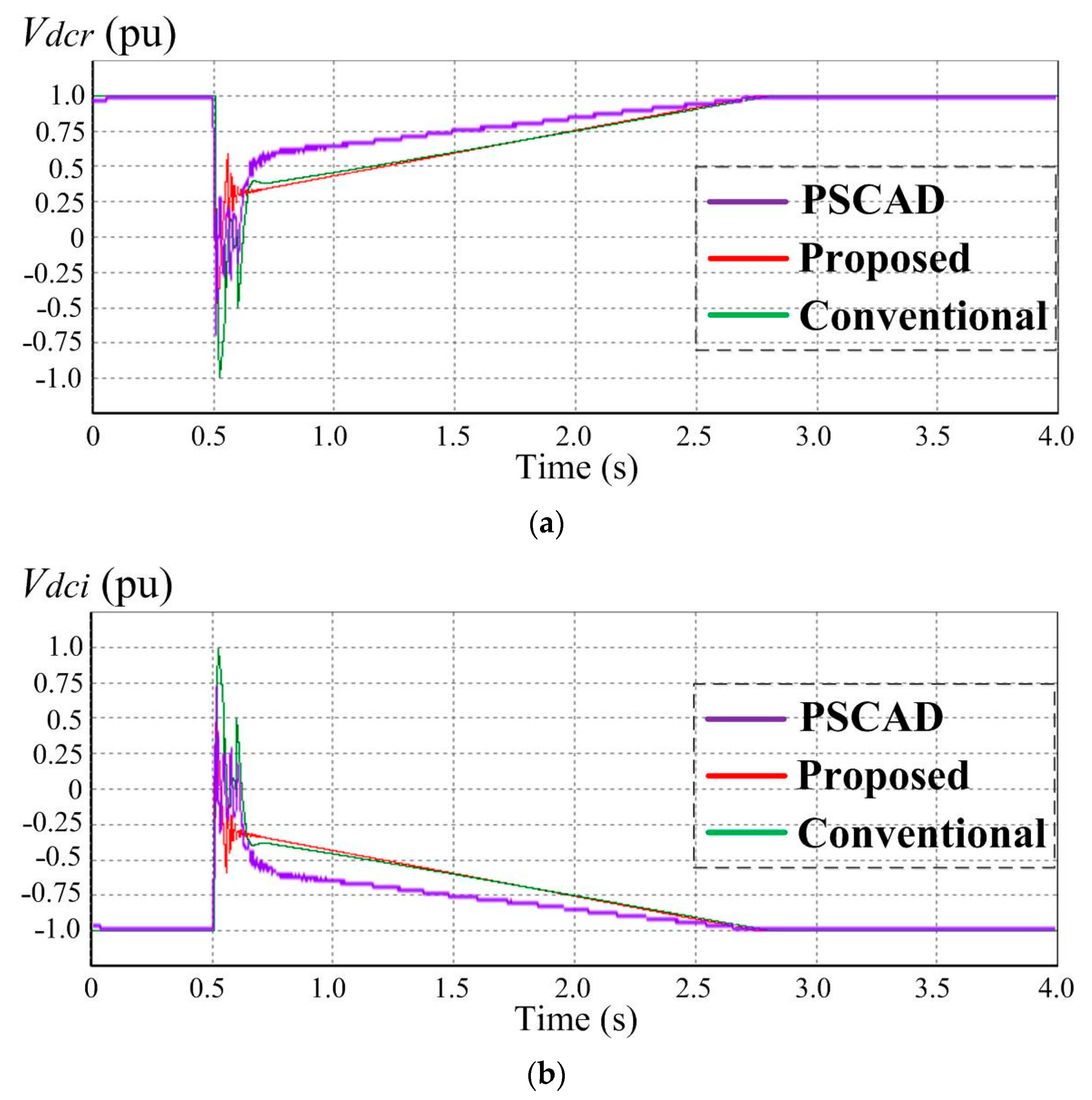

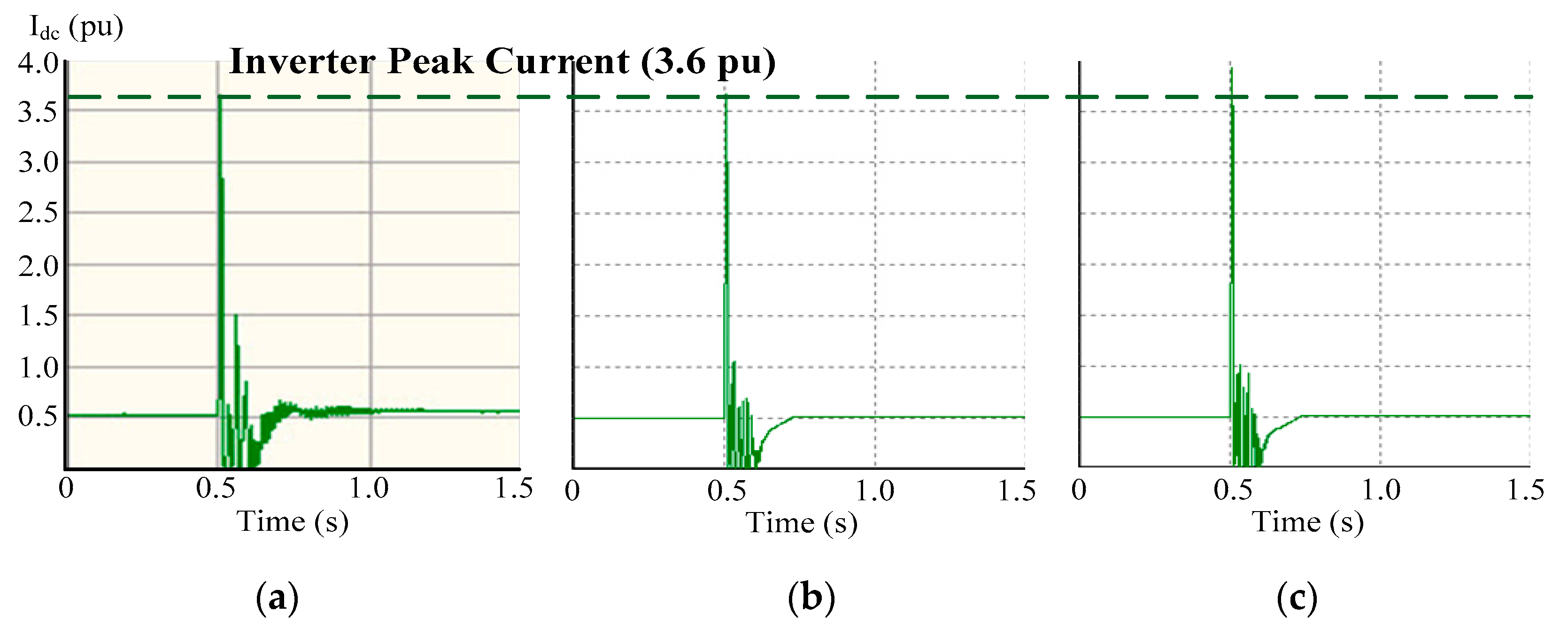

Figure 5 shows a comparison between the conventional and proposed DC-line models. In [

31], the DC line of the HVDC system was modeled using a π-section. The accuracy of the estimation increases with the number of π-sections used, as discussed in

Section 4.

The conventional DC-line model has been used in many previous papers [

7], references [

32,

33] because of its simplicity. However, it may overestimate the fault current, particularly with PSS/E, when there is a commutation failure resulting from a single-phase or three-phase line-to-ground fault in the AC network. Specifically, in the conventional DC-line model, the fault current mainly arises from the difference between the DC voltages

Vdm at the middle of the DC line and

Vdci at the inverter side. In the proposed model, the fault current mainly arises from the difference between

Vdm(n-1) and

Vdmn, as shown in

Figure 5b. Note that

Vdm0 and

VdmN are equal to

Vdcr and

Vdci, respectively. The difference between

Vdm(n-1) and

Vdmn may approximate the actual fault more accurately than the difference between

Vdm and

Vdci. This is because the actual DC-line has a uniformly distributed resistance

R, inductance

L, and capacitance

C. The DC voltage and hence current are influenced by the line components punctuated in the DC-line.

However, as the number of differential equations required to calculate

Idci increase with the number of π-sections, it becomes more difficult to evaluate the PI gains (e.g.,

Kp3 and

Ki3 in

Figure 3) of the rectifier and inverter controllers. Therefore, in this paper, we settled the trade-off between the modeling accuracy and computational complexity by using three π-section lines (i.e.,

N = 3) to model the DC line.