A 9-10-Bit Adjustable and Energy-Efficient Switching Scheme for Successive Approximation Register Analog-to-Digital Converter with One Least Significant Bit Common-Mode Voltage Variation

Abstract

:1. Introduction

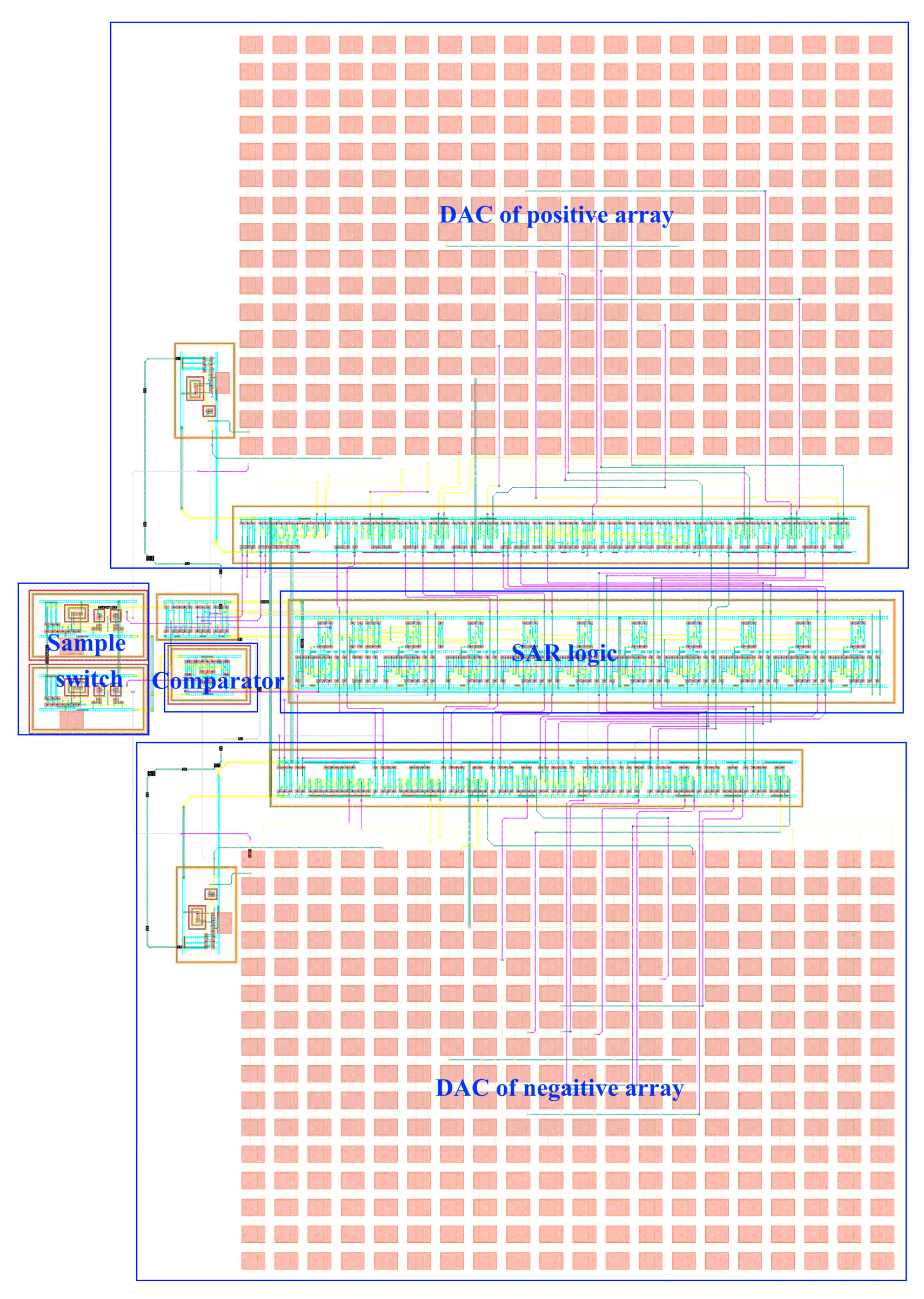

2. Design of the Proposed SAR ADC

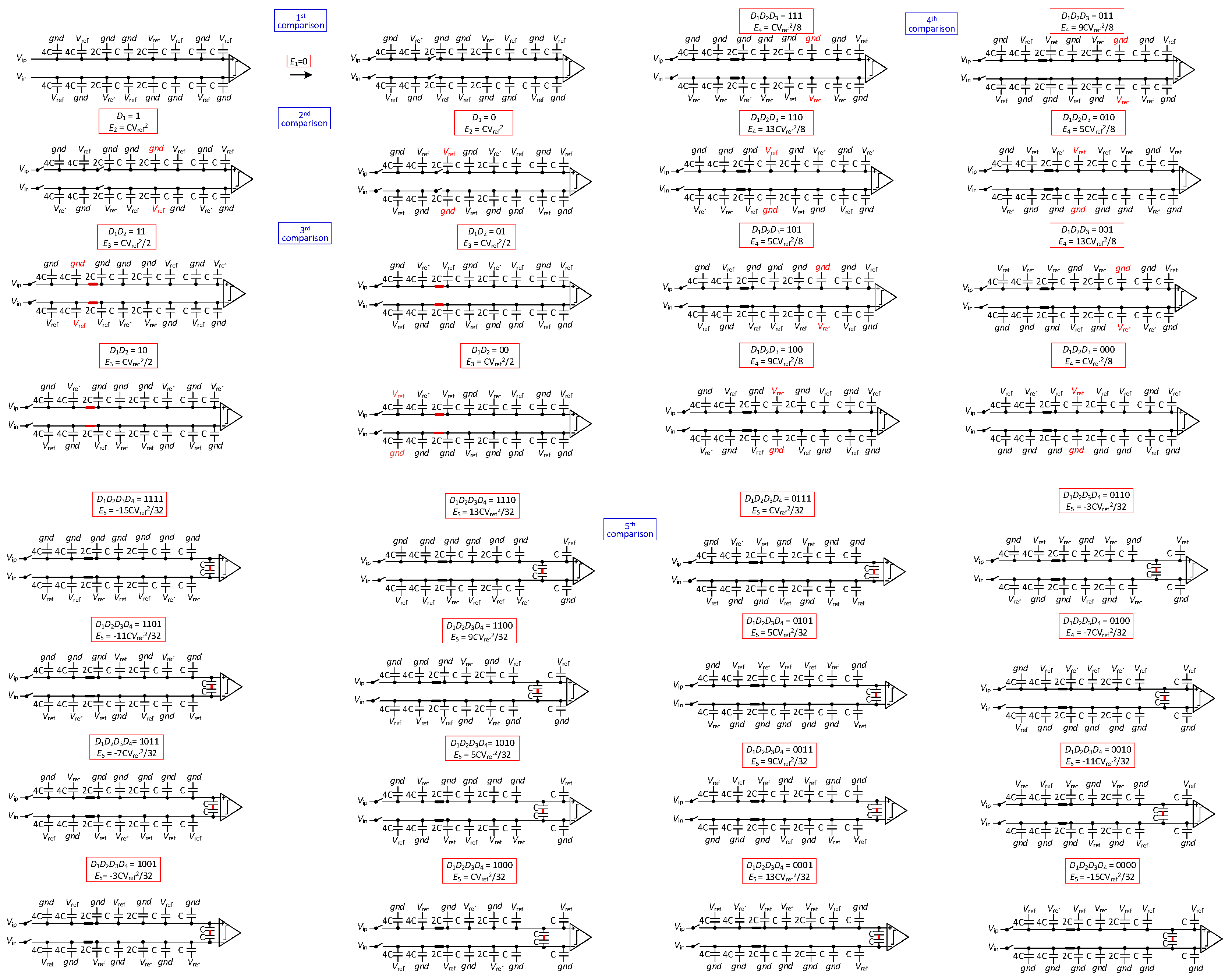

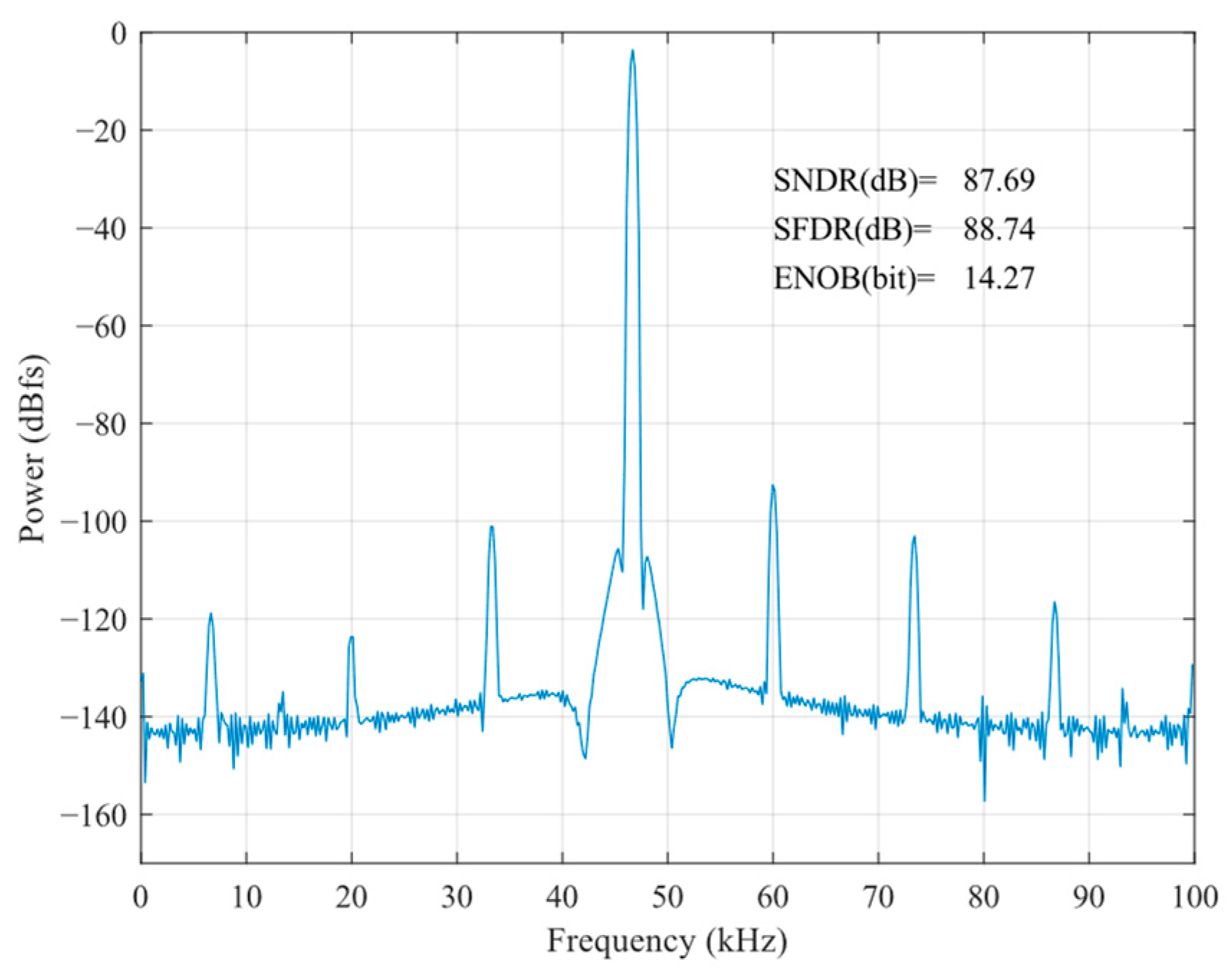

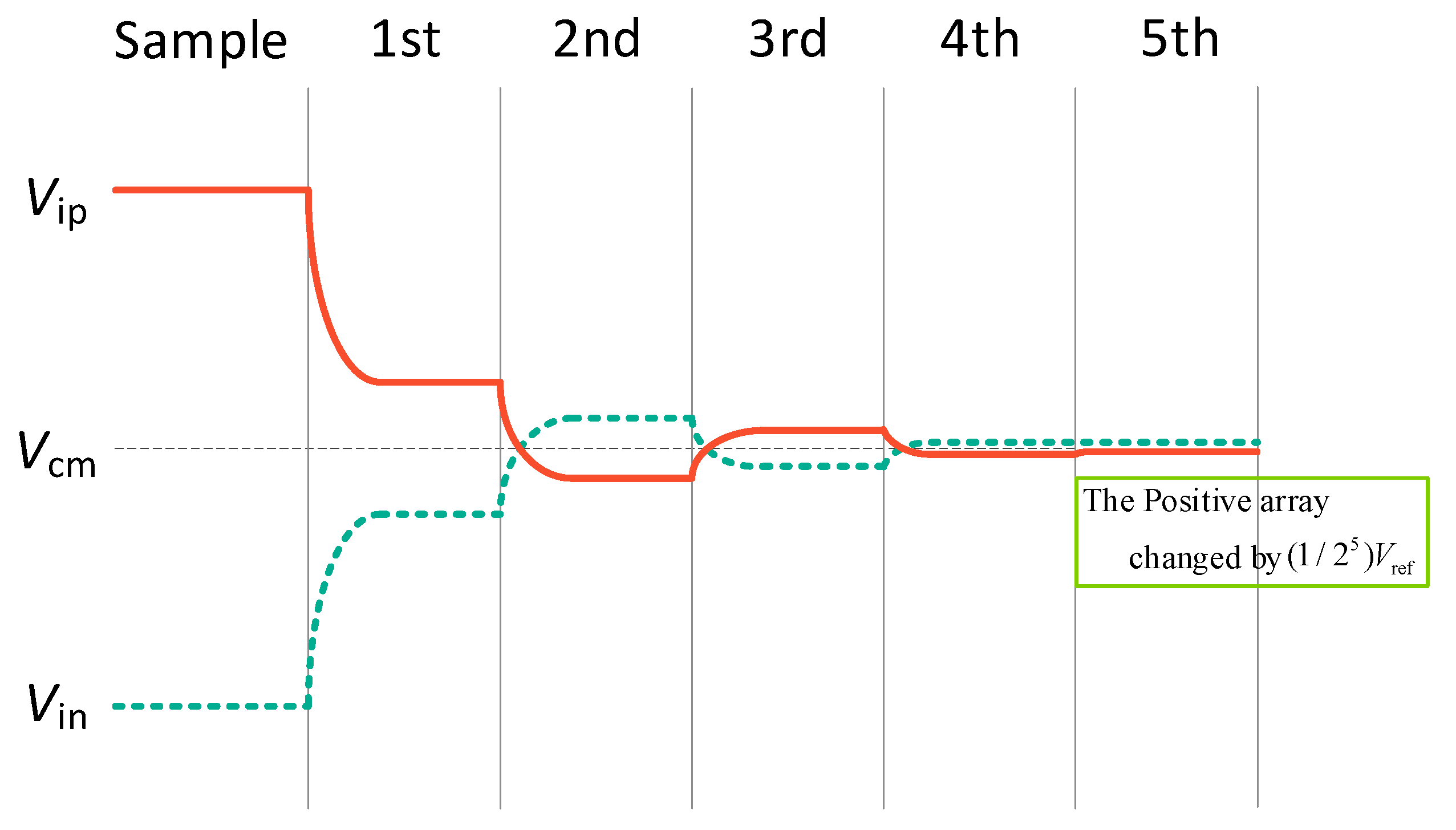

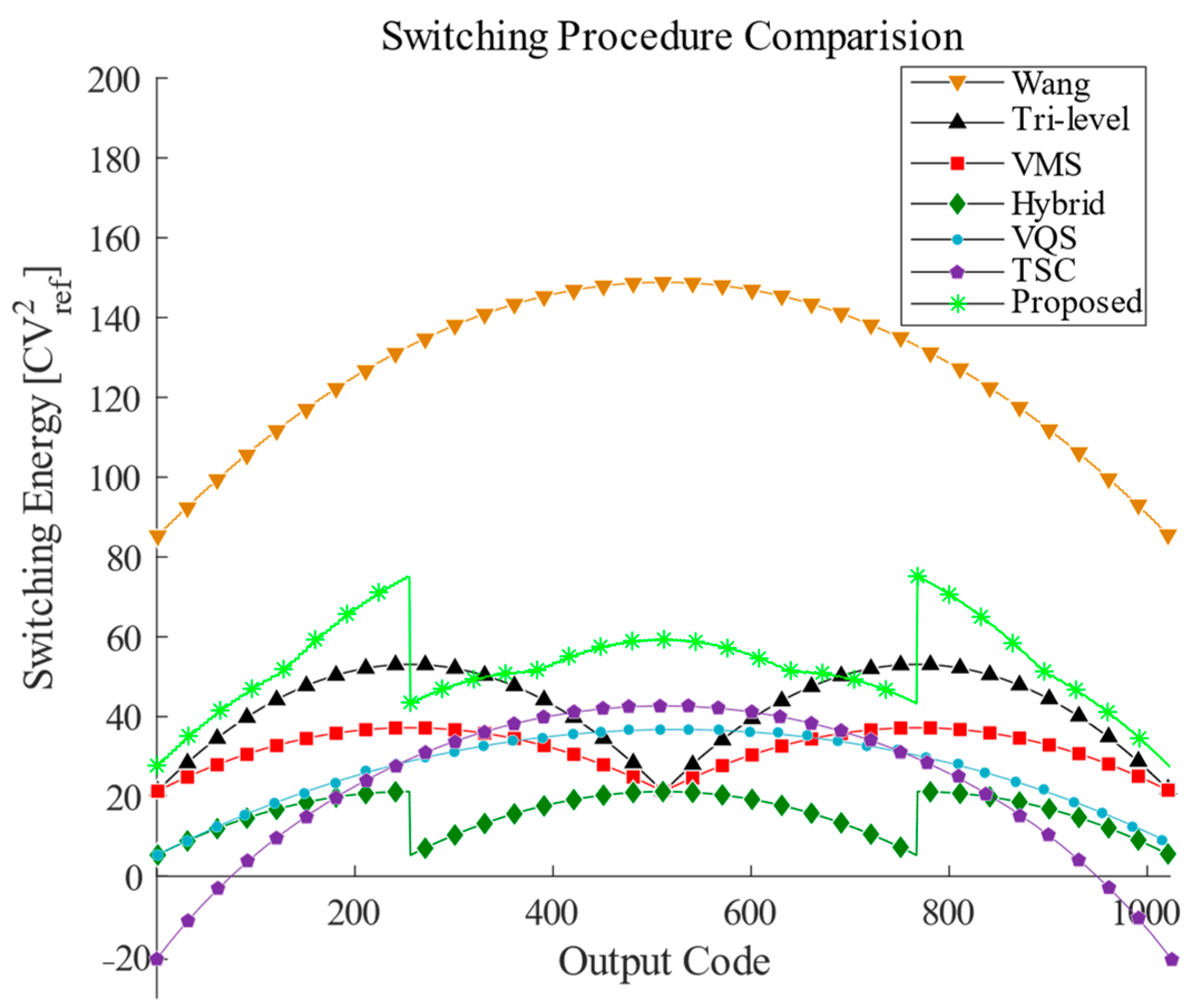

2.1. DAC Switching Scheme

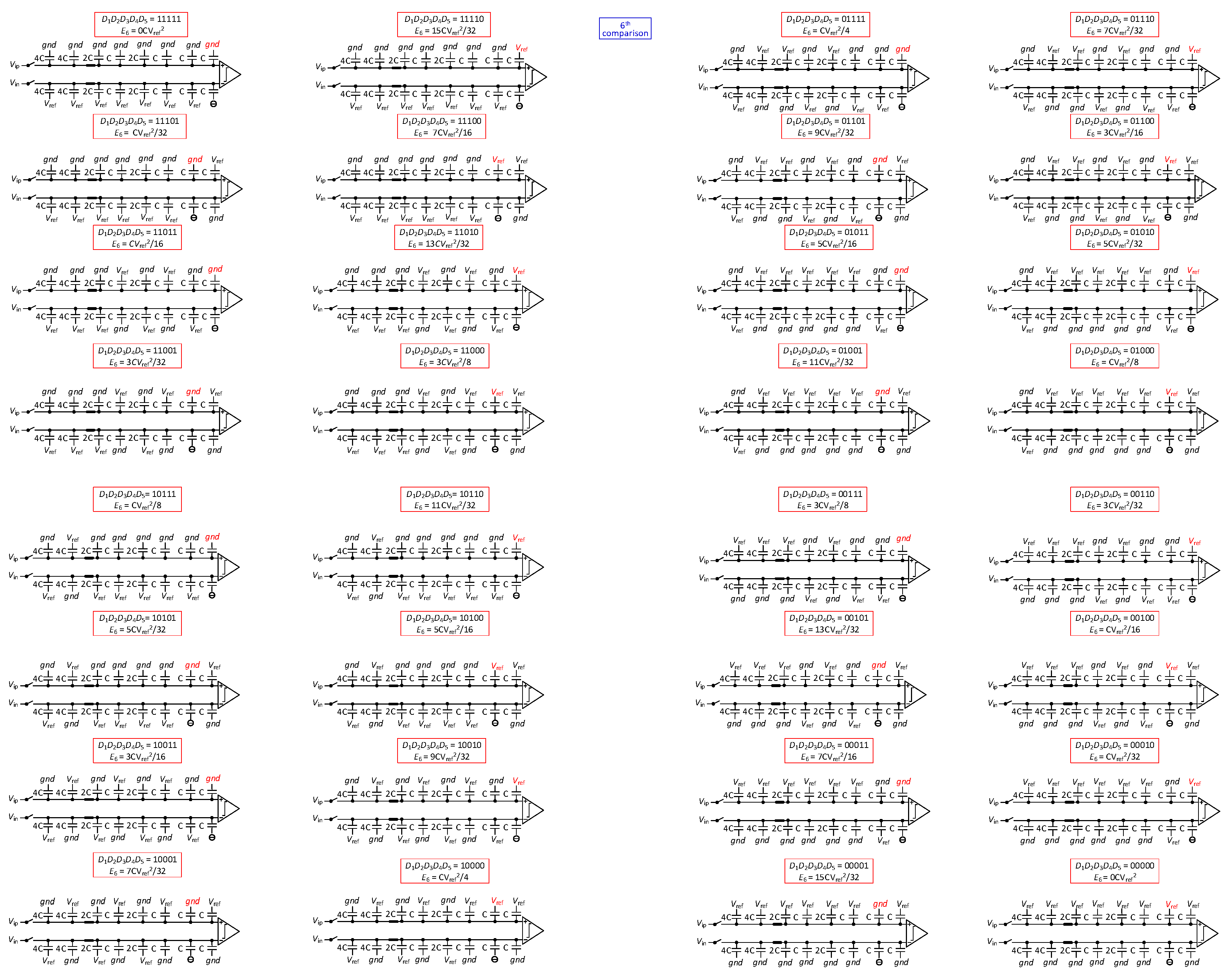

2.2. Bootstrapped Sample Switch

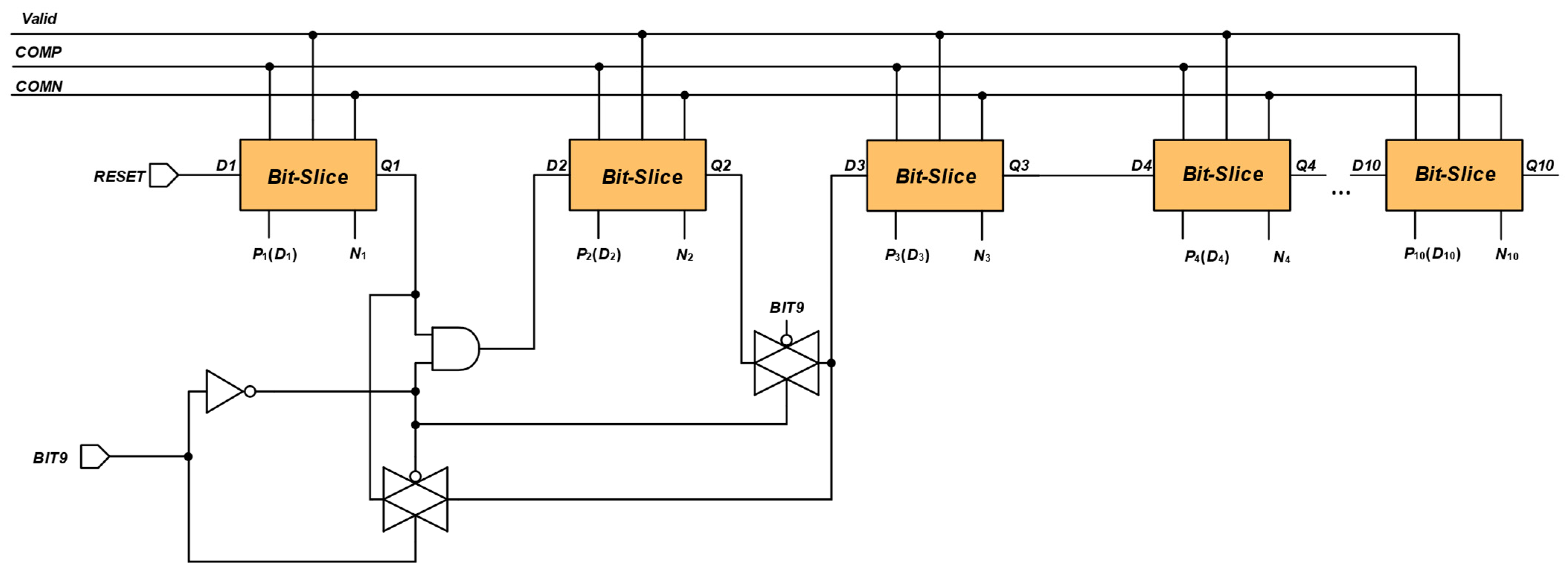

2.3. 9-10-Bit Adjustable SAR Logic

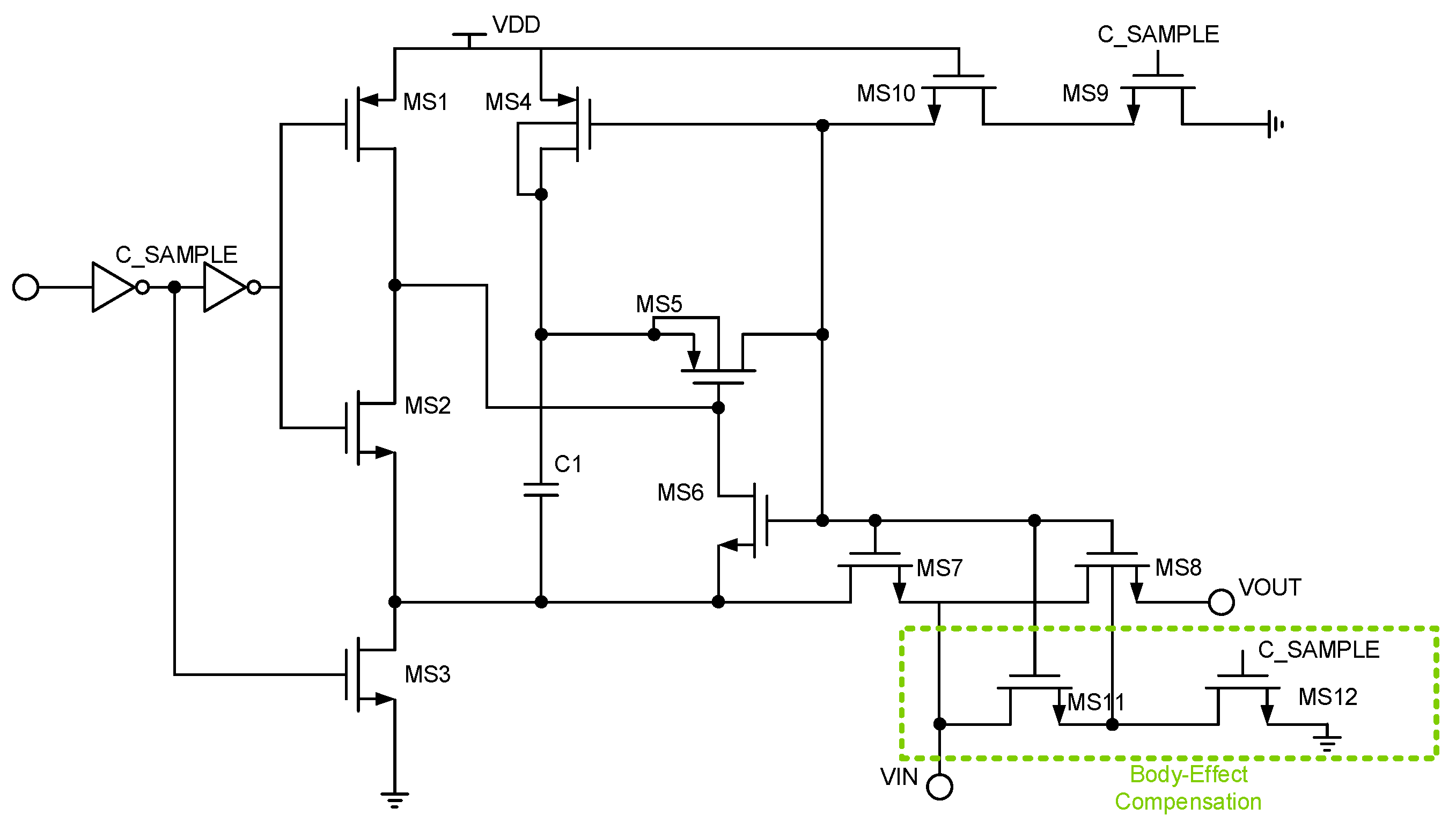

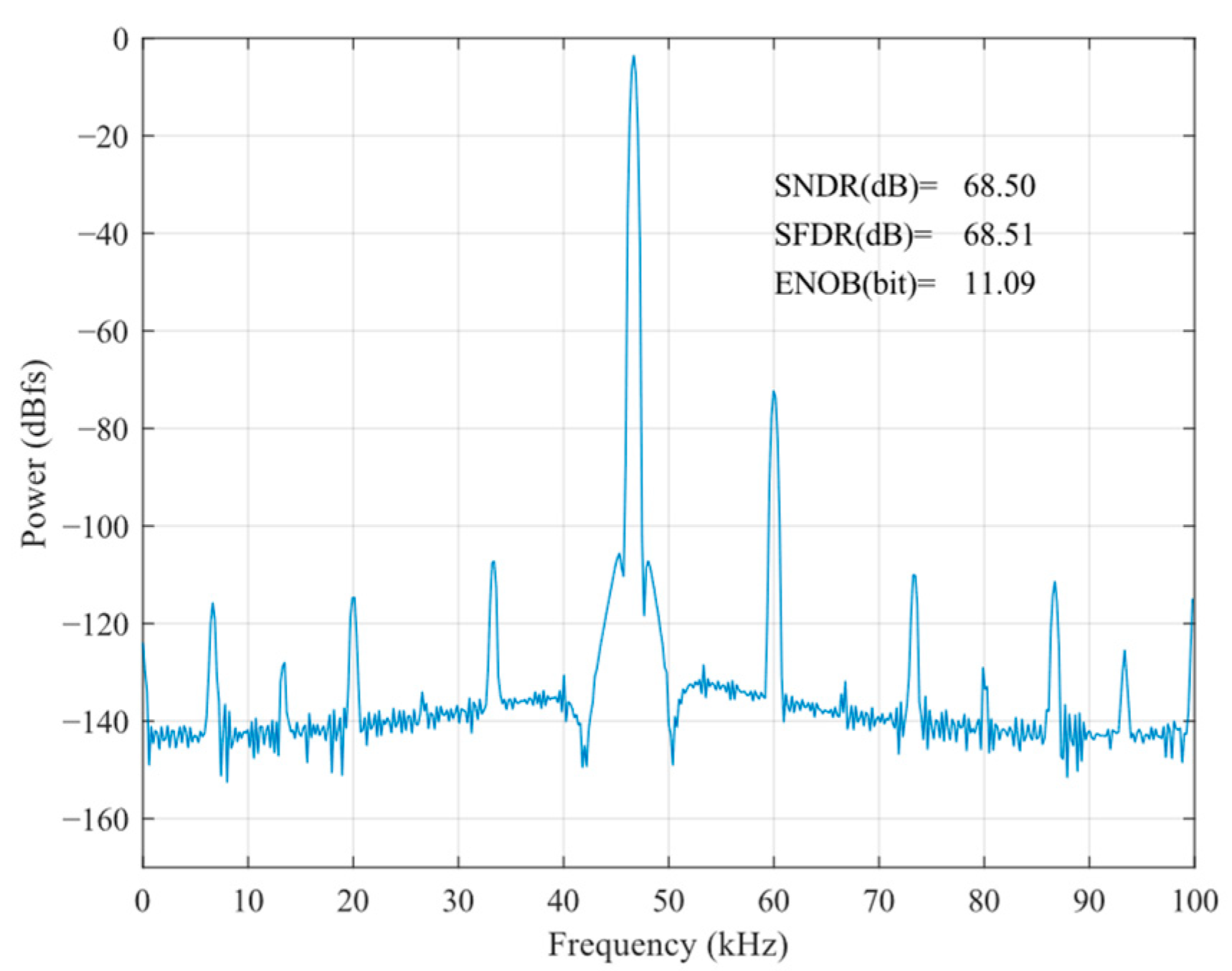

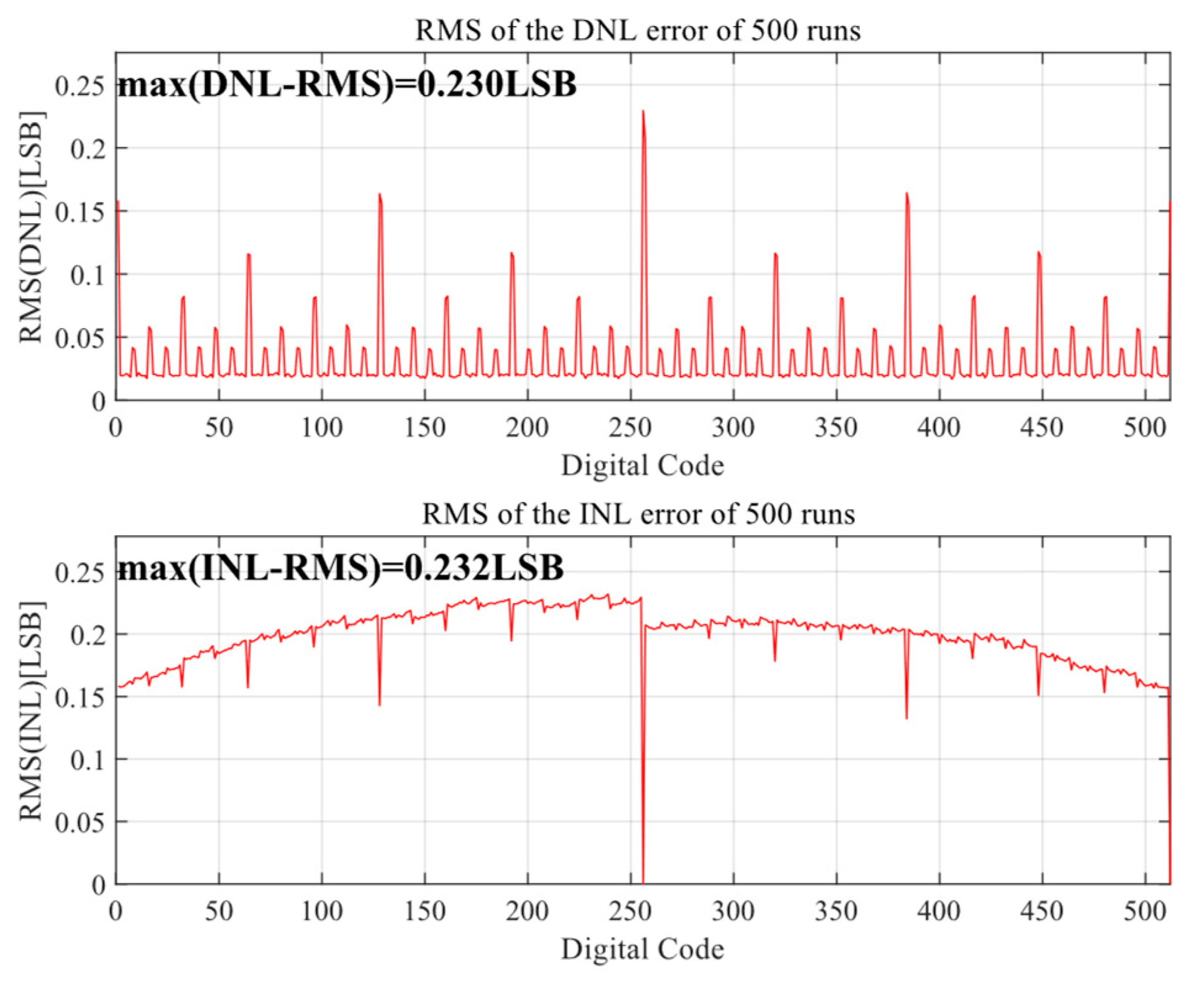

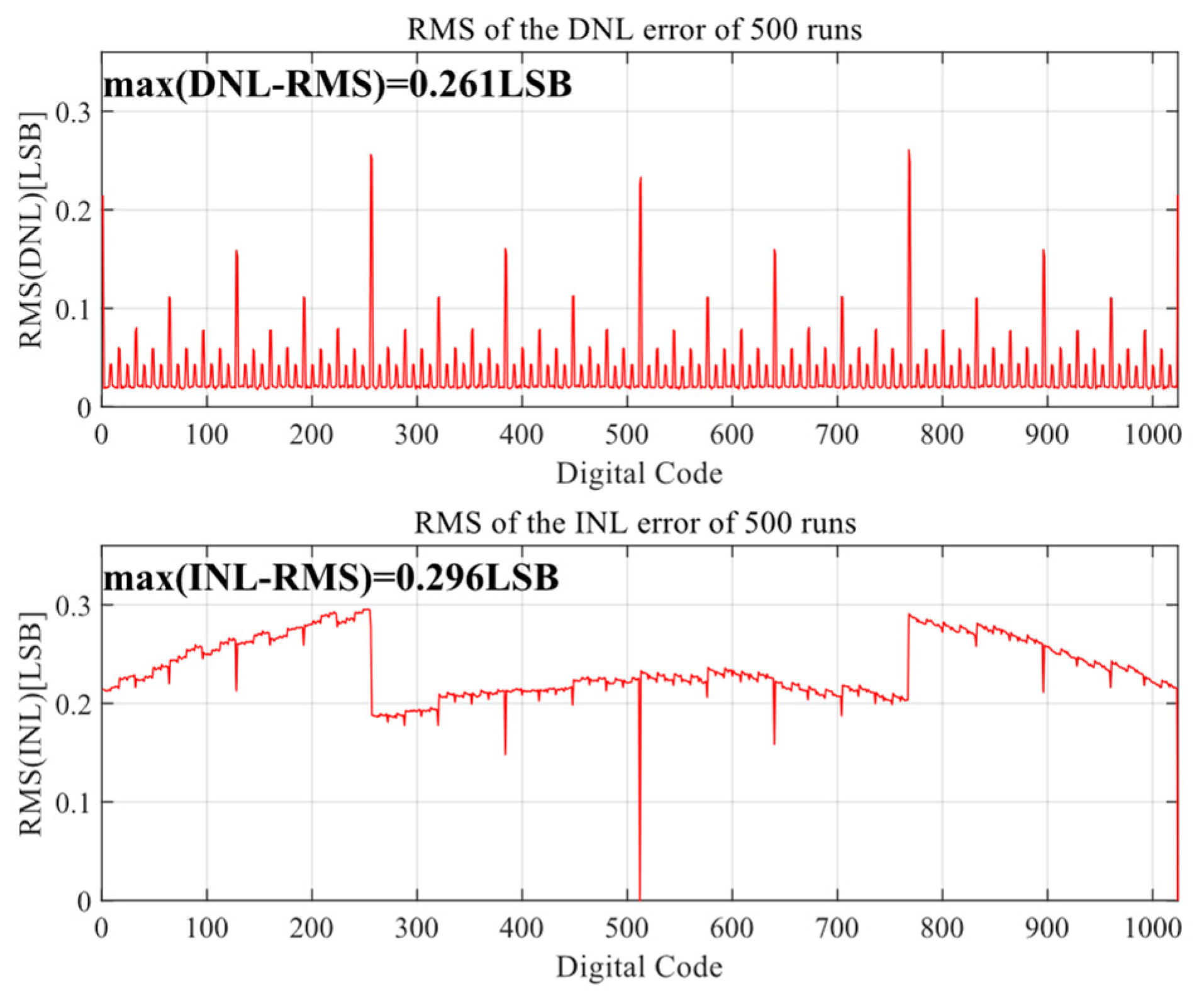

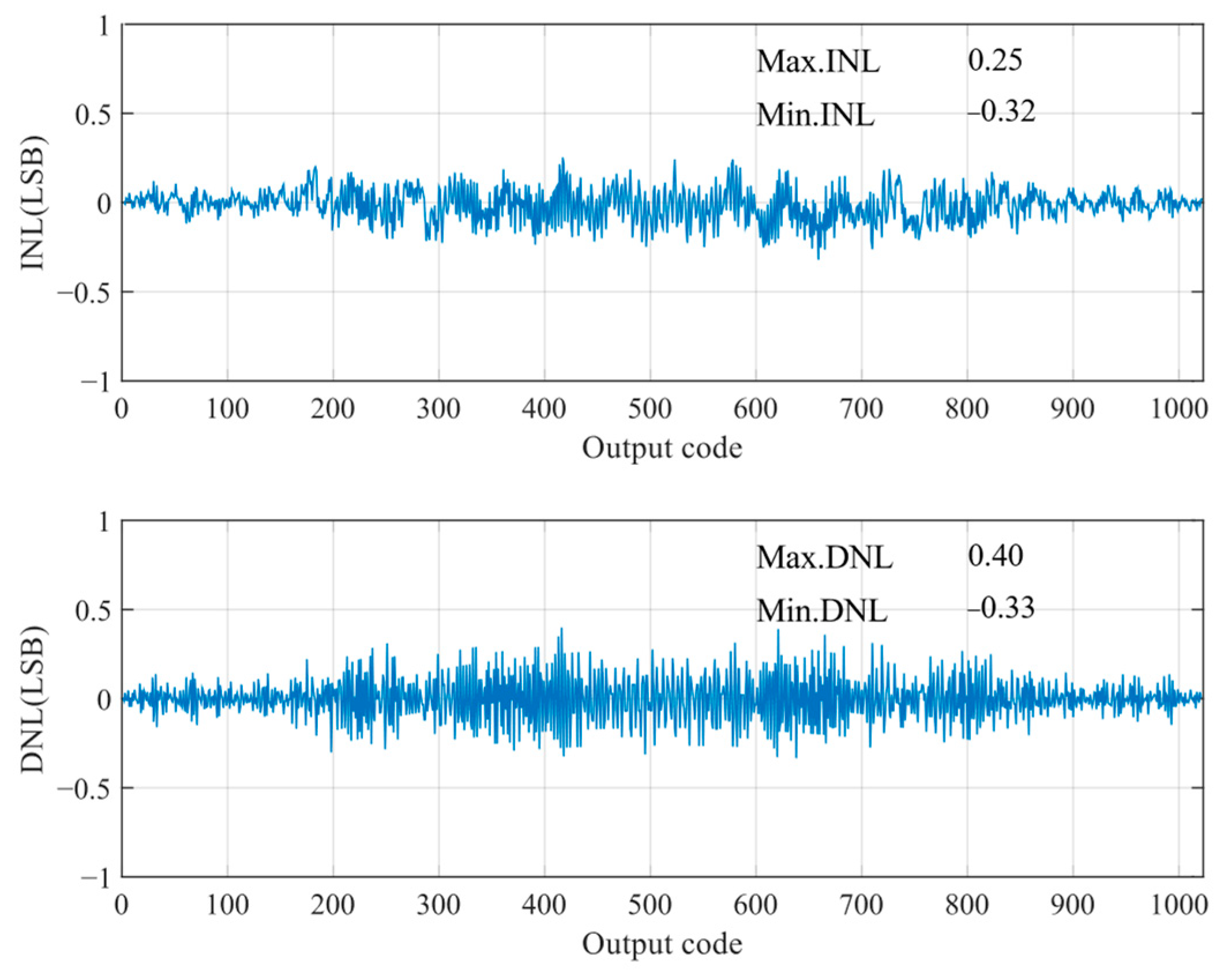

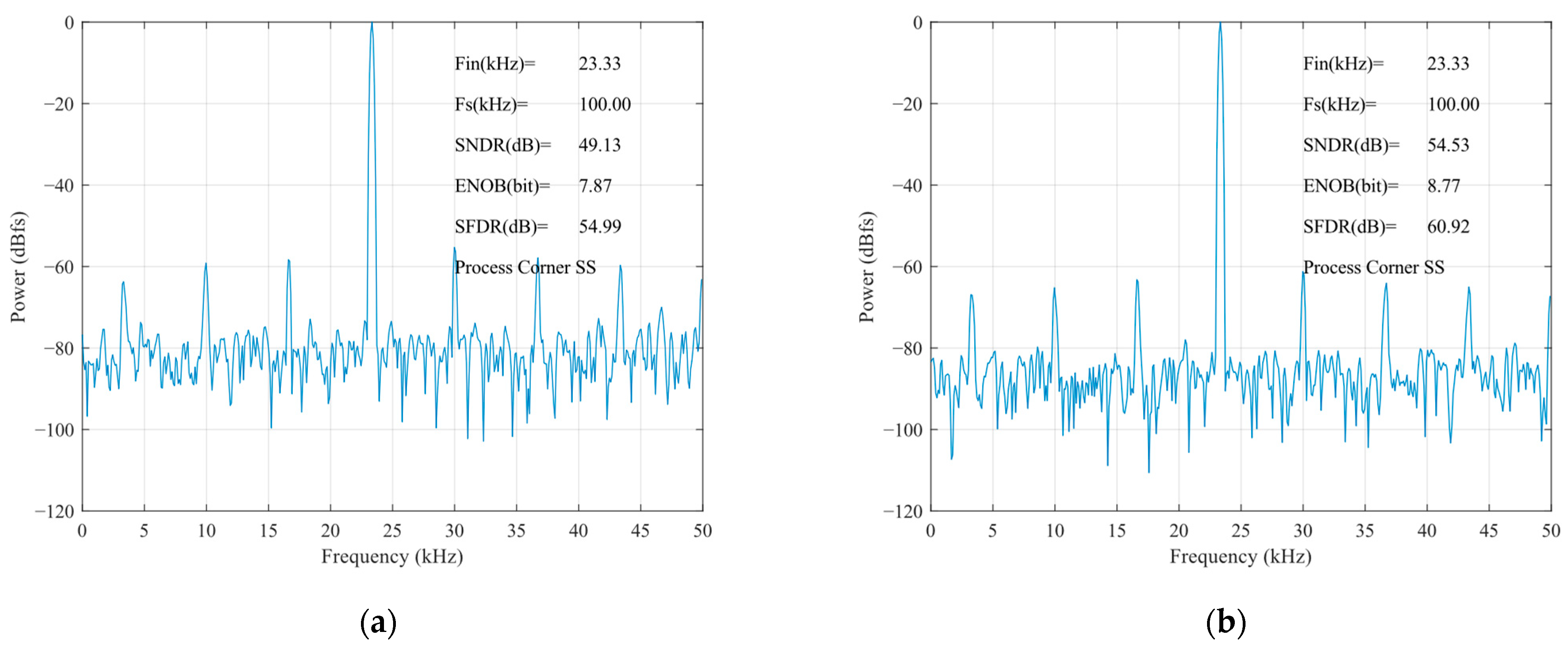

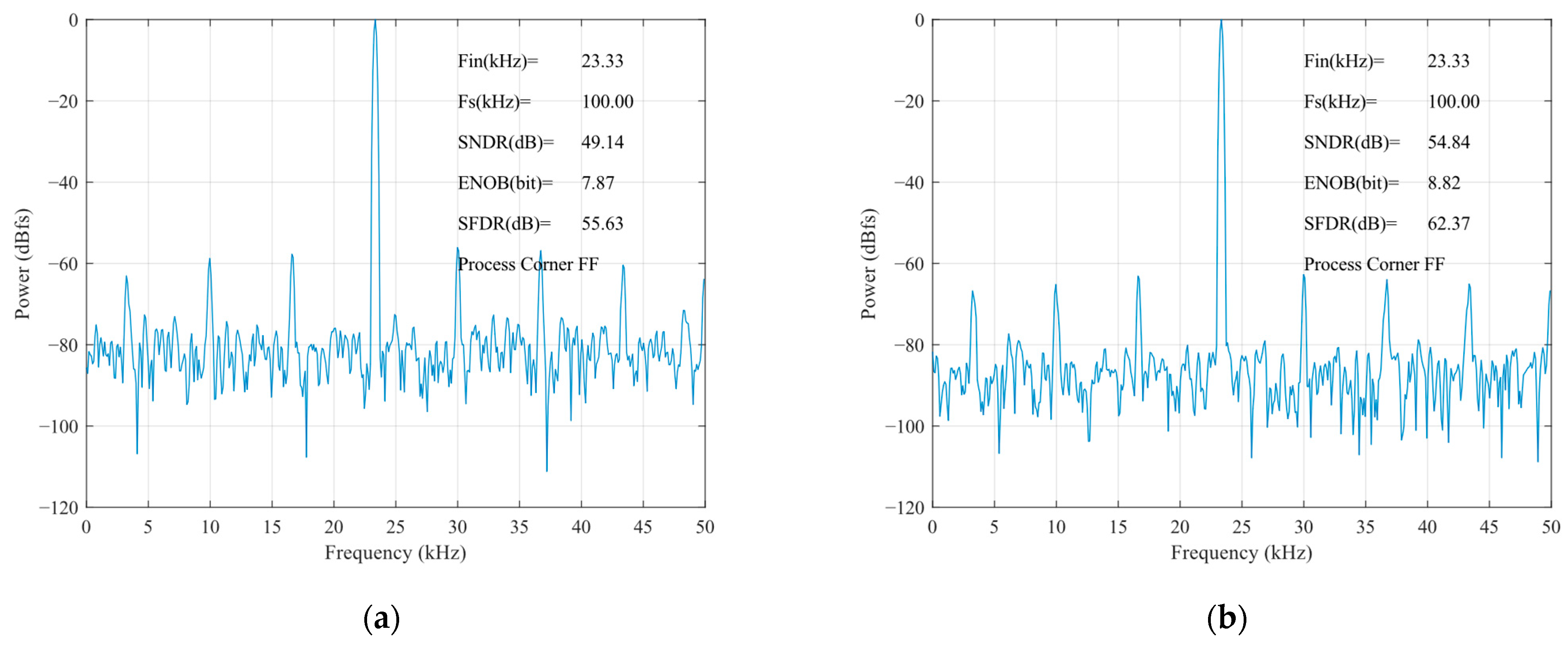

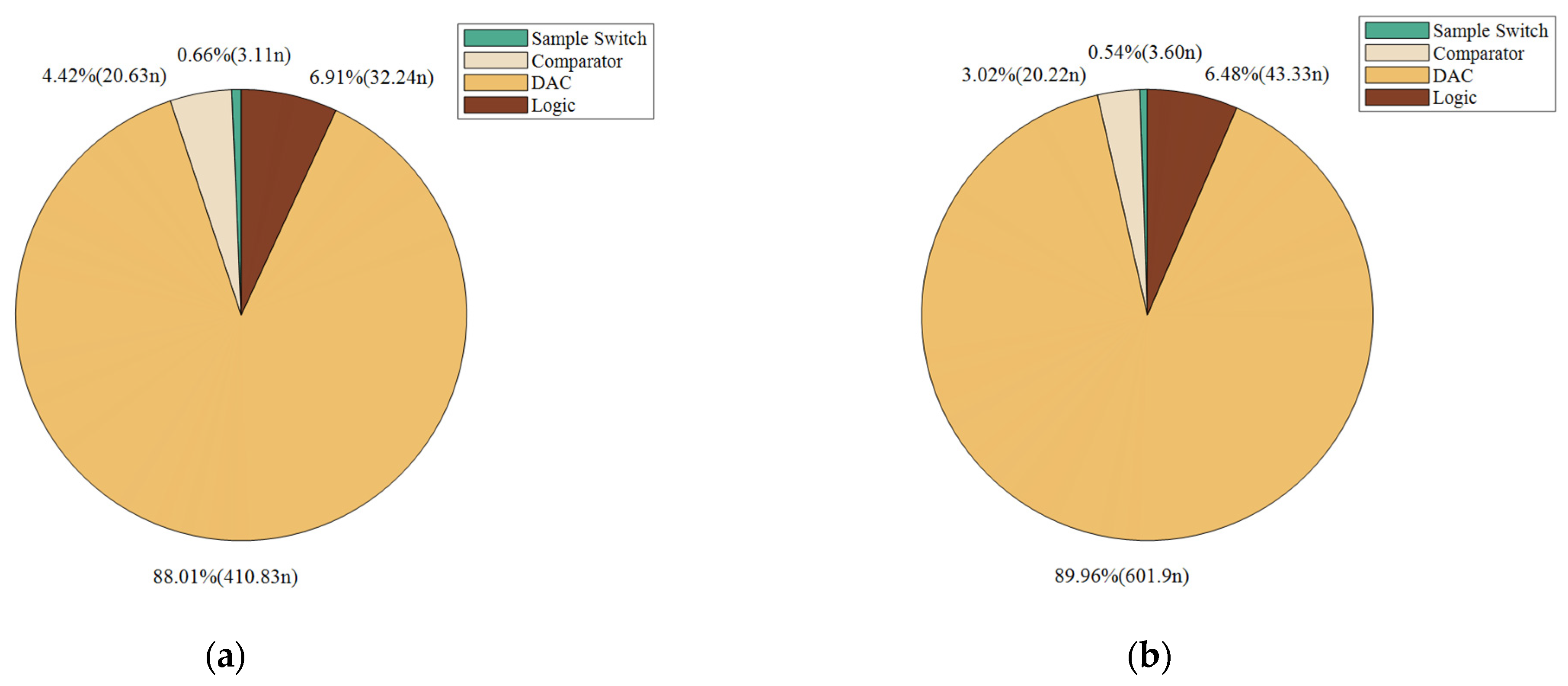

3. Simulation Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Xie, S.; Theuwissen, A. A 10 Bit 5 MS/s Column SAR ADC With Digital Error Correction for CMOS Image Sensors. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 984–988. [Google Scholar] [CrossRef]

- Lin, J.Y.; Chang, K.H.; Kao, C.C.; Lo, S.C.; Chen, Y.J.; Lee, P.C.; Chen, C.H.; Yin, C.; Hsieh, C.C. An 8-Bit Column-Shared SAR ADC for CMOS Image Sensor Applications. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 301–304. [Google Scholar]

- Yu, Z.; Liang, Y. A 99.93% Energy-Efficient Switching Scheme for SAR ADC without Switching Energy in the First Three MSBs. Microelectron. J. 2023, 136, 105771. [Google Scholar] [CrossRef]

- Xu, C.; Zhao, D. A 10-Bit 120MS/s SAR ADC Using Tri-Switch Sampling and VCM-Stable Switching Scheme in 40-Nm CMOS. IEICE Electron. Express 2023, 20, 20230202. [Google Scholar] [CrossRef]

- Guo, Y.; Qiu, L.; Yao, B. A Highly Area-Efficient Switching Scheme Based on Charge Sharing and Capacitor Holding for SAR ADCs. Circuits Syst. Signal Process. 2022, 41, 6561–6580. [Google Scholar] [CrossRef]

- Hu, Y.; Chen, L.; Chen, H.; Wen, Y.; Zhang, H.; Liu, X. A 100 KS/s 8–10 Bit Resolution-Reconfigurable SAR ADC for Bioelectronics Application. In Proceedings of the 2019 32nd IEEE International System-on-Chip Conference (SOCC), Singapore, 3–6 September 2019; pp. 209–212. [Google Scholar]

- Zhu, Z.; Qiu, Z.; Liu, M.; Ding, R. A 6-to-10-Bit 0.5 V-to-0.9 V Reconfigurable 2 MS/s Power Scalable SAR ADC in 0.18μm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 689–696. [Google Scholar] [CrossRef]

- Pahlavanzadeh, H.; Karami, M.A. A Low Settling Time Switching Scheme for SAR ADCs with Reset-free Regenerative Comparator. Int. J. Circuit Theory Appl. 2023, 51, 3078–3092. [Google Scholar] [CrossRef]

- Lee, H.-Y.; Lee, J.-S.; Noh, C.-K.; Kang, H.-J.; Kim, S.-T.; Baek, H.-S.; Kim, Y.-J.; Cho, C.-S. Low-Power Switching Scheme with Quarter Reference Voltage Sources for SAR ADCs. J. Electromagn. Eng. Sci. 2022, 22, 129–137. [Google Scholar] [CrossRef]

- Yaul, F.M.; Chandrakasan, A.P. A 10 Bit SAR ADC With Data-Dependent Energy Reduction Using LSB-First Successive Approximation. IEEE J. Solid-State Circuits 2014, 49, 2825–2834. [Google Scholar] [CrossRef]

- Liang, Y.; Zhu, Z.; Ding, R. SAR ADC Architecture with 98.8% Reduction in Switching Energy over Conventional Scheme. Analog. Integr. Circ. Sig. Process. 2015, 84, 89–96. [Google Scholar] [CrossRef]

- Zhang, H.; Zhang, H.; Sun, Q.; Li, J.; Liu, X.; Zhang, R. A 0.6-V 10-Bit 200-kS/s SAR ADC With Higher Side-Reset-and-Set Switching Scheme and Hybrid CAP-MOS DAC. IEEE Trans. Circuits Syst. I 2018, 65, 3639–3650. [Google Scholar] [CrossRef]

- Johns, D.A.; Martin, K.; Wiley, J. Analog Integrated Circuit Design. IEEE Circuits Devices Mag. 2000, 16, 39–40. [Google Scholar] [CrossRef]

- Liu, C.-C.; Chang, S.-J.; Huang, G.-Y.; Lin, Y.-Z. A 10-Bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Wang, H.; Zhu, Z. Energy-Efficient and Reference-Free Monotonic Capacitor Switching Scheme with Fewest Switches for SAR ADC. IEICE Electron. Express. 2015, 12, 20141202. [Google Scholar] [CrossRef]

- Yuan, C.; Lam, Y. Low-Energy and Area-Efficient Tri-Level Switching Scheme for SAR ADC. Electron. Lett. 2012, 48, 482. [Google Scholar] [CrossRef]

- Zhu, Z.; Xiao, Y.; Song, X. VCM-Based Monotonic Capacitor Switching Scheme for SAR ADC. Electron. Lett. 2013, 49, 327–329. [Google Scholar] [CrossRef]

- Xie, L.; Wen, G.; Liu, J.; Wang, Y. Energy-Efficient Hybrid Capacitor Switching Scheme for SAR ADC. Electron. Lett. 2014, 50, 22–23. [Google Scholar] [CrossRef]

- Wang, H.; Xie, W.; Chen, Z. Area-Efficient Capacitor-Splitting Switching Scheme with a Nearly Constant Common-Mode Voltage for SAR ADCs. J. Circuit Syst. Comp. 2020, 29, 2020005. [Google Scholar] [CrossRef]

- Hu, Y.; Hu, L.; Tang, B.; Yi, Z. A 10 Bit 1 MS/s SAR ADC with One LSB Common-Mode Shift Energy-Efficient Switching Scheme for Image Sensor. Front. Phys. 2022, 10, 1102674. [Google Scholar] [CrossRef]

- Schinkel, D.; Mensink, E.; Klumperink, E.; van Tuijl, E.; Nauta, B. A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007; pp. 314–605. [Google Scholar]

- Xie, Y.; Liang, Y.; Liu, M.; Liu, S.; Zhu, Z. A 10-Bit 5 MS/s VCO-SAR ADC in 0.18-μm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 26–30. [Google Scholar] [CrossRef]

- Song, Y.; Xue, Z.; Xie, Y.; Fan, S.; Geng, L. A 0.6-V 10-Bit 200-kS/s Fully Differential SAR ADC With Incremental Converting Algorithm for Energy Efficient Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 449–458. [Google Scholar] [CrossRef]

- Zhang, H.; Zhang, H.; Song, Y.; Zhang, R. A 10-Bit 200-kS/s 1.76-μW SAR ADC with Hybrid CAP-MOS DAC for Energy-Limited Applications. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

| Switching Scheme | Average Energy | Energy Saving | Number of Reference Voltages | Area Reduction | Common-Mode Shift |

|---|---|---|---|---|---|

| Conventional [13] | 1363.3 | Reference | 2 | Reference | 0 |

| Set and Down [14] | 255.5 | 81.26% | 2 | 50% | 512 LSB |

| Wang [15] | 128 | 90.61% | 3 | 75% | 512 LSB |

| Tri-level [16] | 42.42 | 96.89% | 3 | 75% | 256 LSB |

| VMS [17] | 31.88 | 97.66% | 3 | 75% | 256 LSB |

| Hybrid [18] | 15.88 | 98.83% | 3 | 75% | 384 LSB |

| VQS [19] | 26.58 | 98.10% | 4 | 87.5% | 1 LSB |

| TSC [20] | 21.08 | 98.45% | 3 | 75% | 1 LSB |

| Proposed | 52.58 | 96.14% | 2 | 75% | 1 LSB |

| Parameter | [19] * | [20] * | [23] | [12] | [24] | This Work ** |

|---|---|---|---|---|---|---|

| Process (nm) | 180 | 180 | 180 | 180 | 180 | 180 |

| Resolution (bits) | 10 | 10 | 10 | 10 | 10 | 9/10 |

| Sampling Rate (kS/s) | 20 | 1000 | 200 | 200 | 200 | 100 |

| Supply Voltage (V) | 0.6 | 1.5 | 0.6 | 0.6 | 0.6 | 1 |

| ENOB (bits) | 9.4 | 9.69 | 9.3 | 9.08 | 9.16 | 7.74/8.84 |

| DNL (LSB) | −0.569/0.572 | −0.30/0.33 | −0.26/0.29 | −0.32/0.30 | −0.21/0.27 | −0.33/0.4 |

| INL (LSB) | −0.422/0.533 | −0.20/0.36 | −0.80/0.36 | −0.56/0.38 | −0.45/0.43 | −0.32/0.25 |

| Power Consumption (µW) | 0.042 | 10.45 | 2.01 | 1.01 | 1.76 | 0.47/0.67 |

| FoM (fJ/conv. Step) | 3.11 | 12.65 | 15.51 | 9.32 | 15.38 | 21.9/14.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hu, Y.; Chen, C.; Hu, L.; Huang, Q.; Tang, B.; Hu, M.; Yuan, B.; Wu, Z.; Li, B. A 9-10-Bit Adjustable and Energy-Efficient Switching Scheme for Successive Approximation Register Analog-to-Digital Converter with One Least Significant Bit Common-Mode Voltage Variation. Sensors 2024, 24, 3273. https://doi.org/10.3390/s24113273

Hu Y, Chen C, Hu L, Huang Q, Tang B, Hu M, Yuan B, Wu Z, Li B. A 9-10-Bit Adjustable and Energy-Efficient Switching Scheme for Successive Approximation Register Analog-to-Digital Converter with One Least Significant Bit Common-Mode Voltage Variation. Sensors. 2024; 24(11):3273. https://doi.org/10.3390/s24113273

Chicago/Turabian StyleHu, Yunfeng, Chaoyi Chen, Lexing Hu, Qingming Huang, Bin Tang, Mengsi Hu, Bingbing Yuan, Zhaohui Wu, and Bin Li. 2024. "A 9-10-Bit Adjustable and Energy-Efficient Switching Scheme for Successive Approximation Register Analog-to-Digital Converter with One Least Significant Bit Common-Mode Voltage Variation" Sensors 24, no. 11: 3273. https://doi.org/10.3390/s24113273